一种基于fpga的高分辨率数字pwm信号调制方法及系统

技术领域

1.本发明涉及电力电子技术领域,具体涉及一种基于fpga(fieldprogrammablegatearray,现场可编程门阵列)的高分辨率数字pwm(pulsewidthmodulation,脉冲宽度调制)信号调制方法。

背景技术:

2.电力电子功率变换器的高频化有利于减小装置的体积,提高装置整体功率密度。数字控制技术由于其高效,可靠,控制灵活的优点,已广泛应用于高频电力电子功率变换器中。在电力电子功率变换器的高频数字控制中,开关器件的pwm精度决定了电力电子变换装置的电压调节精度和控制稳定性,更高精度的pwm发波可以保证输出电压的控制精度,避免极限环振荡,改善高频电力电子功率变换器的性能。

3.目前在高频电力电子变换器中用于提高pwm脉宽精度的数字调制方法主要实现方式为两种:一是利用dsp(digitalsignalprocessing,数字信号处理)的hrpwm(high-resolutionpulsewidthmodulator,高分辨率脉宽调制器)外设提供高分辨率的pwm信号,但dsp的专用pwm接口数量较少,在模块化系统应用中模块之间的pwm也较难保持同步,而且随着开关频率的提高,dsp中断周期时间会变短,控制程序的处理时间往往不够,这极大限制了其应用在高性能,高实时性要求的场合。二是fpga,由于其具有以下特点:(1)利用硬件实现并行处理,运算速度快,运算能力强(2)硬件可编程,易于移植,扩展性强(3)接口配置灵活。使得fpga在数字控制中具有明显优势,尤其适合应用在大功率多模块高频电力电子变换器中。

4.目前fpga用于产生pwm信号的方法主要是计数器比较法。即通过内部时钟信号建立相应的载波计数器,通过调制信号与载波计数器进行比较产生期望的pwm信号,但是这种方法调制得到的pwm脉冲精度最小为时钟信号的周期。目前一些低成本,高性价比的fpga最大可运行的时钟频率一般要小于200mhz,即脉冲宽度单步调节精度只能达到5ns。即使一些昂贵的高性能fpga,其最大可运行的时钟频率一般也要小于1ghz,单步脉冲调节精度也只能达到1ns,性价比极低,难以进一步提高pwm信号的输出精度。在更高开关频率,更高直流母线电压,更低输出电压的电力电子变换器中,无法满足输出精度要求。

技术实现要素:

5.针对现有技术的上述问题,为了实现高分辨率pwm信号发波,本发明提供了一种基于fpga的高分辨率数字pwm信号调制方法,在不改变fpga时钟频率的条件下,构造多路移相pwm信号,实现了高分辨率pwm信号发波,提高了电力电子变换器输出电压控制精度,避免了极限环振荡问题,所述方法易于扩展,满足实际应用需求。

6.为实现上述目的,本发明的技术方案如下:一种基于fpga的高分辨率数字pwm信号调制方法,包括如下步骤:步骤一、利用fpga内部锁相环产生n路同频的移相时钟信号;

步骤二、选择移相时钟信号中相角为0度的时钟信号作为基准时钟,用所述的基准时钟产生周期为t的载波计数器;步骤三、将调制波数值记为m,m为大于等于0的自然数,如果m小于2n,用于与基准时钟下产生的载波计数信号进行比较的调制波数值为m,否则用于比较的调制波数值为m-2n,将用于比较的调制波数值记为m0,当载波计数器的计数值大于m0时,pwm输出为低电平,否则输出为高电平,以此生成基准pwm信号;步骤四、对于n路同频的移相时钟信号、

…

,使用移相时钟信号的上升沿及下降沿触发功能,通过dq触发器将基准pwm信号,分别移相0

°

,

…

,共计生成2n路pwm信号,记为,

…

;步骤五、判断m和2n的关系,利用所述的2n路pwm信号,通过逻辑处理功能生成高分辨率pwm信号:5.1)判断m是否小于2n,并计算m0/2n的余数,记为r,r为0至2n-1的自然数;若m《2n,根据r,通过多路选择器选择及对应的移相角为的信号,将与进行异或逻辑运算后再与进行与逻辑运算,得到高分辨率pwm输出信号;5.2)若m≥2n,根据r,通过多路选择器选择及对应的移相角为的信号,将与进行或逻辑运算,得到高分辨率pwm输出信号。

7.进一步的改进,所述步骤一如下所示:利用fpga内部锁相环生成n个频率为f

clk

,相位依次交错滞后的同频移相时钟信号。

8.进一步的改进,所述步骤二如下所示:步骤二、选择移相角为0度的移相时钟信号作为基准时钟,利用基准时钟的上升沿产生周期为t的载波计数器;载波计数器在基准时钟频率下从0开始计数,每个基准时钟周期载波计数器加2n,直至计数值达到((t/f

clk

)-1)*2n,载波计数器置位为0,开始重复下一周期的计数。

9.进一步的改进,n为fpga内部锁相环可支持的数量。

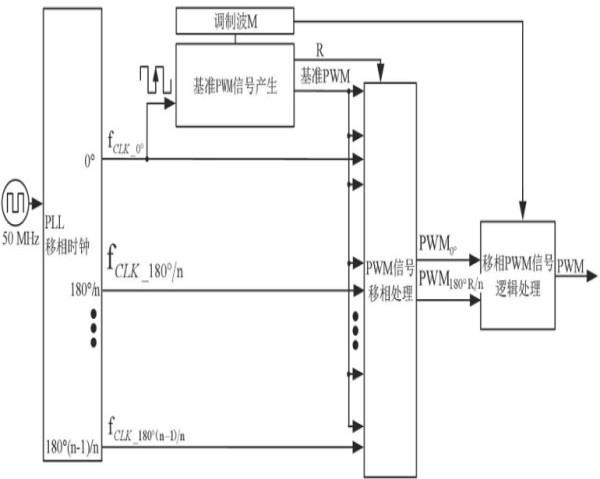

10.一种基于fpga的高分辨率数字pwm信号调制系统,所述系统用于实施上述基于fpga的高分辨率数字pwm信号调制方法;所述系统包括基准pwm信号产生单元、pwm信号移相处理单元和移相pwm信号逻辑处理单元;基准pwm信号产生单元,用于生成基准pwm信号;pwm信号移相处理单元,用于将所述的基准pwm信号进行移相处理,产生2n路移相pwm信号;移相pwm信号逻辑处理单元,用于将所述的2n路移相pwm信号生成高分辨率pwm输出信号。

11.综上所述,本发明所构思的技术方案,与现有技术相比,具有以下优点:本发明提供的一种基于fpga的高分辨率数字pwm信号调制方法,首先利用fpga芯片内部pll产生n路同频的移相时钟,利用产生的基准时钟构造数字载波,然后与调制波比较,生成基准pwm信号,在n路同频移相时钟的作用下,利用时钟的上升沿和下降沿触发功

能,产生2n路移相pwm信号,

…

,通过多路选择器,选择相应移相pwm信号进行逻辑处理,从而产生高分辨率pwm信号;该方法巧妙使用fpga内部pll的移相及时钟边沿触发功能,使用n个移相时钟,在不改变fpga芯片性能的条件下,将pwm脉冲宽度分辨率提高至fpga工作时钟周期的2n倍,且由于fpga内部pll移相精度高,移相pwm信号产生及逻辑处理路径一致,不同移相pwm信号由于逻辑处理延迟导致的偏差也一致,故该方法产生的pwm信号调节线性度极好;该方法特别适用于高频、高输入电压、低输出电压、高实时性控制的场合,可以使用低成本fpga实现电子功率变换器高精度控制,具有较强的通用性及极高的实用价值。

附图说明

12.图1为本发明pwm信号调制方法的控制结构原理框图。

13.图2为基准pwm信号产生单元的控制结构原理框图。

14.图3为pwm信号移相处理单元的控制结构原理框图。

15.图4为移相pwm信号逻辑处理单元的控制结构原理框图。

16.图5为本发明实施实例方法产生高分辨率pwm信号的波形示意图。

17.图6为低压dc/dc电源采样常规pwm调制方法输出1v时的实测波形。

18.图7为低压dc/dc电源采样本发明实施例提供的基于fpga的高分辨率数字pwm信号调制方法输出1v时的实测波形。

具体实施方式

19.为了更清晰的描述本发明方法的技术方案及优点,下面结合附图及实施例对本发明的技术方案及其工作原理进行更为详细的说明。

20.如图1所示,一种基于fpga的高分辨率数字pwm信号调制方法,包括由fpga内部pll产生的相位依次交错滞后的n路时钟信号,基准pwm信号产生单元,pwm信号移相处理单元,移相pwm信号逻辑处理单元;其中图2为基准pwm信号产生单元,图3为pwm信号移相处理单元,图4为移相pwm信号逻辑处理单元,图5为高分辨率pwm信号产生方法的波形图,具体实施步骤如下:(1)利用fpga内部锁相环生成n个频率为,相位依次交错滞后的同频时钟信号,如图1及图5所示。

21.(2)选择移相角为0度的时钟信号作为基准时钟,利用基准时钟的上升沿产生周期为t的载波计数器。载波计数器在基准时钟频率下从0开始计数,每个基准时钟周期计数器加2n,直至计数值达到((t/f

clk

)-1)*2n,载波计数器置位为0,开始重复下一周期的计数,如图1及图5所示。

22.(3)将调制波数值记为m(m为大于等于0的自然数),如果m小于2n,用于与基准时钟下产生的载波计数信号进行比较的调制波数值为m,否则用于比较的调制波数值为m-2n,将用于比较的调制波数值记为m0,当载波计数器数值大于m0时,pwm输出为低电平,否则输出为高电平,以此生成基准pwm信号,如图1、图2及图5所示。

23.(4)利用步骤(1)中生成的移相时钟,

…

,使用移相时钟的上升沿及下降沿触发功能,通过dq触发器将步骤(3)中生成的基准pwm信号分别移相0

°

,

…

,共计生成2n路pwm信号,记为,

…

,如图1、图3及图5所示。

24.(5)判断m是否小于2n,并计算m0/2n的余数,记为r,若m《2n,根据r,通过多路选择器选择及对应的移相角为的信号,将与进行异或逻辑运算后再与进行与逻辑运算,得到高分辨率pwm输出信号,如图1、图4及图5所示。其中r为0至2n-1的自然数。

25.(6)若m≥2n,根据r,通过多路选择器选择及对应的移相角为的信号,将与进行或逻辑运算,得到高分辨率pwm输出信号,如图1、图4及图5所示。

26.该方法巧妙使用fpga内部pll的移相及时钟边沿触发功能,使用n个移相时钟,在不改变fpga芯片性能的条件下,将pwm脉冲宽度分辨率提高至fpga工作时钟周期的2n倍,且由于fpga内部pll移相精度高,移相pwm信号产生及逻辑处理路径一致,不同移相pwm信号由于逻辑处理延迟导致的偏差也一致,故该方法产生的pwm信号调节线性度极好;该方法特别适用于高频、高输入电压、低输出电压、高实时性控制的场合,可以使用低成本fpga实现数字电源高精度控制,具有极高的实用价值。

27.在该实施例中,移相时钟数量n可根据实际选用的fpga内部pll可支持的数量进行扩展,在本实施例中选用cyclone iv系列的ep4ce10,2个pll,共支持10路不同频率相位的时钟,单路时钟工作频率200mhz,周期5ns。将其按照实施例中的方法配置后,通过多路移相pwm信号,最终产生的pwm信号精度相比于常规方法提高了20倍,即脉冲宽度分辨率达到了250ps。以输入48v,输出1v的低压dc/dc电源为例,图6是常规方法产生的pwm信号得到的输出电压波形,图7是采用本发明所提供的方法得到的输出电压波形。通过对比证明,采用本发明方法所生成的pwm信号进行控制,输出电压抖动更小,控制精度更高。在多模块电力电子变换器应用中,只需要将本发明方法的pwm信号生成模块例化调用,即可实现扩展应用。

28.以上所述仅是本发明的优选实施方式,应当指出,任何熟悉本领域的技术人员,在本发明技术方案的基础上,均可利用上述方法对本发明的技术方案进行多种形式的变动,或修改为等效实施例。所以,凡是未超出本发明技术方案的范围,根据本发明技术方法所作的简易变动或等效变化,均属于本发明方法的保护范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。