一种提高贴片无源晶振周围信号质量的pcb布局布线结构

技术领域

1.本实用新型涉及pcb布局、布线技术领域,尤其是指一种提高贴片无源晶振周围信号质量的pcb布局布线结构。

背景技术:

2.晶体振荡器是指从一块石英晶体上按一定方位角切下薄片(简称为晶片),石英晶体谐振器,简称为石英晶体或晶体、晶振,而在封装内部添加ic组成振荡电路的晶体元件称为晶体振荡器。其产品一般用金属外壳封装,也有用玻璃壳、陶瓷或塑料封装的。

3.晶体振荡器包括无源晶振和有源晶振两种类型。

4.无源晶振需要用cpu内的振荡器。无源晶振只有两个引脚,无源晶振没有电源电压,其信号电平是根据起振电路来决定的,是可变的,同样的晶振可以适用于多种电压,可适应于不同电压要求的cpu。通常,无源晶振的价格比较较低,在民用的产品当中为了降低成本大部分都是应用无源晶振。

5.有源晶振是一个完整的振荡器,里面有石英晶体、晶体管和阻容元件。有源晶振的封装如下图所示,有4个引脚。分别为vcc(电源)、gnd(地)、out(时钟信号输出)、nc(空脚)。

6.晶振作为电路系统中的重要器件之一,除了关注其本身的产品质量外,还要重视晶振的pcb layout。相同模块中,若晶振及周围器件的布局、布线处理不当,将引起电磁干扰。在一些对电磁干扰信号比较敏感的电路中,晶振的辐射会干扰到敏感信号,使其信号质量变差,甚至导致电路无法正常工作。

7.大部分pcb layout工程师版图设计时,对晶振的处理包括几种方法:对晶振子功能模块进行简单的同层包地处理;晶振区域下方的一层或多层铜箔挖掉;晶振地与其他信号地之间通过电容或者其他隔离器件进行隔离;将晶振置于屏蔽罩中;晶振周围的地与大地用隔离带进行物理隔离。

8.现有技术存在以下缺点:增加隔离器件将增加模块成本,增大模块的体积;晶振周围的地与大地用隔离带进行物理隔离,对晶振与表层信号的隔离度无益;晶振区域下方的一层或者多层铜箔挖掉,将使晶振与内层信号间的隔离度降低。

技术实现要素:

9.为此,本实用新型所要解决的技术问题在于克服现有技术中对晶振与表层信号的隔离度无益;晶振区域下方的一层或者多层铜箔挖掉,将使晶振与内层信号间的隔离度降低的问题,从而提供一种提高贴片无源晶振周围信号质量的pcb布局布线结构。

10.为解决上述技术问题,本实用新型的一种提高贴片无源晶振周围信号质量的pcb布局布线结构,所述pcb板上依序层叠设有若干功能层,其布线结构包括芯片组、晶振、电容ⅰ、电容ⅱ、晶振周围信号走线、电容接地过孔、地属性通孔、晶振信号走线,所述的pcb板包括pcb板top层、pcb板l2层、pcb板l3层、pcb板l4层、pcb板l5层、pcb板l6层、pcb板l7层、pcb板bottom层,其中各个功能层均通过电容接地过孔、地属性通孔相互连接;

11.所述的芯片组通过osc_in和osc_out引脚与晶振、电容ⅰ、电容ⅱ之间使用晶振信号走线相连,且所述的芯片组、晶振、电容ⅰ、电容ⅱ设于pcb板top层上;

12.所述的地属性通孔设于晶振、电容ⅰ、电容ⅱ的外侧。

13.在本实用新型的一个实施例中,所述的地属性通孔为两排交错放置的通孔。

14.在本实用新型的一个实施例中,所述的晶振信号走线两侧还设有晶振周围信号走线、周围附属信号走线,且晶振信号走线设于设于pcb板top层,以及晶振周围信号走线设于pcb板top层,周围附属信号走线设于pcb板l3层、pcb板l5层、pcb板l7层。

15.在本实用新型的一个实施例中,所述的地属性通孔以及晶振、电容ⅰ、电容ⅱ的区域在pcb板l2层、pcb板l3层、pcb板l4层、pcb板l5层、pcb板l6层、pcb板l7层、pcb板bottom层的投影区域均铺地属性铜皮。

16.在本实用新型的一个实施例中,所述晶振信号走线和信号焊盘距离地铜皮为6mil。

17.在本实用新型的一个实施例中,所述晶振信号走线始于晶振焊盘,沿晶振外侧,连接到芯片组pin脚。

18.本实用新型的上述技术方案相比现有技术具有以下优点:本实用新型所述的一种提高贴片无源晶振周围信号质量的pcb布局布线结构,为了提高晶振与内层其他信号间的隔离度,减小晶振谐波辐射对信号质量造成的影响,其中的晶振作为强干扰源,在布局、布线时应使敏感信号远离干扰源。减小晶振对其他信号产生的干扰,即提高其他信号与晶振及其信号线间的隔离度。晶振及周围器件在内层投影区域铺地铜皮以及在其周围增加两排交错的地属性过孔可以增加内层信号和表层晶振及信号线的隔离度,减小了其他信号线被干扰的风险。

附图说明

19.为了使本实用新型的内容更容易被清楚的理解,下面根据本实用新型的具体实施例并结合附图,对本实用新型作进一步详细的说明。

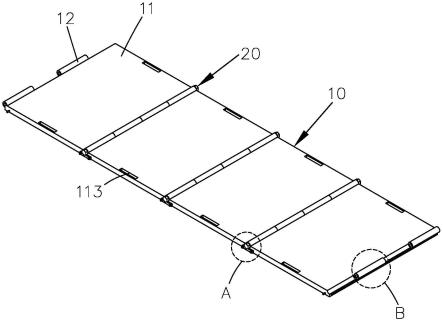

20.图1是本实用新型一种提高贴片无源晶振周围信号质量的pcb布局布线结构中pcb板top层的结构示意图;

21.图2是本实用新型所述pcb板l2层的结构示意图;

22.图3是本实用新型所述pcb板l3层的结构示意图;

23.图4是本实用新型所述pcb板l4层的结构示意图;

24.图5是本实用新型所述pcb板l5层的结构示意图;

25.图6是本实用新型所述pcb板l6层的结构示意图;

26.图7是本实用新型所述pcb板l7层的结构示意图;

27.图8是本实用新型所述pcb板bottom层的结构示意图;

28.图9是本实用新型所述晶振走线与l3层信号线隔离度仿真结果。

29.如图所示:1、芯片组,2、晶振,3、电容ⅰ,4、电容ⅱ,5、晶振周围信号走线,5-1、周围附属信号走线,6、电容接地过孔,7、地属性通孔,8、晶振信号走线。

具体实施方式

30.如图1所示,本实施例提供一种提高贴片无源晶振周围信号质量的pcb布局布线结构,所述pcb板上依序层叠设有若干功能层,其布线结构包括芯片组1、晶振2、电容ⅰ3、电容ⅱ4、晶振周围信号走线5、电容接地过孔6、地属性通孔7、晶振信号走线8,所述的pcb板包括pcb板top层、pcb板l2层、pcb板l3层、pcb板l4层、pcb板l5层、pcb板l6层、pcb板l7层、pcb板bottom层,其中各个功能层均通过电容接地过孔6、地属性通孔7相互连接;

31.所述的芯片组1通过osc_in引脚1-1和osc_out引脚1-2与晶振2、电容ⅰ3、电容ⅱ4之间使用晶振信号走线8相连,且所述的芯片组1、晶振2、电容ⅰ3、电容ⅱ4设于pcb板top层上;

32.所述的地属性通孔7设于晶振2、电容ⅰ3、电容ⅱ4的外侧,其中的pcb印制板的层叠包括但不限于8层结构。

33.进一步地,晶振2的放置位置较为关键,但晶振2不管放置在哪里,都避免不了晶振2投影区域的内层走线层的周围有其他信号线。晶振2作为强干扰源,在布局、布线时应使敏感信号远离干扰源,减小晶振对其他信号产生的干扰,即提高其他信号与晶振及其信号线间的隔离度。晶振2及周围器件在内层投影区域铺地铜皮以及在其周围增加两排交错的地属性通孔7可以增加内层信号和表层晶振及信号线的隔离度,减小了其他信号线被干扰的风险。

34.所述的地属性通孔7为两排交错放置的通孔。

35.进一步地,如图2~8所示,所述的晶振信号走线8两侧还设有晶振周围信号走线5、周围附属信号走线5-1,且晶振信号走线8设于pcb板top层,以及晶振周围信号走线5设于pcb板top层,周围附属信号走线5-1设于pcb板l3层、pcb板l5层、pcb板l7层。所述的地属性通孔7以及晶振2、电容ⅰ3、电容ⅱ4的区域在pcb板l2层、pcb板l3层、pcb板l4层、pcb板l5层、pcb板l6层、pcb板l7层、pcb板bottom层的投影区域均铺地属性铜皮。

36.所述晶振信号走线8和信号焊盘距离地铜皮为6mil,该距离满足印制板加工要求即可。

37.所述晶振信号走线8始于晶振2焊盘,沿晶振2外侧,连接到芯片组1pin脚。

38.进一步地,如图9所示,从仿真结果看出本发明所述方法的晶振走线与内层走线间的隔离度比其他晶振的布局、布线方法更优,至少提高1db。在一定程度上,所述方法减小了周围信号对时钟的干扰,也减小的晶振向外辐射对周围信号造成的干扰;本发明不涉及增加器件和因引入印制板的特殊加工工艺,能在不增加bom成本和pcb加工成本的基础上,最大限度的提高布线在晶振周围信号的信号质量。

39.显然,上述实施例仅仅是为清楚地说明所作的举例,并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引申出的显而易见的变化或变动仍处于本实用新型创造的保护范围之中。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。