1.本公开涉及驱动电路、显示装置和驱动方法。

背景技术:

2.由诸如有机el的微显示器表示的显示装置包括:像素阵列,通过多个像素显示图像;水平驱动电路,将视频信号写入像素阵列的每个像素;垂直驱动电路,选择写入视频信号的视频信号线;水平逻辑电路,被配置为控制水平驱动电路;以及垂直逻辑电路,被配置为控制垂直驱动电路。显示装置进一步包括:接口,将至显示装置的输入信号转换成逻辑电平输出信号;以及控制器,基于由接口转换的输出信号控制垂直驱动电路和水平驱动电路的操作定时。

3.下面的专利文献1公开了通过恒定电流pwm驱动来提高图像质量的像素的驱动实例。在该文献中公开的技术中,首先,将根据输入信号电压的电压保持在像素中的开关控制晶体管的栅极处,然后,将偏置电压保持在有机el的驱动晶体管的栅极处。此后,斜坡(ramp)波经由电容器施加至节点。电路将恒定电流施加至有机el发光元件,直至节点的电压响应于斜波的施加而增大并且节点的电压达到开关控制晶体管的阈值电压。因为像素需要用于有机el发光元件的pwm控制的ramp波,所以存在功耗增加、横向阴影以及横向串扰劣化的问题。

4.现有技术文献专利文献

5.专利文献1:jp2013-76812

技术实现要素:

6.本发明要解决的问题

7.本公开提供一种用于降低功耗的驱动电路、显示装置和驱动方法。

8.问题的解决方案

9.本公开的驱动电路包括:设定电路,被配置为将视频信号线预充电至第一电压,该视频信号线连接至被配置为对所述视频信号线的电压进行采样的第一晶体管;以及调整电路,被配置为通过在与设定在所述视频信号线中的第二电压相对应的时间段期间,对预充电至所述第一电压的所述视频信号线进行充电或放电,来调整所述视频信号线的电压。

10.设定电路可以包括将视频信号线连接到第一电压的第一开关,并且调整电路包括电流源和第二开关,电流源包括第二晶体管,第二开关将视频信号线与电流源连接。

11.驱动电路可以包括检测电路和保持电路,检测电路包括连接到第二电压的第一端子和连接到视频信号线的第二端子,并且被配置为检测第二电压和视频信号线的电压之间的差,保持电路被配置为保持根据差的电压并将电压供应至电流源的控制端子。

12.检测电路可包括放大器,放大器被配置为根据第二电压与视频信号线的电压之间的差生成电流,保持电路包括电容器,该电容器被配置为累计根据电流的电荷。

13.驱动电路包括连接第一端子和第二端子的第三开关,并且调整电路在放大器的操

作之前接通第三开关一段时间。

14.检测电路可包括:比较器,被配置为检测视频信号线的电压变为第二电压的定时;相位比较器,被配置为检测定时与根据第二电压的定时之间的差;以及充电泵,被配置为根据差生成电流,保持电路可包括:电容器,被配置为累计根据电流的电荷。

15.检测电路可包括转换电路,转换电路被配置为将第二电压与视频信号线的电压之间的差转换为数字信号,并且保持电路可包括数模转换器,数模转换器被配置为将根据数字信号的电压供应至控制端子。

16.第一电压可以是与最大灰度或最小灰度对应的电压。

17.第二电压可以是与使包括第一晶体管的像素电路显示的灰度对应的电压。

18.第二电压可包括用于校正用于驱动包括第一晶体管的像素电路中的发光元件的第二晶体管的阈值电压的偏移电压。

19.所述驱动电路可以包括扫描电路,所述扫描电路被配置为导通所述第一晶体管并且将设定为所述偏移电压的所述视频信号线的电压供应至所述像素电路内的节点,所述设定电路可以在向像素电路供应偏移电压之后,将所述视频信号线预充电至所述第一电压,所述调整电路可以通过在根据与灰度对应的电压的时间段期间对预充电至所述第一电压的所述视频信号线进行充电或放电,来将所述视频信号线调整到与所述灰度对应的电压,并且所述扫描电路可以导通所述第一晶体管以将所述视频信号线的电压供应至所述像素电路内的节点。

20.驱动电路可以包括多个子驱动电路和电流生成电路,每个子驱动电路包括设置电路和调整电路,电流生成电路被配置为生成基准电流,多个子驱动电路可以连接到多个视频信号线,多个子驱动电路中的每个的调整电路可以包括被配置为对基准电流进行采样的第三晶体管,多个子驱动电路中的每个的调整电路可以利用由第三晶体管采样的电流对由设定电路预充电的视频信号线进行充电或放电。

21.电流生成电路可包括:第一电容器,连接至第三电压;电流源,包括第四晶体管;第四开关,连接第一电容器和电流源;第五开关,连接第一电容器的两端;检测电路,包括连接至第四电压的第一端子和连接至第四开关的第二端子,检测电路被配置为检测第一端子的电压与第二端子的电压之间的差;保持电路,被配置为保持根据差的电压并且将电压供应至电流源的控制端子;第六开关,二极管连接多个子驱动电路中的每个的第三晶体管;以及第七开关,连接多个子驱动电路中的每个的二极管连接的第三晶体管和电流源。

22.第四开关和第五开关可以接通以对第一电容器预充电,第五开关可以断开以使第一电容器放电以生成参考电流,第四开关可以断开以操作检测电路一段时间,并且第六开关和第七开关可以接通以对子驱动电路中的基准电流进行采样。

23.在第一晶体管截止期间,设定电路将视频信号线预充电到第一电压,调整电路将视频信号线调整到第二电压。

24.第一晶体管截止的周期可包括消隐周期,消隐周期包括包含第一晶体管的像素电路不发光的周期。

25.本公开的显示装置包括:视频信号线,被配置为提供视频信号;像素电路,包括连接至视频信号线的第一晶体管,第一晶体管被配置为对视频信号线的电压进行采样;驱动电路,包括:设定电路,被配置为将视频信号线预充电至第一电压;以及调整电路,被配置为

通过与视频信号线中设定的第二电压相对应的时间段期间,对预充电至第一电压的视频信号线充电或放电,来调整视频信号线的电压;以及扫描电路,被配置为控制第一晶体管的导通和截止。

26.本公开的驱动方法包括将连接到被配置为对视频信号线的电压进行采样的第一晶体管的视频信号线预充电到第一电压;以及通过在与视频信号线中设置的第二电压相对应的时间段期间,对预充电所述第一电压的所述视频信号线进行充电或放电,来调整视频信号线的电压。

附图说明

27.图1是示意性示出根据本公开的第一实施方式的显示装置中的水平驱动电路和像素阵列的配置实例的示图。

28.图2是示出水平驱动电路中的驱动电路和像素的示图。

29.图3是示出了像素及其外围电路的配置的框图。

30.图4是示出图2的驱动电路的时序图的示图。

31.图5是示出在输出电流源是pmos晶体管的情况下的驱动电路的实例的示图。

32.图6是图5的驱动电路的时序图。

33.图7是示出驱动电路的另一配置实例的框图。

34.图8是图7的驱动电路的时序图。

35.图9是示出根据第一特定实例的驱动电路的配置实例的图。

36.图10是示出图7中的ota的电路配置的实例的示图。

37.图11是示出在n信道驱动的情况下的ota的电路配置的实例的示图。

38.图12是示出根据第二特定实例的驱动电路的配置实例的图。

39.图13是示出根据第三特定实例的驱动电路的配置实例的图。

40.图14是示出根据第二实施方式的像素及其外围电路的框图。

41.图15是根据第二实施方式的驱动电路的时序图。

42.图16是根据第三实施方式的驱动电路的框图。

43.图17是示出电流生成电路和子驱动电路的配置实例的图。

44.图18是图17的驱动电路的时序图。

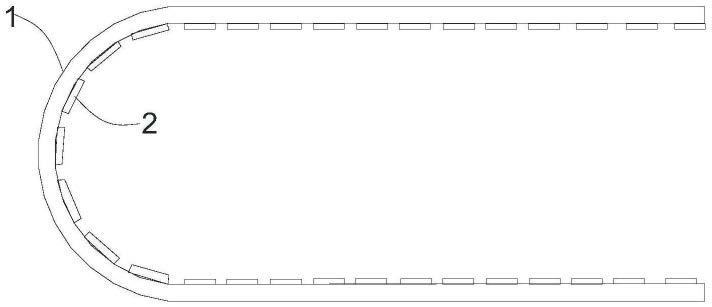

45.图19示意性示出了作为有源矩阵型显示装置中的水平驱动电路的电压跟随器驱动系统的配置。

46.图20是示意性地示出使用rampdac方法的水平逻辑电路和水平驱动电路的配置的示图。

具体实施方式

47.在下文中,将参照附图描述本公开的实施方式。在本技术公开的一个或多个实施例中,各实施例包含的元素可以相互组合,组合结果也构成本技术一部分实施例。

48.首先,将描述本公开的实施方式的技术背景。

49.图19示意性示出了作为有源矩阵型显示装置中的水平驱动电路的电压跟随器驱动系统的配置。水平驱动电路1002从水平逻辑电路1001接收用于像素电路(在下文中,像

素)的数据信号,并且通过电平移位器(ls)1003将数据信号校正为根据伽马特性的电压。校正后的电压由数模转换器(dac)电路1004转换成模拟信号。模拟信号通过施加了预定偏置电压的运算放大器(缓冲放大器)1005进行阻抗变换。阻抗变换之后的信号的电压被施加到像素阵列1007中的由输出选择器(解复用器)1006选择的像素列的视频信号线(像素信号线)。在所选择的像素列中,通过垂直驱动电路(未示出)选择将被写入信号的像素。

50.在图19的电压跟随器系统中,水平驱动电路1002包括对应于多个像素列的一个水平驱动电路(ls、dac、运算放大器、输出选择器),并且对输出选择器1006执行时分控制以抑制功耗和电路面积的增加。在该系统中,由于电压跟随器缓冲用于驱动像素的电压,所以存在在高清晰度的情况下相对不太可能发生图像质量劣化的优点。然而,随着清晰度更高,新道的数量(像素列的数量)增加,并且每个像素列(信道)的电压跟随器的dc偏置电力增加。

51.使用称为rampdac方法的视频信号写入方法也是已知的,而不是图19中的电压跟随器方法。

52.图20示意性地示出了在有源矩阵型显示装置中使用rampdac方法的水平逻辑电路和水平驱动电路的配置。水平逻辑电路包括移位寄存器1100、第一锁存电路1101和第二锁存电路1102。水平驱动电路包括数字比较器1103、同步计数器1104、pwm生成电路1105、电平移位器1106、开关电路1107和斜坡电路1108(模拟缓冲器,rampdac)。

53.第一锁存器电路1101中的n 1锁存器在时钟latck[0]到latck[n]从移位寄存器1100输入到clk端子的定时采样并锁存与每个像素对应的数据信号(数字灰度数据)。

[0054]

第二锁存电路1102中包括的n 1个锁存器在共用线时钟(lineclk)被输入到clk端子的定时读取并锁存第一锁存电路中的n 1个锁存器中保持的信号。锁存的数据信号被输入到数字比较器1103中的n 1个比较器。

[0055]

同步计数器1104在lineclk被输入到第二锁存电路时的定时被复位,并且开始对从外部提供的灰度时钟进行计数。同步计数器1104对在一个水平扫描周期期间生成的灰度时钟进行计数,以将计数值输出至每个比较器。

[0056]

与各个数字比较器1103对应地设置pwm生成电路1105。每个pwm生成电路1105在输入到比较器的数据信号(对应于灰度值)与输入到比较器的计数值相匹配的时间段期间,输出预定电平的电压作为pwm信号。因此,从每个pwm生成电路1105输出具有根据由对应数据信号指示的灰度值的长度的矩形波作为pwm信号。

[0057]

电平移位器1106对应于各个pwm生成电路1105,根据伽马特性调整从pwm生成电路1105输出的矩形波(pwm信号)的长度,以输出调整后的pwm信号。

[0058]

斜坡电路1108包括:rampdac,被配置为生成斜波,该斜波是电压在一个水平扫描周期内从初始电压以恒定速率改变(升高或降低)的电压波;以及模拟缓冲器,缓冲该斜波。斜坡电路1108根据每个电平移位器1106的输出(或pwm生成电路的输出)的开始定时经由模拟缓冲器输出斜坡波。

[0059]

开关电路1107中的开关对应于相应的电平移位器1106。当从每个电平移位器1106输出的pwm信号(矩形波)被输入以输出斜坡波同时被接通时,每个开关被接通。当pwm信号没有被输入时,每个开关被关断以停止斜波的输出。结果,根据pwm信号的长度的电压被输出到像素阵列1109作为表示相应灰度值的电压(灰度电压)。像素阵列1109使用根据灰度电压的电流经由每个开关来驱动对应像素。

[0060]

图20的rampdac方法比图19的电压跟随器方法需要更少的模拟电路,并且因此具有低功耗和适于小型化的配置。然而,所有像素的负载电容器是模拟缓冲器的负载,并且执行写入如斜波的瞬时变化波形的操作。因此,在向像素写入期间,产生与像素的负载电容器和斜波的斜率对应的电流。该电流导致在写入ramp波形的电压时取决于配线的电阻的诸如横向阴影、横向串扰以及切换噪声的图像质量问题。该问题在分辨率增加的情况下特别明显。

[0061]

本公开解决了与显示设备的高清晰度相关联的大dc偏置电力的问题和图像质量劣化的问题。

[0062]

(第一实施例)

[0063]

图1是示出根据本公开的第一实施方式的有源矩阵型显示装置中的水平驱动电路和像素阵列的框图。水平驱动电路包括移位寄存器1100、第一锁存电路1101、第二锁存电路1102、同步计数器1104、数字比较器1103、pwm生成电路1105、电平转换器1106和电流驱动电路101。块1100至1106具有类似于图20的配置。电流驱动电路101包括与每个像素列对应的驱动电路102。如上所述,通过块1100至1106的处理,对于每个像素产生具有根据数据信号(灰度)的时间宽度的电压(pwm信号),并将该电压(pwm信号)供应给与每个像素列对应的驱动电路102。驱动电路102连接到对应于每个像素列的视频信号线(像素信号线)。驱动电路102根据pwm信号生成电压(灰度电压),并将该电压供应给连接到视频信号线的像素作为视频信号的信号电压。本实施例的特征之一是通过驱动电路102以低功耗和高精度的生成信号电压。

[0064]

图2是示出根据本实施方式的驱动电路102的配置的一部分和一个像素103的示图。

[0065]

驱动电路102包括设定电路104、调整电路105和输出端子vout。输出端子vout的电压由与输出端子相同的参考标号vout表示。设定电路104包括开关pchg(第一开关)。调整电路105包括输出电流源ia和开关pwm(第二开关)。输出电流源ia是nmos晶体管。输出端子vout与视频信号线112连接。像素103连接到视频信号线112。从驱动电路102的角度来看,像素103等效地呈现为电容器。具体地,电容器是从驱动电路102至像素的配线(视频信号线)的电容器、包括在像素103中的采样晶体管的寄生电容器等。采样晶体管连接到视频信号线112,并且对视频信号的信号电压进行采样。该电容器表示为cpix。电容器cpix被称为像素负载电容器。将更具体地描述像素负载电容器cpix。

[0066]

图3是示出了根据本实施方式的有源矩阵型显示装置中的像素103及其外围电路的配置的框图。虽然在图3中示出了一个像素103,但是实际上像素以矩阵形式布置在像素阵列。外围电路包括水平驱动电路10、驱动扫描电路20和写入扫描电路60。驱动扫描电路20和写入扫描电路60对应于垂直驱动电路。像素103的配置是示例,可以采用各种其他配置。为每列像素提供驱动电路102。

[0067]

像素103包括采样晶体管wstr、驱动晶体管drtr、电容器cs、和发光元件30。假定每个晶体管是nmos晶体管,但可以是pmos晶体管,或者可以混合两种导电类型的晶体管。发光元件30是包括阳极和阴极的双端子型有机el发光元件。然而,发光元件30不限于有机el发光元件,并且通常包括通过电流驱动发光的任何装置。

[0068]

驱动晶体管drtr具有连接至节点g的栅极、连接至节点s的源极以及连接至驱动线

50的漏极。发光元件30具有连接到节点s的阳极和连接到为所有像素公共布线的公共电源线70(具有电压vcath)的阴极。采样晶体管wstr连接在视频信号线112和节点g之间。采样晶体管wstr的栅极连接至扫描线40。电容器cs连接在节点g和节点s之间。在驱动线50通过驱动扫描电路20被设置为预定电位并且驱动线50被设置为预定电位的同时,执行以下操作。首先,通过写入扫描电路60将采样晶体管wstr导通特定时间段。视频信号线112的信号电压经由节点g被写入电容器cs,并且电容器cs被设置为信号电位。驱动晶体管drtr根据经由电容器cs施加在栅极与源极之间的栅极电压使电流在漏极与源极之间流动,并且通过电流驱动发光元件30。

[0069]

参考图2描述的像素负载电容器cpix包括存在于这种视频信号线112中的配线电容器、存在于采样晶体管wstr的输入侧上的寄生电容器等。

[0070]

图2的输出电流源ia连接至接地电压和开关pwm。输出端子vout连接到视频信号线112。开关pwm经由输出端vout连接输出电流源ia和视频信号线112。开关pchg连接预充电电压vpchg(第一电压)并经由输出端子vout连接视频信号线112。设定电路104使pchg 104导通,将视频信号线112预充电到预充电电压vpchg。pchg 104被断开,并且在电平移位器所提供的pwm信号的时长期间接通开关pwm。pwm信号是具有根据灰度的时间宽度的矩形电压波形。也就是说,开关pwm在根据第二电压的时间段期间接通,第二电压是要在视频信号线中设置的期望电压。因此,预充电的视频信号线112被充电或放电(即,电容器cpix被充电或放电)。结果,视频信号线112的电压被调整到期望电压,例如,对应于由pwm信号指示的灰度的电压。在调整之后,当写入扫描电路60经由扫描线40导通像素103的采样晶体管wstr时,信号电压被写入像素103中。

[0071]

图4示出了图2的驱动电路102的时序图。时序图示出由驱动电路102生成根据从电平移位器提供的pwm信号电压(第二电压)并将所生成的电压设置为视频信号线112中的信号电压的操作的实例。横轴表示时间。在采样晶体管截止的周期期间执行图4的操作。例如,可在所有像素处于非发光周期的消隐周期中执行图4的操作。

[0072]

在图2中,首先,接通开关pchg,视频信号线112被预充电到预充电电压vpchg一定的周期t1。即,像素负载电容器cpix被预充电到预充电电压vpchg。视频信号线112的电压vsig是预充电电压vpchg(=v1)。接着,使开关pchg断开,在根据pwm信号(灰度值)的时间tpwm期间,使开关pwm导通。结果,预充电的视频信号线112通过输出电流源ia被充电或放电。视频信号线的电压vsig的波形以输出电流iout/像素负载电容器cpix(通过将输出电流iout除以像素负载电容器cpix获得的值)的斜率从预充电电压v1下降。在时间tpwm之后,开关pwm被断开。此时的视频信号线112的电压vsig是输出电压vout。输出电压vout可以用作根据灰度的信号电压。输出电压vout由以下表达式定义。

[0073]

vout=vpchg-(iout

×

tpwm/cpix)

···

表达式(a)。

[0074]

如上所述,通过在pwm信号的时间长度内接通开关pwm,可以产生根据灰度的信号电压。此后,通过接通连接到视频信号线112的像素103的采样晶体管,信号电压被写入到像素103中。这里,作为实例,预充电电压vpchg是对应于pwm信号的最小宽度的电压(对应于最大灰度或最小灰度的电压)。电流源ia被调整成使得当开关pchg接通对应于pwm信号的最大宽度的时间段时,预充电视频信号线(电容器cpix)流过达到对应于pwm信号的最大宽度的电压的电流。注意,与最大灰度对应的电压可被表示为vg255,与最小灰度对应的电压可被

表示为vg0。

[0075]

通过以这种方式在根据pwm信号的时间长度上对规定的预充电电压的视频信号线进行充电或放电,可以对视频信号线准确地设定根据灰度的电压。此外,在图2的驱动电路中执行模拟操作的电路仅包括输出电流源ia,不需要被配置为产生并缓冲ramp波形的电路,因此功耗低。

[0076]

图2和图4示出在输出电流源是nmos晶体管(在n沟道驱动的情况下)的情况下的配置和操作,但是可以类似地提供其中输出电流源是pmos晶体管(在p沟道驱动的情况下)的配置。

[0077]

图5示出了在输出电流源ia是pmos晶体管的情况下的驱动电路102的实例。

[0078]

图6示出了图5的驱动电路的时序图。在该配置中,输出电压vout由以下表达式定义。

[0079]

vout=vpchg (iout

×

tpwm/cpix)

···

表达式(b)。

[0080]

因为图5和图6的描述与图2和图4的描述相似,所以将省去其描述。

[0081]

图7是示出驱动电路102的另一配置的实例的框图。电流校正电路106被添加到图2的驱动电路102。电流校正电路106包括电压控制电流源电路(ota)111、开关cal、保持电容器ch和参考端子vref。在该示例中,输出电流源ia由nmos晶体管配置。电流校正电路106具有降低与各像素列对应的驱动电路的输出电流源ia之间的电流相对变化误差的效果。

[0082]

ota 111具有-输入端子(第一端子)、 输入端子(第二端子)和使能端子。ota 111在输入到使能端子的otaen信号被接通的同时操作。期望在视频信号线中设定的电压(期望电压)作为基准电压vref被供应至ota111的输入端。作为实例,供应对应于由pwm信号表示的灰度的电压。在由pwm信号表示的灰度是最大灰度的情况下,基准电压vref是对应于最大灰度的电压(vg255)。 输入端子连接至输出端子vout,并且输出电压vout(cpix的电压)供应至输出端子vout。ota 111是被配置为检测供应到-输入端子的电压与供应到 输入端子的电压之间的差的检测电路的实例。ota 111根据检测到的差生成电流。更具体地,ota 111计算参考电压vref与输出电压vout之间的差δvin,并且将输出电流改变通过将差δvin与跨导gm相乘而获得的电流。

[0083]

开关cal连接ota 111的输出和保持电容器ch的一端。保持电容器ch的另一端连接至接地电压。保持电容器ch的一端连接至作为电流源ia的nmos晶体管的控制端子(栅极)。保持电容器ch是根据差保持电压并将所保持的电压供应至输出电流源ia的控制端的保持电路的实例。

[0084]

由ota 111生成的电流经由开关cal对保持电容器ch充电或放电。即,在保持电容器ch中蓄积与电流相应的电荷。结果,保持电容器ch的电压被调整。保持电容器ch的电压被供应至nos晶体管的栅极。保持电容器ch具有保持输出电流源ia的栅极电压的作用。ota 111的输出电流的范围是可由包括在ota 111中的电流源(参见稍后描述的图10中的电流源123)生成的电流的范围。具体地,使用ota 111的输入电压差δvin、开关cal被接通的时间ton以及保持电容器的电荷量ch,由gmδvin

×

ton/ch表示输出电流的范围。

[0085]

图8示出了图7的驱动电路102的时序图。横轴表示时间。作为初始状态,开关pchg、开关pwm和开关cal都处于断开状态。

[0086]

(1)首先,使开关pchg导通一定时间t1,使用预充电电压vpchg对视频信号线112进

行预充电,即对像素负载电容器cpix进行预充电。预充电之后的电压表示为v1(=vpchg)。电压v1对应于在pwm信号的最小时间宽度上期望实现的电压。注意,最小的pwm信号的时间宽度可以是0或者长于0的时间。

[0087]

(2)断开开关pchg,并且在根据从电平移位器(见图1)输入的pwm信号(灰度值)的时间tpwm期间,接通开关pwm。结果,视频信号线112经由输出电流源ia被充电或放电(即,像素负载电容器cpix被充电或放电)。输出电流源ia的电流是通过上述表达式a确定的恒定电流。

[0088]

(3)当时间tpwm流逝时,开关pwm断开。在附图的示例中,此时的输出电压vout是电压v1d。接通输入到ota 111的使能端子的otaen信号,使ota 111处于工作状态。接着,使开关cal接通一定时间。ota 111将基准电压vref(期望达到的电压)与输出电压vout(像素负载电容器cpix的电压)进行比较以输出根据电压差的电流。

[0089]

(4)通过从ota 111输出的电流对保持电容器ch进行充电或放电。

[0090]

(5)作为保持电容器ch的电压的充电泵(cp)输出改变。cp输出根据保持电容器ch的充电状态在特定电压范围ra1内改变。

[0091]

可以重复(1)至(5)的操作。结果,可以将视频信号线的电压高精度地调整到期望的电压,同时抑制各像素列之间的偏差。然而,操作(1)至(5)可仅执行一次。例如,在像素的采样晶体管在所有像素不发光的消隐周期中被关断的周期中执行(1)至(5)的操作。在设定视频信号线的信号电压之后,像素的采样晶体管在写入像素的定时导通一定周期,并且视频信号线的信号电压vsig被写入像素。

[0092]

执行图7的驱动电路的模拟操作的电路仅是ota 111和输出电流源ia。ota 111需要仅在栅极电压调整的时段期间操作,并且输出电流源ia需要仅在开关pwm被接通的时段期间操作。因此,根据图7的驱动电路的配置,dc偏置电力仅需要消耗必要的最小周期,并且可以获得降低功耗的效果。

[0093]

[第一具体示例]

[0094]

在开始ota 111中的操作之前,可以通过-输入端子与 输入端子之间的短路来执行偏移消除操作。例如,在otaen信号被接通之后,在cal信号被接通之前的时间段内执行偏移消除操作。通过执行偏移消除操作,可以抑制在对应于多个像素列的每个电流校正电路的ota的操作的偏差。因此,可以提高输出电流的偏差精度。

[0095]

图9示出了根据第一具体实例的驱动电路102的配置实例。添加连接ota 111的两个端子(-输入端子, 输入端子)的开关ini(第三开关)。

[0096]

图10中(a)和图10中(b)示出了图9中的ota 111的电路配置的实例。将参考图7描述偏移消除操作的具体实例。图10中(a)示出了在偏移消除操作期间的电路状态,并且图10中(b)示出了在偏移消除操作之后的电流输出操作期间的电路状态。

[0097]

在图10中的(a)中,pmos晶体管121的栅极( 输入端子)连接至基准电压端子vref。开关cal的一端(-输入端子)连接至vfb端子,输出电压vout(像素负载电容器的电压)输入至vfb端子。vfb端子的电压描述为电压vfb。

[0098]

电流源123共同连接到pmos晶体管121的源极和pmos晶体管122的源极。nmos晶体管124和125的漏极连接到pmos晶体管121的漏极和pmos晶体管122的漏极。nmos晶体管124和125的源极连接到接地电压。nmos晶体管125的栅极经由电容器126连接到接地电压。pmos

晶体管122的漏极与nmos晶体管125的漏极之间的连接节点连接到输出端子otaout。pmos晶体管121的栅极电压由vinp表示,并且pmos晶体管122的栅极电压由vinn表示。

[0099]

开关ini设置在开关cal的另一端和参考电压vref端子(-输入端子)之间。此外,开关132设置在电容器126与nmos晶体管125的漏极之间。在偏移消除操作中,开关ini和132接通一定的时间段以在-输入端子和 输入端子之间短路。此外,通过接通开关132,连接nmos晶体管125的栅极和源极。这种连接被称为二极管连接。因此,电压vinp和电压vinn两者变为相同的参考电压vref(即,输入电位差为0v),并且生成输出电流ical。

[0100]

在这种状态下,如图10中的(b)所示,开关ini和开关132被断开,并且开关cal被接通。因此,输出通过根据基准电压vref和电压vfb之间的电位差的电流与输出电流ical(负载电流)之间的差而获得的电流(gm

×

(vfb-vref))。通过这样的操作,可以消除ota 111自身的相对偏差。该转换的偏移消除操作仅仅是示例,并且可以使用其他偏移消除方法。通过以这种方式执行偏移消除操作,可以抑制在对应于多个像素列的每个电流校正电路的ota的操作的偏差。因此,可以提高输出电流的偏差精度。

[0101]

图10示出了p沟道驱动的电路配置的实例,但是n沟道驱动的电路配置也是可能的。图11示出了n沟道驱动的ota 111的电路配置的实例。对应于图10的元件由在端部具有a的相同的参考标号表示。在图11的描述中,晶体管的极性等可在图10的描述中适当地读取,并且因此将省略详细描述。

[0102]

[第二具体示例]

[0103]

图12示出了根据第二具体实例的驱动电路102的配置实例。在图7和图9中,驱动电路102中的检测电路是ota 111,但是在图12中,检测电路包括比较器141、相位比较器142和充电泵143。在图12中,未示出像素负载电容器。在图12的配置中,在不增加诸如图9的偏移消除操作的功能的情况下,通过输出电流源ia可以产生具有高精度的电流。

[0104]

比较器141包括两个输入端子,一个端子连接到基准电压vref,基准电压vref是视频信号中期望设定的电压(期望电压),另一个端子连接到输出端子vout。比较器141检测输出电压vout与基准电压verf匹配的定时。当开关pwm根据pwm信号被导通并且输出端子vout的电压被输入至比较器141时,比较器141检测输入电压与基准电压verf匹配的定时。输出指示检测到的定时的数字信号cmpout。使能信号可以根据开关pwm被接通的定时被输入到比较器141,并且比较器141可以根据使能信号的输入开始操作。

[0105]

相位比较器142包括两个端子,并且其中一个端子被输入指示由比较器141检测的定时的数字信号cmpout。指示与基准电压verf相对应的定时的数字信号refpwm被输入到另一端子。相位比较器142比较两个数字信号,以检测比较器141检测的定时与对应于基准电压verf的定时之间的定时差。

[0106]

充电泵143包括串联连接的上侧开关146和下侧开关147。在上侧开关146和下侧开关147之间的连接节点被连接到保持电容器ch和输出电流源ia(晶体管)的栅极。当上侧开关146接通时,电流被供应至保持电容器ch。当下侧开关147接通时,电流从保持电容器ch释放。

[0107]

相位比较器142根据检测到的定时差的信号选择性地接通充电泵143的上侧开关146和下侧开关147。具体地,根据定时差的信号的符号选择上侧开关146和下侧开关147中的一个,并且根据定时差的时间长度接通所选择的开关。结果,保持电容器ch被充电或放

电,并且输出电流源ia的栅极电压被调整。

[0108]

[第三具体示例]

[0109]

图13示出了根据第三具体实例的驱动电路102的配置实例。在图7和图9中,驱动电路102中的检测电路为ota 111,保持单元为保持电容。在图12中,检测电路是差分放大器电路151和顺序比较电路152,并且保持单元是数模转换器(dac)153。作为偏置电流源的nmos晶体管154连接到输出电流源ia。nmos晶体管154的栅极连接至偏置电压vb。在图12中,未示出像素负载电容器。在图13的配置中,在不增加诸如图9的偏移消除操作的功能的情况下,通过输出电流源ia可以产生具有高精度的电流。

[0110]

差分放大器电路151的 输入端子连接至基准电压vref,基准电压vref是期望在视频信号中设定的电压(期望电压)。差分放大器电路151的-输入端子连接至输出端子vout。差分放大器电路151将基准电压verf与输出端子vout的电压进行比较,以将二者之间的差分电压依次输出至相比较电路152。

[0111]

顺序比较电路152基于从差分放大器电路151输入的差分电压执行顺序比较操作,并且以高精度计算差分电压。即,输出接近期望的输出电流流过的栅极电压的设定值的比较结果。顺序比较电路152根据计算出的差分电压输出数字信号。该数字信号指示期望输出电流流过的栅极电压的设定值或接近于该设定值的值。顺序比较电路152将数字信号输出到dac 153。

[0112]

dac 153将数字信号转换成dc模拟电压。即,dac 153保持从顺序比较电路152输出的数字信号以根据由数字信号表示的设定值生成电压。dac 153将生成的电压提供至输出电流源ia的栅极。

[0113]

在图13的电路的情况下,在调整输出电流源ia的栅极电压之后,不必每帧调整栅极电压,从而可进一步减少功耗。另外,由于驱动电路的许多部分可以通过逻辑电路来实现,所以在进程生成进展的情况下,尺寸减小效果高。

[0114]

ram、触发器电路、锁存电路、fifo等可用作保持作为顺序比较电路152的输出的数字信号的电路。

[0115]

(第二实施例)

[0116]

第二实施方式的驱动电路的配置与第一实施方式的相同,但是对像素的操作部分不同。在第二实施方式中,消除驱动晶体管的阈值电压drtr的像素之间的偏差(称为阈值校正)。因此,首先,将偏移电压的设定设定到视频信号线,并且通过采样晶体管wstr将设定的偏移电压写入到像素103。基于偏移电压来执行阈值校正。在完成偏移电压的写入之后,如在第一实施方式中,在视频信号线中设定用于灰度的电压,并且在像素中写入视频信号的信号电压。第一实施方式的驱动电路还可以用于如上所述设置用于阈值校正的偏移电压的情况。由此,能够在抑制像素之间的偏差的同时,能够高精度地进行阈值校正。在下文中,将详细描述第二实施方式。

[0117]

图14是示出了根据第二实施方式的有源矩阵型显示装置中的像素及其外围电路的框图。虽然在图14中示出了单个像素103,但是实际上像素以矩阵形式布置在像素阵列中。外围电路包括水平驱动电路10、驱动扫描电路20和写入扫描电路60。驱动扫描电路20和写入扫描电路60对应于垂直驱动电路。像素103的配置是示例,可以提供各种其他配置。水平驱动电路10设置有用于每列像素的驱动电路102。

[0118]

像素103包括诸如有机el元件的发光元件30。发光元件30的阴极连接到为所有像素公共布线的公共电源线34。此外,像素103包括驱动晶体管drtr、采样晶体管wstr、发光控制晶体管24、保持电容器25以及辅助电容器26。在该实例中,pmos晶体管用于驱动晶体管drtr、采样晶体管wstr以及发光控制晶体管24,但是可以使用nmos晶体管,或者可以混合两种导电类型。

[0119]

采样晶体管wstr采样通过视频信号线112从驱动电路102供应的信号电压vsig,并且将信号电压vsig写入保持电容器25中。发光控制晶体管24连接在电源电压vcc的电源节点与驱动晶体管drtr的源极之间,并且在由来自驱动扫描电路20的发光控制信号ds驱动下控制发光元件30的发光。

[0120]

保持电容器25连接在驱动晶体管drtr的栅极与源极之间。保持电容器25保持通过采样晶体管wstr进行采样而写入的信号电压vsig。驱动晶体管drtr通过使根据保持电容器25的保持电压的驱动电流流过发光元件30来驱动发光元件30。辅助电容器26连接在驱动晶体管drtr的源极与固定电位的节点(例如,电源电压vcc的电源节点)之间。辅助电容器26在写入信号电压vsig时抑制驱动晶体管drtr的源极电位的波动,并且将驱动晶体管drtr的栅极-源极电压vgs设置为驱动晶体管drtr的阈值电压vth。在下文中,将描述本电路的操作。

[0121]

在偏移电压vofs从驱动电路102被设置为视频信号线112的状态下,使扫描线40的电位ws从高电位转变至低电位,并且接通采样晶体管wstr。驱动晶体管drtr的栅极电位vg是偏移电压vofs。此时,驱动线50的电位ds处于低电位状态,并且发光控制晶体管24导通。因此,驱动晶体管drtr的源极电位vs是电源电压vcc。此时,驱动晶体管drtr的栅极-源极电压vgs是vgs=vofs-vcc。

[0122]

这里,为了执行稍后描述的阈值校正操作(阈值校正处理),必须使得驱动晶体管drtr的栅极-源极电压vgs大于驱动晶体管drtr的阈值电压vth。因此,每个电压值被设置为使得|vgs|=|vofs-vcc|》|vth|。

[0123]

如上所述,将驱动晶体管drtr的栅极电位vg设置为偏移电压vofs并且将驱动晶体管drtr的源极电位vs设置为电源电压vcc的初始化操作是执行下一阈值校正操作之前的准备操作(阈值校正准备)。因此,偏移电压vofs和电源电压vcc分别是驱动晶体管drtr的栅极电位vg和源极电位vs的初始化电压。

[0124]

驱动线50的电位ds从低电位切换到高电位,并且发光控制晶体管24截止。驱动晶体管drtr的源极电位vs是浮动的,并且在驱动晶体管drtr的栅极电位vg保持在偏移电压vofs的状态下开始阈值校正操作。即,驱动晶体管drtr的源极电位vs开始朝向通过从驱动晶体管drtr的栅极电位vg中减去阈值电压vth而获得的电位(vg-vth)下降(减小)。

[0125]

如上所述,以驱动晶体管drtr的栅极电位vg的偏移电压vofs(初始化电压)为基准使驱动晶体管drtr的源极电位vs朝着通过从电压vofs减去阈值电压vth而获得的电位(vg-vth)改变的操作是阈值校正操作。随着阈值校正操作进行,驱动晶体管drtr的栅极-源极电压vgs收敛至驱动晶体管drtr的阈值电压vth。对应于阈值电压vth的电压保持在保持电容器25中。

[0126]

当扫描线40的电位ws从低电位切换到高电位并且采样晶体管wstr截止时,阈值校正周期结束。此后,从驱动电路102对视频信号线112设定视频信号的信号电压vsig。结果,视频信号线112的电位从偏移电压vofs切换到信号电压vsig。

[0127]

扫描线40的电位ws从高电位切换至低电位,采样晶体管wstr截止,并且对信号电压vsig采样并写入像素103中。通过由采样晶体管wstr写入信号电压vsig的操作,驱动晶体管drtr的栅极电位vg变为信号电压vsig。

[0128]

当写入视频信号的信号电压vsig时,连接在驱动晶体管drtr的源极与电源电压vcc的电源节点之间的辅助电容器26抑制驱动晶体管drtr的源极电位vs的波动。然后,当驱动晶体管drtr由视频信号的信号电压vsig驱动时,驱动晶体管drtr的阈值电压vth由与保持电容器25中保持的阈值电压vth对应的电压抵消。

[0129]

扫描线40的电位ws从低电位切换到高电位,并且采样晶体管wstr截止,从而终止信号写入。驱动线50的电位ds从高电位切换到低电位,并且发光控制晶体管24导通。因此,电流通过发光控制晶体管24从电源电压vcc的电源节点供应至驱动晶体管drtr。

[0130]

此时,因为保持电容器25连接在驱动晶体管drtr的栅极与源极之间,所以栅极电位vg也随驱动晶体管drtr的源极电位vs的波动一起波动。即,在保持被保持在保持电容器25中的栅极-源极电压vgs的同时,驱动晶体管drtr的源极电位vs和栅极电位vg增加。然后,驱动晶体管drtr的源极电位vs根据晶体管的饱和电流升高至发光元件30的发光电压。当驱动晶体管drtr的漏极-源极电流开始流过发光元件30时,发光元件30的阳极电位增加。最终,当发光元件30的阳极电位超过发光元件30的阈值电压时,驱动电流开始流过发光元件30,使得发光元件30开始发光。

[0131]

例如,在一个水平周期(1h)内执行上述信号电压vsig的阈值校正准备、阈值校正和写入(信号写入)的每个操作。

[0132]

在下文中,将参考图15描述通过在写入信号电压之前写入偏移电压来执行阈值校正的电路中的根据第二实施方式的驱动电路102的操作,如图14所示。

[0133]

图15是根据第二实施方式的驱动电路102的时序图。这里,假设驱动电路102包括具有图9的偏移消除功能的ota 111。横轴表示时间。为了便于说明,将时间轴划分为多个区间s1至s7。

[0134]

首先,在区间s1中,pchg开关接通,视频信号线112(像素负载电容器)被预充电到预定电压vpchg(输出端子vout具有预充电电压)。

[0135]

在区间s2中,断开开关pchg,并且根据vosf的预定时间接通开关pwm。此时,偏移电压vofs被提供作为ota 111的基准电压ref。当预充电的视频信号线112(像素负载电容器)以恒定斜率放电并且经过预定时间时,开关pwm断开。此时,输出端子vout的电压为vosf或接近vosf的电压。当pwm开关断开时,ota 111的使能信号otaen接通。

[0136]

当ota 111接通时,在区间s3中,开关ini接通,并且执行偏移消除。

[0137]

接下来,在区间s4中,cal开关被接通,并且从ota 111输出电流。此外,像素中的采样晶体管导通(wsen1信号导通),并且偏移电压vosf被供应至像素。在像素中,基于偏移电压vosf执行上述阈值校正。

[0138]

在区间s5中,停止ota 111的操作。保持电容器ch的电压施加到输出电流源ia的栅极,并且栅极电压(cp输出)相应地波动。在ota 111断开之后,开关pchg接通,视频信号线112(像素负载电容器)被再次预充电。输出端子vout被设定为预充电电压。

[0139]

在区间s6中,根据从电平移位器提供的pwm信号的一段时间(根据所需分级的时间),接通开关pchg。当预充电的视频信号线112(像素负载电容器)以恒定斜率放电并且经

过根据pwm信号的时间时,开关pwm断开。此时,输出端子vout的电压是用于写入的信号电压vsig。

[0140]

在区间s7中,像素中的采样晶体管导通(wsen2信号导通),并且经由采样晶体管将信号电压vsig写入像素。

[0141]

此后,操作s1至s7可以重复一次或多次。可替代地,也可以不重复。s1至s7的操作可以在消隐周期期间被执行一次或多次。

[0142]

(第三实施方式)

[0143]

在第三实施方式中,将描述像素是红色(r)、蓝色(g)和绿色(b)子像素的情况。调整输出电流源ia的栅极电压,使得通过使用与使用第一实施例的驱动电路的像素负载电容器不同的电容器(虚拟电容器)使虚拟电容器放电一定时间段来获得具有恒定斜率的电流(基准电流)。然后,通过电流采样操作将基准电流复制到红色(r)、蓝色(g)和绿色(b)每个子像素中的的子驱动电路。在子驱动电路中,使用从驱动电路复制的电流,在根据pwm信号的时间段期间对每个子驱动电路预充电的视频信号线进行充电或放电。由此,对rgb视频信号线中的每一条设定与灰度对应的信号电压。

[0144]

图16是根据第三实施方式的驱动电路的框图。图16的驱动电路包括电流生成电路160和分别对应于红色(r)、蓝色(b)和绿色(g)的三个子驱动电路102r、102b和102g。三个子驱动电路102r、102b、102g的输出端子vout分别通过rbg用的视频信号线112r、112b、112g与子像素103r、103b、103g连接。电流生成电路160经由输出端子out连接到子驱动电路102r、102b和102g。电流生成电路160具有verf端子,预定基准电压ver输入至该verf端子。

[0145]

图17示出了电流生成电路160和子驱动电路102r的配置实例。子驱动电路102b、102g的结构与子驱动电路102r相同,省略图示。

[0146]

电流生成电路160包括输入端子vccp、虚拟电容器cdum、开关cs(第四开关)、开关calprchg(第五开关)、开关wrt_r、wrt_b和wrt_g(第七开关)、以及输出端子outr、outb和ortg。此外,电流生成电路160包括输出电流源ia、保持电容器ch、ota 111、两个开关cal和开关ini。应注意,尽管开关cal连接至ota 111的输入端子,但是可以省略开关cal并且仅可以设置ota 111的输出侧上的开关cal。在上述图9的配置中,开关cal可附加地连接至ota 111的输入端子以提供两个cal开关。因为输出电流源ia、保持电容器ch、ota 111、两个开关cal以及开关ini的操作与第一实施方式的图9中的操作相似,所以将省去其详细描述。

[0147]

子驱动电路102r包括开关wrt_r1(第六开关)、开关wrt_r2、pmos晶体管161r(第三晶体管)、电容器162r、开关pwm、开关prcg|sig_vofs、预充电输入端子165和输出端子vout。开关prcg|sig_vofs对应于设定电路167r,该设定电路167r被配置为基于施加到预充电输入端子165的电压对连接到输出端子vout的视频信号线112r进行预充电。晶体管161r、电容器162r和开关pwm对应于调整电路168r,该调整电路168r被配置为通过在根据pwm信号的时间段期间对预先充电的视频信号线112r充电或放电来调整视频信号线112r的电压。

[0148]

在电流生成电路160中,例如,vg0(对应于最小灰度的电压)被施加到输入端子vccp,并且vg255(对应于最大灰度的电压)被施加到verf端子作为基准电压verf。ota 111和保持电容器ch用于产生具有在一定时间内从对应于最小灰度的电压达到对应于最大灰度的电压的斜率的电流作为基准电流(对应于具有最大宽度的pwm信号)。该基准电流通过电流采样被复制到子驱动电路102r、102b和102g。子驱动电路102r、102b、102g在根据pwm信

号的时间段期间使用复制的参考电流对预充电的视频信号线112r、112b、112g进行充电或放电。结果,对rgb视频信号线中的每一条设定与灰度对应的电压。如在第二实施方式中,在设置视频信号之前,可以在视频信号线中设置偏移电压,并且可以在每个子像素中执行基于偏移电压的阈值校正。在操作的以下描述中,将描述执行阈值校正的情况。

[0149]

图18是图17的驱动电路的时序图。横轴表示时间。在该实例中,假定通过子驱动电路102r、102b、和102g在视频信号线中设置与最小灰度对应的电压(vg0)的情况,即,子驱动电路的输出端子vout的电压被设置为vg0的情况。

[0150]

在区间s1至s4中,并行执行电流生成电路160中用作复制源的参考电流的生成(虚拟电容器cdum的设置)和每个子像素的偏移电压的设置和阈值校正。具体地,首先,在区间s1中,接通开关cs和开关calprchg以将cdum预充电至vg0。另外,接通在ota 111的输入侧上的开关ini以取消偏移。

[0151]

在区段s2中,开关calprchg断开,并且虚拟电容器cdum放电特定时间段。虚拟电容器cdum的电压振幅是通过放电从vg0中减去vg255而获得的值。在某个时间段内从与最小灰度对应的电压达到与最大灰度对应的电压或与其接近的电压的具有恒定斜率的电流(参考电流)(对应于具有最大宽度的pwm信号)流动。

[0152]

在区间s3中,断开开关cs,接通两个cal开关,并且操作ota 111。注意,虽然未示出,但是开启的使能信号otaen也被输入到ota 111。虚拟电容器cdum的输出电压与vref电压(vg255)相比较,保持电容器ch被充电或放电,并且输出电流源ia的栅极电压(附图中的cp输出)被调整。结果,调整像素之间的电流源ia的偏差。

[0153]

在区间s4中,两个cal开关断开,并且ota 111的操作终止。电流生成电路160中的开关wrt_r和子驱动电路102r中的两个开关wrt_r1和wrt_r2被接通,并且由电流生成电路160生成的电流(参考电流)被复制到子驱动电路102r。即,通过接通电流生成电路160中的开关wrt_r和子驱动电路102r中的两个开关wrt_r1和wrt_r2,pmos晶体管161r的栅极和漏极电连接到电流生成电路160的输出端子outr。pmos晶体管161r的源极连接到电压vg0,并且pmos晶体管161是二极管连接的。该电流作为流过pmos晶体管161的源极和漏极并且流过输出电流源ia的电流产生,作为具有与参考电流相同的斜率的电流。在该状态下,电流生成电路160中的开关wrt_r和子驱动电路102r中的两个开关wrt_r1和wrt_r2被断开。栅极-源极电容器162r保持用于产生斜率与基准电流相同的电流所需的栅极-源极电压(图中的输出级vgsr)。

[0154]

类似地,电流生成电路160中的开关wrt_b和子驱动电路102b中的两个开关wrt_b1和wrt_b2被接通,并且由电流生成电路160生成的基准电流被复制到子驱动电路102b。另外,电流生成电路160中的开关wrt_g和子驱动电路102g中的两个开关wrt_g1和wrt_g2接通,并且由电流生成电路160生成的基准电流被复制到子驱动电路102g。

[0155]

与上述区间s1至s4中的操作并行,在每个子驱动电路中,为每个视频信号线设置偏移电压,并且在每个子像素中执行基于所设置的偏移电压的阈值校正。具体地,在区间s2至区间s4的中间,在预充电输入端子165连接至偏移电压vofs的状态下,接通每个子驱动电路中的开关sig_vofs。由此,视频信号线112r、112b、112g被预充电至偏移电压vofs。在视频信号线112r、112b、和112g被预充电的状态下,包括在每个子像素中的采样晶体管导通(wsen1信号导通),并且偏移电压vofs被写入每个子像素。在每个子像素中,使用偏移电压

vofs执行阈值校正操作。

[0156]

当完成每个子驱动电路的偏移电压vofs的设定和写入并且完成基准电流的复制时,每个子驱动电路中的开关prcg被接通一定时间段,并且视频信号线112r、112b、和112g被预充电到vg255。即,视频信号线112r、112b、112g的电压从vofs变为vg255。应注意,开关prcg是与开关sig_vofs相同的开关,但是由于切换的目的不同,为了方便起见,相同的开关由不同的参考符号表示。

[0157]

在区间s5中,当各子驱动电路中的开关prcg断开时,各子驱动电路中的开关pwm接通根据pwm信号的一时间长度。图中仅示出了三个子像素中的一个(这里为子像素103r)的pwm信号。在该实例中,示出了与最小灰度对应的最大时间长度的pwm信号。当开关pwm接通时,根据保持在电容器162r中的栅极-源极电压的电流,即具有与基准电流相同的斜率的电流,经由开关pwm从晶体管161r提供给视频信号线(电流采样)。结果,预充电到vg255的视频信号线被充电或放电(在图实例中被充电)。通过对视频信号线充电,视频信号线的电压(像素负载电容器的电压)被设定为或接近对应于最小灰度的电压vg0。

[0158]

当在区间s6中断开开关pwm时,每个子像素的采样晶体管导通(wsen2信号导通),并且视频信号线的电压vsig被写入每个子像素。在每个子像素中,根据电压vsig驱动发光元件,并且以与信号电压vsig对应的灰度发光。在写入信号电压之前(在采样晶体管导通之前),可以重复区间s1至s5一次或多次。结果,电流生成电路160的输出电流源ia的栅极电压被高精度地调整,并且电压vsig可被高精度地设定为目标电压(附图的实例中的vg0)。在图中,示意性地示出了通过将操作次数从n次增加到(n 1)次,可以使电压接近电压vg0。

[0159]

根据图16和图17的配置,不必为每个子像素提供如在第一实施方式中的驱动电路,并且多个子驱动电路可以共享电流生成电路,使得可减小电路面积。此外,由于仅在调整输出电流源ia时仅需要由一个电流生成电路供应dc偏置电力(verf电压),所以可降低功耗。

[0160]

应注意,上述实施方式示出了用于体现本公开的实例,并且本公开可以以各种其他形式实现。例如,在不背离本公开的要旨的情况下,可进行各种修改、替换、省略或其组合。进行这样的修改、替换、省略等的实施方式也包括在本公开的范围内,并且包括在权利要求及其等同物中描述的本发明中。

[0161]

此外,在本说明书中描述的本公开的效果仅仅是实例,并且可以提供其他效果。

[0162]

应注意,本公开还可具有以下配置。

[0163]

[项目1]

[0164]

一种驱动电路,包括

[0165]

设定电路,被配置为将视频信号线预充电至第一电压,视频信号线连接至被配置为对视频信号线的电压进行采样的第一晶体管;以及

[0166]

调整电路,被配置为通过在与视频信号线中设置的第二电压相对应的时间段期间,对预充电至第一电压的视频信号线进行充电或放电来调整视频信号线的电压。

[0167]

[项目2]

[0168]

根据项1所述的驱动电路,其中,

[0169]

设定电路包括:

[0170]

第一开关,将视频信号线连接至第一电压,以及

[0171]

调整电路包括:

[0172]

电流源,包括第二晶体管和连接视频信号线和电流源的第二开关。

[0173]

[项目3]

[0174]

根据项目2所述的驱动电路,进一步包括:

[0175]

检测电路,包括连接至第二电压的第一端子和连接至视频信号线的第二端子,并且被配置为检测第二电压与视频信号线的电压之间的差,以及

[0176]

保持电路,被配置为保持根据差的保持电压并且将电压供应至电流源的控制端子。

[0177]

[项目4]

[0178]

根据项目3所述的驱动电路,其中,

[0179]

检测电路包括放大器,放大器被配置为根据第二电压与视频信号线的电压之间的差生成电流,以及

[0180]

保持电路包括被配置为累计根据电流的电荷的电容器。

[0181]

[项目5]

[0182]

根据项目4所述的驱动电路,进一步包括:

[0183]

第三开关,连接第一端子与第二端子,其中

[0184]

调整电路在放大器的操作之前接通第三开关一段时间。

[0185]

[项目6]

[0186]

根据项目3所述的驱动电路,其中,

[0187]

检测电路包括:

[0188]

比较器,被配置为检测视频信号线的电压变为第二电压的定时;相位比较器,被配置为检测定时与根据第二电压的定时之间的差,以及

[0189]

充电泵,被配置为根据差生成电流,以及

[0190]

保持电路包括被配置为累积根据电流的电荷的电容器。

[0191]

[项目7]

[0192]

根据项目3所述的驱动电路,其中,

[0193]

检测电路包括转换电路,转换电路被配置为将第二电压与视频信号线的电压之间的差转换为数字信号,以及

[0194]

保持电路包括数模转换器,数模转换器被配置为将根据数字信号的电压供应至控制端子。

[0195]

[项目8]

[0196]

根据项1至7中任一项所述的驱动电路,其中,

[0197]

第一电压包括与最大灰度或最小灰度对应的电压。

[0198]

[项目9]

[0199]

根据项1至8中任一项所述的驱动电路,其中,

[0200]

第二电压包括与使包括第一晶体管的像素电路显示的灰度对应的电压。

[0201]

[项目10]

[0202]

根据项1至9中任一项所述的驱动电路,其中,

[0203]

第二电压包括用于校正用于驱动包括第一晶体管的像素电路中的发光元件的第

二晶体管的阈值电压的偏移电压。

[0204]

[项目11]

[0205]

根据项10所述的驱动电路,还包括:

[0206]

扫描电路,被配置为导通第一晶体管并且将设定为偏移电压的视频信号线的电压供应至像素电路内的节点,其中

[0207]

在向像素电路供应偏移电压之后,设定电路将视频信号线预充电至第一电压,

[0208]

调整电路通过在根据与灰度对应的电压的时间段期间对预充电至第一电压的视频信号线进行充电或放电,来将视频信号线调整到与灰度对应的电压,以及

[0209]

扫描电路导通第一晶体管以将视频信号线的电压供应至像素电路内的节点。

[0210]

[项目12]

[0211]

根据项目1至11中任一项所述的驱动电路,进一步包括:

[0212]

多个子驱动电路,每个子驱动电路均包括设定电路和调整电路,以及

[0213]

电流生成电路,被配置为生成基准电流,其中

[0214]

多个子驱动电路连接至多个视频信号线,

[0215]

多个子驱动电路中的每个的调整电路包括被配置为对基准电流进行采样的第三晶体管,以及

[0216]

多个子驱动电路中的每个的调整电路利用由第三晶体管采样的电流对由设定电路预充电的视频信号线进行充电或放电。

[0217]

[项目13]

[0218]

根据项目12所述的驱动电路,其中,

[0219]

电流生成电路包括:连接至第三电压的第一电容器,

[0220]

电流源,包括第四晶体管,

[0221]

第四开关,连接第一电容器和电流源,

[0222]

第五开关,连接第一电容器的两端,

[0223]

检测电路,包括连接至第四电压的第一端子和连接至第四开关的第二端子,检测电路被配置为检测第一端子的电压与第二端子的电压之间的差,

[0224]

保持电路,被配置为保持根据差的电压并且将电压供应至电流源的控制端子,

[0225]

第六开关,二极管连接多个子驱动电路中的每个的第三晶体管二极管,以及

[0226]

第七开关,连接多个子驱动电路中的每个子驱动电路的二极管连接的第三晶体管和电流源。

[0227]

[项目14]

[0228]

根据项目13所述的驱动电路,其中,

[0229]

第四开关和第五开关接通,以对第一电容器进行预充电,

[0230]

第五开关断开,使第一电容器放电以生成基准电流,

[0231]

第四开关断开以操作检测电路一段时间,并且

[0232]

第六开关和第七开关接通,以对子驱动电路中的基准电流进行采样。

[0233]

[项目15]

[0234]

根据项目1至14中任一项所述的驱动电路,其中

[0235]

在第一晶体管截止期间,设定电路将视频信号线预充电到第一电压,调整电路将

视频信号线调整到第二电压。

[0236]

[项目16]

[0237]

根据项15所述的驱动电路,其中,

[0238]

第一晶体管截止的周期包括消隐周期,消隐周期包括包含第一晶体管的像素电路不发光的周期。

[0239]

[项目17]

[0240]

一种显示装置,包括:

[0241]

视频信号线,被配置为提供视频信号,

[0242]

像素电路,包括连接至视频信号线的第一晶体管,

[0243]

第一晶体管被配置为对视频信号线的电压进行采样,

[0244]

驱动电路,包括:设定电路,被配置为将视频信号线预充电至第一电压;以及调整电路,被配置为通过在与视频信号线中设定的第二电压的时间段期间,对预充电至第一电压的视频信号线进行充电或放电,来调整视频信号线的电压,以及

[0245]

扫描电路,被配置为控制第一晶体管的导通和截止。

[0246]

[项目18]

[0247]

一种驱动方法,包括:

[0248]

将连接至被配置为对视频信号线的电压进行采样的第一晶体管的视频信号线预充电至第一电压,以及

[0249]

通过在与视频信号线中设置的第二电压相对应的时间段期间,对预充电至第一电压的视频信号线进行充电或放电,来调整视频信号线的电压。

[0250]

符号说明

[0251]

10 水平驱动电路

[0252]

20 驱动扫描电路

[0253]

24 发光控制晶体管

[0254]

26 辅助电容器

[0255]

25 保持电容器

[0256]

30 发光元件

[0257]

34 共用电源线

[0258]

60 写扫描电路

[0259]

101 电流驱动电路

[0260]

102 驱动电路

[0261]

104 设定电路

[0262]

103 像素电路(像素)

[0263]

105 调整电路

[0264]

103r,103b,103g 子像素

[0265]

111 电压控制电流源电路(ota)

[0266]

112 视频信号线

[0267]

121,122,124,125 晶体管

[0268]

123 电流源

[0269]

126 电容器

[0270]

132 开关

[0271]

142 相位比较器

[0272]

143 充电泵

[0273]

146 上侧开关

[0274]

147 下侧开关

[0275]

151 差分放大器电路

[0276]

152 顺序比较电路

[0277]

153 dac

[0278]

154 晶体管

[0279]

160 电流生成电路

[0280]

102r,102b,102g 子驱动电路

[0281]

103r,103b,103g 子像素

[0282]

161r 晶体管

[0283]

162r 电容器

[0284]

1100 移位寄存器

[0285]

1101 第一锁存电路

[0286]

1102 第二锁存电路

[0287]

1104 同步计数器

[0288]

1103 数字比较器

[0289]

1105 pwm生成电路

[0290]

1106 电平移位器

[0291]

vout 输出端子,输出电压

[0292]

vref 参考端子,参考电压

[0293]

ia 输出电流源

[0294]

wstr 采样晶体管

[0295]

drtr 驱动晶体管

[0296]

cs 电容器

[0297]

ch 保持电容器

[0298]

虚拟电容器

[0299]

pwm,pchg,cal,ini,cs,calprchg,wrt_r,wrt_b,wrt_g,wrt_r1,wrt_b1,wrt_g1,wrt_r2,wrt_b2,wrt_g2,prog,sig_vofs 开关。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。