1.本发明涉及现场可编程门阵列fpga器件。特别地,本发明涉及用于执行自动驾驶计算的人工智能ai加速器fpga器件和其他硬件。

背景技术:

2.现场可编程门阵列fpga长期以来一直用于构建专用集成电路asic和片上系统soc器件的系统原型。fpga是包含大量可配置逻辑的通用部件,并且是用于构建和测试新集成电路ic的自然选择。随着ic设计在尺寸和复杂性方面的增长,fpga也在不断发展以提供不断增加的对应数量的逻辑门。fpga原型使得能够更灵活地开发和测试系统,并且可以允许软件开发人员更早地达成功能更先进的硬件平台。fpga可以用于通常需要执行非常大量计算的人工智能ai加速器。对于自动驾驶应用程序,尤其是像在电动车辆ev中那样依靠储存的电能进行推进时,这可能成为问题,因为fpga通常会比asic消耗更多的功率。ai加速器fpga功耗的典型数值可能在1kw至5kw范围内。这样,自动ev的续航里程可能大大减少,例如,减少5%至10%。较高的功耗可能归因于fpga中需要更多的逻辑门和更多的逻辑门间布线。另外,更高的功耗还可能导致更大的热损失。另外,随着通过fpga中常用的常规si晶体管的电流泄漏增加,温度升高还可能导致热失控效应。因此,需要在技术领域内进行改进。

技术实现要素:

3.发明人的目的是解决或至少减轻现有技术的上述问题中的一些。

4.根据第一方面,提供了一种现场可编程门阵列fpga器件。fpga器件可以是人工智能ai加速器fpga器件。fpga器件可以被配置用于或适合于执行自动驾驶计算。fpga器件包括可配置逻辑块clb。clb包括一个逻辑反相器。该逻辑反相器包括至少一个高电子迁移率晶体管hemt。每个hemt包括alyga

y-1

n层结构(其中,0《y≤1)以及gan层结构。

5.术语“现场可编程门阵列器件”(及其对应的首字母缩写词)应当理解为是指基于或在很大程度上包括fpga的器件。其不应当将被解释为将本披露内容仅仅限制于fpga本身。

6.术语“逻辑反相器”应当理解为可以将高输入信号转换为相对于输入信号而言较低的输出信号并且反之亦然的器件。

7.术语“高电子迁移率晶体管”(及其对应的首字母缩写词)应当理解为这样的半导体器件,其包括具有不同能带隙的至少两个层结构以形成公共异质结界面,从而实现基本上二维的电子传输。该界面可以理解为使得能够形成所谓的二维电子气2deg。hemt可以可替代地称为异质结场效应晶体管hfet。

8.自动驾驶应用程序可能需要执行大量相关计算和处理数据。这可能与机器学习或基于ai的自动驾驶特别相关。发明人已经意识到氮化物hemt可以有益于在自动驾驶fpga器件中使用。这是由于它们的整体效率提高了。与传统的金属氧化物半导体场效应晶体管mosfet相比,氮化物hemt(例如,包括gan和algan层结构界面的hemt)通常提供更高的电压/

电流操作、更高的开关频率以及更少的能量损失。氮化物hemt的能量效率方面将特别为ev上的车载自动驾驶fpga器件提供优势,使得储存在例如电池中的更多的能量可以用于推进车辆,而不是执行自动驾驶计算。此外,减少的能量损失可以使得产生更少的废热。这样,可以在通过例如冷却装置解决废热积聚方面投入更少的努力。此外,更少的废热对于有关ev电池的安全方面而言也会是优选的。

9.逻辑反相器可以是共源共栅反相器。逻辑反相器可以包括至少两个hemt。每个hemt可以包括alyga

y-1

n层结构以及gan层结构。

10.术语“共源共栅”可以指具有公共源极/发射极级和公共栅极/基极的两级电路或放大器。这两级通常各自包括一个晶体管。

11.使用共源共栅反相器设置可以通过减少电流的反向传输来提供反相器的输入信号和输出信号的更强隔离,因为从输出节点到输入节点没有直接耦合。此外,可以减轻密勒效应(miller effect)的负面后果(比如,输入电容的增加),从而增加反相器带宽。

12.逻辑反相器可以包括至少一个上拉晶体管。

13.引入的例如作为上拉网络的一部分的上拉晶体管可以通过提供产生高输出信号电平的可靠方式来改善反相器操作。

14.clb可以是k输入clb。

15.术语“k输入”应当理解为是指包括任何整数k个输入的clb。

16.clb可以被配置用于学习函数映射。

17.fpga器件可以进一步包括并行移位寄存器。

18.fpga器件可以进一步包括存储器块。这样,fpga器件可以存储指令和数据。

19.fpga器件可以进一步包括可编程输入/输出i/o块。

20.通过可编程io块,fpga器件可以被其他设备(例如,中央处理单元cpu)访问,以便对fpga器件进行编程。

21.clb、并行移位寄存器、存储器块和可编程i/o块可以全部形成在同一si衬底上。

22.通过在同一衬底上形成所有部件,可以使fpga器件小型化,并且可以减少材料的浪费。由于本领域技术人员很容易获得si ic的制造方法,因此可以降低生产复杂性。si与其他替代物(比如块状氮化物材料)相比也相对丰富。此外,较少的单独分立部件会需要在其单独形成后进行集成。

23.fpga器件可以进一步包括互连,该互连被配置为电连接clb、并行移位寄存器、存储器块和可编程i/o块中的至少两者。

24.术语“互连”可以理解为能够传输电流并保持电压电势的电互连/导电互连。

25.每个hemt的alyga

y-1

n层结构可以一体地形成。每个hemt的gan层结构可以一体地形成。

26.这样,相同的层结构可以用于形成多个hemt。

27.每个hemt可以进一步包括si衬底。每个hemt可以进一步包括布置在si衬底上的晶体过渡层结构。

28.通过使hemt以si衬底为基底,可以使生产和与同一衬底上的其他电路和器件的集成变得不那么复杂,并且材料效率更高,这与使用si作为衬底的已提供的优势一致。晶体过渡层在调整材料结构或晶格以满足创造高质量氮化物材料和材料界面的要求方面可以是

有利的。

29.alyga

y-1

n层结构可以布置在晶体过渡层结构上。gan层结构可以布置在alyga

y-1

n层结构上。

30.gan层结构可以布置在晶体过渡层结构上。alyga

y-1

n层结构可以布置在gan层结构上。

31.晶体过渡层可以包括多个垂直布置在si衬底上的竖直纳米线结构。晶体过渡层可以进一步包括al

x

ga

x-1

n层结构,其中,0≤x《1。al

x

ga

x-1

n层结构可以布置为竖直且侧向包围竖直纳米线结构。

32.这种晶体过渡层可以用于为高质量氮化物层结构的外延形成/生长提供良好的材料和晶格条件。晶体过渡层也可以制作得更薄,因此比常规的基于缓冲层的方法的材料强度更低,从而实现更高质量的氮化物层结构。

33.根据第二方面,提供了一种ai处理系统。该系统包括根据第一方面的fpga器件。该系统进一步包括提供模拟传感器输出信号的传感器。该系统进一步包括用于处理所述传感器输出信号的模数转换器adc。该系统进一步包括用于调节所述传感器的数模转换器dac。fpga器件的存储器块保持用于操作ai处理系统的所存储的指令。

34.除了第一方面提供的优点之外,这种系统可以有利地用于执行自动驾驶计算。该系统的特征可以是adc和/或dac包括氮化物hemt,因此可以实现器件的进一步集成。该系统本质上可以集成为soc。

35.根据以下给出的详细描述,本发明的进一步的适用范围将变得清楚。然而,应当理解,具体实施方式和具体示例虽然指示了本发明的优选实施例,但仅以说明性的方式给出,因为根据本具体实施方式,本发明的范围内的各种变化和修改对于本领域技术人员而言将变得清楚。

36.因此,应当理解,本发明不限于所描述的器件的特定组成部分或者所描述的方法的动作,因为这种器件和方法可以改变。还应当理解,本文所使用的术语仅是为了描述特定实施例的目的,并不旨在是限制性的。

37.必须注意,除非上下文另有明确规定,否则如在本说明书和所附权利要求中所使用的那样,冠词“一个(a)”、“一种(an)”、“该(the)”以及“所述(said)”旨在意指存在一个或多个要素。因此,例如,提及“一个单元”或“该单元”可以包括若干器件等。此外,词语“包括(comprising)”、“包含(including)”、“含有(containing)”和类似用语不排除其他要素或步骤。

附图说明

38.下面将参考附图来更详细地描述本发明的上述和其他方面。这些附图不应被认为是限制性的;相反,它们应该被认为是用于解释和理解的目的。

39.如附图所展示的,出于说明性目的,各层和各区域的尺寸可能被夸大,并且因此是为了展示总体结构而提供。在全文中,相同的附图标记指代相同的要素。

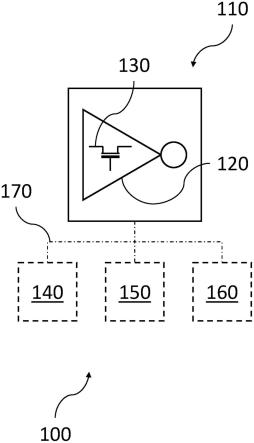

40.图1示出了fpga器件的示意性框图。

41.图2示出了包括多个clb的fpga器件的示意性框图。

42.图3示出了示例性clb的示意性框图。

43.图4示出了示例性触发器逻辑电路。

44.图5a示出了包括一个hemt的逻辑反相器。

45.图5b示出了包括一个hemt和一个上拉晶体管的逻辑反相器。

46.图6a示出了包括两个hemt的共源共栅反相器。

47.图6b示出了包括两个hemt和两个上拉晶体管的共源共栅反相器。

48.图7示出了半导体层结构和hemt的截面图。

49.图8示出了ai处理系统的示意性框图。

具体实施方式

50.现在下文将参考附图对本发明进行更全面地描述,在附图中展示了本发明的当前优选实施例。然而,本发明可以被实施为许多不同的形式并且不应当被解释为限于在此提出的这些实施例;而是,这些实施例被提供用于获得彻底性和完整性、并且向技术人员充分地传达本发明的范围。

51.图1示出了fpga器件100。fpga器件100可以是ai加速器fpga器件。fpga器件100可以被配置用于执行自动驾驶计算。fpga器件100可以适合于执行自动驾驶计算。自动驾驶计算可以包括执行与自动驾驶车辆的操作相关的机器学习或ai辅助计算。车辆可以是自动道路车辆。车辆在其操作中可以是部分或完全自动的。车辆可以是具有电化学电池和电推进装置(例如电动马达)的ev。fpga器件100可以安装在车辆中。另外,fpga器件100还可以在数据中心安装方面找到实用性。

52.fpga器件100包括clb 110。如图2所示,fpga器件100可以包括多个clb 110。clb 110可以是k输入clb,其中,k表示对应于clb 110的输入数量的整数。整数k可以是例如3、4或8。clb 110可以被配置用于学习函数映射。clb 110可以由图3例示。clb 110包括至少一个逻辑反相器120。

53.图3示出了clb,该clb包括查找表lut和具有四个输入的输入级in。这可以理解为k=4。lut输出被示为连接到触发器ff的输入,称为输入d。ff可以是所谓的d型ff。lut输出线也被示为连接到多路复用器mux。ff可以接收呈时钟信号clk形式的另一输入。ff可以提供输出,称为输出q。输出q被示为连接到mux。mux可以产生clb输出信号out。

54.图4示出了d型ff的逻辑电路图。如结合图3所提及的,ff可以包括d输入和clk输入。ff可以包括q输出和q

′

输出。q

′

输出可以被认为是q输出的逆逻辑输出或互补逻辑输出。例如,如果q对应于二进制1,则q

′

将对应于二进制0,反之亦然。ff被示为在d输入线处包括逻辑反相器120。该逻辑反相器120可以被认为是clb 110的逻辑反相器。ff进一步被示为包括四个逻辑与非门。与非门可以包括逻辑与门和逻辑反相器120。

55.逻辑反相器120包括至少一个hemt 130。图5a示出了包括一个hemt 130的逻辑反相器120。hemt 130被示为布置为逻辑反相器120的下拉网络。逻辑反相器120在输出线vout与vdd节点之间包括电阻器作为其上拉网络。电阻器可以实现为常通晶体管,该常通晶体管具有特定的导通状态电阻,从而相当于独立电阻器的电阻。图5a的逻辑反相器是所谓的1晶体管反相器,即1t反相器。连接到hemt 130的栅极节点的输入线vin上的高信号/二进制1可以导致vout处的低信号/二进制0,反之亦然。当hemt 130沟道打开时,1t反相器可以看到在vdd节点与接地节点gnd之间的经由hemt 130漏极节点和源极节点的直流路径。

56.图5b示出了逻辑反相器120,其包括上拉晶体管230,而不是像图5a中那样具有充当上拉网络的电阻器。上拉晶体管230可以用其栅极/基极节点连接到输入线vin。上拉晶体管230可以用其源极/发射极节点和漏极/集电极节点连接到vdd和vout节点中的任一个节点。这种逻辑反相器120的特征可以是从vdd节点到gnd节点的漏电流减小,因为在开关期间这两个节点之间的直流路径只打开很短的时间。由于这个原因,vout节点的上升时间和下降时间也可以更短。vout节点处的电压也可以比没有上拉晶体管230时更高。

57.上拉晶体管230可以是p型mosfet晶体管pmos。上拉晶体管230可以是基于si的晶体管。上拉晶体管230可以是基于ge的晶体管。上拉晶体管230可以是基于gan/氮化物的晶体管。上拉晶体管230可以是基于碳纳米管的晶体管。上拉晶体管230可以是高空穴迁移率晶体管hhmt。上拉晶体管230可以是隧穿场效应晶体管tfet。上拉晶体管230可以是双极结型晶体管bjt。

58.图6a示出了作为共源共栅(cascode)反相器的逻辑反相器120。逻辑反相器120可以包括至少两个hemt 130。该两个hemt 130被示为布置为逻辑反相器120的下拉网络。电阻器被示为以类似于图5a的方式形成上拉网络。顶部hemt 130被示为在其栅极节点处连接到vdd节点。这样,顶部hemt 130可以被认为是常通晶体管。另外,顶部hemt 130还可以被认为是共源共栅配置的逻辑反相器120的公共栅极级。底部hemt 130被示为在其栅极节点处连接到输入线vin。底部hemt 130可以被认为是共源共栅配置的逻辑反相器120的公共源极级。

59.图6b示出了包括两个上拉晶体管230而不是像图6a那样的单个电阻器作为其上拉网络的一部分的共源共栅配置的逻辑反相器120。顶部上拉晶体管230被示为用其栅极节点连接到输入线vin。顶部上拉晶体管230可以被认为是共源共栅配置的逻辑反相器120的公共源极/发射极级。底部上拉晶体管230被示为用其栅极节点连接到gnd节点。底部上拉晶体管230可以被认为是常通晶体管。另外,底部上拉晶体管230还可以被认为是共源共栅配置的逻辑反相器120的公共栅极级。

60.hemt 130包括alyga

y-1

n层结构380,其中,0《y≤1。hemt 130还包括gan层结构382。这些层结构特征没有在图1中示出,而是在图7中示出,现在请读者关注图7。图7示出了包括上述层结构380、382的hemt 130的截面图。图7示出了基于si衬底384的hemt 130。

61.si衬底384可以是基本上单晶的si结构。si衬底384可以是具有《111》密勒指数的si衬底。si衬底384可以是利用柴可拉斯基工艺(czochralski process)形成的si晶圆。si衬底384可以是来自较大si晶圆的芯片或裸片。

62.图7进一步示出了在si衬底384上形成的晶体过渡结构386。晶体过渡结构286被示为包括多个竖直纳米线结构388。竖直纳米线结构388进一步被示为垂直布置在si衬底384上。竖直纳米线结构388可以包括gan或aln或algan。

63.图7还示出了晶体过渡结构286包括al

x

ga

x-1

n层结构389,其中,0≤x《1。al

x

ga

x-1

n层结构389被示为布置为竖直且侧向包围竖直纳米线结构388。al

x

ga

x-1

n层结构389可以包括多个子层。多个子层的特征可以是变量x的值逐渐减小。

64.在欧洲专利申请ep 19215267中进一步描述了这种结构以及基于其的hemt,该申请通过引用并入本文。图1至图6和它们在文本中的对应段落提供了本披露内容的层结构和hemt 130的上下文和替代方案。图7至图12及它们在文本中的对应段落应当理解为关于用

于产生相同层结构和hemt 130的方法的上下文。所引用的申请的发明内容中提供了有关技术优势和语言定义的上下文。词语“晶体过渡结构”未出现在所引用的申请中,但可以理解为是指包括“si衬底”(附图标记102)和“第三半导体层”(附图标记130)中间的每一层和结构的组合结构。

65.图7示出了alyga

y-1

n层结构380布置在晶体过渡结构386上,并且gan层结构382布置在alyga

y-1

n层结构380上。可替代地,gan层结构382可以布置在晶体过渡结构386上并且alyga

y-1

n层结构380可以布置在gan层结构382上。

66.图7进一步示出了hemt 130的源极接触件s、漏极接触件d和栅极接触件g。漏极接触件d不应当与图3或图4中的触发器的输入d混淆。源极接触件、漏极接触件和栅极接触件可以由金属材料形成。源极接触件和漏极接触件可以包括ti、al、cu、ni和/或au。源极接触件和漏极接触件可以包括化合物或合金,例如alcu。除了针对源极接触件和漏极接触件所提及的材料之外,栅极接触件可以另外或可替代地包括pd和/或au。与源极接触件和漏极接触件同样,化合物和合金也是栅极接触件的选项。

67.在逻辑反相器120是共源共栅反相器的情况下,每个逻辑反相器120包括至少两个hemt 130,这些hemt包括alyga

y-1

n层结构380和gan层结构382。共源共栅或以其他方式配置的逻辑反相器120的每个hemt 130的alyga

y-1

n层结构380可以一体地形成。共源共栅或以其他方式配置的逻辑反相器120的每个hemt 130的gan层结构382可以一体地形成。hemt 130的层结构380、382可以通过钝化结构/间隔结构分隔开,以防止各个hemt 130在操作期间无意地相互影响。

68.图1示出了fpga器件100可以包括并行移位寄存器140。并行移位寄存器140可以是clb 110的一部分。可以认为并行移位寄存器140对应于clb 110的lut,例如图3中所示的lut。

69.图1进一步示出了fpga器件100可以包括存储器块150。存储器块150可以是clb 110的一部分。存储器块150可以包括随机存取存储器ram。ram可以是静态sram或动态dram。其他替代性的存储器解决方案可以包括例如磁阻ram,即mram。

70.图1和图3进一步示出了fpga器件100可以包括(多个)可编程i/o块160。图1进一步示出了fpga器件100可以包括互连170。互连170可以被配置为电连接clb 110、并行移位寄存器140、存储器块150和可编程i/o块160中的至少两者。图3示出了电连接clb 110阵列与可编程i/o块160的互连170。

71.clb 110、并行移位寄存器140、存储器块150和可编程i/o块160可以全部形成在同一si衬底384上。

72.图8示出了ai处理系统400。ai处理系统400被示为包括fpga器件100。fpga器件100可以包括存储器块150。存储器块150可以保持或被配置为保持用于操作ai处理系统400的所存储的指令。

73.ai处理系统400进一步被示为包括传感器410。传感器可以提供或被配置为提供模拟传感器输出信号。传感器410可以是例如相机或立体相机设置,包括图像传感器、雷达/激光/声学测距仪/物体检测传感器、麦克风、加速度计、陀螺仪、温度传感器、气压计、运动传感器、射频传感器等。

74.ai处理系统400进一步被示为包括adc 420。adc 420可以被提供或被配置用于从

传感器410接收传感器输出信号并处理该传感器输出信号。特别地,adc 420可以处理模拟传感器输出信号以向fpga器件100提供对应的数字信号。adc 420可以是微芯片型adc。

75.在欧洲专利申请ep 19205265中进一步描述了示例性adc 420,该申请通过引用并入本文。图1至图2的框图和电路图以及它们在文本中的对应段落提供了可以如何实施adc 420的上下文。图3至图5和它们在文本中的对应段落提供了本披露内容的层结构和hemt 130的上下文。特别地,所引用的申请提供了关于紧密地集成两个hemt 130的进一步的上下文。这可以提供对例如fpga器件100的共源共栅配置的逻辑反相器120的改进,因为可以最小化总器件占用面积。所引用的申请的发明内容中提供了有关技术优势和语言定义的进一步的上下文。

76.ai处理系统400进一步被示为包括dac 430。dac 430可被提供或被配置用于调节传感器410。dac 430可以从fpga器件接收数字指令并向传感器410提供对应的模拟信号。dac 430可以是微芯片型dac。

77.另外,所披露实施例的变型是技术人员在实践所要求保护的发明时通过学习附图、披露内容、以及所附权利要求可以理解并实现的。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。