1.本公开内容涉及基于集成光子学的光学陀螺仪的各种制造工艺,包括所述制造工艺,其中一些制造工艺涉及化学机械抛光(cmp)。

背景技术:

2.陀螺仪(也简称为“陀螺仪(gyros)”)是可感测角速度的装置。陀螺仪的应用包括但不限于军事、飞机导航、机器人、自动驾驶汽车、虚拟现实、增强现实、游戏等。陀螺仪可以是机械的或光学的,并且可在精度、性能、成本和大小方面有所不同。由于光学陀螺仪没有任何移动件,因此它们比机械陀螺仪有优势,因为它们比具有移动件的机械陀螺仪更能承受冲击、振动和温度变化的影响。最常见的光学陀螺仪是光纤陀螺仪(fog),所述fog基于因萨格纳克效应(在干涉测量中遇到的由旋转引起的现象)引起的光学相移的干涉测量进行操作。fog的构造通常涉及包括若干匝保偏(pm)光纤的线圈。激光射入保偏光纤线圈的两端,使得两束光束沿相反方向传播。如果光纤线圈正在移动,则沿相反方向传播的光束相对于彼此经历不同的光学路径长度。通过建立干涉测量系统,可测量与光纤线圈的匝所包围的环路的面积和旋转光纤线圈的角速度成正比的较小路径长度差。所述路径长度差被表达为相位信号。

3.光学陀螺仪的相位信号与萨格纳克效应乘以角旋转速度成正比,如以下方程式所示:

4.δφ=(8πna/λc)ω

5.其中,n=陀螺仪的匝数,

6.a=封闭的面积

7.ω=角旋转速度

8.δφ=光学相位差信号

9.λ=光的波长

10.c=光速

11.基于光纤的陀螺仪可提供非常高的精度,但同时,它们占有面积更大,非常昂贵,并且由于装置基于需要精确对齐的离散光学部件构建而难以装配。通常,涉及手动对齐,这难以按比例放大以进行批量生产。

技术实现要素:

12.本发明的发明人提出用基于波导的集成光子学部件代替光纤,以在半导体平台上实现成本效益好的轻松集成,这对于陀螺仪的批量生产更有前途。本技术描述使用重复沉积和退火步骤和/或化学机械抛光(cmp)技术在硅厂中制造氮化硅(sin)波导芯的各种工艺流程,如下文详细说明。

附图说明

13.根据下文给出的详细描述以及根据本公开内容的各种实施方式的附图,将更充分地理解本公开内容。

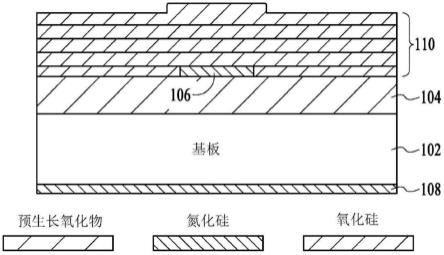

14.图1是根据本公开内容的实施方式的具有在所选波长下具有超低氢离子吸收峰值的预生长氧化物层的基板的示意图。

15.图2是根据本公开内容的实施方式的在预生长氧化物上图案化以充当下部包覆层的氮化硅(sin)波导芯的示意图。

16.图3是根据本公开内容的实施方式的在不同类型的氧化物层上图案化作为充当下部包覆层的起始材料的sin波导芯的示意图。

17.图4是根据本公开内容的实施方式的具有氧化硅顶部包覆层的sin波导芯的示意图。

18.图5是示出根据本公开内容的实施方式的氧化硅顶部包覆层的单独层的示意图。

19.图6是如根据本公开内容的示例性工艺制造的具有其顶部包覆层和底部包覆层的sin波导芯的横截面的透射电子显微照片(tem)。

20.图7是根据本公开内容的实施方式的在远离先前形成的sin波导芯的竖直距离处图案化的第二sin波导芯的示意图。

21.图8是根据本公开内容的实施方式的两个竖直分离的sin波导芯的示意图,其中氧化硅顶部包覆层和底部包覆层用于sin波导芯的顶层,并且氧化硅顶部包覆层和预生长氧化物底部包覆层用于sin波导芯的底层。

22.图9是根据本公开内容的实施方式的用于后续晶片结合工艺的氧化硅层的化学机械抛光(cmp)的第一示意图。

23.图10是根据本公开内容的实施方式的用于后续晶片结合工艺的氧化硅层的化学机械抛光(cmp)的第二示意图。

24.图11是根据本公开内容的实施方式的在基于cmp的工艺流程中结合在sin波导芯的顶部的晶片的示意图。

25.图12是根据本公开内容的实施方式的用于镶嵌工艺流程的起始材料的示意图。

26.图13是根据本公开内容的实施方式的在镶嵌工艺流程中对sin波导芯蚀刻的沟槽的示意图。

27.图14是根据本公开内容的实施方式的在镶嵌工艺流程中填充有sin以形成sin波导芯的沟槽的示意图。

28.图15是根据本公开内容的实施方式的在镶嵌工艺流程中向下抛光到平面的sin波导芯的示意图。

29.图16是根据本公开内容的实施方式的在镶嵌工艺流程中沉积在sin波导芯的顶部的氧化硅层的示意图。

30.图17是根据本公开内容的实施方式的处于“全玻璃”(熔融二氧化硅顶部包覆层和底部包覆层)配置的sin波导芯的示意图。

31.图18是根据本公开内容的实施方式的sin波导芯的示意图,其中底部包覆层是熔融二氧化硅并且顶部包覆层是氧化硅。

32.图19至图21是根据本公开内容的实施方式的工艺流程的示意图,所述工艺流程使

用厚氧化物晶片作为起始材料,然后在顶部沉积和图案化sin波导芯。

33.图22至图24示出根据本公开内容的实施方式的在氧化物底部包覆层中产生sin波导芯的一种可能的cmp流程。

34.图25至图26示出了根据本公开内容的实施方式的用于产生sin波导芯的另选cmp流程。

35.图27示出根据本公开内容的实施方式的在一个层中具有波导芯的单层陀螺仪感测芯片的最终横截面。

36.图28示出根据本公开内容的实施方式的在两个层中具有波导芯的多层陀螺仪感测芯片的最终横截面。

具体实施方式

37.本公开内容的方面涉及用于光学陀螺仪应用的基于紧凑型超低损耗集成光子学的波导的配置,以及制造那些波导以便于大规模制造的方法。描述了四个主要工艺流程:(1)基于氧化物沉积和退火的重复序列的工艺流程;(2)基于化学机械抛光(cmp)的工艺流程,然后是晶片结合;(3)镶嵌工艺流程,然后是氧化物沉积和退火或晶片结合;以及(4)基于cmp的工艺流程,然后是氧化物沉积。可采用这些工艺流程的任何组合来满足使用标准硅制造技术在硅基板上以一个或多个层制造光学陀螺仪波导的最终目标。在此特定应用中,基于cmp的工艺流程至少实现了两个目标:获得层的准确厚度,而无需精确控制沉积参数,以及获得sin芯的基于cmp的顶表面的期望表面粗糙度,原因是表面粗糙度对波导损耗有很大影响。应注意,可即使在沉积sin层之前使用cmp以进一步减小所沉积的sin层的粗糙度。

38.基于光纤的光学陀螺仪的高性能的关键是用于测量萨格纳克效应的高质量、低损耗的光纤具有较长长度。本发明的发明人认识到,随着适用于晶片规模处理的集成硅光子学的出现,有机会在不牺牲性能的情况下用更小的集成光子芯片解决方案代替fog。基于光子学的光学陀螺仪具有减小的大小、重量、功率和成本,但另外可大批量生产,并且不受振动影响,并且潜在地提供与fog相当的性能。

39.此集成光子学解决方案的一个关键要素是生产非常低损耗的波导,所述波导可使用晶片级工艺制造,并且可用于替代光学陀螺仪中的较长长度的pm光纤。用于此基于集成光子学的光学陀螺仪的技术平台是基于被氧化物或熔融二氧化硅包覆层包围的氮化硅(si3n4)波导芯。为简单起见,有时将整个波导结构称为sin波导。

40.本文公开了生产非常低损耗的sin波导的配置和方法,所述sin波导可用作较小占有面积集成光学陀螺仪(其缩写为siphog

tm

(硅光子学光学陀螺仪)的集成部件)。根据本文所述的工艺流程制造的sin波导中的传播损耗可远低于0.1db/米。这是对传播损耗在0.1db/cm范围内的当前最先进的sin工艺的巨大改进。在使用标准硅厂工艺和设备时降低损耗的关键是要么使用高质量的熔融二氧化硅(有时称为“玻璃”)晶片,要么使用具有预生长氧化物的晶片作为下部包覆层,然后通过重复的沉积/退火步骤沉积所需厚度的氧化硅作为上部包覆层。重复的沉积/退火步骤确保对上部包覆层的厚度的精确控制,以及从所沉积层中清除捕获的氢。

41.本发明的发明人认识到将sin波导线圈(或螺线)和/或环分布到不同的竖直分离的层(例如,两个或更多个层)中导致陀螺仪灵敏度的更低值而不增加形状因数。2019年6月

7日提交的标题为“integrated silicon photonics optical gyroscope on fused silica platform”的共同未决的共同拥有的临时申请62/858,599中涵盖了堆叠的多层陀螺仪配置的详细信息。2019年9月5日提交的标题为“single-layer and multi-layer structures for integrated silicon photonics optical gyroscopes”的后续临时申请62/896,365描述了附加的实施方式。所述申请以引用方式并入本文。另外,2019年7月10日提交的标题为“system architecture for silicon photonics optical gyroscopes”的共同未决的共同拥有的临时申请62/872,640以及2019年9月23日提交的标题为“system architecture for silicon photonics optical gyroscopes with mode-selective waveguides”的62/904,443中已经涵盖了基于硅光子学的前端芯片和sin波导芯片的系统级集成。所述申请以引用方式并入本文。

42.图1至图8示出用于在常规硅基板上制造sin波导芯(一个层或两个层)的示例性工艺流程,其中sin波导芯周围具有不对称上部包覆层(原硅酸四乙酯(teos))和下部包覆层(生长氧化物)。具体地,图1示出具有带预生长氧化物层104的基板102的晶片。基板102可以是硅基板并且预生长氧化物层可以是具有10μm-15μm的示例性尺寸的结晶层。层104的关键特性在于其在感兴趣的波长下具有低吸收峰值(例如,约1550nm,但未必处于精确的1550nm,原因是波导传播损耗可针对与1550nm稍微不同的波长进行优化)。晶片的两面都可抛光。

43.图2示出sin层被沉积以在预生长氧化物层104的顶部和附近形成层,所述层被图案化以产生波导芯106。sin波导芯106的非限制性说明性尺寸是60nm-100nm的高度(即,波导层的厚度

‘

h’)和2μm-10μm的侧向宽度。本领域技术人员将了解,说明书中提及的这些说明性尺寸值不会限制本公开内容的范围。sin层可使用低压化学气相沉积(lpcvd)工艺或其他工艺来沉积。底部sin层108可保持完整,其中顶部sin层通过光刻或以其他方式在预生长氧化物层104上图案化以形成波导芯106。为了减小sin波导芯106中的线边缘粗糙度,可能需要一定的蚀刻后处理。例如,可移除光刻胶和光刻辅助层(例如,barc)之后的覆盖氩(ar)溅射步骤,以使sin波导芯106的顶部和侧面平滑。另选地,可执行热磷酸中的覆盖浸渍,这在sin(高蚀刻速率)与预生长氧化物104之间具有非常高的选择性。蚀刻后清洁可包括过氧硫酸清洁(例如,与过氧化物混合的热硫酸)和sc1(稀释的热氢氧化铵和过氧化物混合物)或sc2(与过氧化物混合的盐酸)。最终,可执行蚀刻后高温退火以从sin层中驱除任何剩余的氢或其他杂质。图3示出在另选的实施方式中,代替结晶预生长氧化物层104,也可使用其他类型的氧化物起始材料103作为底部包覆层,其实例是非结晶熔融二氧化硅(“玻璃”)或石英。

44.继续利用预生长氧化物层104的工艺流程,如图4所示,生长氧化硅层(也称为teos层)110以覆盖sin波导芯106。氧化硅层110可具有2μm-3μm的总厚度。需要最小化teos层中的氢,并且相应地调节生长速率。任选地,可执行预沉积退火(例如,在1150℃-1200℃下持续2小时或更多小时)。可在若干轮中获得teos层的总最终厚度,例如,每一轮生产0.1μm至0.2μm厚的层。应注意,图4所示的结构在波导芯106周围具有不对称包覆层,原因是上部包覆层是teos(层110),而下部包覆层是生长氧化物(层104)。波导损耗在很大程度上取决于充当上部包覆层的teos层的质量。

45.如图5所示,氧化物层110包括所沉积的teos的单独层,每次沉积之后是退火步骤

以驱除氢。尽管图中仅示出了5个层,但可根据沉积速率和退火时间选择任意数量的层。例如,如果层110的总厚度为2μm,则可沉积十个层,每个层具有0.2μm的厚度。通常,高温lpcvd方法用于teos沉积。所述方法可从预沉积退火开始。然后,多次重复沉积-退火-沉积-退火序列。对于每次退火,温度可以是1150℃-1200℃,并且持续时间可以是2小时。应注意,代替teos作为前驱物气体,氯化源或氘化源可用于氧化硅沉积。

46.图6是如根据本公开内容的示例性工艺制造的具有其顶部包覆层和底部包覆层的sin波导芯的横截面的透射电子显微照片(tem)。此tem证明所沉积的上部包覆氧化物层110具有与下部包覆预生长氧化物层104一样好的属性。

47.图7和图8示出形成另一波导芯112以实现多层光学陀螺仪。应注意,尽管出于说明性目的仅示出了两个波导核芯层,但可通过本文所讨论的工艺流程产生多于两个波导芯层。具体地,图7示出所沉积的氧化硅层110被抛光,然后使用与以上所讨论的形成底部sin波导芯106相同的工艺在层110的顶部图案化顶部sin波导芯112。图8示出重复沉积-退火-沉积-退火序列以将顶部sin波导芯112掩埋在上部包覆层之下。换句话讲,图7中的氧化物层110在波导芯112上方延伸以产生图8中的氧化物层114的总厚度。最终退火步骤可更长(例如,6小时,以防止氢向下扩散。

48.图9至图11示出另选工艺流程,其涉及化学机械抛光(cmp)和晶片结合以产生上部包覆层。具体地,图9示出如上所述在sin波导芯106上方形成氧化硅层110。所述工艺可包括利用硫酸和sc1或sc2的预沉积清洁步骤。附加地,可执行预沉积退火步骤。通过使用高温lpcvd,最小化了sin-氧化物界面处的气隙的可能性。图10示出氧化物层110的初始厚度通过cmp减小到与sin波导芯106几乎齐平或稍微延伸到sin波导芯106上方。可添加虚设结构以确保cmp均匀性和工艺控制。图11示出熔融二氧化硅晶片120可结合在cmp变薄的氧化物层110的顶部,其中晶片120充当上部包覆层。

49.图12至图16示出涉及镶嵌工艺的又一另选工艺流程。如图12所示,在镶嵌工艺中,氧化物起始材料103可以是预生长氧化物(诸如图1所描述的104)。图13示出通过定时蚀刻在氧化物起始材料103中产生沟槽(或凹口)122。沟槽122的尺寸与sin波导芯106的尺寸相同(例如,期望波导芯高度97.5nm可以是沟槽122的示例性深度,并且沟槽的侧向宽度匹配波导宽度(例如,2.5um-4.5um))。沟槽122的侧壁应具有竖直侧壁,如由定时蚀刻参数控制。

50.图14示出氮化硅层107被沉积在氧化物起始材料103的顶部,以符合凹口122。同时,sin层108也形成在基板的背面上。至少顶部sin层107需要尽可能不含污染物。sin沉积的lpcvd方法是优选的。而且,执行退火以将污染物(包括氢)驱出sin层107。图15示出sin层107被向下抛光到氧化物层103,使得沟槽122中剩余的sin产生sin波导芯106。在抛光之后,执行清洁步骤,然后执行退火(例如,在1150c-1200c下持续2-6小时)。

51.图16示出上部包覆层的形成,所述上部包覆层可包括如上所述的沉积的氧化硅层110。teos氧化物层110可通过沉积和退火的重复序列形成,以达到2um-3um的期望厚度。退火长度可发生变化,并且退火的总长度可长达20小时以驱除污染物。

52.应注意,如上所述的晶片结合可用于在镶嵌工艺中产生上部包覆层。

53.图17示出一个实例,其中起始晶片(例如,具有凹口122)和结合的晶片都是熔融二氧化硅,使得具有“全玻璃”配置250。另选地,可使用具有预生长氧化物的硅基板(如图1所示)作为起始晶片,并且从顶部结合另一此类晶片(与面向sin波导芯106的预生长氧化物层

颠倒)以产生顶部包覆层。

54.图18示出另选方案,其中起始晶片是顶部形成有sin波导芯106的熔融二氧化硅晶片250,并且上部包覆层由teos(或其他另选源,诸如氯化源、氘化源等)形成。退火长度在1200c下可以是6-10小时多次,以驱除污染物。

55.图19至图21是根据本公开内容的实施方式的工艺流程的示意图,所述工艺流程使用厚氧化物晶片作为起始材料,然后在顶部沉积和图案化sin波导芯。如图19所示,热氧化晶片可以是14.5um厚并且在基板204的两侧上具有厚的氧化物层204和205。图20示出sin波导芯106被沉积和图案化在层204的顶部。图21示出形成上部包覆层206以包围波导芯106。可使用如上所述的teos氧化物源来沉积层206。

56.已知基于干涉式光纤的光学陀螺仪的灵敏度由两个反向旋转光束的相位差确定,并且由以下方程式表示:其中l是光纤的长度,并且d是每个环路的直径。相同类比适用于平面装置,诸如siphog,其中光纤被平面波导取代。为了设计灵敏系统,希望获得更长的长度并且最大化产品(l*d)。然而,对这种系统的限制是sin波导的传播损耗。本发明的发明人已经开发了若干方法来减小传播损耗,诸如上述沉积-退火序列。根据测量数据确定损耗的减小逼近由块状材料的属性引起的损耗极限,并且损耗将在很大程度上取决于由制造工艺中的缺陷引起的散射。由于波导纤芯又薄又宽(例如,60nm-100nm厚和2um-3um宽),因此传播损耗对波导芯的侧壁的粗糙度的依赖性非常低,而对粗糙度的波导芯的底部和顶部的依赖性很高。具有多个匝的基于波导的陀螺仪传感线圈可有几十米长,并且已经通过实验验证sin芯片中的过量损耗可归因于散射损耗。为了改善散射损耗,发明人已经证明可使用化学机械抛光(cmp)来减小波导芯的顶表面和底表面的粗糙度。cmp后所得的损耗水平与新抛光的硅晶片相当。

57.图22至图24示出根据本公开内容的实施方式的在氧化物底部包覆层中产生sin波导芯的一种可能的cmp流程。在此工艺流程中,在二氧化硅底部包覆层104上沉积和图案化(106a)sin的更厚层,如图22所示。厚度

‘

h1’可高得多(例如,最终期望厚度的两倍),即,在此步骤中不需要对sin层进行精确的厚度控制。然后,如图23所示,环绕波导芯106a沉积顶部氧化物层110,其仍然比最终期望厚度

‘

h2’厚。最后,使用cmp工艺抛光顶部氧化物层110和sin层106a的一部分,使得波导芯106的最终厚度为期望厚度

‘

h2’,并且波导芯106的顶表面与底部包覆层氧化物层104的顶表面自动齐平。

58.图25至图26示出根据本公开内容的实施方式的用于产生sin波导芯的另选cmp流程。在此工艺流程中,在二氧化硅底部包覆层104上沉积sin的更厚层106b,如图25所示。厚度

‘

h1’可高得多(例如,最终期望厚度的两倍),即,在此步骤中不需要对sin层进行精确的厚度控制。然后可使用cmp工艺抛光sin层106b,以将厚度降低到期望厚度

‘

h2’(层106c)。在实例中,h1可在200nm的范围内,而h2可在100nm或更低的范围内。然后可图案化减薄的层106c以产生波导芯106。

59.图27示出根据本公开内容的实施方式的在一个层中具有波导芯的单层陀螺仪感测芯片的最终横截面。波导芯106-1和106-2中的每一者(具有厚度h2和宽度w)可被设想为光学陀螺仪的多匝感测线圈的相邻匝。可使用上述cmp流程(或其他制造流程)中的一个流程在底部包覆层104上形成芯。在cmp后,沉积顶部包覆层110-1。应注意,当底部包覆层104(厚度h1)、sin层106和顶部包覆层110-1(厚度h2)形成在硅基板102的一侧上时,对应氧化

物层104-1(厚度h1)、sin层108-1和氧化物层110-2也形成在基板102的另一侧上。间断101在硅基板102的中间示出以传达硅基板102的厚度比其余装置层高几个数量级的想法。

60.图28示出根据本公开内容的实施方式的在两个层中具有波导芯的多层陀螺仪感测芯片的最终横截面。这里,重复氧化物层(110-1和110-3)和sin层(106-1、106-2、106-3、106-4)的沉积和cmp工艺以产生最终的多层结构。第一层波导芯106-1和106-2与第二层波导芯106-3和106-4竖直隔开距离

‘

s’(氧化物层110-1的厚度)。在硅基板102的另一侧上,自动形成对应氧化物层104-1、110-2和110-4以及sin层108-1和108-2,但这些层可能并不用于导波目的。

61.本领域技术人员将了解,可结合各种计量步骤(包括但不限于在各种阶段的翘曲度检验、在某些感兴趣波长下的折射率测量、线边缘粗糙度测量等)来监测工艺流程的功效并且确定工艺参数调节。

62.附加地,本领域技术人员将了解,不同代的siphog可基于干涉波导线圈或环形谐振器,但两种配置都依赖于如本公开内容中的图中所描述的低损耗波导芯和包覆结构。

63.在前述说明书中,已经参考其具体示例性实施方式对本公开内容的实施方式进行了描述。将显而易见的是,在不脱离如以下权利要求中阐述的本公开内容的具体实施的更宽广精神和范围的情况下,可对其做出各种修改。因此,应以说明性意义而不是限制性意义来理解本说明书和附图。附加地,方向术语,例如,“顶部”、“底部”等,不会将本公开内容的范围限制为任何固定取向,而是涵盖取向的各种排列和组合。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。