一种4h-sic基超结功率场效应晶体管器件

技术领域

1.本实用新型涉及到半导体功率器件技术领域,具体涉及一种4h-sic基超结功率场效应晶体管器件。

背景技术:

2.超结功率mosfet即金属-氧化物-半导体场效应晶体管,是为改善传统功率mosfet中击穿电压与比导通电阻之间的矛盾而提出的,被广泛地应用于中低功率电源设备中。然而,现有的超结功率mosfet器件存在关断时间长、开关功耗较大的缺陷。因此,如何进一步提高器件导通电流的能力,降低器件的开关功耗,缩短关断时间则成为新的研究方向。

技术实现要素:

3.针对现有技术的不足,本实用新型的目的是提供一种4h-sic基超结功率场效应晶体管器件,以提高器件导通电流的能力,降低器件的开关功耗,缩短关断时间。

4.为达到上述目的,本实用新型采用的技术方案如下:

5.一种4h-sic基超结功率场效应晶体管器件,其关键在于:由多个重复元胞结构相互拼接而成,所述元胞结构包括漏电极、源电极、栅电极、衬底区、源区、源体区、栅区以及绝缘层;所述漏电极贴合于所述衬底区的下表面,所述衬底区的一侧上表面上设置有缓冲区,所述缓冲区的高度大于所述衬底区的高度,在所述缓冲区上设置有第一漂移区,在所述衬底区另一侧的上表面设置有第二漂移区,且该第二漂移区部分位于所述缓冲区的上方,所述第二漂移区的内表面与所述第一漂移区的内表面相接触,所述第二漂移区的厚度大于所述第一漂移区的厚度,所述源区与所述源电极并排嵌入所述源体区,所述源区、源电极的上表面与所述源体区的上表面齐平,且所述源区位于所述源电极的内侧,所述源体区的下表面与所述第二漂移区的上表面接触且其内侧延伸至与所述第一漂移区接触,所述栅电极、栅区和绝缘层从上到下依次层叠设置在所述第一漂移区的上方,且所述绝缘层的下表面与所述第一漂移区、源体区以及部分源区的上表面接触。

6.进一步的,所述源区、第一漂移区、衬底区、缓冲区、栅区与所述源体区、第二漂移区的掺杂类型不同,当所述源区、第一漂移区、缓冲区、衬底区和栅区的掺杂类型为n型时,所述源体区、第二漂移区的掺杂类型为p型;当所述源区、第一漂移区、缓冲区、衬底区和栅区的掺杂类型为p型时,所述源体区、第二漂移区的掺杂类型为n型。

7.进一步的,所述缓冲区的掺杂浓度低于所述衬底区的掺杂浓度,且缓冲区的掺杂浓度高于第一漂移区的掺杂浓度。

8.进一步的,所述衬底区与所述第二漂移区接触的面积小于与所述缓冲区接触的面积。

9.进一步的,所述源区、第一漂移区、衬底区、源体区、第二漂移区和栅区均由半导体材料制成,所述漏电极、源电极和栅电极均由金属材料制成。

10.进一步的,所述半导体材料为硅、砷化镓、氮化镓或者碳化硅。

11.本实用新型的显著效果是:结构简单,易于实现,通过将源体区下沉并将源电极嵌设于下沉位置,从而有效缩短了电流路径,降低了器件的比导通电阻,提高了器件导通电流的能力,减小了器件元胞尺寸,进而减小了器件面积,提升了mosfet器件的uis雪崩耐量能力;此外,还通过缓冲区的设置,有效地提高了寄生体二极管反向恢复电流的软度,改善反向恢复特性,使得器件在开关过程中不易产生振荡,抑制了电磁干扰信号,器件工作更加安全可靠。

附图说明

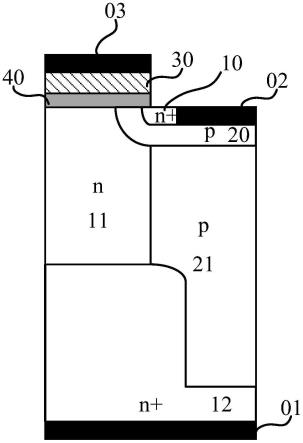

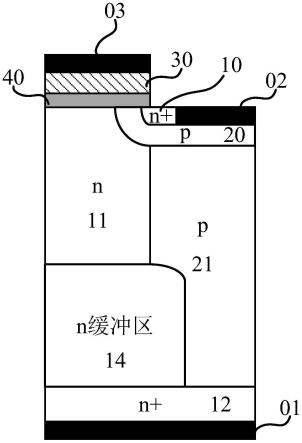

12.图1是本实用新型的结构示意图。

具体实施方式

13.下面结合附图对本实用新型的具体实施方式以及工作原理作进一步详细说明。

14.如图1所示,一种4h-sic基超结功率场效应晶体管器件,由多个重复元胞结构相互拼接而成,所述元胞结构包括漏电极01、源电极02、栅电极03、衬底区12、源区10、源体区20、栅区30以及绝缘层40;所述漏电极01贴合于所述衬底区12的下表面,所述衬底区12的一侧上表面上设置有缓冲区14,所述缓冲区14的高度大于所述衬底区12的高度,在所述缓冲区14上设置有第一漂移区11,在所述衬底区12另一侧的上表面设置有第二漂移区21,且该第二漂移区21部分位于所述缓冲区14的上方,所述第二漂移区21的内表面与所述第一漂移区11的内表面相接触,所述第二漂移区21的厚度大于所述第一漂移区11的厚度,所述源区10与所述源电极02并排嵌入所述源体区20,所述源区10、源电极02的上表面与所述源体区20的上表面齐平,且所述源区10位于所述源电极02的内侧,所述源体区20的下表面与所述第二漂移区21的上表面接触且其内侧延伸至与所述第一漂移区11接触,所述栅电极03、栅区30和绝缘层40从上到下依次层叠设置在所述第一漂移区11的上方,且所述绝缘层40的下表面与所述第一漂移区11、源体区20以及部分源区10的上表面接触。

15.4h-sic基超结功率场效应晶体管器件的元胞结构图由第一种导电类型的第一漂移11区和第二种导电类型的第二漂移区21组成的耐压层,且第一漂移区11与第二漂移区21的下表面齐平,耐压层有两个表面;在上表面中设有至少一个第二种导电类型的源体区20,源体区20之内又至少有一个第一种导电类型的重掺杂的源区10,部分源区10和部分源体区20通过导体相连,构成器件的源电极02;在部分源区10和部分源体区20以及部分耐压层的表面覆盖有绝缘层40,在绝缘层40上覆盖有作为器件栅电极的第一种导电类型的重掺杂的半导体多晶硅栅区30,栅区30的部分表面覆盖有导体,形成器件的栅电极03;在下表面中设有一个第一种导电类型的重掺杂的半导体衬底区12,在衬底区12表面覆盖有作为漏电极01的导体。

16.其中,所述的第一导电类型为n型时,第二导电类型为p型;第一导电类型为p型时,第二导电类型为n型。

17.本例中,所述源区10、第一漂移区11、衬底区12、缓冲区14、栅区30与所述源体区20、第二漂移区21的掺杂类型不同,当所述源区10、第一漂移区11、缓冲区14、衬底区12和栅区30的掺杂类型为n型时,所述源体区20、第二漂移区21的掺杂类型为p型;当所述源区10、第一漂移区11、缓冲区14、衬底区12和栅区30的掺杂类型为p型时,所述源体区20、第二漂移

区21的掺杂类型为n型。

18.优选的,所述缓冲区14的掺杂类型与所述衬底区12相同,且其掺杂浓度低于所述衬底区12的掺杂浓度,且缓冲区14的掺杂浓度高于第一漂移区11的掺杂浓度。

19.进一步的,所述衬底区12与所述第二漂移区21接触的面积小于与所述缓冲区14接触的面积。

20.优选的,所述源区10、第一漂移区11、衬底区12、缓冲区14、源体区20、第二漂移区21和栅区30均由半导体材料制成,所述漏电极01、源电极02和栅电极03均由金属材料制成。所述半导体材料为硅、砷化镓、氮化镓或者碳化硅。

21.本实施例与常规超结mosfet结构相比,所述第二漂移区21延伸至衬底区12里面。延伸部分在体二极管导通时会积累一定量的非平衡载流子。在体二极管反向恢复过程中,当超结结构部分载流子浓度突然减小时,这些积累的载流子及时予以补充,从而保证反向恢复电流平滑衰减,实现软恢复。晶体管的正向阻断特性与第二漂移区21中的延伸部分密切有关,基本要求是在第二漂移区21中,被衬底区12包围的部分的宽度小于被第一漂移区11包围的部分的宽度。

22.本实施例的最重要之处在于,在保证寄生体二极管反向恢复电流的软度、不增加器件的比导通电阻的前提下,通过将源体区20下沉并将源电极02嵌设于下沉位置,从而有效缩短了电流路径,减小了器件元胞尺寸,进而减小了器件面积,提升了mosfet器件的uis雪崩耐量能力。此外,还通过缓冲区14的设置,有效地提高了寄生体二极管反向恢复电流的软度,改善反向恢复特性,使得器件在开关过程中不易产生振荡,抑制了电磁干扰信号,器件工作更加安全可靠。

23.以上对本实用新型所提供的技术方案进行了详细介绍。本文中应用了具体个例对本实用新型的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本实用新型的方法及其核心思想。应当指出,对于本技术领域的普通技术人员来说,在不脱离本实用新型原理的前提下,还可以对本实用新型进行若干改进和修饰,这些改进和修饰也落入本实用新型权利要求的保护范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。