1.本发明涉及复合基板及其制造方法。

背景技术:

2.为了扩大传统功能材料(如半导体和氧化物单晶)的应用范围,近年来广泛进行了针对不同种类的基板的粘合从而获得更高性能的开发。在半导体领域中已知有绝缘体上硅(silicon on insulator:soi)等,而在氧化物单晶领域中报告了通过将诸如钽酸锂(lithium tantalate,litao3缩写为lt)或铌酸锂(lithium niobate,linbo3缩写为ln)的氧化物单晶基板与蓝宝石等进行粘合并且通过减薄该氧化物单晶基板来使复合基板的温度特性得到改善。

3.也有人试图在功能性薄膜与硅晶片之间设置夹层(又称“间层”或“中间层”)以用于分离。诸如sio2那样的绝缘性高、高频损耗少(低介电损耗)且易加工(平坦化)的材料通常用作夹层的材料。为了满足上述性质,经常选择金属氧化物(除sio2以外例如sion、tio2、al2o3、ta2o5、nb2o5、y2o3或zro2等)用于夹层。特别常用的材料是通过硅的热氧化而获得的sio2。由此获得的soi晶片或“硅晶片上的氧化物单晶(oxide single-crystal on si wafer)”(以下称为“绝缘体上压电材料(piezo-material on insulator:poi)”)由于其活性层较薄,所以通常具有诸如优异的高频特性(低高频损耗、线性度改进和串扰减少)等优异性能。现有技术文献专利文献

4.专利文件1:us2017/0033764a

技术实现要素:

本发明要解决的技术问题

5.然而,通过经由夹层粘合而获得的上述复合基板也具有缺点。通常作为基底基板的硅使用高电阻的硅以减少高频损耗,但已知在这种情况下硅晶片的上层会带电并且导致所获得的复合基板的特性恶化。为了避免上述问题,通过在soi(通常称为“富陷阱soi(trap-rich soi)”)中设置有埋入的绝缘膜的正下方的载流子陷阱层以赋予使其产生的载流子消失的功能来采取对策。具体而言,载流子陷阱层通常由多晶硅(polysilicon)形成,然而伴随的问题点是在soi或poi的制造过程中进行粘合时应该将多晶硅层平滑化到原子水平(ra《1nm)。从时间或成本的观点出发,由于硅的抛光速率因方位而稍有不同,因此对多晶硅进行平滑化并不是上策。

6.为了解决上述问题,本发明人设计了以下方法。该方法是利用氢离子针对成为基底基板的硅晶片或者通过热氧化、cvd法或pvd法形成了绝缘膜的晶片进行离子注入,并由此通过离子注入在硅基板的上部中形成损伤层。专利文献1等中还提出通过离子注入来形成损伤层并将所得基板用作poi晶片的基底基板。在专利文献1中,通过离子注入将“损伤

层”转换为“非单晶层”来获得载流子陷阱层。这种方法非常有利,这是由于即使在离子注入之后表面粗糙度也不会大幅劣化,并且晶片可以按原样直接粘合。特别地,当针对诸如经受热氧化的硅晶片那样具有原子水平的平滑表面的基板进行离子注入时,可以在注入后不施加抛光等步骤而直接按原样进行粘合。

7.然而,已知这种方法会导致问题发生。具体地,在离子注入处理期间用于离子注入的大量离子会保留在晶片中,并且在粘合之后经过热处理或长期使用等情况下晶片中保留的这些多余离子会到达粘合界面且导致膜剥离发生。因此,为了保持高可靠性,有必要在粘合前去除多余的离子。虽然为了去除多余的残存离子可以进行热处理以使多余的离子向外扩散,但是离子注入的硅晶片通过热处理在其中产生被称为“微腔”的气泡,使表面的粗糙度劣化,由此会产生不适合粘合的表面状态。

8.鉴于上述问题,本发明的目的在于提供一种复合基板以及提供一种制造复合基板的方法,所述复合基板的待粘合的晶片具有足够小的表面粗糙度并且能够防止膜剥离的发生。解决问题的方法

9.为了达到上述目的,作为本发明的一个方面,本发明提供了一种制造复合基板的方法,该复合基板具有按列出顺序层叠的硅晶片、夹层、单晶硅薄膜或氧化物单晶薄膜,该方法包括下列步骤:对硅晶片进行离子注入处理后进行热处理,以在硅晶片的上层部分形成损伤层;将所述硅晶片和与所述单晶硅晶片或所述氧化物单晶硅晶片经由其间的夹层彼此粘合以获得接合体;以及,将所述接合体的所述单晶硅晶片或所述氧化物单晶晶片减薄成为单晶硅薄膜或氧化物晶体薄膜。

10.夹层优选包含sio2、sion、sin、al2o3、tio2、ta2o5、nb2o5、y2o3或zro2。

11.所述夹层优选通过对所述硅晶片进行热氧化来形成。或者,所述夹层优选通过化学气相沉积法(cvd法)或物理气相沉积法(pvd法)来形成。

12.在上述离子注入处理中注入的离子种类是氢原子离子(h

),且剂量优选设定在2.5

×

10

16

~5.0

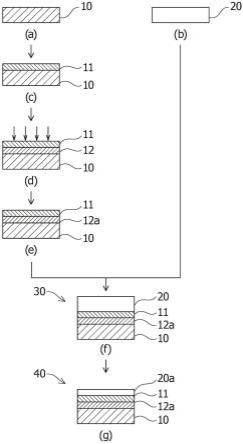

×

10

16

atom/cm2之间。或者,在上述离子注入处理中注入的离子种类是氢分子离子(h

2

),且剂量优选设定在1.25

×

10

16

至2.5

×

10

16

atom/cm2之间。

13.热处理优选在400℃或更高的温度下进行。

14.接合体的单晶硅晶片或氧化物单晶晶片优选通过磨削或抛光或者它们的组合来减薄。本发明的方法可还包括对单晶硅晶片或氧化物单晶晶片的待粘合表面(简称“粘合面”)进行离子注入处理处理以在单晶硅晶片或氧化物单晶晶片的内部形成离子注入层的步骤,并且优选通过在所述接合体上留下离子注入层作为单晶硅薄膜或氧化物单晶薄膜并且从所述接合体上剥离所述单晶硅晶片或所述氧化物单晶晶片的剩余部分,以使所述接合体的所述单晶硅晶片或所述氧化物单晶晶片减薄。

15.在本发明的另一方面,本发明提供一种复合基板,该复合基板具有按列出顺序层叠的硅晶片、夹层和单晶硅薄膜或氧化物单晶薄膜,并且该复合基板在该所述夹层一侧的所述硅晶片的一部分中还具有损伤层。

16.夹层优选包含sio2、sion、sin、al2o3、tio2、ta2o5、nb2o5、y2o3或zro2。

17.氧化物单晶薄膜优选包含钽酸锂(lt)或铌酸锂(ln)。

发明效果

18.因此,本发明提供一种复合基板以及提供一种制造复合基板的方法,所述复合基板的待粘合的晶片具有足够小的表面粗糙度并且能够防止膜剥离的发生。

附图说明

19.图1是说明本发明的制造复合基板的方法的一个实施方式的示意性流程图。图2是示出发生膜剥离的晶片表面的显微镜照片。图3是示出实施例1的晶片上热氧化膜表面的原子力显微镜(afm)图像。图4是示出实施例1的晶片的截面的透射电子显微镜(tem)图像。

具体实施方式

20.下面,通过参考附图来描述本发明的复合基板的实施方式及其制造方法,但本发明的范围不局限于这些。

21.本实施例的制造复合基板的方法,如图1所示,包括:准备硅晶片10的步骤(图1中的(a)),准备单晶硅晶片或氧化物单晶晶片20的步骤(图1中的(b)),在硅晶片上形成夹层11的步骤(图1中的(c)),对硅晶片10的夹层11一侧进行离子注入处理的步骤(图1中的(d)),对离子注入处理后的硅晶片10进行热处理的步骤(图1中的(e)),将硅晶片10与单晶硅晶片或氧化物单晶晶片20经由夹层11和损伤层12a彼此粘合而得到接合体30的步骤(图1中的(f)),以及将接合体30的单晶硅晶片或氧化物单晶晶片20减薄成为单晶硅薄膜或氧化物单晶薄膜20a而得到复合基板40的步骤(图1中的(g))。下面针对各步骤进行详细说明。

22.在步骤(a)中准备的硅晶片10可以是通常用作复合基板的支承晶片的硅晶片,晶片的尺寸具有例如2至12英寸的直径和500至800μm的晶片厚度(板厚)。

23.关于在步骤(b)中准备的单晶硅晶片或氧化物单晶晶片20(下面也可称为“第二晶片20”),作为单晶硅晶片例如可以使用通过提拉法(czochralski method)培育的通常市售的单晶硅晶片,并且作为氧化物单晶晶片优选为压电单晶,例如由锂以及钽或铌等金属元素和氧来构成的化合物。此类化合物的实例包含钽酸锂(litao3缩写为“lt”)和铌酸锂(linbo3缩写为“ln”)。第二晶片20的尺寸没有特别限制,可以具有例如2至8英寸的直径以及100至1000μm的晶片厚度。

24.在步骤(c)中,在硅晶片10的待粘合表面上形成夹层11。夹层11的材料优选绝缘性高、高频损失少(低介电损耗)、加工(平坦化)容易的材料。该材料的实例包括但不限于sio2、sion、sin、al2o3、tio2、ta2o5、nb2o5、y2o3或zro2。作为夹层11的形成方法,例如可以通过对硅晶片10进行热氧化来形成热氧化膜(sio2),也可以通过化学气相沉积法(cvd法)或物理气相沉积法(pvd法)形成sio2层或上述金属氧化物等的层。

25.当形成热氧化膜时,例如可以在空气气氛中在700至1200℃下对硅晶片10进行热处理,以在硅晶片10的表面上形成热氧化膜。cvd法的实例包括热cvd法、等离子体cvd法和光cvd法等。pvd法的实例包括气相沉积法、离子镀法和溅射法等。夹层11优选具有例如100至5000nm的厚度。

26.在步骤(d)中,对硅晶片10的夹层11一侧进行离子注入处理。通过该处理,大部分离子穿过夹层11并累积于硅晶片10的上层部分(夹层11一侧的部分内),由此形成损伤层

12。对于离子注入处理的条件,例如,氢原子离子(h

)的剂量(注入量)优选在2.5

×

10

16

atom/cm2至5.0

×

10

16

atom/cm2之间。当剂量不足2.5

×

10

16

atom/cm2时,难以形成损伤层。当剂量超过5.0

×

10

16

atom/cm2时,随后的热处理可能会致使在经受这种离子注入的硅晶片内部产生被称为微腔的气泡并且使损伤层表面的粗糙度劣化,可能导致表面状态不适合于粘合。氢分子离子(h

2

)的剂量优选在1.25

×

10

16

atom/cm2至2.5

×

10

16

atom/cm2之间,由其可产生类似于氢原子离子的效果。

27.损伤层12的表面粗糙度例如可以用算术平均粗糙度ra表示(jis b 0601:2013)。可通过原子力显微镜(afm)进行观察和测量。算术平均粗糙度ra例如优选为0.3nm或更小。rms也称为jis b 0601:2013规定的“均方根粗糙度rq”,例如,优选为0.3nm或更小。rmax表示jis b 0601:2013中规定的最大高度,例如优选为3.0nm或更小。

28.关于离子的加速能,氢原子离子(h

)的加速能优选为25至200kev,氢分子离子(h

2

)的加速能优选为50至400kev。通过调节加速能可以改变离子注入的深度。优选将损伤层12的厚度调节至100nm至500nm。

29.在步骤(e)中,对形成有损伤层12的硅晶片10进行热处理。这使得能够通过离子注入处理使硅晶片10中保留的大量多余离子向外扩散。热处理温度优选为400℃或更高。这确保了多余离子的向外扩散,同时能够形成损伤层12a。热处理温度的上限不受特别限制,但优选例如为800℃或更低。

30.在步骤(f)中,经由夹层11和损伤层12a将硅晶片10和第二晶片20彼此粘合以获得接合体30。在粘合之前,使硅晶片10和第二晶片20中的一者或两者的待粘合表面经受表面活化处理。作为表面活化处理,只要可活化待粘合表面即可,不受特别限制。实例包括等离子体活化处理、真空离子束法、臭氧水处理法以及uv臭氧处理法等。作为表面活化处理的气氛,可以单独或组合使用惰性气体(例如氮气或氩气)和氧气。

31.通过经由夹层11和损伤层12a将硅晶片10和第二晶片20彼此粘合而获得的接合体30可经受热处理。通过这种处理,接合体增加了接合强度。

32.在步骤(g)中,将接合体30中的第二晶片20减薄成单晶硅薄膜或氧化物单晶薄膜20a。结果,可获得在硅晶片10上经由损伤层12a及夹层11而形成有单晶硅薄膜或氧化物单晶薄膜20a的复合基板40。单晶硅薄膜或氧化物单晶薄膜20a的厚度例如优选为0.1至30μm。作为第二晶片20的减薄方法,例如可使用磨削或抛光或者也可使用smart-cut法(智能剥离法)。

33.具体而言,smart-cut法是一种执行如下步骤的方法:预先对第二晶片20的待粘合表面进行离子注入处理,从而在第二晶片20的内部形成离子注入层,从接合体30剥离第二晶片20的剩余部分而留下离子注入层作为单晶硅薄膜或氧化物单晶薄膜20a。可通过使用楔形刀片(图中未示出)施加机械冲击或者施加规定的热处理来实现剥离。

34.在如此获得的复合基板40中,即使在热处理之后也不会在其中产生被称为微腔的气泡,在损伤层12a的表面粗糙度未见劣化,与单晶硅薄膜或氧化物单晶薄膜20a适当地彼此粘合,并且硅晶片20中的多余离子也充分地向外扩散,所以即使经过粘合后的热处理或长时间的使用等,也可以防止膜剥离的发生。实施例

35.下面针对实施例和比较例进行说明,但本发明并不局限于这些示例。

36.实施例1在直径为150mm的硅晶片的表面上,通过热氧化法(在1000℃的水蒸气气氛中)形成500nm的热氧化膜(sio2膜)。通过10

×

10μm原子力显微镜(afm)观察,此时热氧化膜的表面粗糙度ra=0.16nm。以3.6

×

10

16

/cm2的剂量(注入量)和83kev的加速能对所得晶片进行氢离子(h

)离子注入处理。作为afm观察的结果,此时热氧化膜的表面粗糙度也为ra=0.16nm。针对通过热氧化获得的热氧化硅晶片单体在氮气气氛中在500℃的温度下进行热处理12小时。

37.作为afm观察的结果,此时热氧化膜的表面粗糙度也为ra=0.16nm,rms为0.20nm,rmax为1.92nm。此时的热氧化膜表面的afm图像如图3所示。图4中示出了此时的晶片截面的透射电子显微镜(tem)图像。如图4所示,确认到在硅晶片上层中形成有损伤层61,但可知没有使热氧化膜与硅之间的界面62变粗糙。

38.实施例2在直径为150mm的第一硅晶片的表面上,通过热氧化法(在1000℃的水蒸气气氛中)形成500nm热氧化膜(sio2膜)。通过10

×

10μmafm观察,此时热氧化膜的表面粗糙度ra=0.16nm。以表1所示的剂量范围1.5

×

10

16

/cm2至5.5

×

10

16

/cm2、加速能83kev针对通过热氧化获得的热氧化硅晶片进行氢离子(h

)离子注入处理。在表1所示的300至800℃的各温度下对这些施加离子注入后获得的热氧化物硅晶片单体进行热处理。(在各种情况下保留时间均为6小时)。

39.接下来,分别将所得晶片与第二硅晶片在表面活化处理之后彼此粘合以获得接合体。将所得接合体在250℃下热处理24小时后通过磨削或抛光将第二硅晶片减薄至10μm厚度以获得复合基板。将如此获得的复合基板在900℃下热处理10分钟。选择900℃作为制造硅器件时的最高温度。调查研究了各试验例中是否存在膜剥离现象。此外,通过对各试验例的截面(剖面)进行tem观察,调查研究了热氧化膜中损伤层的形成。关于有无损伤层的形成以及有无膜剥离的发生的结果如表1所示。应注意,表1中纵向列出的数值是注入氢离子的剂量(

×

10

16

/cm2)、横向列出的数值是针对粘合前已完成离子注入的硅晶片实施的热处理温度(℃)。

40.表1

41.如表1所示,在形成损伤层(载流子陷阱层)的试验例中显示没有发生膜剥离的结果的试验例的剂量在2.5

×

10

16

/cm2至5.0

×

10

16

/cm2的范围。图2中示出具有损伤层并且产生了外周和内部剥离的试验例的晶片表面的显微镜照片。如图2所示,在硅晶片表面50上产生多个膜剥离51。

42.实施例3除了使用钽酸锂(lt)晶片替代第二硅晶片、通过磨削或抛光使lt晶片减薄至5μm的厚度并且在表2所示的300℃至600℃的范围的各温度下对已施行离子注入的热氧化硅晶片进行热处理(600℃是从lt的居里温度开始的上限温度)以外,与实施例2同样地制备了复合基板。将所得复合基板在300℃下处理30分钟,以调查研究有无损伤层的形成以及有无膜剥离发生。其结果如表2所示。表2中纵向列出的数值是注入氢离子的剂量(

×

10

16

/cm2)、横向列出的数值是针对粘合前已完成离子注入的硅晶片实施的热处理温度(℃)。

43.表2

44.如表2所示,在形成损伤层(载流子陷阱层)的试验例中显示没有发生膜剥离的结果的试验例的剂量在2.5

×

10

16

/cm2至5.0

×

10

16

/cm2的范围。

45.实施例4除了使用cvd法和pvd法各种方法替代热氧化法在硅晶片上形成氧化硅膜并且通过抛光使表面平滑化以外,与实施例2和3同样地制备了复合基板,并且调查研究了有无损伤层的形成以及有无膜剥离发生。其结果与实施例2和3的结果相似,表明本发明的效果不依赖于氧化膜的形成方法。

46.实施例5除了使用真空离子束法、臭氧水处理法和uv臭氧处理法等各种处理法来替代等离子体活化处理对待粘合表面进行活化处理以外,与实施例2和3同样地制备了复合基板,并且调查研究了有无损伤层的形成以及有无膜剥离发生。其结果,未见由活化处理的不同引起的显著差异。因此,可知本发明的效果不强烈依赖于活化处理的方法。此外,对任一个晶片施加活化处理的情况与对两个晶片都施加活化处理的情况进行了试验,结果没有大的差异。

47.实施例6除了使用h

2

替代h

作为待注入离子并且使剂量减少一半且使加速能加倍(成为2倍)以外,与实施例2和实施例3同样地制备了复合基板,并且调查研究了有无损伤层的形成以及有无膜剥离发生。其结果,得到与实施例2和3同样的结果。

48.实施例7除了使用sion、sin、al2o3、tio2、ta2o5、nb2o5、y2o3或zro2各种材料替代热氧化膜(sio2)而形成夹层以外,与实施例2和3同样地制备了复合基板,并且调查研究了有无损伤层的形成以及有无膜剥离发生。其结果,得到与实施例2和3同样的结果。

49.实施例8除了将通过预先在硅晶片或lt晶片的待粘合表面上注入氢离子并且在粘合后的

接合体中沿注入界面进行剥离来减薄硅晶片或lt晶片的操作替代通过磨削或抛光接合体来减薄其硅晶片或lt晶片的操作以外,与实施例2和3同样地制备了复合基板,并且调查研究了有无损伤层的形成以及有无膜剥离发生。其结果,得到与实施例2和3同样的结果。附图标记的说明

50.10:硅晶片11:夹层12:损伤层20:单晶硅晶片或氧化物单晶晶片20a:单晶硅薄膜或氧化物单晶薄膜30:接合体40:复合基板

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。