1.本发明是有关一种治具系统,且尤其是有关一种用于测试待测电路板的测试治具系统及其方法。

背景技术:

2.随着科技逐渐发展,人们对于电子产品的需求也随之增加,而为了满足电子产品各种功能的需求,使用于电子产品的电路板也趋向复杂化,例如系统级封装(system in package;sip)模块芯片。因此,电路板在使用于电子产品之前,需要进行在线测试等多种测试,以确保电路板可正常运行。相关业者发展一测试治具,将待测电路板放置于治具内,再通过上盖盖合形成封闭的测试空间,并以治具的测试探针供电并测试待测电路板。然而,现有的测试治具是直接通过一控制板电路提供或停止测试治具的电源,当在测试过程中,若上盖不正常开合,控制板电路并无法停止供电至待测电路板,而可能因测试治具上的电力造成的突波损害待测电路板,增加测试上的风险,甚至损毁电路板而导致成本上的损失。

3.有鉴于此,一种可提升供电安全性的测试治具系统及其方法,仍是目前相关业者共同努力的目标。

技术实现要素:

4.依据本发明的一实施方式提供一种测试治具系统,用以测试一待测电路板,且包含一治具、一治具电路板、一处理器以及一断电感测组件。治具包含一基座、一上盖、一底部及多个测试探针。基座包含一测试空间,测试空间供容设待测电路板。上盖枢接于基座的上端,其中上盖用以盖合于基座上以闭合测试空间。底部连接于基座的下端。测试探针设置于底部,且各测试探针的一端凸入于测试空间中。治具电路板设置于底部的下方。处理器电性连接治具电路板。断电感测组件包含一断电感测元件及一导电元件。断电感测元件设置于基座,且电性连接处理器。导电元件设置于上盖朝向基座的一侧。其中,待测电路板放置于测试探针上,上盖盖合基座并下压待测电路板,使得待测电路板接触测试探针,当上盖处于一正常盖合状态时,导电元件接触断电感测元件,断电感测元件产生一通电信号,处理器感应通电信号并使处理器供电至治具电路板,并通过测试探针测试待测电路板;当上盖处于一非盖合状态,导电元件未接触断电感测元件,处理器未感应通电信号而停止供电至治具电路板,无法通过测试探针测试待测电路板。

5.依据本发明的另一实施方式提供一种测试治具方法,用以测试一待测电路板,且包含一待测电路板放置步骤、一上盖盖合步骤、一盖合通电步骤以及一盖合异常断电步骤。待测电路板放置步骤中,是将待测电路板放置于一测试治具系统的一治具的多个测试探针上。上盖盖合步骤中,是将治具的一上盖盖合于治具的一基座,使得待测电路板受压接触测试探针。盖合通电步骤中,是感测上盖处于一正常盖合状态或一非盖合状态,其中当上盖正常盖合于基座,测试治具系统的一断电感测组件传送一通电信号至测试治具系统的一处理器,处理器判断上盖处于正常盖合状态,允许通过测试探针测试待测电路板。盖合异常断电

步骤中,当上盖盖合异常使通电信号断开时,处理器判断上盖处于非盖合状态,停止通过测试探针测试待测电路板。

附图说明

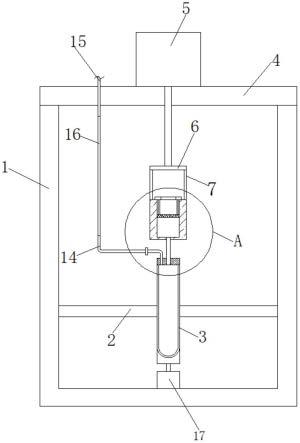

6.图1绘示依照本发明一实施例的测试治具系统的立体示意图;

7.图2绘示依照图1实施例的上盖的局部示意图;

8.图3绘示依照图1实施例的基座的局部示意图;

9.图4绘示依照图1实施例的待测电路板放置于测试空间的示意图;

10.图5绘示依照本发明另一实施例的测试治具方法的步骤方块图;

11.图6绘示依照图5实施例中的测试治具系统测试待测电路板的流程示意图;以及

12.图7绘示依照图5实施例的测试治具方法的步骤流程图。

13.其中,附图标记说明如下:

14.100:测试治具系统

15.110:治具

16.111,211:基座

17.112,212:上盖

18.1121:抵顶板

19.1122:旋钮

20.113:底部

21.1131:限位槽

22.114,214:测试探针

23.115,215:凹槽

24.120:治具电路板

25.130:处理器

26.131:断电感测模块

27.140:断电感测组件

28.141,241:断电感测元件

29.1411:接地探针

30.1412:信号探针

31.142,242:导电元件

32.1421:退镀区

33.1422:导电区

34.s1:测试空间

35.t1:待测电路板

36.s100:测试治具方法

37.s110:待测电路板放置步骤

38.s120:上盖盖合步骤

39.s130:盖合通电步骤

40.s140:盖合异常断电步骤

41.s210,s220,s230,s240,s251,s252:步骤

具体实施方式

42.请参照图1、图2、图3及图4,其中图1绘示依照本发明一实施例的测试治具系统100的立体示意图,图2绘示依照图1实施例的上盖112的局部示意图,图3绘示依照图1实施例的基座111的局部示意图,图4绘示依照图1实施例的待测电路板t1放置于测试空间s1的示意图。如图1至图4所示,测试治具系统100用以测试一待测电路板t1,且包含一治具110、一治具电路板120、一处理器130以及一断电感测组件140。治具110包含一基座111、一上盖112、一底部113及多个测试探针114。基座111包含一测试空间s1,测试空间s1供容设待测电路板t1。上盖112枢接于基座111的上端,其中上盖112用以盖合于基座111上以闭合测试空间s1。底部113连接于基座111的下端。测试探针114设置于底部113,且各测试探针114的一端凸入于测试空间s1中。治具电路板120设置于底部113的下方。处理器130电性连接治具电路板120。断电感测组件140包含一断电感测元件141及一导电元件142。断电感测元件141设置于基座111,且电性连接处理器130。导电元件142设置于上盖112朝向基座111的一侧。其中,待测电路板t1放置于测试探针114上,上盖112盖合基座111并下压待测电路板t1,使得待测电路板t1接触测试探针114,当上盖112处于一正常盖合状态时,导电元件142接触断电感测元件141,断电感测元件141产生一通电信号,处理器130感应通电信号并使处理器130供电至治具电路板120,并通过测试探针114测试待测电路板t1;当上盖112处于一非盖合状态,导电元件142未接触断电感测元件141,处理器130未感应通电信号而停止供电至治具电路板120,无法通过测试探针114测试待测电路板t1。

43.通过断电感测组件140的配置,在测试治具系统100测试待测电路板t1期间因外力、故障或不当操作等因素,导致上盖112未完全闭合或开启测试空间s1时,断电感测元件141与导电元件142不接触,使得处理器130未感应通电信号,进而立即停止供电及测试待测电路板t1,借以避免治具电路板120供给的电力造成突波损害待测电路板t1。借此,可提升供电的安全性。

44.如图1及图2所示,上盖112可包含一抵顶板1121及一旋钮1122。抵顶板1121位于上盖112朝向基座111的一侧,且用以抵顶待测电路板t1于测试探针114。旋钮1122位于上盖112远离基座111的一侧并连接于抵顶板1121,且用以受力旋转,进而驱动抵顶板1121下压待测电路板t1,使得待测电路板t1接触测试探针114通过抵顶板1121及旋钮1122的配置,可进一步增加待测电路板t1抵顶测试探针114的力道,避免待测电路板t1在测试过程中脱离测试探针114。借此,可进一步提升待测电路板t1测试的稳定度。

45.再者,导电元件142可包含一退镀区1421及一导电区1422。退镀区1421为绝缘材料制成,导电区1422凸出于退镀区1421且具有导电能力。断电感测元件141可包含一接地探针1411及一信号探针1412。基座111可更包含一凹槽115,其毗邻于测试空间s1,断电感测元件141部分露出于凹槽115内,且凹槽115用以供导电元件142插入。进一步来说,接地探针1411及信号探针1412是插设于基座111且各包含一端露出于凹槽115内,且当上盖112盖合测试空间s1时,导电元件142的导电区1422插入凹槽115并与接地探针1411及信号探针1412接触,使得接地探针1411、信号探针1412与导电区1422可形成通路,进而传输通电信号至处理器130,借以供电并测试待测电路板t1。借此,可进一步提升供电的稳定度。并且通过接地探

针1411及信号探针1412接触导电区1422,可简化断电感测组件140的结构,降低断电感测组件140的制造成本。

46.处理器130可包含一断电感测模块131,其电性连接接地探针1411及信号探针1412并接收通电信号。具体而言,处理器130可以是一微处理器控制电路板,断电感测模块131可以是一侦测引脚或一mosfet开关,但本发明不以此为限。当接地探针1411、信号探针1412与导电区1422接触,断电感测模块131提供一准位电压至处理器130,使得处理器130判断上盖112处于正常盖合状态,进而供电至治具电路板120,并且治具电路板120具有集成电路(integrated circuit;ic)通用型的输入输出(general-purpose input/output;gpio)的准位电压,gpio的准位电压提供至治具电路板120的ic上,再由治具电路板120的ic发出测试信号至各测试探针114,借以供电并测试待测电路板t1;当接地探针1411、信号探针1412与导电区1422未接触,处理器130接收不到断电感测模块131的准位电压,处理器130停止供电至治具电路板120,使得治具电路板120无法供电至待测电路板t1,并停止测试。

47.如图3及图4所示,底部113可具有一限位槽1131,其用以限位待测电路板t1于一限位位置。具体而言,限位槽1131具有多个穿孔,其用以供测试探针114穿过并凸入于测试空间s1中,待测电路板t1可放置于限位槽1131上,进而将待测电路板t1限位于限位位置,借以避免当抵顶板1121下压待测电路板t1时,待测电路板t1偏移位置的可能。借此,可提升测试时的稳定度。

48.请参照图5及图6,其中图5绘示依照本发明另一实施例的测试治具方法s100的步骤方块图,图6绘示依照图5实施例中的测试治具系统测试待测电路板t1的流程示意图。值得说明的是,图6实施例中,测试治具系统可以是图1实施例的测试治具系统100,在此不赘述其细节。如图5及图6所示,测试治具方法s100用以测试一待测电路板t1,且包含一待测电路板放置步骤s110、一上盖盖合步骤s120、一盖合通电步骤s130以及一盖合异常断电步骤s140。待测电路板放置步骤s110是将待测电路板t1放置于一测试治具系统的一治具的多个测试探针214上。上盖盖合步骤s120是将治具的一上盖212盖合于治具的一基座211,使得待测电路板t1受压接触测试探针214。盖合通电步骤s130是感测上盖212处于一正常盖合状态或一非盖合状态,其中当上盖212正常盖合于基座211,测试治具系统的一断电感测组件传送一通电信号至测试治具系统的一处理器,处理器判断上盖212处于正常盖合状态,允许通过测试探针214测试待测电路板t1。盖合异常断电步骤s140中,当上盖212盖合异常使通电信号断开时,处理器判断上盖212处于该非盖合状态,停止通过测试探针214测试待测电路板t1。

49.通过断电感测组件感测上盖是否正常盖合,可避免在测试待测电路板t1过程中,治具因外力或其他操作因素不当开合上盖212,使得测试探针214提供至待测电路板t1的电力产生突波,损害待测电路板t1。

50.具体而言,待测电路板放置步骤s110中,可将待测电路板t1限位于基座211的一限位位置。

51.再者,盖合通电步骤s130中,可通过位于上盖212的断电感测组件的一导电元件242是否接触位于基座211的断电感测组件的一断电感测元件241判断上盖212处于正常盖合状态或非盖合状态。进一步来说,盖合通电步骤s130中,导电元件242插入基座211的一凹槽215以接触断电感测元件241。

52.请配合参照图7,其绘示依照图5实施例的测试治具方法s100的步骤流程图。如图7所示,测试治具方法s100可包含步骤s210、s220、s230、s240、s251、s252。步骤s210中,放置待测电路板t1至基座211的测试空间s1,并执行步骤s220。步骤s220中,将盖合上盖212于基座211上,并执行步骤s230。步骤s230中,上盖212下压使得待测电路板t1接触测试探针214,并执行步骤s240。步骤s240中,判断导电元件242是否接触断电感测元件241,当导电元件242接触断电感测元件241,执行步骤s251;当导电元件242未接触断电感测元件241,执行步骤s252。步骤s251中,可供电给治具电路板,并对待测电路板t1进行测试。步骤s252中,停止供电给治具电路板,并停止对待测电路板t1进行测试。

53.综合上述,本发明具有下列优点:其一,通过断电感测元件是否接触导电元件,可简单判断上盖是否正常盖合,借以提升供电的安全性。其二,通过将导电元件插入于凹槽,可提升导电元件接触断电感测元件的稳定度。其三,通过接地探针、信号探针及导电区的配置,可简化断电感测组件的结构。

54.虽然本发明已以实施方式公开如上,然其并非用以限定本发明,任何熟习此技艺者,在不脱离本发明的精神和范围内,当可作各种的更动与润饰,因此本发明的保护范围当视后附的权利要求书所界定者为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。