高压ldmos器件及其制备方法

技术领域

1.本发明涉及半导体集成电路制造领域,特别是涉及一种高压ldmos器件及其制备方法。

背景技术:

2.在同一芯片上同时制备双极型晶体管、cmos器件和dmos器件的工艺为bcd工艺。而开关型nldmos(snldmos)器件是bcd工艺中常用的器件,其重要参数包括击穿电压(bv)、特征导通电阻(rsp)、开态击穿电压(onbv)及安全工作区(soa),其中,安全工作区包括电安全工作区(esoa)及瞬态脉冲安全工作区(tlp soa)。由于安全工作区(soa)是功率器件能够安全、可靠工作的电流和电压范围,若超过该范围有可能会使得器件受到毁坏,因此,在设计nldmos器件时,安全工作区也是必须要考虑的重要参数。

3.图1示出了现有的一种开关型高压nldmos器件,所述器件中体区2形成于漂移区1内。该器件与低压ldmos器件共用体区2,若通过增加体区2浓度的方式来提升高压ldmos器件的onbv以提升该器件的安全工作区,会使得低压ldmos器件的特性受到影响。

技术实现要素:

4.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种高压ldmos器件及其制备方法,用于解决现有的开关型高压ldmos器件的安全工作区受限的问题。

5.为实现上述目的及其他相关目的,本发明提供一种高压ldmos器件,所述器件包括;

6.半导体衬底,且所述半导体衬底的表层中形成有掩埋层;

7.外延层,形成于所述掩埋层的表面;

8.两个漂移区,包括第一漂移区及第二漂移区,形成于所述外延层内且间隔设置;

9.掺杂区,形成于所述第一漂移区及所述第二漂移区之间,且其离子掺杂类型与所述漂移区的离子掺杂类型不同;

10.体区,形成于所述掺杂区内;

11.隔离区,形成于所述外延层内,且形成于所述掩埋层的表面,并位于所述漂移区及所述掺杂区的下方。

12.可选地,所述器件包括两个第一阱区,分别形成于所述第一漂移区远离所述掺杂区的一侧及所述第二漂移区远离所述掺杂区的一侧,且均位于所述隔离区的表面。

13.可选地,所述器件包括高压氧化层,所述高压氧化层包括第一高压氧化层及第二高压氧化层,所述第一高压氧化层形成于所述第一漂移区的表面,所述第二高压氧化层形成于所述第二漂移区的表面。

14.可选地,所述器件包括栅极结构,所述栅极结构包括第一栅极结构及第二栅极结构,所述第一栅极结构的一侧延伸至部分所述第一高压氧化层的表面,另一侧延伸至部分所述掺杂区的表面;所述第二栅极结构的一侧延伸至部分所述第二高压氧化层的表面,另

一侧延伸至部分所述掺杂区的表面。

15.可选地,所述器件包括源区及漏区,所述源区包括第一源区及第二源区,均形成于所述体区表层中,且所述第一源区与所述第二源区之间具有间隔;所述漏区包括第一漏区及第二漏区,所述第一漏区形成于所述第一漂移区表层中且位于所述第一高压氧化层远离所述第一栅极结构的一侧,所述第二漏区形成于所述第二漂移区表层中且位于所述第二高压氧化层远离所述第二栅极结构的一侧。

16.可选地,所述器件还包括体区引出区,形成于所述第一源区及所述第二源区之间。

17.相应地,本发明还提供了一种高压ldmos器件的制备方法,所述方法包括:

18.提供一形成有掩埋层的半导体衬底;

19.于所述掩埋层的表面形成外延层;

20.于所述外延层内形成两个间隔设置的漂移区,其中,所述漂移区包括第一漂移区及第二漂移区;

21.于所述第一漂移区及所述第二漂移区之间形成掺杂区;

22.于所述掺杂区内形成体区;

23.于所述外延层内形成隔离区,且所述隔离区形成于所述掩埋层的表面,并位于所述漂移区及所述掺杂区的下方。

24.可选地,所述方法包括于所述外延层内形成两个第一阱区的步骤。

25.可选地,所述方法包括形成高压氧化层的步骤,其中,所述高压氧化层包括第一高压氧化层及第二高压氧化层。

26.可选地,所述方法包括形成栅极结构的步骤,其中,所述栅极结构包括第一栅极结构及第二栅极结构。

27.可选地,所述方法还包括形成源区及漏区的步骤。

28.如上所述,本发明的高压ldmos器件及其制备方法,通过于外延层中形成两个间隔设置的漂移区,并于两个漂移区之间形成掺杂区,之后再将体区形成于掺杂区内的方式来增加体区的浓度,减小体区电阻,从而减小体区电阻因电流流过产生的电位差,增大开启电压,进而增强所述高压ldmos器件的安全工作电压特性;本发明的所述高压ldmos器件与低压ldmos器件共用体区,而通过上述方式来增加体区浓度不会影响到低压ldmos器件的特性;而且,通过上述方式增加体区的浓度,能够提升器件的esd自保护能力;所述掺杂区与其它器件的掺杂区(比如cmos器件的阱区)可同步形成,而不需要增加新的掩膜版,从而也就不会增加成本。

附图说明

29.图1显示为现有的高压ldmos器件的剖面结构示意图。

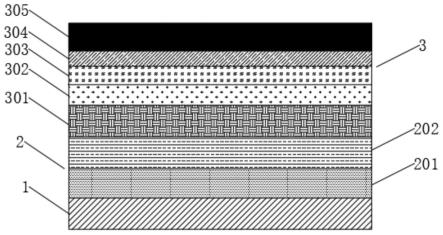

30.图2显示为本发明的高压ldmos器件的剖面结构示意图。

31.元件标号说明

32.10:半导体衬底;11:掩埋层;20:外延层;1、21:漂移区;21a:第一漂移区;21b:第二漂移区;22:隔离区;30:掺杂区;2、31:体区;32:体区引出区;40:第一阱区;50:高压氧化层;51:第一高压氧化层;52:第二高压氧化层;60:栅极结构;61:第一栅极结构;62:第二栅极结构;70:源区;71:第一源区;72:第二源区;80:漏区;81:第一漏区;82:第二漏区;90:第二阱

区;91:掩埋引出区;100:浅沟槽隔离结构

具体实施方式

33.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

34.请参阅图1至图2。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,虽图示中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的形态、数量及比例可为一种随意的改变,且其组件布局形态也可能更为复杂。

35.如图2所示,本实施例提供了一种高压ldmos器件,所述器件包括:

36.半导体衬底10,且所述半导体衬底10的表层中形成有掩埋层11;

37.外延层20,形成于所述掩埋层11的表面;

38.两个漂移区21,包括第一漂移区21a及第二漂移区21b,形成于所述外延层20内且间隔设置;

39.掺杂区30,形成于所述第一漂移区21a及所述第二漂移区21b之间,且其离子掺杂类型与所述漂移区21的离子掺杂类型不同;

40.体区31,形成于所述掺杂区30内;

41.隔离区22,形成于所述外延层20内,且形成于所述掩埋层11的表面,并位于所述漂移区21及所述掺杂区30的下方。

42.本实施例中,所述高压ldmos器件所适用的电压包括30~40v、60v、100v或800v。所述半导体衬底10包括但不限于硅衬底。所述掩埋层11通过离子注入工艺形成于所述半导体衬底10的表层中,且其离子掺杂类型为n型。所述第一漂移区21a、所述第二漂移区21b、所述掺杂区30、所述体区31及所述隔离区22均通过离子注入工艺而形成,且所述第一漂移区21a及所述第二漂移区21b具有相同的离子掺杂类型,均为n型,所述掺杂区30、所述体区31及所述隔离区22的离子掺杂类型相同,均为p型。

43.本实施例中,所述掺杂区30与所述第一漂移区21a及所述第二漂移区21b相贴设置,且所述掺杂区30、所述第一漂移区21a及所述第二漂移区21b形成于所述隔离区22的表面。

44.具体的,所述器件包括两个第一阱区40,分别形成于所述第一漂移区21a远离所述掺杂区30的一侧及所述第二漂移区21b远离所述掺杂区30的一侧,且均位于所述隔离区22的表面。

45.本实施例中,所述第一阱区40通过离子注入工艺形成于所述第一漂移区21a及所述第二漂移区21b远离所述掺杂区30的一侧,且其离子掺杂类型为p型。而且,所述第一阱区40的离子掺杂浓度与所述掺杂区30的离子掺杂浓度可以相同也可以不同,可选地,本实施例中,所述第一阱区40的离子掺杂浓度与所述掺杂区30的离子掺杂浓度相同。

46.具体的,所述器件包括高压氧化层50,所述高压氧化层50包括第一高压氧化层51及第二高压氧化层52,所述第一高压氧化层51形成于所述第一漂移区21a的表面,所述第二

高压氧化层52形成于所述第二漂移区21b的表面。

47.本实施例中,所述高压氧化层50的存在使得所述高压ldmos器件具有更高的耐压性能。所述高压氧化层50的材质包括但不限于氧化硅。

48.具体的,所述器件包括栅极结构60,所述栅极结构60包括第一栅极结构61及第二栅极结构62,所述第一栅极结构61的一侧延伸至部分所述第一高压氧化层51的表面,另一侧延伸至部分所述掺杂区30的表面;所述第二栅极结构62的一侧延伸至部分所述第二高压氧化层52的表面,另一侧延伸至部分所述掺杂区30的表面。

49.如图2所示,本实施例中,所述第一栅极结构61与所述第二栅极结构62之间具有间隔,且二者均包括栅氧化层及形成于所述栅氧化层表面的多晶硅层。

50.具体的,所述器件包括源区70及漏区80,所述源区70包括第一源区71及第二源区72,均形成于所述体区31表层中,且所述第一源区71与所述第二源区72之间具有间隔;所述漏区80包括第一漏区81及第二漏区82,所述第一漏区81形成于所述第一漂移区21a的表层中且位于所述第一高压氧化层51远离所述第一栅极结构61的一侧,所述第二漏区82形成于所述第二漂移区21b表层中且位于所述第二高压氧化层52远离所述第二栅极结构62的一侧。

51.本实施例中,所述第一源区71与所述第一栅极结构61相贴设置,所述第二源区72与所述第二栅极结构62相贴设置。所述第一源区71及所述第二源区72均是通过离子注入工艺形成于所述体区31表层中,且其掺杂类型为n型。所述第一漏区81与所述第一高压氧化层51相贴设置,并通过离子注入工艺形成于所述第一漂移区21a的表层中;所述第二漏区82与所述第二高压氧化层52相贴设置,并通过离子注入工艺形成于所述第二漂移区21b的表层中,而且,所述第一漏区81及所述第二漏区82的离子掺杂类型均为n型。

52.具体的,所述器件还包括体区引出区32,形成于所述第一源区71及所述第二源区72之间。本实施例中,所述体区引出区32与所述第一源区71及所述第二源区72相贴设置,并通过离子注入工艺形成于所述第一源区71及所述第二源区72之间,且其离子掺杂类型为p型。

53.作为示例的,所述高压ldmos器件还包括两个第二阱区90,所述第二阱区90形成于所述掩埋层11的表面,且分别位于两个所述第一阱区40远离所述漂移区21的一侧。本实施例中,所述第二阱区90通过离子注入工艺形成于所述外延层20内,且其离子掺杂类型为n型。进一步地,所述第二阱区90的表层中通过离子注入工艺形成有所述掩埋层11的掩埋引出区91,且所述掩埋引出区91的离子掺杂类型为n型。

54.作为示例的,所述高压ldmos器件还包括浅沟槽隔离结构100,所述浅沟槽隔离结构100形成于所述第一阱区40的上方并向两侧延伸至部分所述第二阱区90内及部分所述漂移区21内,及形成于所述掩埋引出区91远离所述漂移区21的一侧。

55.相应地,本实施例还提供了一种高压ldmos器件的制备方法,所述方法包括:

56.提供一形成有掩埋层11的半导体衬底10;

57.于所述掩埋层11的表面形成外延层20;

58.于所述外延层20内形成两个间隔设置的漂移区21,所述漂移区21包括第一漂移区21a及第二漂移区21b;

59.于所述第一漂移区21a及所述第二漂移区21b之间形成掺杂区30;

60.于所述掺杂区30内形成体区31;

61.于所述外延层20内形成隔离区22,且所述隔离区22形成于所述掩埋层11的表面,并位于所述漂移区21及所述掺杂区30的下方。

62.具体的,所述方法包括于所述外延层20内形成两个第一阱区40的步骤。

63.具体的,所述方法包括于所述漂移区21的表面高压氧化层50的步骤,其中,所述高压氧化层50包括第一高压氧化层51及第二高压氧化层52。本实施例中,所述第一高压氧化层51形成于所述第一漂移区21a的表面,所述第二高压氧化层52形成于所述第二漂移区21b的表面。

64.具体的,所述方法包括形成栅极结构60的步骤,所述栅极结构60包括第一栅极结构61及第二栅极结构62。本实施例中,在形成所述体区31之前形成所述第一栅极结构61及所述第二栅极结构62。具体制备方法包括:利用第一掩膜版形成第一掩膜时,所述第一掩膜保护形成于所述掺杂区30表面的栅氧化层及多晶硅层,因此,在进行刻蚀工艺形成所述第一栅极结构61及所述第二栅极结构62时,形成于所述掺杂区30表面的栅氧化层及多晶硅层不被刻蚀掉,也即是所述第一光栅结构61及所述第二光栅结构62在所述掺杂区30的表面连接,之后,利用第二掩膜版形成第二掩膜,所述第二掩膜作为进行离子注入形成所述体区31的掩膜层,而在进行离子注入形成所述体区31之前,利用所述第二掩膜对形成于所述掺杂区30表面的栅氧化层及多晶硅层进行刻蚀。通过上述方式可缩小热过程。

65.具体的,所述方法还包括形成源区70及漏区80的步骤。

66.作为示例的,所述方法还包括形成两个第二阱区90及对应数目的掩埋引出区91的步骤,其中,所述掩埋引出区91通过离子注入工艺形成于所述第二阱区90的表层中。

67.作为示例的,所述方法还包括形成浅沟槽隔离结构100的步骤。

68.综上所述,本发明的高压ldmos器件及其制备方法,通过于外延层中形成两个间隔设置的漂移区,并于两个漂移区之间形成掺杂区,之后再将体区形成于掺杂区内的方式来增加体区的浓度,减小体区电阻,从而减小体区电阻因电流流过产生的电位差,增大开启电压,进而增强所述高压ldmos器件的安全工作电压特性;本发明的所述高压ldmos器件与低压ldmos器件共用体区,而通过上述方式来增加体区浓度不会影响到低压ldmos器件的特性;而且,通过上述方式增加体区的浓度,能够提升器件的esd自保护能力;所述掺杂区与其它器件的掺杂区(比如cmos器件的阱区)可同步形成,而不需要增加新的掩膜版,从而也就不会增加成本。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

69.上述实施例仅为本发明的优选实施例,而不用于限制本发明。对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。