1.本发明涉及半导体技术领域,具体涉及一种全局栅和局域栅协同调控的神经突触器件及其制备方法。

背景技术:

2.传统的计算机均基于冯诺依曼式计算架构,尽管可以应对大部分的计算任务,但是对于数据庞大的计算需求仍难以满足。超级计算机等设备被提出用以解决大数据计算的问题,然而占地面积大、成本高、操作专业性强、功耗巨大等问题限制了其推广与应用。因此,需要另寻更为高效的计算设备实现大数据的计算任务。神经形态计算作为一种新型计算模式,可以从根本上解决传统计算机面临的存储与计算单元分离的问题,避免频繁的数据传输与高密度集成带来的成本剧增问题,具有极大的发展潜力。

3.神经突触器件作为神经形态计算的基本功能单元,可以模仿生物突触前端到后端的信号传递,在权重更迭计算等方面扮演着关键角色。然而,传统的神经突触器件仅由突触前端和突触后端组成,难以满足需要不同权重调制的神经形态计算需求以及复杂信息的处理,需要开发具有不同调制能力的新型多端突触器件。

4.硫化钼等二维材料是一类新型的半导体材料,不仅具有优异的迁移率、亚阈值摆幅、高开关比等特性,而且具有原子级厚度,在单个原子尺寸便可进行工作,使得晶体管的尺寸沿着摩尔定律路线进行微缩成为可能。将二维材料用于制备新型神经突触器件在灵活的栅极调控方面具有重要意义,特别是利用全局栅和局域栅的结合,可以极大程度地提高突触权重的特异性调控,具有结构简单、易控、功耗低等优点。

技术实现要素:

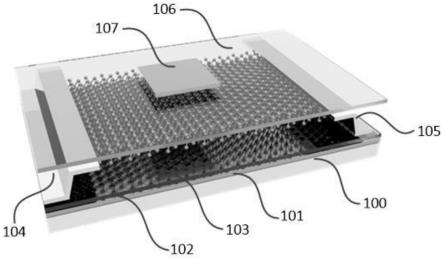

5.本发明公开一种全局栅和局域栅协同调控的神经突触器件,包括:衬底;背栅电极,形成在所述衬底上,铺满整个衬底,作为全局栅;背栅介质层,形成在所述背栅电极上;沟道层,其为二维半导体材料,形成在所述背栅介质层上;源电极和漏电极,形成在所述沟道层两侧;顶栅介质层,覆盖上述结构;顶栅电极,形成在所述顶栅介质层上,覆盖部分沟道区,作为局域栅,通过分别仅对局域栅施加正向电压,仅对全局栅施加正向电压,或对局域栅和全局栅共同施加正向电压,使得器件实现不等同权重的神经突触可塑性,获得特异性调制功能,实现多维复杂信息的传输。

6.本发明的全局栅和局域栅协同调控的神经突触器件中,优选为,所述背栅介质层或所述顶栅介质层为hfo2,zro2,tio2。

7.本发明的全局栅和局域栅协同调控的神经突触器件中,优选为,所述全局栅的长度为2μm~10μm;宽度为1μm~9μm。

8.本发明的全局栅和局域栅协同调控的神经突触器件中,优选为,所述二维半导体材料为mos2,ws2,res2,hfs2。

9.本发明的全局栅和局域栅协同调控的神经突触器件中,优选为,所述二维半导体

材料的厚度为1nm~10nm。

10.本发明还公开一种全局栅和局域栅协同调控的神经突触器件制备方法,包括以下步骤:在衬底上形成背栅电极,使其铺满整个衬底,作为全局栅;在所述背栅电极上形成背栅介质层;在所述背栅介质层上形成二维半导体材料,作为沟道层;在所述沟道层两侧形成源电极和漏电极;在上述结构上覆盖顶栅介质层;在所述顶栅介质层上形成顶栅电极,使之覆盖部分沟道区,作为局域栅,通过分别仅对局域栅施加正向电压,仅对全局栅施加正向电压,或对局域栅和全局栅共同施加正向电压,使得器件实现不等同权重的神经突触可塑性,获得特异性调制功能,实现多维复杂信息的传输。

11.本发明的全局栅和局域栅协同调控的神经突触器件制备方法中,优选为,所述背栅介质层或所述顶栅介质层为hfo2,zro2,tio2。

12.本发明的全局栅和局域栅协同调控的神经突触器件制备方法中,优选为,所述全局栅的长度为2μm~10μm;宽度为1μm~9μm。

13.本发明的全局栅和局域栅协同调控的神经突触器件制备方法中,优选为,所述二维半导体材料为mos2,ws2,res2,hfs2。

14.本发明的全局栅和局域栅协同调控的神经突触器件制备方法中,优选为,所述二维半导体材料的厚度为1nm~10nm。

15.有益效果:

16.(1)打破传统的计算机工作模式,解决冯诺依曼式计算架构存在的计算瓶颈问题,提供了一种高效的类脑计算电子器件,模拟生物神经突触功能模式,实现高效的神经网络计算。

17.(2)采用二维半导体材料作为沟道,解决传统硅基半导体材料面临的尺寸微缩导致的短沟道、漏电流、电子散射等问题,保证器件尺寸可以按照摩尔定律继续向亚纳米尺寸推进。

18.(3)通过设计全局栅和局域栅的结构,实现具有全局调控功能和局域调控功能的协同神经突触特性,对于实现具有特异性神经形态调控需求的多维神经网络计算具有重要意义。

附图说明

19.图1是全局栅和局域栅协同调控的神经突触器件制备方法的流程图。

20.图2~图7是全局栅和局域栅协同调控的神经突触器件制备方法各阶段的结构示意图。

21.如图8a~8c是全局栅和局域栅协同调控的神经突触器件运行示意图。

具体实施方式

22.为了使本发明的目的、技术方案及优点更加清楚明白,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

23.在本发明的描述中,需要说明的是,术语“上”、“下”、“垂直”“水平”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性。

24.此外,在下文中描述了本发明的许多特定的细节,例如器件的结构、材料、尺寸、处理工艺和技术,以便更清楚地理解本发明。但正如本领域的技术人员能够理解的那样,可以不按照这些特定的细节来实现本发明。除非在下文中特别指出,器件中的各个部分可以由本领域的技术人员公知的材料构成,或者可以采用将来开发的具有类似功能的材料。

25.图1是全局栅和局域栅协同调控的神经突触器件制备方法的流程图。如图1所示,全局栅和局域栅协同调控的神经突触器件制备方法包括以下步骤:

26.步骤s1,准备硅片作为衬底100,用于制备全局栅和局域栅协同调控的神经突触器件。衬底还可以是玻璃、sic等。

27.步骤s2,利用物理气相沉积在衬底100上形成背栅电极101,背栅电极101铺满整个衬底100,作为器件的全局栅,如图2所示。全局栅的材料优选为pt,还可以是au,al,pd等金属材料;厚度优选为70nm,范围可取50nm~150nm。

28.步骤s3,利用原子层沉积技术在背栅电极101上制备厚度为10nm~30nm的背栅介质层hfo2102,如图3所示。原子层沉积的温度为200℃~260℃。背栅介质层的材料还可以是zro2,tio2等氧化物绝缘层。

29.步骤s4,利用机械剥离法在背栅介质层102上制备1nm~10nm厚的mos2二维半导体材料作为沟道层103,如图4所示。沟道层的材料还可以是ws2,res2,hfs2等二维半导体材料。二维半导体材料的长度优选为10μm,范围可取5μm~30μm;宽度优选为5μm,范围可取2μm~20μm。

30.步骤s5,利用物理气相沉积在沟道层103两侧生长50nm~150nm厚的au层作为源电极104和漏电极105,如图5所示。源漏电极的材料还可以是pt,al,pd等金属材料。

31.步骤s6,利用原子层沉积技术在上述结构上制备厚度为10nm~30nm的顶栅介质层hfo2106,如图6所示。原子层沉积的温度优选为200℃~260℃。顶栅介质层的材料还可以是zro2,tio2等氧化物绝缘层。

32.步骤s7,利用物理气相沉积在顶栅介质层106上生长50nm~150nm厚的顶栅电极pt107,顶栅电极仅覆盖沟道的部分区域作为局域栅,如图7所示。顶栅电极的长度优选为5μm,范围可取2μm~10μm;宽度优选为2μm,范围可取1μm~9μm。顶栅电极的材料还可以是au,al,pd等金属材料。

33.如图7所示,全局栅和局域栅协同调控的神经突触器件包括:衬底100;背栅电极101,形成在衬底100上,铺满整个衬底,作为全局栅;背栅介质层102,形成在背栅电极101上;沟道层103,其为二维半导体材料,形成在背栅介质层102上;源电极104和漏电极105,形成在沟道层103两侧;顶栅介质层106,覆盖上述结构;顶栅电极107,形成在顶栅介质层106上,覆盖部分沟道区,作为局域栅。

34.如图8a~8c所示通过分别对位于顶部的局域栅107和位于底部的全局栅101施加正向电压,使得器件实现不等同权重的神经突触可塑性,获得特异性调制功能,实现多维复

杂信息的传输。其中,图8a中所示为仅对位于顶部的局域栅施加正向电压的示意图;图8b中所示为仅对位于底部的全局栅施加正向电压的示意图;图8c中所示为对位于顶部的局域栅和位于底部的全局栅施加正向电压的示意图。

35.以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。