1.本技术涉及芯片技术领域,特别是涉及从快时钟域到慢时钟域的同步处理电路、方法和芯片。

背景技术:

2.受疫情影响,全球汽车芯片告急,全球主要芯片供应商降低产能或关停工厂的事件陆续发生。而中国车市快速复苏,进一步推动了芯片需求增长。

3.随着对复杂功能汽车的需求增加,高性能、高安全性芯片需求激增,而高性能、高安全性的需求会增加硬件开销和设计复杂度,需要在设计中使用特定方法实现满足要求的电路,提高电路的正确性和可靠性。

4.相关技术中,对于从快时钟的软件寄存器到慢时钟电路的同步配置,在没有握手机制情况下,应用层面上软件无法得知配置生效的时间点,容易发生前级配置未被同步、后级配置无法生效的问题,直接影响电路的正确性和可靠性。特别是在时钟频率相差较大时,进行多次配置的情况下,问题尤为凸现。

技术实现要素:

5.为了解决现有技术存在的不足,本技术的目的在于提供从快时钟域到慢时钟域的同步处理电路、方法和芯片,能够确保在跨异步时钟域的同步处理中,每一次写入都能同步生效到慢时钟电路,且配置不会被改写,从而有效提高了电路功能的正确性和可靠性,同时还能够节省硬件逻辑开销。特别是对于时钟频率相差较大时进行多次配置的情况,效果尤为明显。

6.为实现上述目的,本技术提供的一种从快时钟域到慢时钟域的同步处理电路,连接于快时钟电路和慢时钟电路之间,所述同步处理电路包括:脉冲产生模块,用于接收快时钟域同步使能信号,根据所述快时钟域同步使能信号生成快时钟域同步使能脉冲信号;翻转产生模块,用于根据所述快时钟域同步使能脉冲信号生成快时钟域同步使能翻转信号;第一同步模块,用于将所述快时钟域同步使能翻转信号同步至慢时钟域,生成慢时钟域同步使能脉冲信号和同步使能翻转延迟信号;第一d触发器,用于接收快时钟域配置参数信号,根据所述快时钟域配置参数信号和所述慢时钟域同步使能脉冲信号,生成慢时钟域配置参数信号并发送至所述慢时钟电路;第二同步模块,用于将所述同步使能翻转延迟信号同步至快时钟域,生成同步清除脉冲信号,并发送至所述快时钟电路。

7.进一步地,所述脉冲产生模块的输入端与所述快时钟电路的输出使能端电性连接,所述脉冲产生模块的输出端与所述翻转产生模块的输入端电性连接,所述翻转产生模

块的输出端与所述第一同步模块的输入端电性连接,所述第一同步模块的使能脉冲输出端与所述第一d触发器的置位端电性连接,所述第一同步模块的使能延迟输出端与所述第二同步模块的输入端电性连接,所述第一d触发器的输入端与所述快时钟电路的输出配置参数端电性连接,所述第一d触发器的输出端与所述慢时钟电路的输入端电性连接,所述第二同步模块的输出端与所述快时钟电路的同步清除端电性连接。

8.进一步地,所述脉冲产生模块,用于将所述快时钟域同步使能信号经延迟并进行取反后,与所述快时钟域同步使能信号的原始信号进行做与运算,以生成所述快时钟域同步使能脉冲信号。

9.进一步地,所述翻转产生模块包括:第二d触发器和反相器;其中,所述第二d触发器的时钟端与所述脉冲产生模块的输出端电性连接,以接收所述快时钟域同步使能脉冲信号;所述第二d触发器的输出端与所述反相器的输入端电性连接,所述反相器的输出端与所述第二d触发器的输入端电性连接;所述第二d触发器的输出端还与所述第一同步模块的输入端电性连接,以向所述第一同步模块发送所述快时钟域同步使能翻转信号。

10.进一步地,所述第一同步模块,用于对所述快时钟域同步使能翻转信号进行慢时钟域的d触发器同步处理,生成慢时钟域同步使能翻转信号。

11.更进一步地,所述慢时钟域的d触发器同步处理,为二级慢时钟域的d触发器同步处理。

12.进一步地,所述第一同步模块,用于将所述慢时钟域同步使能翻转信号通过一级慢时钟域的d触发器输出后取反,并与所述慢时钟域同步使能翻转信号的原始信号进行做与运算,以生成慢时钟域同步使能上升沿脉冲信号;将所述慢时钟域同步使能翻转信号通过一级慢时钟域的d触发器输出,并与取反后的所述慢时钟域同步使能翻转信号的原始信号进行做与运算,以生成慢时钟域同步使能下降沿脉冲信号;对所述慢时钟域同步使能上升沿脉冲信号和所述慢时钟域同步使能下降沿脉冲信号进行做或运算,以生成慢时钟域同步使能脉冲信号。

13.进一步地,主端通过寄存器协议总线向所述快时钟域的配置参数寄存器和同步使能寄存器进行通信;所述寄存器协议总线为先进外设总线或高级高性能总线。

14.为实现上述目的,本技术还提供的一种从快时钟域到慢时钟域的同步处理方法,应用于从快时钟域到慢时钟域的同步处理电路,所述同步处理电路连接于快时钟电路和慢时钟电路之间,包括:接收快时钟域同步使能信号,根据所述快时钟域同步使能信号生成快时钟域同步使能脉冲信号;根据所述快时钟域同步使能脉冲信号生成快时钟域同步使能翻转信号;将所述快时钟域同步使能翻转信号同步至慢时钟域,生成慢时钟域同步使能脉冲信号和同步使能翻转延迟信号;接收快时钟域配置参数信号,根据所述快时钟域配置参数信号和所述慢时钟域同步使能脉冲信号,生成慢时钟域配置参数信号并发送至所述慢时钟电路;

将所述同步使能翻转延迟信号同步至快时钟域,生成同步清除脉冲信号,并发送至所述快时钟电路。

15.为实现上述目的,本技术提供的芯片,包括如上所述的从快时钟域到慢时钟域的同步处理电路。

16.为实现上述目的,本技术提供的车载设备,包括如上所述的芯片。

17.本技术的从快时钟域到慢时钟域的同步处理电路、方法、芯片和车载设备,能够确保在跨异步时钟域的同步处理中,每一次写入都能同步生效到慢时钟电路,且配置不会被改写,从而有效提高了电路功能的正确性和可靠性,同时还能够节省硬件逻辑开销。特别是对于时钟频率相差较大时进行多次配置的情况,效果尤为明显。

18.本技术的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本技术而了解。

附图说明

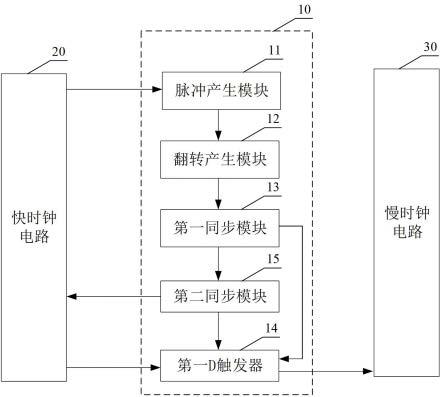

19.附图用来提供对本技术的进一步理解,并且构成说明书的一部分,并与本技术的实施例一起,用于解释本技术,并不构成对本技术的限制。在附图中:图1为根据本技术实施例的从快时钟域到慢时钟域的同步处理电路的结构框图;图2为根据本技术实施例的从快时钟域到慢时钟域的同步处理电路的结构示意图;图3为根据本技术实施例的从快时钟域到慢时钟域进行同步处理时的时序图;图4为根据本技术实施例的从快时钟域到慢时钟域的同步处理方法的流程图;图5为根据本技术实施例的芯片的结构框图;图6为根据本技术实施例的车载设备的结构框图。

具体实施方式

20.下面将参照附图更详细地描述本技术的实施例。虽然附图中显示了本技术的某些实施例,然而应当理解的是,本技术可以通过各种形式来实现,而且不应该被解释为限于这里阐述的实施例,相反提供这些实施例是为了更加透彻和完整地理解本技术。应当理解的是,本技术的附图及实施例仅用于示例性作用,并非用于限制本技术的保护范围。

21.应当理解,本技术的方法实施方式中记载的各个步骤可以按照不同的顺序执行,和/或并行执行。此外,方法实施方式可以包括附加的步骤和/或省略执行示出的步骤。本技术的范围在此方面不受限制。

22.本文使用的术语“包括”及其变形是开放性包括,即“包括但不限于”。术语“基于”是“至少部分地基于”。术语“一个实施例”表示“至少一个实施例”;术语“另一实施例”表示“至少一个另外的实施例”;术语“一些实施例”表示“至少一些实施例”。其他术语的相关定义将在下文描述中给出。

23.需要注意,本技术中提及的“第一”、“第二”等概念仅用于对不同的装置、模块或单元进行区分,并非用于限定这些装置、模块或单元所执行的功能的顺序或者相互依存关系。

24.需要注意,本技术中提及的“一个”、“多个”的修饰是示意性而非限制性的,本领域技术人员应当理解,除非在上下文另有明确指出,否则应该理解为“一个或多个”。“多个”应

理解为两个或以上。

25.下面,将参考附图详细地说明本技术的实施例。

26.实施例1图1为根据本技术实施例的从快时钟域到慢时钟域的同步处理电路的结构框图,该同步处理电路10连接于快时钟电路20和慢时钟电路30之间,同步处理电路10包括:脉冲产生模块11、翻转产生模块12、第一同步模块13、第一d触发器14和第二同步模块15。

27.其中,脉冲产生模块11,用于从快时钟电路20接收快时钟域同步使能信号,根据快时钟域同步使能信号生成快时钟域同步使能脉冲信号;翻转产生模块12,用于根据快时钟域同步使能脉冲信号生成快时钟域同步使能翻转信号,即,将快时钟域同步使能脉冲信号作为翻转使能,产生快时钟域同步使能翻转信号;第一同步模块13,用于将快时钟域同步使能翻转信号同步至慢时钟域,生成慢时钟域同步使能脉冲信号和同步使能翻转延迟信号;第一d触发器14,用于接收快时钟域配置参数信号,根据快时钟域配置参数信号和慢时钟域同步使能脉冲信号,生成慢时钟域配置参数信号并发送至慢时钟电路30;第二同步模块15,用于将同步使能翻转延迟信号同步至快时钟域,生成同步清除脉冲信号,并发送至快时钟电路20。

28.具体来说,在快时钟电路20中,设有配置参数寄存器(config_dat_reg),以及与config_dat_reg处于同一时钟域的同步使能寄存器(sync_en_reg),当主端通过寄存器协议总线使快时钟域中的config_dat_reg和sync_en_reg同时生效后,寄存器输出数据线,同时引出快时钟域的寄存器输出配置参数信号(o_config_dat)和寄存器输出使能信号(o_sync_en),以对慢时钟电路30做参数配置。

29.同步处理电路10运行时,通过脉冲产生模块11,从快时钟电路20接收快时钟域同步使能信号(即由sync_en_reg发出的o_sync_en),并转换为快时钟域同步使能脉冲信号(即快时钟域同步使能信号从0到1跳变的周期脉冲信号),并通过翻转产生模块12,根据快时钟域同步使能脉冲信号生成快时钟域同步使能翻转信号(即同步使能的翻转标志位),以及通过第一同步模块13,将快时钟域同步使能翻转信号同步至慢时钟域,生成慢时钟域同步使能脉冲信号和同步使能翻转延迟信号,并通过第一d触发器14接收快时钟域配置参数信号(即由config_dat_reg发出的o_config_dat),根据快时钟域配置参数信号和慢时钟域同步使能脉冲信号,生成慢时钟域配置参数信号并发送至慢时钟电路30,以及通过第二同步模块15,将同步使能翻转延迟信号同步至快时钟域,生成同步清除脉冲信号,并发送至快时钟电路20的同步清除端(sync_clear)。

30.通过同步处理电路的运行,一方面,通过将生成的慢时钟域配置参数信号发送至慢时钟电路,能够确保每一次写入都能同步生效到慢时钟电路,避免了亚稳态和毛刺等异步电路风险;另一方面,通过将生成的同步清除脉冲信号发送至快时钟电路,能够确保配置寄存器在上一次配置未生效到慢时钟电路之前,不会被重复改写。由此,不仅保证了电路功能的正确性和可靠性,同时还节省了硬件逻辑开销。

31.需要说明的是,本技术的从快时钟域到慢时钟域的同步处理电路可以适用于采用多种寄存器协议总线的快时钟域,以及多种慢时钟域。在具体示例中,当寄存器协议总线为先进外设总线(advanced peripheral bus,apb)时,快时钟域为p时钟(pclk)域;当寄存器协议总线为高级高性能总线(advanced high-performance bus,ahb)时,快时钟域为h时钟

(hclk)域;而慢时钟域可以是32k时钟(32k_clk)域、100k时钟(100k_clk)域等。

32.为了使描述更直观,以下实施例中可以采用与apb总线对应的pclk域作为快时钟域示例,采用32k_clk域作为慢时钟域示例,二者的时钟频率(前者时钟频率为200m,后者时钟频率为32k)相差上千倍,效果尤为明显。具体示例中的应用于por(power on reset,上电复位)电路,但可以理解的是,本技术并不局限于上述具体场景。

33.本技术的实施例中,参考图2所示,快时钟电路(fast clk circuit)20通过输入端输入软件配置信号(sw_cfg),脉冲产生模块11的输入端与快时钟电路(fast clk circuit)20的输出使能端电性连接,脉冲产生模块11的输出端与翻转产生模块(toggle)12的输入端(即第二d触发器的clk端)电性连接,翻转产生模块(toggle)12的输出端(即第二d触发器的q端)与第一同步模块(1-synchroniser)13的输入端电性连接,第一同步模块(1-synchroniser)13的使能脉冲输出端与第一d触发器(1-dff,1-delay flip flop)14的置位端(set)电性连接,第一同步模块(1-synchroniser)13的使能延迟输出端与第二同步模块(2-synchroniser)15的输入端电性连接,第一d触发器(1-dff)14的输入端(d)与快时钟电路(fast clk circuit)20的输出配置参数端(o_cfg_dat)电性连接,第一d触发器(1-dff)14的输出端(q)与慢时钟电路(slow clk circuit)30的输入端电性连接,第二同步模块(2-synchroniser)15的输出端与快时钟电路(fast clk circuit)20的同步清除端(sync clear)电性连接。由此,能够通过将生成的慢时钟域配置参数信号(config_dat_32k)发送至慢时钟电路(slow clk circuit)30,能够确保每一次写入都能同步生效到慢时钟电路(slow clk circuit)30,避免了亚稳态和毛刺等异步电路风险;同时,通过将生成的同步清除脉冲信号(sync_clr_pulse)发送至快时钟电路(fast clk circuit)20,能够确保配置寄存器在上一次配置未生效到慢时钟电路(slow clk circuit)30之前,不会被重复改写。

34.本技术的实施例中,脉冲产生模块11用于:将快时钟域同步使能信号(sync_en_pclk)经延迟电路进行延迟,并对延迟后信号进行取反后,与快时钟域同步使能信号(sync_en_pclk)的原始信号进行做与运算,以生成快时钟域同步使能脉冲信号(sync_en_pulse_pclk),即生成快时钟域同步使能信号(sync_en_pclk)从0到1跳变的周期脉冲信号。

35.本技术的实施例中,参考图2所示,翻转产生模块(toggle)12包括第二d触发器(2-dff)121和反相器(inverter)122。其中,第二d触发器(2-dff)121的时钟端与脉冲产生模块11的输出端电性连接,以接收快时钟域同步使能脉冲信号(sync_en_pulse_pclk);第二d触发器(2-dff)121的输出端(q)与反相器(inverter)122的输入端电性连接,反相器(inverter)122的输出端与第二d触发器(2-dff)121的输入端(d)电性连接;第二d触发器(2-dff)121的输出端还与第一同步模块(1-synchroniser)13的输入端电性连接,以向第一同步模块(1-synchroniser)13发送快时钟域同步使能翻转信号(sync_en_toggle_pclk),从而能够输出同步使能的翻转标志位。

36.进一步地,第一同步模块13具体用于:对快时钟域同步使能翻转信号(sync_en_toggle_pclk)进行慢时钟域的d触发器同步处理,生成慢时钟域同步使能翻转信号(sync_en_toggle_32k)。

37.需要说明的是,此处的慢时钟域的d触发器同步处理可以是一级、二级或三级d触发器同步处理,作为优选,设为二级慢时钟域的d触发器同步处理,兼顾了避免毛刺和节省硬件开销。

38.进一步地,参考图2所示,第一同步模块(1-synchroniser)13还用于:将慢时钟域同步使能翻转信号(sync_en_toggle_32k)通过一级慢时钟域的d触发器输出后取反,并与慢时钟域同步使能翻转信号(sync_en_toggle_32k)的原始信号进行做与运算,以生成慢时钟域同步使能上升沿脉冲信号(sync_en_32k_pos);将慢时钟域同步使能翻转信号(sync_en_toggle_32k)通过一级慢时钟域的d触发器输出,并与取反后的慢时钟域同步使能翻转信号(sync_en_toggle_32k)的原始信号(即取反后的原始信号)进行做与运算,以生成慢时钟域同步使能下降沿脉冲信号(sync_en_32k_neg);对慢时钟域同步使能上升沿脉冲信号(sync_en_32k_pos)和慢时钟域同步使能下降沿脉冲信号(sync_en_32k_neg)进行做或运算,以生成慢时钟域同步使能脉冲信号(sync_en_pulse_32k)。

39.需要说明的是,第二同步模块(2-synchroniser)15可以采用与第一同步模块(1-synchroniser)13类似的结构。

40.也就是说,在具体示例中,第二同步模块(2-synchroniser)15可以用于:对同步使能翻转延迟信号(sync_en_toggle_32k_delay)进行二级快时钟域的d触发器同步处理,生成快时钟域同步使能翻转信号(sync_en_toggle_pclk)。而后,将快时钟域同步使能翻转信号(sync_en_toggle_pclk)通过一级快时钟域的d触发器输出后取反,并与快时钟域同步使能翻转信号(sync_en_toggle_pclk)的原始信号进行做与运算,以生成快时钟域同步使能上升沿脉冲信号(sync_en_pclk_pos);将快时钟域同步使能翻转信号(sync_en_toggle_pclk)通过一级快时钟域的d触发器输出,并与取反后的快时钟域同步使能翻转信号(sync_en_toggle_pclk)的原始信号(即取反后的原始信号)进行做与运算,以生成快时钟域同步使能下降沿脉冲信号(sync_en_pclk_neg);对快时钟域同步使能上升沿脉冲信号(sync_en_pclk_pos)和快时钟域同步使能下降沿脉冲信号(sync_en_pclk_neg)进行做或运算,以生成同步清除脉冲信号(sync_clr_pulse)。

41.图3为根据本技术具体实施例的从快时钟域到慢时钟域的同步处理时的时序图。参考图3所示,pclk为快时钟域的时钟脉冲;32k_clk为慢时钟域的时钟脉冲;o_sync_en为寄存器输出使能信号,即,相当于输入至脉冲产生模块11的sync_en_pclk;sync_en_toggle_pclk为由sync_en_pclk先后经脉冲产生模块11和翻转产生模块12处理后,得到的快时钟域同步使能翻转信号;sync_en_toggle_32k为由sync_en_toggle_pclk在第一同步模块13处理的过程中,得到的慢时钟域同步使能翻转信号;sync_en_toggle_32k_delay为由sync_en_toggle_32k经第一同步模块13处理后,相比于sync_en_toggle_pclk,延迟了一个32k_clk脉冲周期的同步使能翻转延迟信号;sync_en_pulse_32k为由sync_en_toggle_pclk经第一同步模块13处理后,生成的慢时钟域同步使能脉冲信号;cfg_dat_pclk为快时钟域配置参数信号,即,源于快时钟电路20中由config_dat_reg发出的o_config_dat;cfg_dat_32k为由sync_en_pulse_32k和cfg_dat_pclk经第一d触发器14处理后,生成的慢时钟域配置参数信号;sync_clr_pulse为由sync_en_toggle_32k_delay经第二同步模块15处理后,生成的同步清除脉冲信号。由此,在跨异步时钟域的同步处理中,采用组合电路产生脉冲信号,并进行翻转,用来作为使能标志位,即通过每次翻转的sync_en_pulse_32k作为异步数据的的采样保证信号(qualifier),避免了亚稳态和毛刺等异步电路风险。不仅在快时钟域的清零同步标志位电路中减少了响应周期数,同时在慢时钟域的数据同步中减少了响应周期数,而且确保了软件的每一次配置不会被改写,保证了功能的安全可靠性,还能够节

省硬件开销。

42.综上所述,通过脉冲产生模块接收快时钟域同步使能信号,根据快时钟域同步使能信号生成快时钟域同步使能脉冲信号,并通过翻转产生模块根据快时钟域同步使能脉冲信号生成快时钟域同步使能翻转信号,以及通过第一同步模块将快时钟域同步使能翻转信号同步至慢时钟域,生成慢时钟域同步使能脉冲信号和同步使能翻转延迟信号,并通过第一d触发器接收快时钟域配置参数信号,根据快时钟域配置参数信号和慢时钟域同步使能脉冲信号,生成慢时钟域配置参数信号并发送至慢时钟电路,以及通过第二同步模块将同步使能翻转延迟信号同步至快时钟域,生成同步清除脉冲信号,并发送至快时钟电路。由此,能够确保在跨异步时钟域的同步处理中,每一次写入都能同步生效到慢时钟电路,且配置不会被改写,从而有效提高了电路功能的正确性和可靠性,同时还能够节省硬件逻辑开销。特别是对于时钟频率相差较大时进行多次配置的情况,效果尤为明显。

43.实施例2图4为根据本技术实施例的从快时钟域到慢时钟域的同步处理方法的流程图。该同步处理方法应用于从快时钟域到慢时钟域的同步处理电路,该同步处理电路连接于快时钟电路和慢时钟电路之间。参考图4所示,该从快时钟域到慢时钟域的同步处理方法包括以下步骤:在步骤401,接收快时钟域同步使能信号,根据快时钟域同步使能信号生成快时钟域同步使能脉冲信号。

44.在步骤402,根据快时钟域同步使能脉冲信号生成快时钟域同步使能翻转信号。

45.在步骤403,将快时钟域同步使能翻转信号同步至慢时钟域,生成慢时钟域同步使能脉冲信号和同步使能翻转延迟信号。

46.在步骤404,接收快时钟域配置参数信号,根据快时钟域配置参数信号和慢时钟域同步使能脉冲信号,生成慢时钟域配置参数信号并发送至慢时钟电路。

47.在步骤405,将同步使能翻转延迟信号同步至快时钟域,生成同步清除脉冲信号,并发送至快时钟电路。

48.需要说明的是,上述对从快时钟域到慢时钟域的同步处理电路的解释说明,同样适用于本技术实施例中的从快时钟域到慢时钟域的同步处理方法,此处不作赘述。

49.根据本技术实施例的从快时钟域到慢时钟域的同步处理方法,通过接收快时钟域同步使能信号,根据快时钟域同步使能信号生成快时钟域同步使能脉冲信号,并通过根据快时钟域同步使能脉冲信号生成快时钟域同步使能翻转信号,以及通过将快时钟域同步使能翻转信号同步至慢时钟域,生成慢时钟域同步使能脉冲信号和同步使能翻转延迟信号,并通过接收快时钟域配置参数信号,根据快时钟域配置参数信号和慢时钟域同步使能脉冲信号,生成慢时钟域配置参数信号并发送至慢时钟电路,以及通过将同步使能翻转延迟信号同步至快时钟域,生成同步清除脉冲信号,并发送至快时钟电路。由此,能够确保在跨异步时钟域的同步处理中,每一次写入都能同步生效到慢时钟电路,且配置不会被改写,从而有效提高了电路功能的正确性和可靠性,同时还能够节省硬件逻辑开销。特别是对于时钟频率相差较大时进行多次配置的情况,效果尤为明显。

50.实施例3图5为根据本技术实施例的芯片的结构框图。参考图5所示,芯片100,包括上述实

施例的从快时钟域到慢时钟域的同步处理电路10。

51.实施例4图6为根据本技术实施例的车载设备的结构框图。参考图6所示,车载设备1000,包括上述实施例的芯片100。

52.本领域普通技术人员可以理解:以上所述仅为本技术的优选实施例而已,并不用于限制本技术,尽管参照前述实施例对本技术进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例记载的技术方案进行修改,或者对其中部分技术特征进行等同替换。凡在本技术的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。