1.本技术涉及显示技术领域,具体涉及一种数据驱动器及显示装置。

背景技术:

2.目前,可量产且较高的主流刷新频率为144hz,但随着显示技术的发展及客户应用场景的多样化,对于高频显示的需求越来越强烈。然而,在更高频显示的研发过程中发现,随着刷新频率的提高,子像素的充电时间也越来越受到限制,容易出现充电时间不足导致的视觉效果变差等显示问题。

技术实现要素:

3.本技术提供一种数据驱动器及显示装置,以缓解更高频显示下充电时间不足的技术问题。

4.第一方面,本技术提供一种数据驱动器,该数据驱动器包括缓存模块和至少两个数据处理支路,缓存模块用于同步输出至少两行子像素对应的画面数据;每个数据处理支路与缓存模块、一组数据线连接,至少两个数据处理支路用于根据接收到的画面数据同步输出对应的数据信号至至少两行子像素。

5.在其中一些实施方式中,缓存模块包括至少两个依次串接的线缓冲器,每个线缓冲器的输出端与一数据处理支路的输入端对应连接,每个线缓冲器用于暂存一行子像素对应的画面数据。

6.在其中一些实施方式中,数据驱动器还包括寄存器,寄存器存储有选择参数,选择参数用于控制数据处理支路处于工作状态的数量和/或线缓冲器处于工作状态的数量。

7.在其中一些实施方式中,数据驱动器还包括计数器,计数器与缓存模块连接,计数器用于计算缓存模块暂存画面数据的行数,以触发缓存模块输出。

8.在其中一些实施方式中,每个数据处理支路包括数据锁存器、数模转换器以及数据映射模块,数据锁存器的输入端与缓存模块连接,用于逐行抓取对应行子像素的画面数据;数模转换器的输入端与数据锁存器的输出端连接;数据映射模块的输入端与数模转换器的输出端连接,数据映射模块的各输出端与一组数据线对应连接,用于按照排列后的顺序输出对应的数据信号。

9.在其中一些实施方式中,数据驱动器还包括放大模块,放大模块的各输入端与至少两个数据处理支路的输出端对应连接,放大模块的各输出端与至少两组数据线对应连接。

10.第二方面,本技术提供一种显示装置,该显示装置包括上述至少一实施方式中的数据驱动器,数据驱动器应用于更高频显示中。

11.在其中一些实施方式中,显示装置还包括阵列分布的多个子像素、至少一组扫描线以及至少两组数据线,每组扫描线与至少两行子像素连接;每组数据线与至少两行子像素中的一行连接,以同步地提供数据信号至至少两行子像素。

12.在其中一些实施方式中,每组扫描线连接的子像素的行数与数据线的组数相同。

13.在其中一些实施方式中,至少两组数据线包括作为一组数据线的奇数数据线和作为另一组数据线的偶数数据线,奇数数据线、偶数数据线沿第一方向依次交替排列;每列子像素包括沿第二方向交替排列的奇数子像素和偶数子像素,奇数子像素与奇数数据线或者偶数数据线中的一种连接,偶数子像素与奇数数据线或者偶数数据线中的另一种连接。

14.在其中一些实施方式中,显示装置还包括一起始信号线和至少两个栅极驱动电路,起始信号线与至少两个栅极驱动电路连接;每组扫描线包括至少两条相邻的扫描线,每组扫描线中的一条与至少两行子像素中的一行、两个栅极驱动电路中的一个连接,每组扫描线中的另一个与至少两行子像素中的另一行、两个栅极驱动电路中的另一个连接。

15.本技术提供的数据驱动器及显示装置,通过缓存模块对至少两行子像素对应的画面数据的同步,至少两个数据处理支路可以同步输出对应的数据信号至至少两行子像素,这样能够为至少两行子像素同时充电,相较于传统技术中的逐行充电,在相同刷新频率下所需的充电时间更短,有效缓解了更高频显示下充电时间不足的技术问题。

附图说明

16.下面结合附图,通过对本技术的具体实施方式详细描述,将使本技术的技术方案及其它有益效果显而易见。

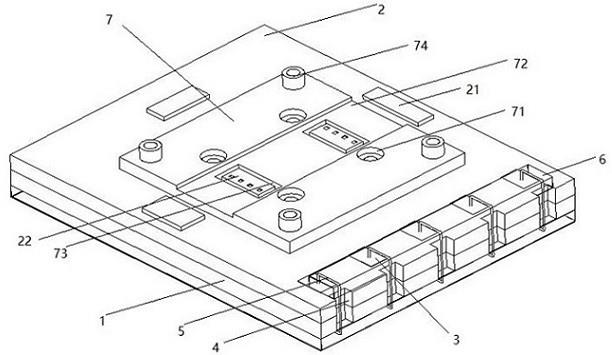

17.图1为相关技术中显示装置的结构示意图。

18.图2为图1所示显示装置的驱动时序示意图。

19.图3为图1中数据驱动器的结构示意图。

20.图4为本技术实施例提供的显示装置的结构示意图。

21.图5为图4所示显示装置的驱动时序示意图。

22.图6为图4中数据驱动器的结构示意图。

23.图7为本技术实施例提供的寄存器的选择参数的第一种工作示意图。

24.图8为本技术实施例提供的寄存器的选择参数的第二种工作示意图。

25.图9为本技术实施例提供的缓存模块的工作示意图。

具体实施方式

26.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

27.图1为相关技术中显示装置的结构示意图,该显示装置包括多条扫描线、多条数据线、阵列分布的子像素以及数据驱动器100。其中,子像素可以为红色子像素r、蓝色子像素b或者绿色子像素g。

28.每条扫描线与一行子像素连接,以逐行打开对应的子像素。例如,扫描信号g1从第一扫描线的一端或者两端输入,已打开第一行子像素;扫描信号g2从第二扫描线的一端或者两端输入,已打开第二行子像素;扫描信号g3从第三扫描线的一端或者两端输入,已打开第三行子像素;扫描信号g4从第四扫描线的一端或者两端输入,已打开第四行子像素。

29.每条数据线与一列子像素连接,为同一行中的子像素逐列充电。

30.数据驱动器100的每个输出端分别与一数据线对应连接,为每条数据线提供对应的数据信号,例如,上述显示装置若设置有2160列子像素的话,则对应的有2160条数据线,数据驱动器100需要对应提供第1数据信号s1至第2160数据信号s2160。

31.图2为图1所示显示装置的驱动时序示意图,扫描信号逐行打开对应行子像素时,数据信号集ds为每行子像素逐个进行充电,其中,数据信号集ds可以包括上述的第1数据信号s1至第2160数据信号s2160。例如,扫描信号g1在负脉冲期间打开了第一行子像素,此时,数据信号集ds为第一行子像素中的每个子像素逐个进行充电;扫描信号g2在负脉冲期间打开了第二行子像素,此时,数据信号集ds为第二行子像素中的每个子像素逐个进行充电;扫描信号g3在负脉冲期间打开了第三行子像素,此时,数据信号集ds为第三行子像素中的每个子像素逐个进行充电;扫描信号g4在负脉冲期间打开了第四行子像素,此时,数据信号集ds为第四行子像素中的每个子像素逐个进行充电;其他行子像素的驱动时序可以依次类推。

32.对应地,上述显示装置的驱动架构、驱动时序需要数据驱动器100具有如图3所示的结构,该数据驱动器100包括依次连接的前端处理器10、移动产业处理器接口20、随机存取存储器30、中端处理器40、数据锁存器50、数模转换器60、数据映射器以及放大模块80。其中,前端处理器10接入视频数据,放大模块80输出数据信号至对应的数据线。

33.然而,随着高频显示的不断发展,上述驱动架构、驱动时序已经难以在更高频显示下为对应的子像素提供所需的充电时间,有鉴于此,本实施例提供了一种数据驱动器100,请参阅图4至图9,如图6所示,数据驱动器100包括缓存模块41和至少两个数据处理支路,缓存模块41用于同步输出至少两行子像素对应的画面数据;每个数据处理支路与缓存模块41、一组数据线连接,至少两个数据处理支路用于根据接收到的画面数据同步输出对应的数据信号至至少两行子像素。

34.需要进行说明的是,相较于图3所示的数据驱动器100,本实施例增加了缓存模块41和数据处理支路,两者配合可以对中端处理器40处理后的画面数据进行同步处理,以同步输出数据信号至对应的数据线。

35.可以理解的是,本实施例提供的数据驱动器100及显示装置,通过缓存模块41对至少两行子像素对应的画面数据的同步,至少两个数据处理支路可以同步输出对应的数据信号至至少两行子像素,这样能够为至少两行子像素同时充电,相较于传统技术中的逐行充电,在相同刷新频率下所需的充电时间更短,有效缓解了更高频显示下充电时间不足的技术问题。

36.其中,缓存模块41的输入端与中端处理器40的输出端连接。

37.在其中一个实施例中,每个数据处理支路包括数据锁存器50、数模转换器60以及数据映射模块70,数据锁存器50的输入端与缓存模块41连接,用于逐行抓取对应行子像素的画面数据;数模转换器60的输入端与数据锁存器50的输出端连接;数据映射模块70的输入端与数模转换器60的输出端连接,数据映射模块70的各输出端与一组数据线对应连接,用于按照排列后的顺序输出对应的数据信号。

38.例如,第一数据处理支路571可以包括依次连接的第一数据锁存器51、第一数模转换器61以及第一数据映射模块71,第二数据处理支路572可以包括依次连接的第二数据锁

存器52、第二数模转换器62以及第二数据映射模块72。其中,第一数据锁存器51、第二数据锁存器52可以具有与数据锁存器50对应相同的作用,第一数模转换器61、第二数模转换器62可以具有与数模转换器60对应相同的作用,第一数据映射模块71、第二数据映射模块72可以具有与数据映射模块70对应相同的作用。

39.需要进行说明的是,数据处理支路的数量可以与数据线的组数或者同一组扫描线连接的子像素的行数相同。

40.在其中一个实施例中,如图6所示,数据驱动器100还包括放大模块80,放大模块80的各输入端与至少两个数据处理支路的输出端对应连接,放大模块80的各输出端与至少两组数据线对应连接。

41.具体地,放大模块80的输入端与各数据映射模块70的输出端连接,例如,可以与第一数据映射模块71的输出端、第二数据映射模块72的输出端连接。该放大模块80可以对数据信号进行电流和/或电压放大,以提高数据信号的驱动能力。

42.在其中一个实施例中,如图7、图8所示,数据驱动器100还包括寄存器90,寄存器90存储有选择参数,选择参数用于控制数据处理支路处于工作状态的数量和/或线缓冲器处于工作状态的数量。

43.需要进行说明的是,在其中一个实施例中,如图7所示,上述的选择参数可以为2bits,当该2bits为00时,则数据驱动器100中仅有一个数据处理支路处于工作状态,此时,缓存模块41接入对应的画面数据之后,依次经第一数据锁存器51、第一数模转换器61以及第一数据映射模块71以及放大模块80之后,输出数据信号s1-s2160至显示面板300中对应的子像素,然后在扫描信号g1、g2等的控制下为对应的子像素充电。其中,此处是以显示面板300中有2160列子像素为例的。

44.在其中一个实施例中,如图8所示,上述的选择参数可以为2bits,当该2bits为01时,则数据驱动器100中具有两个数据处理支路处于工作状态,此时,缓存模块41接入对应的画面数据之后,依次经第一数据锁存器51、第一数模转换器61以及第一数据映射模块71以及放大模块80之后,输出数据信号s1-s2160中的奇数个数据信号至显示面板300中对应的子像素;同时,依次经第二数据锁存器52、第二数模转换器62以及第二数据映射模块72以及放大模块80之后,输出数据信号s1-s2160中的偶数个数据信号至显示面板300中对应的子像素,然后在扫描信号g1、g2等的控制下为对应的子像素充电。其中,此处是以显示面板300中有2160列子像素为例的。

45.同理可知,上述的选择参数可以为2bits,当该2bits为10时,则数据驱动器100中具有三个数据处理支路处于工作状态。或者,上述的选择参数可以为2bits,当该2bits为11时,则数据驱动器100中具有四个数据处理支路处于工作状态。

46.在其中一个实施例中,缓存模块41包括至少两个依次串接的线缓冲器,每个线缓冲器的输出端与一数据处理支路的输入端对应连接,每个线缓冲器用于暂存一行子像素对应的画面数据。

47.需要进行说明的是,上述的选择参数可以为2bits,当该2bits为00时,则线缓冲器的个数可以为0个或者1个;当该2bits为01时,则线缓冲器的个数可以为2个;当该2bits为10时,则线缓冲器的个数可以为3个;当该2bits为11时,则线缓冲器的个数可以为4个。

48.如图9所示,上述的选择参数可以为11时,数据驱动器100中具有四个数据处理支

路处于工作状态,同时具有四个线缓冲器处于工作状态。

49.与图8相比,第一数据锁存器51的输入端与第一线缓冲器411的输出端连接,第二数据锁存器52的输入端与第二线缓冲器412的输出端连接,第三数据锁存器53的输入端与第三线缓冲器413的输出端连接,第四数据锁存器54的输入端与第四线缓冲器414的输出端连接。其中,也新增加了第三数据处理支路和第四数据处理支路,第三数据处理支路包括依次连接的第三数据锁存器53、第三数模转换器63以及第三数据映射模块73,第四数据处理支路包括依次连接的第四数据锁存器54、第四数模转换器64以及第四数据映射模块74。

50.其中,第三数据映射模块73的输出端、第四数据映射模块74的输出端分别与放大模块80的输入端连接,然后经放大模块80对数据信号放大后输出至显示面板300。

51.需要进行说明的是,中端处理器40输出的画面数据中的第一段数据先进入第一线缓冲器411;然后画面数据中的第二段数据进入第一线缓冲器411时,第一段数据同步进入第二线缓冲器412;然后画面数据中的第三段数据进入第一线缓冲器411时,第二段数据同步进入第二线缓冲器412,第一段数据同步进入第三线缓冲器413;然后画面数据中的第四段数据进入第一线缓冲器411时,第三段数据同步进入第二线缓冲器412,第二段数据同步进入第三线缓冲器413,第一段数据同步进入第四线缓冲器414。此时,每个线缓冲器中存储有一段数据,而计数器91也统计到一共进入了四段数据,这是会触发缓存模块41同时输出该四段数据至对应的数据处理支路。

52.其中,每段数据可以为画面数据中的一行或者多行等等画面数据中的一部分。

53.在其中一个实施例中,数据驱动器100还包括计数器91,计数器91与缓存模块41连接,计数器91用于计算缓存模块41暂存画面数据的行数,以触发缓存模块41输出。

54.在其中一个实施例中,本实施例提供一种显示装置,该显示装置包括上述至少一实施例中的数据驱动器,数据驱动器应用于更高频显示中。

55.可以理解的是,本实施例提供的显示装置,通过缓存模块41对至少两行子像素对应的画面数据的同步,至少两个数据处理支路可以同步输出对应的数据信号至至少两行子像素,这样能够为至少两行子像素同时充电,相较于传统技术中的逐行充电,在相同刷新频率下所需的充电时间更短,有效缓解了更高频显示下充电时间不足的技术问题。

56.需要进行说明的是,该显示装置可以但不限于为自发光型显示装置例如有机发光二极管显示装置、微发光二极管显示装置、迷你发光二极管显示装置或者量子点发光二极管显示装置,也可以为液晶显示装置。

57.在其中一个实施例中,如图4、图5所示,显示装置还包括阵列分布的多个子像素、至少一组扫描线以及至少两组数据线,每组扫描线与至少两行子像素连接;每组数据线与至少两行子像素中的一行连接,以同步地提供数据信号至至少两行子像素。

58.可以理解的是,本实施例提供的显示装置,通过每组扫描线与至少两行子像素连接,可以同时打开至少两行子像素,每组数据线与至少两行子像素中的一行连接,能够同步地提供数据信号至至少两行子像素,这样可以为至少两行子像素同时充电,相较于传统技术中的逐行充电,在相同刷新频率下所需的充电时间更短,有效缓解了更高频显示下充电时间不足的技术问题。

59.需要进行说明的是,每组扫描线可以为一条或者多条,例如,扫描线gl1可以为一组扫描线,其与至少两行子像素连接以同时打开该至少两行子像素。扫描线gl1、扫描线gl2

可以为一组扫描线,其中,扫描线gl1与第一行子像素连接以打开该第一行子像素,扫描线gl2与第二行子像素连接以打开该第二行子像素;扫描线gl3、扫描线gl4可以为一组扫描线,其中,扫描线gl3与第三行子像素连接以打开该第三行子像素,扫描线gl4与第四行子像素连接以打开该第四行子像素;其他组扫描线可以依次类推。同理可知,每组扫描线可以包括三条、四条或者更多条扫描线等等,以同时打开对应行的子像素。

60.其中,同一组扫描线中的各扫描线可以是相邻的或者是相隔的,同一组扫描线也可以连接相邻行的子像素或者不相邻行的子像素。作为优选的,同一组扫描线中的各扫描线是相邻的且连接相邻行的子像素,如此便于可以减少显示面板300内的线路的交叉,并减少布线距离。

61.在其中一个实施例中,至少两组数据线包括作为一组数据线的奇数数据线和作为另一组数据线的偶数数据线,奇数数据线、偶数数据线沿第一方向dr1依次交替排列;每列子像素包括沿第二方向dr2交替排列的奇数子像素和偶数子像素,奇数子像素与奇数数据线或者偶数数据线中的一种连接,偶数子像素与奇数数据线或者偶数数据线中的另一种连接。

62.具体地,如图4所示,其采用了两组数据线,其中一组数据线为奇数条数据线,例如数据线dl1、数据线dl3、数据线dl4317...等等,该组数据线为第一行子像素、第三行子像素...等等奇数行子像素提供对应的数据信号;其中另一组数据线为偶数条数据线,例如数据线dl2、数据线dl4、数据线dl4320...等等,该组数据线为第二行子像素、第四行子像素...等等偶数行子像素提供的对应的数据信号。或者,奇数条数据线也可以与对应的偶数行子像素连接,偶数条数据线也可以与对应的奇数行子像素连接。

63.其中,数据线dl1用于传输源自数据驱动器100的数据信号s1、数据线dl2用于传输源自数据驱动器100的数据信号s2、数据线dl3用于传输源自数据驱动器100的数据信号s3、数据线dl4用于传输源自数据驱动器100的数据信号s4...等等。

64.在上述记载的基础上可以理解,在一些实施例中,也可以采用三组数据线,其中一组数据线可以为一些行子像素提供对应的数据信号,例如,第1、4、7...等等行子像素;其中另一组数据线可以为另一些行子像素提供对应的数据信号,例如,第2、3、8...等等行子像素;其中再一组数据线可以为再一些行子像素提供对应的数据信号,例如,第3、6、9...等等行子像素。

65.可以理解的是,在上述实施例中,在更高频显示中每帧所能够占用的时间也越少,而数据线的分组越多,一帧中数据信号的写入时间也越短,如此可以满足每帧中数据信号充电至对应子像素的时间需求。

66.在其中一个实施例中,如图4所示,显示装置还包括一起始信号线stvl和至少两个栅极驱动电路200,起始信号线stvl与至少两个栅极驱动电路200连接;每组扫描线包括至少两条相邻的扫描线,每组扫描线中的一条与至少两行子像素中的一行、两个栅极驱动电路200中的一个连接,每组扫描线中的另一个与至少两行子像素中的另一行、两个栅极驱动电路200中的另一个连接。

67.需要进行说明的是,本实施例的两个栅极驱动电路200分别位于显示区的左右两侧,可以为同一扫描线同时提供对应的扫描信号。其中,每个栅极驱动电路200包括多个级联的栅极驱动单元,例如,栅极驱动单元gu11、栅极驱动单元gu12、栅极驱动单元gu13、栅极

驱动单元gu14...等等,其中,栅极驱动单元gu11与栅极驱动单元gu13级联,栅极驱动单元gu12与栅极驱动单元gu14级联,其他可以依次类推。

68.其中,用于传输扫描信号g1的扫描线gl1的两端分别与两个栅极驱动单元gu11连接。用于传输扫描信号g2的扫描线gl2的两端分别与两个栅极驱动单元gu12连接。用于传输扫描信号g3的扫描线gl3的两端分别与两个栅极驱动单元gu13连接。用于传输扫描信号g4的扫描线gl4的两端分别与两个栅极驱动单元gu14连接。其他可以依次类推,如此可以降低各扫描信号在对应扫描线中的传输损耗,提高了扫描信号的驱动力。

69.其中,起始信号线stvl用于传输起始信号stv,该起始信号stv可以控制两个栅极驱动电路200同步工作,并输出对应相同的扫描信号。

70.在其中一个实施例中,上述显示装置可以采用一个栅极驱动电路200,其同样可以实现与两个栅极驱动电路200相同的驱动时序。这样不仅可以节省一个栅极驱动电路200,而且也减少了显示装置的边框占用空间。

71.图5为图4所示显示装置的驱动时序示意图,其中,扫描信号g1、扫描信号g2具有相同的波形,并在其负脉冲的持续期间同时打开了第一行子像素、第二行子像素,在该持续期间中,对应组的数据信号同时写入至第一行子像素、第二行子像素,例如,奇数条数据线传输的数据信号s1...等等被写入至第一行子像素,偶数条数据线传输的数据信号s2...等等被写入至第二行子像素。接着,具有相同波形的扫描信号g3、扫描信号g4的负脉冲到来,对应的数据信号被同时写入至第三行子像素、第四行子像素,如此循环扫描直至所有的子像素被充电完毕,在相同的刷新频率下,这样每帧可以减少一半的充电时间。依次类推,当有更多行子像素被同时写入数据信号时,每帧可以减少更多的充电时间。

72.在其中一个实施例中,每组扫描线连接的子像素的行数与数据线的组数相同。

73.需要进行说明的是,本实施例中每组数据线为一行子像素进行充电,随着数据线的组数或者每组扫描线连接的子像素的行数的增加,会有更多行子像素被同时写入数据信号,可以在每帧中减少更多的充电时间。

74.在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

75.以上对本技术实施例所提供的数据驱动器及显示装置进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例的技术方案的范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。