高效率小体积ac-dc电源控制器模块

技术领域

1.本发明涉及一种用于电力电子系统中ac-dc电源控制器模块,属于集成电路技术领域。

背景技术:

2.电源管理芯片主要分为线性稳压器和开关电源转换器。开关电源转换器使用开关双极型晶体管或场效应管将输入电压斩波成方波,方波由占空比调节,并通过低通输出滤波器得到直流输出电压。相比于线性稳压器,开关电源转换器具有转换效率高,体积小等优点。所以开关电源在现今电源管理市场占据着主要的地位。

3.随着便携式电子设备对其供电电源的要求不断提高,开关电源市场正在围绕着低功耗、高精度、小体积等性能展开激烈地角逐,反激式ac-dc转换器也不例外。反激式ac-dc电源系统需要将输出端信息反馈到控制芯片中,通过负反馈来调整功率开关管的导通时间占空比,以此达到稳定输出的目的。根据反馈方式,反激式ac-dc转换器可分为原边反馈(primary side regulation,psr)和副边反馈(secondary side regulation,ssr)。副边反馈技术也称为光耦隔离反馈,该系统由反激拓扑电路,光耦隔离反馈电路和控制芯片组成。原边反馈技术是通过采样辅助绕组电压,来间接采样输出电压。原边反馈技术所需要的外围器件少,少的外围元器件即降低了pcb的成本,也提高了系统的可靠性,所以原边反馈技术目前得到了更为广泛的应用。

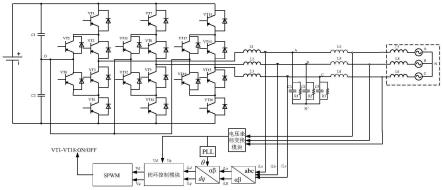

4.典型原边反馈技术的系统框图如图1所示。当功率管导通时,辅助绕组电压与原边绕组电压成正比且为负值;当功率管关断时,辅助绕组电压与副边绕组电压成正比且为正值,所以,就可以在副边导通时采样辅助绕组的电压信息,来间接得到副边绕组两端的电压,忽略二极管正向导通压降,副边绕组导通时其两端的电压即为输出电压。所以,原边反馈就是在副边绕组导通时采样辅助绕组两端的电压,并将其反馈到控制芯片中,通过调节占空比进行闭环控制。

5.图1所示开关电源系统中,ac-dc控制芯片00、功率mosfet和电阻rcs为分开的3个器件。ac-dc控制芯片通常采用面积最小化的封装体如sop,而650v耐压的功率mosfet器件m0通常采用体积相对更大的to封装管壳,再加上电阻rcs的固定面积,上述电路在pcb上的平面布局总体上集成度可以进一步提升。若采用系统集成或封装集成技术,将上述ac-dc控制芯片、mosfet器件m0和电阻rcs集成在同一颗封装芯片内,那么上述原边反馈技术的开关电源系统的pcb布局面积将会进一步减小,实现更小体积的ac-dc电源系统。基于此,本发明提供了一种高效率小体积ac-dc电源控制器模块,以实现更小体积的ac-dc开关电源系统。

技术实现要素:

6.本发明在现有技术基础上,提供了一种高效率小体积ac-dc控制器模块。图2为使用本发明ac-dc电源控制器模块技术的开关电源系统框图。本发明的ac-dc电源控制器模块300会将图1中分开的ac-dc控制芯片、功率mosfet和电阻rcs这3个器件,集成在一个模块内

部。整体模块的封装体积比原来3个单独封装体相比,将会有两个改进:一是体积较小,那么采用本发明模块的开关电源系统的pcb布局面积将会进一步减小,实现高的功率密度;二是模块的引脚减小一个,对应的外部电阻减小一个,从而进一步降低ac-dc电源系统的成本。

7.本发明提供的高效率小体积ac-dc电源控制器模块,包括开关输出引脚sw、电源引脚vcc、反馈电压信号引脚fb、地电压引脚vss,其模块内部包括:第一封装基板、第二封装基板,在第一封装基板上焊接有高压功率mosfet晶体管,在第二封装基板上焊接有ac-dc控制芯片;所述高压功率mosfet晶体管的漏极连接到模块的开关输出引脚sw,高压功率mosfet晶体管的栅极连接到ac-dc控制芯片的栅驱动引脚vo,高压功率mosfet晶体管的源极连接到ac-dc控制芯片的输出电流信号引脚cs;所述ac-dc控制芯片的高压电源引脚连接到模块的电源引脚vcc,ac-dc控制芯片的反馈电压信号引脚连接到模块的反馈电压信号引脚fb,ac-dc控制芯片的地电压引脚连接到模块的地电压引脚vss。

8.当高压功率mosfet晶体管的源极位于芯片反面,则高压功率mosfet晶体管的源极通过焊锡连接到第一封装基板,第一封装基板通过引线连接到ac-dc控制芯片的输出电流信号引脚cs,即高压功率mosfet晶体管的源极经过导电性良好的第一封装基板间接连接到ac-dc控制芯片的输出电流信号引脚cs。

9.所述高压功率mosfet晶体管可以采用单颗芯片,也可以采用多颗芯片并联实现;当所述高压功率mosfet晶体管采用多颗芯片并联实现时,需要使用导电基板进行并联连接,每个mosfet晶体管芯片的栅极均连接到共同的导电基板,经过导电基板连接ac-dc控制芯片的栅驱动引脚vo;每个mosfet晶体管芯片的源极连接到共同的导电基板,经过导电基板连接ac-dc控制芯片的输出电流信号引脚cs,或者每个mosfet晶体管芯片的源极通过焊锡连接到第一封装基板,第一封装基板再通过引线连接到ac-dc控制芯片的输出电流信号引脚cs。

10.具体的,所述ac-dc控制芯片包括:电流检测电阻rcs、反馈电压检测电路、原边峰值电流检测模块、反馈电流检测电路、电压电流混合检测电路、参考电压产生电路、第一电压判别电路、第二电压判别电路、电流综合补偿电路、综合比较器、总体功能控制电路、输出驱动模块和保护电路;电流检测电阻rcs连接在开关电源输出电流信号引脚cs和地电压引脚vss之间;所述反馈电压检测电路用于检测开关电源输出的反馈电压fb,并产生检测信号vf;所述原边峰值电流检测模块用于检测开关电源输出电流信号cs,并产生检测信号leb,分别连接到反馈电流检测电路和电压电流混合检测电路;所述反馈电流检测电路用于对检测信号leb进行处理,并产生检测信号vcs2;所述电压电流混合检测电路的输入端连接开关电源输出的反馈电压fb、检测信号leb、检测信号vcs2,用于对反馈电压fb和检测信号leb进行处理,并结合检测信号vcs2产生检测信号vcs1;所述第一电压判别电路的输入端连接检测信号vcs1、电流综合补偿电路反馈的补偿参考电压vrc,用于对检测信号vcs1和补偿参考电压vrc比较得到补偿信号vc1;所述第二电压判别电路的输入端连接开关电源输出的反馈电压fb和电流综合补偿电路反馈的补偿参考电压vrc,对反馈电压fb和补偿参考电压vrc比较得到补偿信号vc2;所述电流综合补偿电路的输入端连接补偿信号vc1、补偿信号vc2、参考电压vadj1,在控制信号ctr4的控制下,将补偿信号vc1、补偿信号vc2、参考电压vref和参考电压vadj1进行补偿处理,得到电流补偿信号vcom;综合比较器的输入端连接电流补偿信号vcom、参考电压vadj2,对电流补偿信号vcom和参考电压vadj2进行比较,得到补偿输出信

号dcom;总体功能控制电路的输入端连接补偿输出信号dcom、检测信号vf、检测信号vcs2、欠压保护信号uvlo、过压保护信号ovp、过温保护信号otp、过流保护信号ocp,总体功能控制电路产生控制信号ctr1~ctr5分别用于控制反馈电压检测电路、反馈电流检测电路、电压电流混合检测电路、电流综合补偿电路和综合比较器的工作状态,并根据检测信号vf、检测信号vcs2、补偿输出信号dcom、欠压保护信号uvlo、过压保护信号ovp、过温保护信号otp以及过流保护信号ocp,综合处理产生脉冲驱动信号vin,输出给输出驱动模块;所述输出驱动模块用于将脉冲驱动信号vin进行电流和电压放大,输出有大电流驱动能力的栅驱动信号vo;所述保护电路10内部包括欠压保护电路、过压保护电路、过温保护电路和过流保护电路,分别产生欠压保护信号uvlo、过压保护信号ovp、过温保护信号otp以及过流保护信号ocp;所述参考电压产生电路的输入端连接到外部高压电源,用于产生可调整的参考电压vadj1和参考电压vadj2,还产生上述所有电路工作需要的片内低压电源和参考信号。

11.所述ac-dc控制芯片上电之后,参考电压产生电路和总体功能控制电路最先工作,然后总体功能控制电路按照先后次序分别输出控制信号ctr1~ctr5,输出控制信号ctr1~ctr5的次序为:首先,同时输出控制信号ctr3、控制信号ctr4和控制信号ctr5,分别控制电压电流混合检测电路、电流综合补偿电路和综合比较器开始工作,使反馈电压fb和检测信号leb形成一个简单控制环路,并输出脉冲驱动信号vin使驱动信号vo输出一个初始输出电压;然后,输出控制信号ctr1和控制信号ctr2,分别控制反馈电压检测电路和反馈电流检测电路开始工作;此时整体ac-dc电源控制器的所有控制环路开启,芯片形成多环路控制模式。

12.具体的,所述总体功能控制电路包括:时钟产生电路、第一数字滤波器、第二数字滤波器、错误处理逻辑、计数器组、判别控制逻辑和寄存器组;所述时钟产生电路产生的高频时钟clk同时输入到第一数字滤波器、第二数字滤波器、计数器组和判别控制逻辑;所述第一数字滤波器在高频时钟clk的控制下,对检测信号vf进行滤波处理,得到补偿数据dc1;所述第二数字滤波器在高频时钟clk的控制下,对检测信号vcs2进行滤波处理,得到补偿数据dc2;所述错误处理逻辑根据欠压保护信号uvlo、过压保护信号ovp、过温保护信号otp以及过流保护信号ocp的情况产生错误信号err;所述计数器组根据判别控制逻辑输出的计数选择信号sel的情况选择计数输出count,并将计数输出count输出给判别控制逻辑;判别控制逻辑的输入端分别连接上述补偿数据dc1、补偿数据dc2、错误信号err、计数输出count以及补偿输出信号dcom,根据各信号状态进行逻辑运算,先产生输出给寄存器组的状态控制信号set,然后综合处理产生脉冲驱动信号vin;

13.电路上电之后,时钟产生电路和错误处理逻辑开始工作,时钟产生电路正常工作后输出高频时钟clk;紧接着,判别控制逻辑先产生第一种状态控制信号set并输出给寄存器组,寄存器组根据第一种状态控制信号set先输出控制信号ctr3、ctr4和ctr5,同时将脉冲驱动信号vin设置为一种固定频率的方波脉冲;紧接着经过一段延时时间td1,待补偿输出信号dcom由初始状态开始改变为脉冲信号时,判别控制逻辑将会解锁脉冲驱动信号vin,使之改为由补偿输出信号dcom控制;然后经过一段延时时间td2,判别控制逻辑产生第二种状态控制信号set并输出给寄存器组,寄存器组根据第二种状态控制信号set输出控制信号ctr1和ctr2,开启其余控制环路;

14.上述判别控制逻辑改变状态控制信号set所依据的延时时间td1、延时时间td2和

延时时间td3,均由判别控制逻辑通过依次提供不同的计数选择信号sel给计数器组进而通过计数器组产生不同计数输出count进行控制。

15.具体的,所述电流综合补偿电路由以下功能部分组成:由pmos管m401、pmos管m402、pmos管m404、电阻r41、电阻r42、nmos管m413、nmos管m414、nmos管m419、nmos管m420、nmos管m428、nmos管m429、电容c41和电容c42构成补偿信号调整电路;由pmos管m405、pmos管m406、pmos管m409、pmos管m410、pmos管m415、pmos管m416、电阻r43、电阻r44、电阻r45、nmos管m421、nmos管m422、nmos管m426、nmos管m427构成补偿信号放大电路;由pmos管m407、pmos管m408、pmos管m411、pmos管m412、nmos管m417、nmos管m418、nmos管m423、nmos管m424、nmos管m425、电容c43、电容c44、电阻r46构成补偿输出电路;剩余部分电路构成一个单位增益缓冲器,包括:pmos管m430栅极连接到参考电压vref;pmos管m431栅极、pmos管m432栅极、pmos管m433栅极连接偏置电压vbc43,nmos管m441栅极连接偏置电压vbc44;pmos管m430漏极连接电阻r47上端和pmos管m435栅极;pmos管m431漏极连接pmos管m435源极和pmos管m436源极;pmos管m435漏极连接nmos管m438漏极、nmos管m438栅极、nmos管m439栅极;pmos管m436漏极连接nmos管m439漏极、nmos管m440栅极、电阻r48上端,电阻r48下端连接电容c45上端;pmos管m432漏极与nmos管m440漏极相连,并连接到nmos管m437源极;pmos管m433漏极连接nmos管m437栅极、nmos管m437漏极、nmos管m434栅极;nmos管m434源极连接nmos管m441漏极、pmos管m436栅极,并作为电流补偿信号vcom输出端,还反馈连接到电容c43上端、nmos管m424的漏极;pmos管m430源极、pmos管m431源极、pmos管m432源极、pmos管m433源极和nmos管m434漏极同时连接到电源电压vccl;nmos管m438源极、nmos管m439源极、nmos管m440源极、nmos管m441源极、电阻r47下端、电容c45下端同时连接到地电压vss。

16.具体的,所述电压电流混合检测电路内部包括:单位增益放大器、分压电路、可变增益运算放大器和同相加法运算放大器电路,单位增益放大器将反馈电压fb信号进行隔离缓冲输出电压信号vf_in,连接到同相加法运算放大器电路;分压电路对信号leb进行电流转电压转换,输出电压vc_det,连接到可变增益运算放大器,经可变增益运算放大器转换放大得到电压信号vc_in,再连接到同相加法运算放大器电路;同相加法运算放大器电路对电压信号vf_in和vc_in求和,输出最终的检测信号vcs1。

17.具体的,所述保护电路包括:温度检测电路的输入端连接第一钳位电路构成温度检测支路,电流检测电路的输入端连接第二钳位电路构成电流检测支路,第一电压检测电路的输入端连接第三钳位电路构成欠压检测支路,第二电压检测电路的输入端连接第四钳位电路构成过压检测支路;所述温度检测电路、电流检测电路、第一电压检测电路、第二电压检测电路的输出端均连接检测输入开关选择电路,检测输入开关选择电路的输出端依次连接高精度比较器、整形缓冲电路、检测输出开关选择电路;所述检测输出开关选择电路输出过温保护信号otp、温度锁定信号otlock、过流保护信号ocp、过流锁定信号oclock、欠压保护信号uvlo、欠压锁定信号uvlock、过压保护信号ovp和过压锁定信号ovlock,其中温度锁定信号otlock连接到第一钳位电路的输入端,过流锁定信号oclock连接到第二钳位电路的输入端,欠压锁定信号uvlock连接到第三钳位电路的输入端,过压锁定信号ovlock连接到第四钳位电路的输入端;

18.所述第一钳位电路根据温度锁定信号otlock的状态提供偏置电压vbt,并输出给温度检测电路,温度检测电路根据偏置电压vbt得到温度检测输出信号vint;所述第二钳位

电路根据过流锁定信号oclock的状态提供偏置电压vbc,并输出给电流检测电路,电流检测电路根据偏置电压vbc得到电流检测输出信号vinc;所述第三钳位电路根据欠压锁定信号uvlock的状态提供偏置电压vbl,并输出给电流检测电路,电流检测电路根据偏置电压vbc得到欠压检测输出信号vinl;所述第四钳位电路根据过压锁定信号ovlock的状态提供偏置电压vbh,并输出给电流检测电路,电流检测电路根据偏置电压vbh得到过压检测输出信号vinh;

19.所述温度检测输出信号vint、电流检测输出信号vinc、欠压检测输出信号vinl、过压检测输出信号vinh同时进入检测输入开关选择电路,经开关选择控制信号selp选择,输出检测信号vind;所述开关选择控制信号selp共有4种开关状态,状态一时温度检测输出信号vint选通并连接到检测信号vind,状态二时电流检测输出信号vinc选通并连接到检测信号vind,状态三时欠压检测输出信号vinl选通并连接到检测信号vind,状态四时过压检测输出信号vinh选通并连接到检测信号vind;所述高精度比较器将检测信号vind和内部参考信号进行比较,得到比较输出信号vo;整形缓冲电路将比较输出信号vo进行处理得到保护信号op和保护锁定信号opl,同时连接检测输出开关选择电路的输入端;经开关选择控制信号selp选择,状态一时保护信号op和保护锁定信号opl选通分别连接过温保护信号otp和温度锁定信号otlock,状态二时选通分别连接过流保护信号ocp和过流锁定信号oclock,状态三时选通分别连接欠压保护信号uvlo和欠压锁定信号uvlock,状态四时选通分别连接过压保护信号ovp和过压锁定信号ovlock。

20.具体的,所述高精度比较器包括:pmos管m121栅极连接偏置电压,pmos管m121漏极连接nmos管m122漏极、nmos管m122栅极、nmos管m123栅极、nmos管m128栅极和nmos管m129栅极;nmos管m123漏极连接pmos管m124漏极、pmos管m124栅极、pmos管m125栅极;pmos管m125漏极连接pmos管m126源极和pmos管m127源极;pmos管m126栅极连接到高精度比较器的参考电压;pmos管m127栅极为比较电压输入端,连接vind;pmos管m126漏极连接nmos管m129漏极和nmos管m1210栅极;pmos管m127漏极连接nmos管m128漏极和nmos管m1214栅极;pmos管m1211漏极连接nmos管m1210漏极和pmos管m1212栅极;pmos管m1212漏极连接pmos管m1211的栅极、nmos管m1214漏极、pmos管m1213栅极和nmos管m1215栅极;pmos管m1213漏极连接nmos管m1215的漏极、电阻r121上端和电容c121上端,并作为信号vo输出端;nmos管m122源极、nmos管m123源极、nmos管m128源极、nmos管m129源极、nmos管m1210源极、nmos管m1214源极、nmos管m1215源极、电阻r121下端和电容c121下端均连接到地电压vss;pmos管m121源极、pmos管m124源极、pmos管m125源极、pmos管m1211源极、pmos管m1212源极、pmos管m1213源极均连接到电源电压vccl。

21.本发明的优点是:所提供的高效率小体积ac-dc电源控制器模块,在现有技术基础上,首先将ac-dc控制芯片、功率mosfet和电阻rcs进行封装集成实现体积优化,减小开关电源系统的pcb布局面积实现高功率密度,并减少了外部引脚和外部电阻,进一步降低系统成本;另一方面,本发明对ac-dc控制芯片进行效率优化,增加了电压电流混合检测控制环路和多环路控制逻辑,提高反馈信号控制精度和响应速度的同时,保持ac-dc控制器的稳定性,对各环路的工作模式和状态进行精确控制,最终实现更高效率。本发明与现有技术相比有明显的效率和体积优势,可以广泛应用于各类ac-dc开关电源系统中。

附图说明

22.图1为典型原边反馈技术的开关电源系统框图。

23.图2为采用本发明技术的开关电源系统框图。

24.图3a为本发明封装结构的实施例一。

25.图3b为本发明封装结构的实施例二。

26.图3c为本发明封装结构的实施例三。

27.图3d为本发明封装结构的实施例四。

28.图4为典型原边反馈ac-dc控制器内部框图。

29.图5为本发明ac-dc控制芯片的电路结构框图。

30.图6为本发明电流综合补偿电路原理图。

31.图7为本发明电压判别电路原理图。

32.图8为本发明电压电流混合检测电路的一种实施例。

33.图9为本发明总体功能控制电路的电路结构框图。

34.图10a为本发明保护电路的一种实施例结构框图。

35.图10b为本发明保护电路的另一种实施例结构框图。

36.图11为本发明钳位电路的一种实施例。

37.图12为本发明高精度比较器的一种实施例。

38.图13为本发明整形缓冲电路的一种实施例。

具体实施方式

39.下面结合附图和实施例对本发明进行进一步详细的说明。

40.本发明的电源控制器模块外部引脚包括:开关输出引脚sw、电源引脚vcc、反馈电压信号引脚fb和地电压引脚vss。本文中,引脚的字母名称采用该引脚传输的信号名称。

41.图3a为本发明的一种封装结构。所述高效率小体积ac-dc电源控制器模块300内部包括第一封装基板31、第二封装基板32、焊接在第一封装基板31上的高压功率mosfet晶体管301和焊接在第二封装基板32上的ac-dc控制芯片302;所述高压功率mosfet晶体管301的漏极连接到高效率小体积ac-dc电源控制器模块300的开关输出引脚sw,所述高压功率mosfet晶体管301的栅极连接到ac-dc控制芯片302的栅驱动引脚vo,所述高压功率mosfet晶体管301的源极连接到ac-dc控制芯片302的输出电流信号cs引脚;所述ac-dc控制芯片302的高压电源vcc引脚连接到ac-dc电源控制器模块300的电源引脚vcc,所述ac-dc控制芯片302的反馈电压信号fb引脚连接到ac-dc电源控制器模块300的反馈电压信号fb引脚,所述ac-dc控制芯片302的地电压引脚vss连接到ac-dc电源控制器模块300的地电压引脚vss。

42.由于功率mosfet的漏极和源极需要流过大电流,因此两个引脚和外部的连线必须采用多根绑定线才能满足需求。图3a中给出的方案,适合于功率mosfet的栅极、漏极和源极3个电极全部在一个正面的器件类型,当所采用的功率mosfet的3个电极不在同一个正面时,则需要对上述方案进行一定修改。图3b为本发明适用于功率mosfet的栅极、漏极和源极不在同一个正面情况下的另一种模块结构图。例如功率mosfet采用vdmos结构,则栅极和漏极在正面,而源极在芯片的反面,功率mosfet芯片需要采用焊锡将其源极焊接到第一封装基板31上,此时第一封装基板31变为功率mosfet芯片的源极,同时第一封装基板31必须具

备优良的导电性才能满足要求。

43.在功率半导体器件应用中,为增大输出电流能力,通常采用多个功率器件并联的方式来增大功率输出,因此本发明还给出了多个功率mosfet并联使用的情况下的控制器模块结构。图3c给出的方案适合于多个功率mosfet的栅极、漏极和源极3个电极全部在一个正面的器件类型,图3d给出的方案适合于多个功率mosfet的栅极和漏极在正面,而源极在芯片的反面的器件类型。

44.图3b所示的ac-dc电源控制器模块300内部包括第一封装基板31、第二封装基板32、焊接在第一封装基板31上的高压功率mosfet晶体管301、给第一封装基板31和高压功率mosfet晶体管301提供连接的焊锡303和焊接在第二封装基板32上的ac-dc控制芯片302;所述高压功率mosfet晶体管301的漏极连接到ac-dc电源控制器模块300的开关输出引脚sw,所述高压功率mosfet晶体管301的栅极连接到ac-dc控制芯片302的栅驱动引脚vo,所述高压功率mosfet晶体管301的源极通过焊锡303连接第一封装基板31,然后第一封装基板31通过引线连接到ac-dc控制芯片302的输出电流信号cs引脚;所述ac-dc控制芯片302的高压电源vcc引脚连接到ac-dc电源控制器模块300的电源引脚vcc,所述ac-dc控制芯片302的反馈电压信号fb引脚连接到ac-dc电源控制器模块300的反馈电压信号fb引脚,所述ac-dc控制芯片302的地电压引脚vss连接到ac-dc电源控制器模块300的地电压引脚vss。

45.图3c所示的结构则包括第一封装基板31、第二封装基板32、第一导电基板33、第二导电基板34、焊接在第一封装基板31上的第一高压功率mosfet晶体管和第二高压功率mosfet晶体管、焊接在第二封装基板32上的ac-dc控制芯片;第一、第二高压功率mosfet晶体管的漏极均连接到ac-dc电源控制器模块300的开关输出引脚sw;第一、第二高压功率mosfet晶体管的栅极均连接到第一导电基板33,第一导电基板33还连接到所述ac-dc控制芯片302的栅驱动引脚vo;第一、第二高压功率mosfet晶体管的源极均连接到第二导电基板34,第二导电基板34还连接到所述ac-dc控制芯片302的输出电流信号cs引脚;ac-dc控制芯片302的高压电源vcc引脚连接到ac-dc电源控制器模块300的电源引脚vcc,所述ac-dc控制芯片302的反馈电压信号fb引脚连接到ac-dc电源控制器模块300的反馈电压信号fb引脚,所述ac-dc控制芯片302的地电压引脚vss连接到ac-dc电源控制器模块300的地电压引脚vss。

46.图3c给出的方案中,第一导电基板33用于将第一高压功率mosfet晶体管的栅极、第二高压功率mosfet晶体管的栅极和ac-dc控制芯片302的栅驱动引脚vo之间进行连接过渡;第二导电基板34用于将第一高压功率mosfet晶体管的源极、第二高压功率mosfet晶体管的源极和ac-dc控制芯片302的输出电流信号引脚cs之间进行连接过渡。主要起2个方面的改进工作,一是减少引线长度和保持每根引线长度相当,减小寄生电感的影响;二是方便进一步扩展功率mosfet的并联使用个数,很容易进行并联扩展使用。图3c给出的方案中仅给出了2个功率mosfet的并联使用的方案,采用相同的策略,很容易扩展到更多的功率mosfet的并联使用。

47.图3d为本发明高效率小体积ac-dc电源控制器模块的第四种结构图。该ac-dc电源控制器模块300内部包括第一封装基板31、第二封装基板32、第一导电基板33、焊接在第一封装基板31上的第一高压功率mosfet晶体管和第二高压功率mosfet晶体管、给第一封装基板31和第一高压功率mosfet晶体管提供连接的第一焊锡305、给第一封装基板31和第二高

压功率mosfet晶体管提供连接的第二焊锡304、焊接在第二封装基板32上的ac-dc控制芯片302;第一、第二高压功率mosfet晶体管的漏极均连接到ac-dc电源控制器模块300的开关输出引脚sw;第一、第二高压功率mosfet晶体管的栅极连接到第一导电基板33,第一导电基板33还连接到所述ac-dc控制芯片302的栅驱动引脚vo;第一高压功率mosfet晶体管的源极通过第一焊锡305连接第一封装基板31,第二高压功率mosfet晶体管的源极通过第二焊锡304连接第一封装基板31,然后第一封装基板31通过引线连接到所述ac-dc控制芯片302的输出电流信号cs引脚;ac-dc控制芯片302的高压电源vcc引脚连接到ac-dc电源控制器模块300的电源引脚vcc,ac-dc控制芯片302的反馈电压信号fb引脚连接到ac-dc电源控制器模块300的反馈电压信号fb引脚,ac-dc控制芯片302的地电压引脚vss连接到ac-dc电源控制器模块300的地电压引脚vss。

48.如图4所示为常用原边反馈ac-dc控制芯片的内部框图,其中包含了电源模块40、恒压控制模块41、输出驱动模块42、恒流控制模块43、原边峰值电流检测模块44、控制模块45以及芯片的各种辅助模块。由于整体控制器芯片输出还提供具有大电流驱动能力的gate输出信号,为了保障gate输出高压功率器件栅极电容能快速充放电,使器件迅速的饱和导通和可靠关断,要求输出驱动电路的输出阻抗小,输出电流大(安培级)。因此需要集成保护电路模块46用于对芯片的状态进行监测,以避免异常情况对输出控制对象造成损坏,典型保护电路有欠压保护、过压保护、过温保护和过流保护等。图4所示的现有解决方案中,控制模块42用于根据恒压开启信号cv_ctrl、恒流开启信号cc_ctrl、峰值电流检测信号leb,产生用于输出驱动外部功率管脉冲信号vin,然后经输出驱动进行打压及电流放大得到输出栅控制信号vo。其中,恒压开启信号cv_ctrl和恒流开启信号cc_ctrl均为数字信号,由开关电源的输出电压反馈信号fb单独产生;峰值电流检测信号leb为模拟信号,由开关电源的输出电流反馈信号cs单独产生。

49.上述控制系统中,输出电压反馈信号(对应本发明的反馈电压信号fb)和输出电流反馈信号(对应本发明的输出电流信号cs)两个模拟信号之间无直接关联,而实际的开关电源系统中fb和cs二者之间存在直接密切的联系,若能在芯片控制环路中,将fb和cs两个模拟信号直接进行一定的关联,引入新的控制环路,势必可以增加ac-dc控制器的控制精度。但是引入新的控制环路后,控制模式相比要复杂不少,容易造成谐波震荡,影响系统稳定性,因此需要通过更严格的控制技术来消除这种风险。

50.如图5所示,本发明的ac-dc控制芯片302包括:电流检测电阻rcs、反馈电压检测电路1、原边峰值电流检测模块2、反馈电流检测电路3、电压电流混合检测电路4、参考电压产生电路5、第一电压判别电路6、第二电压判别电路7、电流综合补偿电路9、综合比较器10、总体功能控制电路11、输出驱动模块12和保护电路13。

51.所述电流检测电阻rcs连接在开关电源输出电流信号cs和地电压vss之间;所述反馈电压检测电路1用于检测开关电源输出的反馈电压fb,并产生检测信号vf;所述原边峰值电流检测模块2用于检测开关电源输出电流信号cs,并产生检测信号leb;所述反馈电流检测电路3用于对检测信号leb进行处理,并产生检测信号vcs2;所述电压电流混合检测电路4用于对开关电源输出的反馈电压fb和检测信号leb进行处理,并结合检测信号vcs2产生检测信号vcs1。

52.所述第一电压判别电路6对检测信号vcs1和电流综合补偿电路9反馈的补偿参考

电压vrc比较得到补偿信号vc1;所述第二电压判别电路7对开关电源输出后的反馈电压fb和电流综合补偿电路9反馈的的补偿参考电压vrc比较得到补偿信号vc2;所述电流综合补偿电路9在控制信号ctr4的控制下,将补偿信号vc2、补偿信号vc1、参考电压vref和参考电压vadj1进行补偿处理,并得电流补偿信号vcom;综合比较器10对电流补偿信号vcom和参考电压vadj2进行比较,得到补偿输出信号dcom。

53.总体功能控制电路11产生控制信号ctr1~ctr5分别用于控制反馈电压检测电路1、反馈电流检测电路3、电压电流混合检测电路4、电流综合补偿电路9和综合比较器10的工作状态,并根据检测信号vf、检测信号vcs2、补偿输出信号dcom、欠压保护信号uvlo、过压保护信号ovp、过温保护信号otp以及过流保护信号ocp,综合处理产生脉冲驱动信号vin。所述输出驱动模块用于将脉冲驱动信号vin进行电流和电压放大,输出有大电流驱动能力的栅驱动信号vo。所述保护电路13其内部包括欠压保护电路、过压保护电路、过温保护电路和过流保护电路,分别产生欠压保护信号uvlo、过压保护信号ovp、过温保护信号otp以及过流保护信号ocp,并全部输出给总体功能控制电路11。所述参考电压产生电路5连接到外部高压电源,产生可调整的参考电压vadj1和参考电压vadj2,还产生上述所有电路工作需要的片内低压电源和参考信号。

54.所述第一电压判别电路6和第二电压判别电路7采用相同的电压判别电路实现。

55.本发明所提供的ac-dc控制芯片提供了多个反馈控制环路,提高ac-dc电源控制器的反馈控制精度和效率。首先,开关电源输出后的反馈电压fb改为同时由反馈电压检测电路1控制、电压电流混合检测电路4和第二电压判别电路7等3个环路同时处理;其次,开关电源输出电流信号cs经检测得到的leb信号,由反馈电流检测电路3和电压电流混合检测电路4同时处理,提供输出电流检测功能。由于增加了控制环路,为保持控制器的稳定性,需要总体功能控制电路对各环路的工作模式和状态进行精确控制。

56.图5所示电路中,反馈电压fb经反馈电压检测电路1产生的检测信号vf和检测信号leb经反馈电流检测电路3产生的检测信号vcs2均为逻辑电平信号,并直接进入总体功能控制电路11。整体ac-dc控制芯片上电之后,参考电压产生电路5和总体功能控制电路11最先工作,然后总体功能控制电路11按照先后次序分别输出控制信号ctr1~ctr5,并按照先后优先次序分别用于控制反馈电压检测电路1、反馈电流检测电路3、电压电流混合检测电路4、电流综合补偿电路9和综合比较器10的工作状态。总体功能控制电路11输出控制信号ctr1~ctr5的先后优先次序为:首先,同时输出控制信号ctr3、控制信号ctr4和控制信号ctr5,分别控制电压电流混合检测电路4、电流综合补偿电路9和综合比较器10开始工作,使反馈电压fb和检测信号leb形成一个简单控制环路,并输出脉冲驱动信号vin使vo输出一个初始输出电压;其次,输出控制控制信号ctr1和控制信号ctr2,分别控制反馈电压检测电路1和反馈电流检测电路3开始工作;此时整体ac-dc电源控制器的所有控制环路开启,芯片形成多环路控制模式。

57.如图6所示,所述电流综合补偿电路9自左向右大致分为4个功能电路:pmos管m401、pmos管m402、pmos管m404、电阻r41、电阻r42、nmos管m413、nmos管m414、nmos管m419、nmos管m420、nmos管m429、nmos管m428、电容c41和电容c42构成补偿信号调整电路;pmos管m405、pmos管m406、pmos管m409、pmos管m410、pmos管m415、pmos管m416、电阻r43、电阻r44、电阻r45、nmos管m421、nmos管m422、nmos管m427、nmos管m426、nmos管m429、nmos管m428、电

容c41和电容c42构成补偿信号放大电路;pmos管m407、pmos管m408、pmos管m411、pmos管m412、nmos管m417、nmos管m418、nmos管m423、nmos管m424、nmos管m425和电容c44构成补偿输出电路,pmos管m407、pmos管m408、pmos管m411和pmos管m412组成共源共栅镜像电流源电路;最右侧的电路中,pmos管m431、m432、m435、m436和nmos管m438、m439、m440构成一个两级运算放大器;nmos管m434和nmos管m441构成一个源跟随器,nmos管m434的偏置点信号需要比较高的电压,所以两级运算放大器的输出端连接了一个由m433和m437构成的电平移位电路,然后在输出到nmos管m434的栅端;nmos管m434和m441构成的源跟随器的输出即为电流综合补偿电路9的电流补偿信号vcom输出端,该输出端重新连接到两级运算放大器的输入端,使得右侧总体电路构成一个单位增益缓冲器。参考电压vref经过pmos管m430和电阻r47构成输入偏置电路,输入偏置电路的输出点为m435的栅端。

58.具体电路连接关系如下。

59.pmos管m401、pmos管m402、pmos管m404、电阻r41、电阻r42、nmos管m413、nmos管m414、nmos管m419、nmos管m420、nmos管m429、nmos管m428、电容c41和电容c42构成补偿信号调整电路;pmos管m401的漏极和栅极相连,并作为偏置输入信号ibc41的输入端,还连接到pmos管m402、pmos管m404的栅极和、电容c41下端;pmos管m402的漏极连接到nmos管m419的漏极和栅极、nmos管m420栅极、nmos管m429漏极;pmos管m404的漏极连接到nmos管m420的漏极、nmos管m413的源极、nmos管m414的源极和电阻r44的左端,还作为补偿参考电压vrc的输出端;nmos管m413的漏极连接到电阻r41的下端,nmos管m413的栅极连接到补偿信号vc1,nmos管m414的漏极连接到电阻r42的下端,nmos管m414的栅极连接到补偿信号vc2;pmos管m401的源极、pmos管m402的源极、pmos管m404的源极、电容c41上端、电阻r41上端和电阻r42上端均连接到电源电压vccl;nmos管m419源极、nmos管m420源极、nmos管m428源极、nmos管m429源极、电容c42下端均连接地电压vss;电容c41和电容c42为滤波电容,nmos管m429和nmos管m428为受复位信号s1控制的复位晶体管。

60.pmos管m405、pmos管m406、pmos管m409、pmos管m410、pmos管m415、pmos管m416、电阻r43、电阻r44、电阻r45、nmos管m421、nmos管m422、nmos管m427、nmos管m426、nmos管m429、nmos管m428、电容c41和电容c42构成补偿信号放大电路;pmos管m405、pmos管m406、pmos管m409、pmos管m410和电阻r43构成自偏置共源共栅镜像电流源电路,电阻r43的下端作为偏置输入信号ibc42的输入端,还连接pmos管m409栅极、pmos管m410栅极、pmos管m411栅极、pmos管m412栅极,电阻r43上端连接pmos管m409漏极、pmos管m405栅极、pmos管m406栅极,pmos管m409源极连接pmos管m405漏极,pmos管m406漏极连接pmos管m410源极;pmos管m406和pmos管m410构成共源共栅电流源,pmos管m410的漏极连接到pmos管m415的源极和pmos管m416的源极,pmos管m415的栅极连接到电阻r44的右端和电阻r46的下端,pmos管m416的栅极连接到电阻r45的左端,r45的右端即为电流综合补偿电路9的调制参考信号vadj1,pmos管m415的漏极连接到nmos管521的漏极和栅极及nmos管m423栅极、nmos管m427漏极,pmos管m416的漏极连接到nmos管522的漏极和栅极及nmos管m424栅极,nmos管m427和nmos管m426为受复位信号s1控制的复位晶体管;pmos管m405源极、pmos管m406源极均连接到电源电压vccl;nmos管m421源极、nmos管m422源极、nmos管m426源极、nmos管m427源极均连接地电压vss。

61.pmos管m407、pmos管m408、pmos管m411、pmos管m412、nmos管m417、nmos管m418、

nmos管m423、nmos管m424、nmos管m425、电容c43、电容c44、电阻r46构成补偿输出电路,pmos管m407、pmos管m408、pmos管m411和pmos管m412组成共源共栅镜像电流源电路,pmos管m407栅极连接pmos管m408栅极、pmos管m411漏极、pmos管m417漏极,pmos管m407漏极连接pmos管m411源极,pmos管m408漏极连接pmos管m412源极,pmos管m411的漏极和pmos管m412的漏极为共源共栅镜像电流源的输出端;pmos管m411的漏极连接到nmos管m417的漏极,nmos管m417栅极连接偏置电压vbc41;pmos管m412的漏极连接到nmos管m418的漏极和栅极,并作为电流补偿信号vcom输出端,还连接到电容c43的上端、nmos管m424的漏极、nmos管m425漏极、电容c43上端、电容c44上端;电容c43的下端连接到电阻r46的上端;nmos管m417的源极连接到nmos管m423的漏极和nmos管m418的源极;nmos管m425为受复位信号s1控制的复位晶体管;电容c44为滤波电容;pmos管m407源极、pmos管m408源极均连接到电源电压vccl;nmos管m423源极、nmos管m424源极、nmos管m425源极、电容c44下端均连接地电压vss。

62.pmos管m430栅极连接到参考电压vref;pmos管m431、pmos管m432、pmos管m433的栅极连接到偏置电压vbc43,nmos管m441的栅极连接到偏置电压vbc44;pmos管m430漏极同时连接到电阻r47的上端和pmos管m435的栅极;pmos管m431的漏极同时连接pmos管m435和pmos管m436的源极;pmos管m435的漏极与nmos管m438的漏极相连,同时连接nmos管m439和nmos管m438的栅极;pmos管m436的漏极和nmos管m439漏极相连,同时连接到nmos管m440的栅极,以及电阻r48的上端,电阻r48的下端连接电容c45的上端;pmos管m432的漏极与nmos管m440的漏极相连,并连接到nmos管m437的源极;pmos管m433的漏极与nmos管m437的栅极和漏极相连,同时连接nmos管m434的栅极;nmos管m434的源极和nmos管m441的漏极相连,同时连接到pmos管m436的栅极,该端作为电流补偿信号vcom输出端,还反馈连接到电容c43的上端、nmos管m424的漏极;pmos管m430、pmos管m431、pmos管m432、pmos管m433的源极和nmos管m434漏极同时连接到电源电压vccl;nmos管m438、nmos管m439、nmos管m440、nmos管m441的源极和电阻r47的下端,电容c45的下端同时连接到地电压vss。

63.图6所示的本发明电流综合补偿电路9首先通过补偿信号调整电路将补偿信号vc2和补偿信号vc1转换为补偿参考电压vrc,补偿参考电压vrc一方面输出给本发明前面所述的2个电压判别电路,另一方面输入到补偿信号放大电路的左输入端;补偿信号放大电路的右输入端为调制参考信号vadj1,补偿信号放大电路将补偿参考电压vrc和调制参考信号vadj1的差值进行放大,并转换为电流补偿信号vcom;电流补偿信号vcom一方面输出,另一方面还通过电容c43和电阻r46反馈到补偿信号放大电路的左输入端,形成交流信号的缓冲器结构;电流补偿信号vcom最终还经过图6右侧的单位增益缓冲器缓冲输出得到电流综合补偿电路9的电流补偿信号vcom。

64.图7为本发明电压判别电路的一种实施例。该电路包含pmos管m71、pmos管m72、pmos管m73、pmos管m74、pmos管m75、pmos管m76、pmos管m77、pmos管m711、pmos管m712、pmos管m715、nmos管m78、nmos管m79、nmos管m710、nmos管m713、nmos管m714、nmos管m716、电阻r71和电容c71。

65.其中,pmos管m72、pmos管m73、pmos管m76、pmos管m77、nmos管m78、nmos管m79、nmos管m710构成一个两级比较器;pmos管m711、pmos管m712、pmos管m715、nmos管m713、nmos管m714、nmos管m716构成一个输出整形电路;电阻r71和电容c71构成的一个低通滤波器;两级比较器的一个输入端连接电流综合补偿电路的输出信号vrc,输入待判别信号vi经过低通

滤波器后连接到两级比较器的另一个输入端,两级比较器的输出连接到输出整形电路进行信号整形,得到电压判别电路输出信号out;pmos管m71、pmos管m74、pmos管m75用于产生电压判别电路的迟滞量;

66.所述pmos管m71的栅极、pmos管m72的栅极、pmos管m73的栅极、pmos管m74的栅极连接偏置电压vbc71,pmos管m71的源极、pmos管m72的源极、pmos管m73的源极、pmos管m711的源极接电源电压vccl;pmos管m71的漏极连接到pmos管m74的源极;pmos管m74的漏极连接到pmos管m75的源极;pmos管m75的漏极和pmos管m76的漏极、nmos管m78的漏极相连,且同时连接到nmos管m79和m78的栅极;pmos管m72的漏极同时连接到pmos管m76、pmos管m77的源极;pmos管m77的漏极和nmos管m79的漏极相连,且同时连接到nmos管m710的栅极;pmos管m76的栅极连接补偿参考电压vrc;pmos管m77的栅极同时连接到电阻r71的右端和电容c71的上端;电阻r71的左端连接输入待判别信号vi;pmos管m73的漏极与nmos管m710的漏极相连,还连接到pmos管m711的栅极和nmos管m713的栅极;pmos管m711的漏极连接到pmos管m712的源极;pmos管m712的漏极连接到nmos管m713的漏极和nmos管m714的漏极,还连接到pmos管m715的栅极和nmos管m716的栅极,另外还连接到pmos管m75的栅极;pmos管m715的漏极和nmos管m716的漏极相连,还作为电压判别电路输出信号out;pmos管m712的栅极和nmos管m714的栅极作为复位信号s1的输入端;nmos管m78的源极、nmos管m79的源极、nmos管m710的源极、nmos管m713的源极、nmos管m714的源极、nmos管m716的源极和电容c51的下端同时连接到地电压vss。

67.图7所示的电压判别电路中,当输入待判别信号vi低于补偿参考电压vrc时,两级比较器输出高电平,对应得到电压判别电路输出信号out也为高电平,此时pmos管m71、pmos管m74、pmos管m75的迟滞量不起作用;当输入待判别信号vi大于补偿参考电压vrc时,两级比较器输出改为低电平,对应得到比较器输出信号out也改为低电平,此时pmos管m71、pmos管m74、pmos管m75构成的迟滞量开始起作用,m75导通,增大m78的电流和栅压,进一步拉低两级比较器的输出,此时输入待判别信号vi若要将输出信号out的低电平重新改为高电平,则需要比补偿参考电压vrc高一个迟滞量才行。上述过程迟滞量取决于m71和m72的比例,m71尺寸越大,则迟滞量越大。

68.图8为本发明电压电流混合检测电路4的一种实施例。该电路用于将反馈电压信号fb和反馈电流信号leb进行处理,并最终形成一个综合的补偿信号vcs1。所述电压电流混合检测电路内部包括单位增益放大器80、分压电路81、可变增益运算放大器82和同相加法运算放大器电路83,单位增益放大器80将fb信号进行隔离缓冲得到电压信号vf_in,分压电路81对反馈电流信号leb进行电流转电压转换,得到电压vc_det,经分可变增益运算放大器82转换放大得到电压信号vc_in,同相加法运算放大器电路83对电压信号vf_in和vc_in求和,得到最终的检测信号vcs1。可变增益运算放大器82可以采用现有的成熟vga技术实现。

69.图9为本发明总体功能控制电路11的内部框图,所述总体功能控制电路11包括时钟产生电路90、第一数字滤波器91、第二数字滤波器92、错误处理逻辑93、计算器组94、判别控制逻辑95和寄存器组96;所述时钟产生电路90产生的高频时钟clk同时输入到第一数字滤波器91、第二数字滤波器92、计算器组94和判别控制逻辑95;所述第一数字滤波器91在高频时钟clk的控制下,对检测信号vf进行滤波处理,得到补偿数据dc1;所述第二数字滤波器92在高频时钟clk的控制下,对检测信号vcs2进行滤波处理,得到补偿数据dc2;所述错误处

理逻辑93根据欠压保护信号uvlo、过压保护信号ovp、过温保护信号otp以及过流保护信号ocp的情况产生错误信号err;所述计算器组94根据判别控制逻辑95输入的计数选择信号sel情况选择计算器组计数输出count,并将计数输出count输出给判别控制逻辑95;判别控制逻辑95,根据计数输出count、补偿数据dc1、补偿数据dc2、补偿输出信号dcom和错误信号err的状态,先产生输出给寄存器组的状态控制信号set,后综合处理产生脉冲驱动信号vin。

70.本发明所述ac-dc控制芯片上电后,总体功能控制电路11中首先开始正常工作的是时钟产生电路90和错误处理逻辑93;时钟产生电路90正常工作后输出高频时钟clk同时输入到第一数字滤波器91、第二数字滤波器92、计算器组94和判别控制逻辑95;紧接着,判别控制逻辑95先产生第一种状态控制信号set并输出给寄存器组,寄存器组根据第一种状态控制信号set先输出控制信号ctr3、控制信号ctr4和控制信号ctr5,同时将脉冲驱动信号vin设置为一种固定频率的方波脉冲;紧接着经过一段延时时间td1,待补偿输出信号dcom由初始状态开始改变为脉冲信号时,判别控制逻辑95将会解锁脉冲驱动信号vin,使之改为由补偿输出信号dcom控制;然后经过一段延时时间td2,判别控制逻辑95产生第二种状态控制信号set并输出给寄存器组,寄存器组根据第二种状态控制信号set输出控制信号ctr1和控制信号ctr2,此时所述ac-dc控制芯片的所有控制环路开启。

71.上述判别控制逻辑95改变状态控制信号set所依据的延时时间td1和延时时间td2,均由判别控制逻辑95通过依次提供不同的计数选择信号sel进而产生不同计算器组计数输出count进行控制。

72.本发明总体功能控制电路11的一种典型控制过程如下:所述ac-dc控制芯片上电后,时钟产生电路90产生一种10mhz的时钟信号clk;紧接着,判别控制逻辑95先输出计数选择信号sel=“0000”使计算器组开始计数,同时产生第一种状态控制信号set=“00”,输出控制信号ctr3、ctr4和ctr5,分别控制电压电流混合检测电路4、电流综合补偿电路9和综合比较器10开始正常工作,将脉冲驱动信号vin设置为100khz的脉冲信号;紧接着,当计算器组第一次计数10000个周期(即1ms)时count状态改变,并且待补偿输出信号dcom由初始状态开始改变为脉冲信号后,判别控制逻辑95将会解锁脉冲驱动信号vin,使之改为由dcom控制,同时复位count信号,并输出计数选择信号sel=“0001”使计算器组重新开始计数;然后,当计算器组计数100000个周期(即10ms)时count状态再次改变,判别控制逻辑95将会产生第二种状态控制信号set=“01”,寄存器组此时输出控制信号ctr1和控制信号ctr2,分别控制反馈电压检测电路1和反馈电流检测电路3开始工作,判别控制逻辑95将会复位count信号,并输出计数选择信号sel=“0010”使计算器组重新开始计数;此时整体ac-dc控制芯片的所有控制环路开启,芯片形成多环路控制模式,脉冲驱动信号vin将会同时由补偿数据dc2、补偿数据dc1和补偿输出信号dcom进行控制。

73.本发明所述总体功能控制电路11中,第一、第二数字滤波器为相同的电路功能模块,可以采用现有的各种数字滤波实现技术实现,其功能是将vf和vcs2中的异常波动脉冲信号滤除,使得补偿数据dc2和补偿数据dc1具有更好的鲁棒性。所述判别控制逻辑95为整个ac-dc控制芯片工作控制核心电路,全部为数字逻辑电路,其实现方式多种多样,最普通的实现方式为状态机控制实现,而要实现更高的控制精度可以采用dsp内核或者mcu进行控制,当然硬件开销会增加不少。

74.图9中用到的错误处理逻辑电路93通常由组合逻辑门构成,作用在于综合芯片状态监测信号,对电路是否正常做出判断,当芯片异常时关断数据输出,现有的各种公开技术已经可以提供各种解决。任何时间错误输出信号err出现低电平,整个ac-dc控制芯片都会进入复位模式,所有电路停止工作,直到err重新恢复高电平,整个ac-dc控制芯片内部各功能模块才能在总体功能控制电路11的控制下先后启动,恢复芯片的整体工作模式。

75.图10a和图10b为本发明保护电路13的2种实施例结构。

76.图10a中,所述保护电路13包括:第一钳位电路1011、第二钳位电路1021、第三钳位电路1031、第四钳位电路1041、温度检测电路1012、电流检测电路1022、电压检测电路1032、电压检测电路1042、第一高精度比较器1013、第二高精度比较器1023、第三高精度比较器1033、第四高精度比较器1043、第一整形缓冲电路1014、第二整形缓冲电路1024、第三整形缓冲电路1034、第四整形缓冲电路1044。

77.第一钳位电路1011根据温度锁定信号otlock的状态提供偏置电压vbt,并输出给温度检测电路1012;温度检测电路1012根据偏置电压vbt得到温度检测输出信号vint;所述第一高精度比较器1013将温度检测输出信号vint和内部参考信号进行比较,得到比较输出信号vot;第一整形缓冲电路1014将比较输出信号vot进行处理得到过温保护信号otp和温度锁定信号otlock;过温保护信号otp输出给总体功能控制电路11中的错误处理逻辑电路93,温度锁定信号otlock将输入到第一钳位电路1011用于控制偏置电压vbt大小。

78.第二钳位电路1021根据过流锁定信号oclock的状态提供偏置电压vbc,并输出给电流检测电路1022;电流检测电路1022根据偏置电压vbc得到电流检测输出信号vinc;所述第二高精度比较器1023将电流检测输出信号vinc和内部参考信号进行比较,得到比较输出信号voc;第二整形缓冲电路1024将比较输出信号voc进行处理得到过流保护信号ocp和过流锁定信号oclock;过流保护信号ocp输出给总体功能控制电路11中的错误处理逻辑电路93,过流锁定信号oclock将输入到第二钳位电路1021用于控制偏置电压vbc大小。

79.第三钳位电路1031根据欠压锁定信号uvlock的状态提供偏置电压vbl,并输出给电流检测电路1032;电流检测电路1032根据偏置电压vbc得到欠压检测输出信号vinl;所述第三高精度比较器1033将欠压检测输出信号vinl和内部参考信号进行比较,得到比较输出信号vol;第三整形缓冲电路1034将比较输出信号vol进行处理得到欠压保护信号uvlo和欠压锁定信号uvlock;欠压保护信号uvlo输出给总体功能控制电路11中的错误处理逻辑电路93,欠压锁定信号uvlock将输入到第三钳位电路1031用于控制偏置电压vbl大小。

80.第四钳位电路1041根据过压锁定信号ovlock的状态提供偏置电压vbh,并输出给电流检测电路1042;电流检测电路1042根据偏置电压vbh得到过压检测输出信号vinh;所述第四高精度比较器1043将过压检测输出信号vinh和内部参考信号进行比较,得到比较输出信号voh;第四整形缓冲电路1044将比较输出信号voh进行处理得到过压保护信号ovp和过压锁定信号ovlock;过压保护信号ovp输出给总体功能控制电路11中的错误处理逻辑电路93,过压锁定信号ovlock将输入到第四钳位电路1041用于控制偏置电压vbh大小。

81.图10a所示的保护电路13工作原理如下:当温度正常时,温度锁定信号otlock为高电平,otlock高电平将控制钳位电路1011产生一个较高的偏置电压vbt;温度检测电路1012将根据vbt产生温度检测输出信号vint。正常情况下第一高精度比较器1013得到的输出信号vot应该为高电平;第一整形缓冲电路1014将比较输出信号vot进行处理得到otlock也为

高电平逻辑信号。当芯片温度异常时,温度检测电路1012产生的温度检测输出信号vint将会出现变化,第一高精度比较器1013根据得到的比较输出信号vot变为低电平信号,第一整形缓冲电路1014得到的温度锁定信号otlock也改变为低电平逻辑信号,过温保护信号otp变为低电平,温度锁定信号otlock低电平将控制第一钳位电路1011产生一个较低的偏置电压vbt,较低的偏置电压vbt将会进一步改变温度检测输出信号vint的大小,使得第一高精度比较器1013输出的vot进一步锁定为低电平信号。

82.当电流正常时,过流锁定信号oclock为高电平,oclock高电平将控制钳位电路1021产生一个较高的偏置电压vbc;电流检测电路1022将根据vbc产生电流检测输出信号vinc。正常情况下第二高精度比较器1023得到的输出信号voc应该为高电平;第二整形缓冲电路1024将比较输出信号voc进行处理得到oclock也为高电平逻辑信号。当芯片电流异常时,电流检测电路1022产生的电流检测输出信号vinc将会出现变化,第二高精度比较器1023根据得到的比较输出信号voc变为低电平信号,第二整形缓冲电路1024得到的电流锁定信号otlock也改变为低电平逻辑信号,过流保护信号ocp变为低电平,过流锁定信号oclock低电平将控制第二钳位电路1021产生一个较低的偏置电压vbc,较低的偏置电压vbc将会进一步改变电流检测输出信号vinc的大小,使得第二高精度比较器1023输出的voc进一步锁定为低电平信号。

83.当电压正常时,欠压锁定信号uvlock为高电平,uvlock高电平将控制钳位电路1031产生一个较高的偏置电压vbl;电压检测电路1032将根据vbl产生欠压检测输出信号vinl。正常情况下第三高精度比较器1033得到的输出信号vol应该为高电平;第三整形缓冲电路1034将比较输出信号vol进行处理得到uvlock也为高电平逻辑信号。当芯片电压严重偏低异常时,电压检测电路1032产生的欠压检测输出信号vinl将会出现变化,第三高精度比较器1033根据得到的比较输出信号vol变为低电平信号,第三整形缓冲电路1034得到的欠压锁定信号uvlock也改变为低电平逻辑信号,欠压保护信号uvlo变为低电平,欠压锁定信号uvlock低电平将控制第三钳位电路1031产生一个较低的偏置电压vbl,较低的偏置电压vbl将会进一步改变欠压检测输出信号vinl的大小,使得第三高精度比较器1033输出的vol进一步锁定为低电平信号。

84.所述过压保护过程的工作和欠压保护过程类似。电压正常时,过压锁定信号ovlock为高电平;电压过高时,过压锁定信号ovlock也改变为低电平逻辑信号,过压保护信号ovp变为低电平。

85.图10b的电路对图10a进行了整合,该保护电路13包括:第一钳位电路1011、第二钳位电路1021、第三钳位电路1031、第四钳位电路1041、温度检测电路1012、电流检测电路1022、电压检测电路1032、电压检测电路1042、检测输入开关选择电路103、高精度比较器104、整形缓冲电路105、检测输出开关选择电路106。

86.所述第一钳位电路1011根据温度锁定信号otlock的状态提供偏置电压vbt,并输出给温度检测电路1012,温度检测电路1012根据偏置电压vbt得到温度检测输出信号vint;所述第二钳位电路1021根据过流锁定信号oclock的状态提供偏置电压vbc,并输出给电流检测电路1022,电流检测电路1022根据偏置电压vbc得到电流检测输出信号vinc;所述第三钳位电路1031根据欠压锁定信号uvlock的状态提供偏置电压vbl,并输出给电流检测电路1032,电流检测电路1032根据偏置电压vbc得到欠压检测输出信号vinl;所述第四钳位电路

1041根据过压锁定信号ovlock的状态提供偏置电压vbh,并输出给电流检测电路1042,电流检测电路1042根据偏置电压vbh得到过压检测输出信号vinh。所述温度检测输出信号vint、电流检测输出信号vinc、欠压检测输出信号vinl、过压检测输出信号vinh同时进入检测输入开关选择电路103,经开关选择控制信号selp选择,输出检测信号vind。开关选择控制信号selp共有4种开关状态,状态一时温度检测输出信号vint选通并连接到检测信号vind,状态二时电流检测输出信号vinc选通并连接到检测信号vind,状态三时欠压检测输出信号vinl选通并连接到检测信号vind,状态四时过压检测输出信号vinh选通并连接到检测信号vind。所述高精度比较器103将检测信号vind和内部参考信号进行比较,得到比较输出信号vo;所述整形缓冲电路104将比较输出信号vo进行处理得到保护信号op和保护锁定信号opl;保护信号op和保护锁定信号opl同时进入检测输出开关选择电路106。

87.经开关选择控制信号selp选择,状态一时保护信号op和保护锁定信号opl选通并分别连接到过温保护信号otp和温度锁定信号otlock,状态二时保护信号op和保护锁定信号opl选通并分别连接到过流保护信号ocp和过流锁定信号oclock,状态三时保护信号op和保护锁定信号opl选通并分别连接到欠压保护信号uvlo和欠压锁定信号uvlock,状态二时保护信号op和保护锁定信号opl选通并分别连接到过压保护信号ovp和过压锁定信号ovlock。

88.图10b给出的方案,与图10a相比,通过检测输入开关选择电路103和检测输出开关选择电路106两个数据选择器电路,实现了高精度比较器104和整形缓冲电路105的复用,减小了硬件开销。检测输入开关选择电路103和检测输出开关选择电路106采用常规的4选1数据选择器即可实现。

89.图11为本发明所使用的钳位电路的一种实施例,图11中的信号标识采用了温度检测部分的信号,本发明的第一钳位电路1011、第二钳位电路1021、第三钳位电路1031、第四钳位电路1041均采用和图11相同的钳位电路实现。该电路由pmos管m111、nmos管m112、nmos管m113、nmos管m114、电阻r111、电阻r112、电阻r113和电阻r114组成。pmos管m111的源极、电阻r111的上端和nmos管m114的漏极同时连接到电源电压vccl;所述pmos管m111的栅极连接到nmos管m112的栅极,并同时作为钳位电路的控制信号输入端,连接到温度锁定信号otlock;pmos管m111的漏极连接到nmos管m112的漏极,并同时连接到nmos管m113的栅极;nmos管m113的漏极同时连接电阻r113的上端和电阻r112的下端;电阻r112的上端和电阻r111的下端相连,并连接到nmos管m114的栅极;nmos管m114的源极连接到电阻r114的上端,并作为钳位电路的偏置电压输出节点;nmos管m112的源极、电阻r113的下端、电阻r114的下端和nmos管m113的源极,并同时连接到地电压vss。

90.该钳位电路中,电源电压vcc被分压电阻r111,r112和r113实时分压检测,分压得到的电压值经过nmos管m114和电阻r114构成的源跟随器,得到偏置电压vbt,然后进入后面的温度检测电路1012。r113电阻值受m113控制,而m113的开和关受otlock信号控制。当otlock信号为高电平时,m113的栅极为低,m113处于关闭状态,r113为大电阻,分压得到的电压值vbt为较高的偏置电压;当otlock信号为低电平时,m113的栅极为高,m113处于导通状态,r113被m113短路为很小电阻,此时分压得到的电压值vbt为较低的偏置电压。

91.图12为高精度比较器104的一种实施例。所述高精度比较器包括:pmos管m121、nmos管m122、nmos管m123、pmos管m124、pmos管m125、pmos管m126、pmos管m127、nmos管m128、

nmos管m129、nmos管m1210、pmos管m1211、pmos管m1212和pmos管m1213、nmos管m1214、nmos管m1215、电阻r121和电容c121。

92.其中,pmos管m121栅极连接偏置电压,pmos管m121漏极连接nmos管m122漏极、nmos管m122栅极、nmos管m123栅极、nmos管m128栅极和nmos管m129栅极;nmos管m123漏极连接pmos管m124漏极、pmos管m124栅极、pmos管m125栅极;pmos管m125漏极连接pmos管m126源极和pmos管m127源极;pmos管m126栅极连接到高精度比较器104的参考电压;pmos管m127栅极为比较电压输入端,连接vind;pmos管m126漏极连接nmos管m129漏极和nmos管m1210栅极;pmos管m127漏极连接nmos管m128漏极和nmos管m1214栅极;pmos管m1211漏极连接nmos管m1210漏极和pmos管m1212栅极;pmos管m1212漏极连接pmos管m1211的栅极、nmos管m1214漏极、pmos管m1213栅极和nmos管m1215栅极;pmos管m1213漏极连接nmos管m1215的漏极、电阻r121上端和电容c121上端,并作为信号vo输出端。

93.nmos管m122源极、nmos管m123源极、nmos管m128源极、nmos管m129源极、nmos管m1210源极、nmos管m1214源极、nmos管m1215源极、电阻r121下端和电容c121下端均连接到地电压vss;pmos管m121源极、pmos管m124源极、pmos管m125源极、pmos管m1211源极、pmos管m1212源极、pmos管m1213源极均连接到电源电压vccl。

94.图13为整形缓冲电路的实施例,图13中的信号标识采用了整形缓冲电路105实施例的信号,本发明的第一整形缓冲电路1014、第二整形缓冲电路1024、第三整形缓冲电路1034、第四整形缓冲电路1044均为和图13相同的整形缓冲电路。该电路包括pmos管m131、pmos管m133、pmos管m135、pmos管m136、pmos管m139、pmos管m1311、nmos管m132、nmos管m134、nmos管m137、nmos管m138、nmos管m1310、nmos管m1312、电阻r131、电阻r132和电容c131。其中,pmos管m131、pmos管m133、nmos管m132、nmos管m134、电阻r131、电阻r132和电容c131组成一个带rc滤波功能的缓冲器;pmos管m135、pmos管m136、pmos管m139、nmos管m137、nmos管m138、nmos管m1310组成一个施密特触发器;pmos管m1311和nmos管m1312组成一个输出反相器。所述带rc滤波功能的缓冲器的输入端连接到高精度比较器104的比较输出电压vo,带rc滤波功能的缓冲器的输出端连接到施密特触发器的输入端,施密特触发器的输出端连接到输出反相器的输入端和op信号输出端,输出反相器的输出端输出温度锁定信号opl。

95.以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。