技术特征:

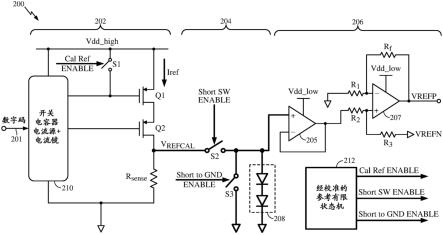

1.一种电子电路,包括:电压参考电路,所述电压参考电路被配置为由相对较高的电压供电;缓冲电路,所述缓冲电路被配置为生成与所述相对较高的电压相比相对较低的电压;以及耦合在所述电压参考电路的输出与所述缓冲电路的输入之间的电路,所述电路被配置为防止所述较高的电压到达所述缓冲电路的所述输入。2.根据权利要求1所述的电子电路,其中所述电路被配置为在微调模式或校准模式中的至少一个模式期间,防止所述较高的电压到达所述缓冲电路的所述输入。3.根据权利要求1所述的电子电路,其中所述电路包括耦合在所述电压参考电路的所述输出与所述缓冲电路的所述输入之间的第一开关。4.根据权利要求3所述的电子电路,其中所述电路还包括耦合在所述缓冲电路的所述输入与参考电位节点之间的第二开关。5.根据权利要求4所述的电子电路,还包括耦合在所述缓冲电路的所述输入与所述参考电位节点之间的钳位电路。6.根据权利要求5所述的电子电路,还包括耦合在所述钳位电路与所述缓冲电路的所述输入之间的第三开关。7.根据权利要求6所述的电子电路,其中所述第三开关被配置为在用于所述电压参考电路的微调模式期间闭合。8.根据权利要求4所述的电子电路,其中所述第一开关被配置为在校准模式期间断开,并且被配置为从所述校准模式被使能时的时间起的预定数量的时钟周期闭合。9.根据权利要求8所述的电子电路,其中所述第二开关被配置为在所述校准模式期间闭合,并且被配置为在从所述校准模式被使能时的时间起的所述预定数量的时钟周期处断开,或在从所述校准模式被使能时的时间起的所述预定数量的时钟周期之后的一个时钟周期内断开。10.根据权利要求4所述的电子电路,其中所述第一开关最初被配置为在所述电子电路的上电或复位之后的正常操作模式期间断开,并且被配置为从所述上电或所述复位开始起的预定数量的时钟周期闭合。11.根据权利要求10所述的电子电路,其中所述第二开关最初被配置为在所述上电或所述复位之后的所述正常操作模式期间闭合,并且被配置为在所述上电或所述复位开始处断开,或在所述上电或所述复位开始之后的一个时钟周期内断开。12.根据权利要求1所述的电子电路,还包括耦合在所述缓冲电路的所述输入与参考电位节点之间的钳位电路。13.根据权利要求1所述的电子电路,其中所述缓冲电路包括用于模数转换器的电压参考缓冲器。14.根据权利要求1所述的电子电路,其中所述电压参考电路包括经温度补偿和经校准的电压参考电路。15.一种驱动缓冲电路的方法,包括:从相对较高的电压为电压参考电路供电;利用所述缓冲电路生成与所述相对较高的电压相比相对较低的电压,所述较低的电压

基于从所述电压参考电路输出的电压参考值;以及防止所述较高的电压到达所述缓冲电路的输入。16.根据权利要求15所述的方法,其中所述防止包括:断开耦合在所述电压参考电路的输出与所述缓冲电路的所述输入之间的第一开关;闭合耦合在所述缓冲电路的所述输入与参考电位节点之间的第二开关;调整从所述电压参考电路输出的所述电压参考值;在所述调整之后,闭合所述第一开关;以及在所述调整之后,断开所述第二开关。17.根据权利要求16所述的方法,其中:所述第一开关在校准模式期间断开;所述第二开关在所述校准模式期间闭合;所述第一开关从所述校准模式被使能时的时间起的预定数量的时钟周期闭合;以及所述第二开关在从所述校准模式被使能时的时间起的所述预定数量的时钟周期处断开,或在从所述校准模式被使能时的时间起的所述预定数量的时钟周期之后的一个时钟周期内断开。18.根据权利要求16所述的方法,其中:所述第一开关在微调模式期间断开;所述第二开关在所述微调模式期间闭合;所述第一开关从所述微调模式被使能时的时间起的预定数量的时钟周期闭合;以及所述第二开关在从所述微调模式被使能时的时间起的所述预定数量的时钟周期处断开,或在从所述微调模式被使能时的时间起的所述预定数量的时钟周期之后的一个时钟周期内断开。19.根据权利要求15所述的方法,还包括选择性地钳住所述缓冲电路的所述输入处的电压。20.一种电子电路,包括:电压参考电路,所述电压参考电路被配置为由相对较高的电压供电;缓冲电路,所述缓冲电路被配置为生成与所述相对较高的电压相比相对较低的电压;耦合在所述电压参考电路的输出与所述缓冲电路的输入之间的第一开关;以及耦合在所述缓冲电路的所述输入与用于所述电子电路的参考电位节点之间的第二开关。

技术总结

本公开的某些方面提供了电路,该电路将由相对高电压供电的电压参考电路的输出连接到电压缓冲器的输入,该电压缓冲器被配置为生成低于高电压的电压。连接电路防止高电压到达电压缓冲器的输入。一个示例电子电路通常包括:被配置为由相对较高的电压供电的电压参考电路,被配置为生成与相对较高的电压相比相对较低的电压的缓冲电路,以及耦合在电压参考电路的输出与缓冲电路的输入之间的电路,该电路被配置为防止较高的电压到达缓冲电路的输入。配置为防止较高的电压到达缓冲电路的输入。配置为防止较高的电压到达缓冲电路的输入。

技术研发人员:K

受保护的技术使用者:高通股份有限公司

技术研发日:2021.01.27

技术公布日:2022/9/13

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。