1.本发明整体涉及成像系统,并且更具体地涉及具有降低的峰值功率(例如,降低的峰均功率比)的图像传感器及其操作方法。

背景技术:

2.图像传感器包括图像传感器像素,该图像传感器像素通常使用并行像素读出路径诸如列路径耦接到对应的像素读出电路,该并行像素读出路径将图像传感器像素的列耦接到对应的读出电路。读出电路可以在活动状态下工作(在此期间,读出电路消耗相对较高的功率)或者处于静态状态(在此期间,读出电路消耗相对较低的功率)。

3.在一些图像传感器中,尤其是在具有相对大的像素阵列(例如,拼接像素阵列)的那些图像传感器中,读出电路可以在相对较长的时间段内处于静态(低功率使用)状态,并且可以在相对较短的时间段内在活动(高功率使用)状态下工作。这可能导致不期望的高峰均功率比(papr)。高papr是不期望的,因为对系统施加了额外的电源完整性和信号完整性需求(例如,由于功率使用基本上随时间波动,系统必须耐受电流浪涌引起的所有劣化)。

4.虽然系统可以经适配以缓和这些问题中的至少一些问题,但是此类调整将导致额外的不期望的成本,诸如噪声增强(例如,由于增加的模拟-数字转换时间和来自模拟-数字转换器元件的渗漏)以及物理实施区域和平均功率增加。因此,可期望降低峰值功率(峰均功率比),同时降低这些额外成本。

5.本文的实施方案就是在这种背景下出现的。

附图说明

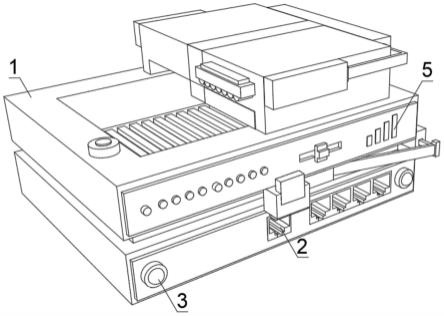

6.图1是根据一些实施方案的具有图像传感器和处理电路的例示性成像系统的示意图。

7.图2是根据一些实施方案的具有像素阵列和对应的控制和读出电路的例示性图像传感器的示意图。

8.图3是根据一些实施方案的控制和读出电路中针对相应像素列的例示性读出电路的图。

9.图4是根据一些实施方案的并行执行针对不同像素列的读出操作的例示性时序图。

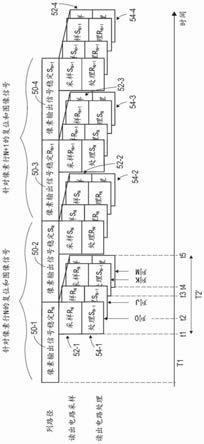

10.图5是根据一些实施方案的跨不同像素列的时域复用读出操作的例示性时序图。

11.图6a和图6b是根据一些实施方案的例示性方式的图,其中不同对应像素行内的针对不同像素列的模拟-数字转换操作可以在行时间内彼此偏移。

12.图7是根据一些实施方案的示出针对不同像素列的模拟-数字转换操作可如何分布的例示性图。

具体实施方式

13.诸如数码相机、计算机、蜂窝电话和其他电子设备的电子设备可包括图像传感器,该图像传感器收集传入的光以捕获图像(例如,图像帧)。图像传感器可包括图像传感器像素阵列。图像传感器中的像素可包括光敏元件,诸如将传入的光转换成图像信号的光敏元件。图像传感器可具有任何数量(例如,数百或数千或更多)的像素。典型的图像传感器可例如具有数十万或数百万像素(例如,数兆像素)。图像传感器可包括控制电路(诸如,用于操作图像像素的电路)和用于读出图像信号的读出电路,该图像信号与光敏元件所生成的电荷相对应。

14.图1是例示性成像系统(诸如,电子设备)的示意图,该成像系统使用图像传感器捕获图像。图1的成像系统10可为相机、蜂窝电话、平板计算机、网络摄像头、摄像机、视频监控系统、汽车成像系统、具有成像能力的视频游戏系统、增强现实和/或虚拟现实系统、无人飞行器系统(例如,无人机)、工业系统或捕获数字图像数据的任何其他期望的成像系统或设备。相机模块12(有时称为成像模块)可用于将入射光转换成数字图像数据。相机模块12可包括一个或多个透镜14以及一个或多个对应图像传感器16。在图像捕获操作期间,可通过透镜14将来自场景的光聚焦到图像传感器16上。图像传感器16可包括用于将模拟像素信号转换成提供给存储和处理电路18的对应数字图像数据的模拟-数字转换器(adc)电路。

15.存储和处理电路18可包括一个或多个集成电路(例如,图像处理电路、微处理器、诸如随机存取存储器和非易失性存储器等存储设备),并且可使用与相机模块分开和/或形成相机模块的一部分的组件来实现。当不同于图像传感器16的集成电路的集成电路上包括存储和处理电路18时,可相对于具有图像传感器16的集成电路竖直地堆叠或封装具有电路18的集成电路。可使用处理电路18处理和存储已被相机模块捕获的图像数据(例如,使用处理电路18上的图像处理引擎、使用处理电路18上的成像模式选择引擎等)。可根据需要使用耦接到处理电路18的有线通信路径和/或无线通信路径将处理后的图像数据提供给外部设备(例如,计算机、外部显示器或其他设备)。

16.如图2所示,图像传感器16可包括含有布置成行和列的图像传感器像素22(有时在本文称为图像像素或像素)的图像阵列20,并且可包括控制和处理电路24。阵列20可包含例如数百或数千行以及数百或数千列的图像传感器像素22。控制电路24可耦接到行控制电路26和列读出和控制电路28(有时在本文中称为列读出电路或列控制电路)。行控制电路26可接收来自控制电路24的行地址和控制信号并且通过行控制路径30将对应的行控制信号(诸如复位控制信号、抗光晕控制信号、行选择控制信号、电荷转移控制信号、双转换增益模式控制信号和读出控制信号)提供给像素22的行。虽然仅针对像素22的每个行示出了一个路径30,但这仅仅是例示性的。任何对应数量的路径30可以耦接到像素22的每个行。

17.可将一根或多根导线(诸如,列线32)耦接到阵列20中的像素22的每一列。列线32可用于从像素22读出(复位电平或图像电平)信号以及用于将偏置信号(例如,偏置电流或偏置电压)提供给像素22。如果需要,在像素读出操作期间,可使用行控制电路26选择阵列20中的像素行,并且可沿相应列线32读出由该像素行中的每个对应图像像素22生成的信号。

18.列读出电路28可通过列线32接收信号(例如,由像素22生成的模拟像素值)。列读出电路28可包括用于临时存储从阵列20读出的校准信号(例如,复位电平信号、参考电平信

号)和/或图像信号(例如,图像电平信号)的存储器电路、放大器电路或乘法器电路、模拟-数字转换器(adc)电路、偏置电路、用于选择性启用或禁用列电路的锁存电路或耦接到阵列20中的一个或多个像素列以用于操作像素22和用于从像素22读出信号的其他电路。在读出和/或处理来自像素22的信号之后,列读出电路28可以将读出像素数据提供给控制和处理电路24和/或处理器18(图1)以用于进一步处理和/或存储。

19.图像阵列20可设置有具有多个(颜色)过滤元件(每个过滤元件对应于相应像素)的过滤器阵列,该过滤器阵列允许单个图像传感器对不同颜色或波长组的光进行采样。例如,图像传感器像素22可设置有具有红色、绿色和蓝色过滤元件的滤色器阵列,该滤色器阵列允许单个图像传感器使用被布置成拜耳马赛克图案的对应红色、绿色和蓝色图像传感器像素对红光、绿光和蓝光(rgb)进行采样。这些示例仅仅是例示性的,一般来讲,可在任何期望数量的图像像素22上方形成任何期望颜色和/或波长以及任何期望图案的过滤元件。另外,像素阵列20还可以设置有具有一种或多种类型的多个微透镜的微透镜阵列。每个微透镜可以被配置为将光聚焦到像素中的对应光敏元件上。如果需要,可以针对一个或多个光敏元件省略微透镜。

20.图3进一步详细描述图2中的控制和读出电路28的例示性具体实施方式。如图3所示,列控制和读出电路28包括针对阵列20中的每个像素列的对应读出电路40。作为实例,每个读出电路(例如,耦接到针对列0中的像素22的列路径32-0的读出电路40-0、耦接到针对列j中的像素22的列路径32-j的读出电路40-j、耦接到针对列k中的像素22的列路径32-k的读出电路40-k和耦接到针对列m中的像素22的列路径40-m的读出电路40-m)包括采样和保持(s/h)电路、adc电路、相关双采样(cds)电路(例如,被配置为执行数字或模拟cds操作的电路)等电路中的一者或多者。

21.并行列路径32(在本文中有时称为列线32)可以用于从对应像素列中的每个像素22读出像素信号(例如,用于cds操作的复位电平信号和对应图像电平信号)。特别是,控制电路24(图2)可以被配置为向行控制电路26(并且由此向像素22)和每个读出电路40提供控制信号以逐行执行读出操作。例如,在针对第一像素行(例如,行n)的读出操作期间,列路径32-0和读出电路40-0可以从行n和列0中的像素22接收复位和图像电平信号,并且在针对第二像素行(例如,行n 1)的读出操作期间,列路径32-0和读出电路40-0可以从行n 1和列0中的像素22接收复位和图像电平信号。以类似的方式,其他列路径32和读出电路40可以各自在适当的像素行读出操作期间从对应行和列中的像素接收像素信号。

22.在一些例示性配置中,每个读出电路40可以在流水线操作模式下操作。特别是,给定读出电路40可以包括执行多个操作的多个电路。例如,可以在第一电路处接收第一信号并且随后传递到第二下游电路以进行进一步处理。当在第一电路处接收第二信号时,第二下游电路可以处理第一信号。例如,第一电路可以是信号采样电路,而第二电路可以是信号处理电路。其中第一电路是采样电路(用于adc电路)并且第二电路是adc电路的例示性配置在本文中作为例示性示例进行了描述。然而,这仅仅是例示性的。如果需要,第二电路可以是任何合适的信号处理电路,诸如(数字)相关双采样(cds)电路。如果需要,除第一电路和第二电路之外,每个读出电路40可以包括其他功能电路。

23.图4是用于在读出操作期间操作例示性成像系统的例示性时序图。特别是,为了执行这些读出操作,控制电路可以协调(例如,发送控制信号到)行控制电路(行驱动器)和列

读出电路,使得像素和列读出电路执行图4所示的读出操作。

24.在图4的示例中,读出操作是流水线的(例如,读出操作中的每个步骤或操作以流水线方式发生)。换句话讲,对针对当前行n的复位电平信号进行采样(在给定读出电路40的第一部分处)可以与针对先前行n-1的信号电平信号的处理(在给定读出电路40的第二部分处)并行发生。然而,这仅仅是例示性的。如果需要,图4中的一些操作可以略微彼此偏移(例如,可以稍微延迟)而不是如图所示完美对准。

25.如图4所示,针对给定像素行中的每个像素22,将复位电平信号和图像电平信号读出到列读出电路28中。若要从给定像素22正确读出像素信号,控制电路(例如,行控制电路26中的行驱动器)可以控制给定像素22(例如,针对整个像素行生效行选择控制信号)以从给定像素22输出像素信号到耦接到列路径32的像素输出路径。在触发行读取的合适的时间段(在本文中称为稳定时间段)之后,输出像素信号可以在列路径32的输出端子(例如,耦接到列读出电路28中的给定读出电路40的端子)处稳定为准确的电压。

26.在图4的示例中,列路径32可以呈现出用于针对像素行n中的像素22的复位电平信号rn的第一稳定时间段(例如,与图3中的列路径32中的每一个列路径上的并行稳定操作50-1相关联)并且可以随后呈现出用于针对像素行n中的像素22的图像电平信号sn的第二稳定时间段(例如,与图3中的列路径32中的每一个列路径上的并行稳定操作50-2相关联)。如图4所示,列路径32可以类似地呈现出用于针对像素阵列20的其他像素行(例如,像素行n-1、像素行n 1等)中的每个像素22的对应像素输出信号的稳定时间段。

27.列读出电路28(例如,图3中的每个读出电路40)可以在对应像素输出信号已经在列路径32上准确地稳定之后对对应像素输出信号进行采样。在流水线操作模式下,每个读出电路40还可以并行执行其他操作,诸如针对来自先前像素行中的像素22的像素输出信号的处理操作。例如,当每个读出电路40针对来自当前行n中的像素22的信号rn执行采样操作时(例如,操作52-1),读出电路40还可以针对先前行n-1中的像素22执行adc转换操作或其他处理操作(例如,操作54-1)。

28.在图4的例示性定时配置中(例如,与对应的读出电路配置相关联),采样操作52-1(例如,在时间段t2期间)在稳定操作50-1结束之前(例如,在像素输出线稳定完成之前)开始,使得采样操作52-1的一部分可以与稳定操作50-1并行(同时)发生。然而,这仅仅是例示性的,并且仅可以在一些读出电路配置中实现。在其他读出电路配置中,采样操作可以在稳定操作结束时或之后开始(例如,稳定操作50-1和采样操作52-1可以在时间上不重叠或严格依次发生)。本文描述的涉及降低峰值功率的实施方案(例如,结合图5详细描述)可以类似地(以类似的方式)适用于这些场景中的任何场景(例如,适用于这些读出电路实施方式中的任何实施方式)。

29.另外,采样操作52-1和处理操作54-1在图4中例示性地示出以同时发生(例如,具有相同的开始和结束时间)。然而,这是相似地例示性的,并且仅可以在一些读出电路配置中实现。在其他读出电路配置中,采样操作和处理操作可以具有不同的相应长度,在不同的相应时间(彼此偏移)发生(例如,开始或结束),和/或根椐特定读出电路配置具有其他特征。本文描述的涉及降低峰值功率的实施方案(例如,结合图5详细描述)可以类似地(以类似的方式)适用于这些场景中的任何场景(例如,适用于这些读出电路实施方式中的任何实施方式)。

30.在一些成像系统中,诸如具有大图像传感器像素阵列的成像系统(例如,从基于相同像素阵列图块的多个实例的戳记-重复过程形成的拼接图像传感器像素阵列),像素输出信号稳定时间段可以比列读出电路28被激活的时间段(例如,采样操作52期间、处理操作54期间等)长。特别是,作为例示性示例,由于列路径的长度较长和耦接到每个列路径32的大量像素(例如,所得寄生效应),像素输出信号稳定时间段会比其他成像系统中的像素输出信号稳定时间段长。这可能不期望地增加成像系统中的峰值功率使用(例如,可能不期望地增加峰均功率比)。

31.如图4所示,在时间段t1期间,列读出电路28(例如,图3中的读出电路40中的每一个读出电路执行操作52和54)可以处于静态状态(例如,低功率使用状态或被动状态)。在时间段t2期间,列读出电路28(例如,图3中的读出电路40中的每一个读出电路执行操作52和54)可以处于活动状态(例如,高功率使用状态)。换句话讲,在时间段t2期间,耦接到图3中的所有列路径32的对应读出电路40可以同时处于激活状态,从而消耗大量的功率。列读出电路28在时间段t1和t2期间(以及在针对其他像素信号和针对其他像素行的类似时间段期间)的这种例示性操作可以导致相对于平均功率的高峰值功率。

32.为了降低峰值功率使用(例如,峰均功率比),成像系统可以以如图5所示的方式或以结合图4修改自上文所述图5的方式执行像素读出操作(例如,采样操作在对应稳定操作结束时或之后开始,采样操作和处理操作具有不同的相应长度、在不同的相应时间发生和/或具有其他特征等)。特别是,控制电路24可以协调(例如,将控制信号发送到)行控制电路26和列读出电路28(例如,图3中的读出电路40),使得像素22和列读出电路28执行图5中所示的读出操作。

33.如图5所示,列读出电路28可以被配置为以偏移方式针对同一列中的不同像素执行采样操作52和处理操作54(例如,耦接到第一像素列的第一读出电路40可以在从第二时间段偏移的第一时间段期间执行采样和/或处理操作,在第二时间段期间,耦接到第二像素列的第二读出电路40执行采样和/或处理操作)。此偏移过程有时可以称为时域复用。

34.在图5的例示性示例中,针对来自像素行n中的像素22的复位电平信号rn的采样操作52-1示出为逐列偏移。换句话讲,在时间t1,图3中耦接到像素列0的读出电路40-0的一部分可以被激活(例如,处于活动状态)以针对列路径32-0上的信号rn执行采样操作52-1。在时间t2,图3中耦接到像素列j的读出电路40-j的一部分可以被激活(例如,处于活动状态)以针对列路径32-j上的信号rn执行采样操作52-1。在时间t3,图3中耦接到像素列k的读出电路40-k的一部分可以被激活(例如,处于活动状态)以针对列路径32-k上的信号rn执行采样操作52-1。在时间t4,图3中耦接到像素列m的读出电路40-m的一部分可以被激活(例如,处于活动状态)以针对列路径32-m上的信号rn执行采样操作52-1。如果需要,针对其他列的其他读出电路可以以类似的偏移方式执行采样操作52-1。通过以这种方式操作列读出电路28(例如,执行时域复用),成像系统中的峰值功率使用可以显著降低,并且可以基本上缓和不期望的峰均功率比效应。

35.在流水线操作模式下,在针对每个读出电路40的采样操作52-1期间,读出电路40(例如,读出电路40的adc转换部分)还可以被激活以执行其他功能,诸如针对来自先前像素行的像素信号(例如,针对像素行n-1的图像电平信号s

n-1

)的处理操作(例如,adc转换操作)。以与针对跨不同像素列的采样操作52-1执行时域复用的列读出电路28类似的方式,列

读出电路28还可以针对跨不同像素列的处理操作54-1执行时域复用。换句话讲,每个读出电路40(图3)可以在不同时间被激活以执行其对应处理操作54-1。

36.其中处理操作54是由读出电路40中的对应adc电路执行的adc转换操作的配置在本文中作为例示性示例进行了描述。在这些配置中,在操作52-1期间,每个adc电路40可以以如图5所示的偏移方式将来自对应列路径的像素信号(信号rn)采样到adc电路40的输入端子上。在流水线操作模式下的同时操作54-1期间,每个adc电路40还可以以如图5所示的偏移方式针对先前采样的像素信号(信号r

n-1

)执行实际转换操作。如果需要,至少针对图3中的一个或多个adc电路40的采样操作和/或转换操作可以相对于针对图3中的一个或多个其他adc电路40的采样操作和/或转换操作进行偏移以实现时域复用。

37.采样和/或处理操作52-1和54-1可以在时间段t2’期间(在时间t1与t5之间)发生。在图5的示例中,为了进行示意性的说明,操作52-1和54-1的长度被放大。可能期望基本上所有针对不同像素列的采样操作52-1(以及基本上所有针对不同像素列的处理操作54-1)与稳定操作50-1在时间上重叠。换句话讲,用于稳定操作50-1的时间段(例如,稳定时间段)可以是时间段t1和t2’的总和,并且稳定操作50-1可以在时间t5附近、在时间t5或在时间t5之后结束。

38.虽然上文已经结合针对像素行n的复位电平信号的采样操作(操作52-1)和针对像素行n-1的图像电平信号的处理操作(操作54-1)描述了时域复用,但这仅仅是例示性的。如果需要,列读出电路28(例如,读出电路40)可以针对以下执行时域复用:针对像素行n的图像电平信号的采样操作(操作52-2)和针对像素行n的复位电平信号的处理操作(操作54-2)、针对像素行n 1的复位电平信号的采样操作(操作52-3)和针对像素行n的图像电平信号的处理操作(操作54-3)、针对像素行n 1的图像电平信号的采样操作(操作52-4)和针对像素行n的复位电平信号的处理操作(操作54-2),以及针对任何其他像素行的信号的类似操作。如果需要,对应相关双采样(cds)操作可以发生以从对应图像电平信号中减去复位电平信号。如果需要,数字cds操作也可以是流水线的和跨不同列时域复用的。

39.在一些具体实施方式中,当从不同的像素行中读出像素信号或读出像素信号用于不同的图像帧时,可能期望通过以不同次序激活不同模式或组的读出电路(例如,图3中的读出电路40)来执行时域复用。图6a和图6b是示出针对两个不同像素行的两个例示性adc转换方案的图。在图6a和图6b的例示性示例中,描述了adc转换操作(例如,实现图5中的操作54)。如果需要,可以类似地发生其他采样和处理操作(例如,数字cds操作),代替这些adc转换操作。

40.图6a示出了针对具有来自多个列(例如,列0至列m)的像素的例示性像素行(例如,行n)的例示性adc转换方案,该多个列各自耦接到对应读出电路40(图3)。耦接到行n中的不同像素的不同读出电路40(例如,adc电路)可以在行时间内的不同时间被激活(例如,如结合图5所描述的包括列路径稳定时间的行时间)。这被示出为线性带60,其指示相对于行时间的针对每个列的adc转换时间。如图6a所示,耦接到列0和m的对应adc电路(例如,在图3中的读出电路40-0和40-m中)可以首先被激活以在行时间的开始附近执行adc转换操作(例如,图5中的处理操作54)。耦接到列0与列m之间的列的其他adc电路系统可以以由带60所指示的相对于行时间的开始的偏移时间执行adc转换操作。

41.特别是,在图6a的示例中,耦接到中间列(例如,列l)的adc电路(在对应读出电路

40中)可以在行时间的结束(例如,待激活的最后一个adc电路)附近执行adc转换操作。耦接到列0与列l之间的列的adc电路可以逐渐并且稍后从行时间的开始开始adc转换操作。相似地,耦接到列m与列l之间的列的adc电路可以逐渐并且稍后从行时间的开始开始adc转换操作。

42.然而,使用由带60指示的adc转换时间的此示例仅仅是例示性的。如果需要,也可以使用激活adc电路或耦接到不同列的其他读出电路的其他模式。另外如图6a所示,如果需要,指示在行时间内跨不同列执行adc转换的另一模式或次序的带60’可以用于转换方案,代替由60指示的adc转换时间。使用由带60’指示的adc转换时间,耦接到列m的adc电路可以在行时间期间首先开始和执行adc转换,并且针对其他列的adc电路可以逐渐地稍后执行adc转换,直到由adc电路针对列0执行的最后一个adc转换操作。

43.图6b示出了针对具有来自多个列(例如,列0至列m)的像素的例示性像素行(例如,像素行n 1)的例示性adc转换方案,该多个列各自耦接到对应读出电路40(图3)。类似于结合图6a描述的adc转换方案,可以在跨行时间的不同时间激活耦接到不同列的adc电路(以执行转换或其他处理操作)。在图6b的示例中,可以首先在行时间中激活耦接到列x的adc电路以在转换时间期间执行转换操作,而耦接到列y的adc电路可以在行时间中最后被激活以在转换时间期间执行转换操作。耦接到其他列的其他adc电路可以在针对列x和列y的第一转换时间和最后转换时间之间的增量时间执行转换操作。此具有对应转换时间的例示性adc转换方案由带62示出。

44.然而,使用由带62指示的adc转换时间的此示例仅仅是例示性的。如果需要,也可以使用激活adc电路或耦接到不同列的其他读出电路的其他模式。另外如图6b所示,如果需要,指示在行时间内跨不同列执行adc转换的另一模式或次序的带62’可以用于转换方案,代替adc转换时间62。使用由带62’指示的转换时间,耦接到列x的adc电路仍然可以在行时间期间首先开始并执行adc转换,但是耦接到列x 1的adc电路可以最后被激活以执行adc转换,并且其他adc电路可以在第一adc转换时间与最后adc转换时间之间的时间逐渐开始和执行adc转换(例如,以线性量化的方式)。

45.图6a和图6b中针对不同行的adc转换定时仅仅是例示性的。特别是,虽然针对每个像素行仅示出了两个不同的进展方案,但也可以使用其他量化或线性进展来跨像素行分布转换时间。如果需要,可以使用非线性(例如,伪随机、随机等)进展代替图6a和图6b中所示的线性进展。作为示例,针对跨列的转换时间的模式的定时可以由状态机电路、存储器电路、逻辑电路等确定。

46.通过以结合图6a和图6b(以及图5)描述的方式执行列偏移adc转换,adc转换活动(或其他处理活动)可以跨可用行时间的大部分或全部进行分布,从而允许读出电路激活的更均匀分布和更均匀的功率使用。

47.图7示出了相对于针对像素行的跨列的行时间的adc转换时间的例示性发生的图。特别是,可能期望实施adc转换时间的均匀分布,使得在行时间中的每个时刻,相同和/或最小数量的adc电路被置于活动模式(例如,执行adc转换操作)下。这有助于确保adc电路跨不同列的累积系统功率最均匀地进行分布。

48.如图7所示的转换时间的均匀分布仅仅是例示性的。如果需要,转换时间的分布可以仅是基本上均匀的或可以以其他方式变化。

49.为了减轻和解决图像内的固定模式伪影,可能期望使用跨不同像素行的不同进展以不同的方式跨列执行时域复用。如图6a和6b所示,针对像素行n的转换时间带60可以与针对像素行n 1的转换时间带62不同(例如,即使转换操作是针对同一图像帧生成数据)。相似地,行时间内的转换时间模式也可以跨针对同一图像帧的其他像素行处理信号而变化。

50.另外,为了减轻和解决不同图像帧之间的固定模式伪影,可能期望在处理不同帧时使用针对同一像素行的不同进展以不同的方式跨列执行时域复用。如图6a中例示性所示,转换时间带60可以用于针对第一图像帧执行adc转换,而转换时间带60’可以用于针对第二图像帧执行adc转换。相似地,在图6b中,转换时间带62可以用于针对第一图像帧执行adc转换,而转换时间带62’可以用于针对第二图像帧执行adc转换。

51.通常,根据需要,其中应用跨列时域复用的模式和方式(例如,用于降低峰均功率比)可以跨行变化和/或可跨图像帧变化(例如,以在不同电平减轻固定噪声伪影)。成像系统可以包括合适的数据存储电路,该合适的数据存储电路存储指示跨列时域复用的期望模式的数据,并且可以包括(固定或随机)数据生成电路,该数据生成电路被配置为生成指示期望模式的数据。如果需要,可以按每行、按每帧和/或以任何其他合适的方式更新模式数据。

52.已经描述了各种实施方案,其说明用于降低图像传感器中的峰值功率的系统和方法。

53.例如,图像传感器包括布置成列和行的图像传感器像素(例如,形成拼接图像传感器阵列),并且包括多个读出电路,该多个读出电路各自经由对应列路径(例如,列线)耦接到图像传感器像素的对应列。多个读出电路可以被配置为在行时间(例如,包括列路径上的像素信号稳定时间)期间执行读出操作。图像传感器可以进一步包括控制电路,该控制电路被配置为通过在行时间内的至少第一偏移时间段和第二偏移时间段期间激活多个读出电路,控制多个读出电路针对跨多个读出电路的读出操作执行时域复用。

54.如果需要,读出操作可以以线性或非线性(例如,伪随机或随机)方式跨行时间发生。如果需要,模拟-数字转换操作的发生可以以均匀方式在时间上跨行时间分布。在一些配置中,多个读出电路各自包括模拟-数字转换器电路,并且读出操作包括模拟-数字转换操作。在一些配置中,多个读出电路各自包括相关双采样电路,并且读出操作可以包括相关双采样操作。如果需要,多个读出电路中的每一个读出电路可以在流水线操作模式下操作,并且读出操作可以包括与模拟-数字转换操作至少部分并行地执行的采样操作。

55.在一些配置中,多个读出电路可以被配置为在附加的行时间期间执行附加的读出操作。控制电路可以被配置为控制多个读出电路以相比于其中多个读出电路被激活以针对读出操作执行时域复用的次序(或模式),通过以不同的次序(或模式)激活多个读出电路来针对跨多个读出电路的附加的读出操作执行时域复用。

56.在一些配置中,多个读出电路可以被配置为在与图像帧相关联的附加的行时间期间执行附加的读出操作,该图像帧与和行时间相关联的图像帧不同。控制电路可以被配置为控制多个读出电路以相比于其中多个读出电路被激活以针对读出操作执行时域复用的次序(或模式),通过以不同的次序(或模式)激活多个读出电路来针对跨多个读出电路的附加的读出操作执行时域复用。

57.又如,操作具有布置成列和行的图像传感器像素的图像传感器的方法可以包括:

在各自耦接到图像传感器像素的对应列的多个读出电路处从图像传感器像素的行接收像素信号;在与图像传感器像素的行相关联的行时间期间执行读出操作;以及通过在跨行时间的不同时间激活多个读出电路,针对跨多个读出电路的读出操作执行时域复用。

58.如果需要,执行读出操作可以包括在行时间期间执行模拟-数字转换操作。如果需要,该方法可以进一步包括:在与图像传感器像素的附加的行相关联的附加的行时间期间执行附加的读出操作,以及相比于其中多个读出电路被激活以针对读出操作执行时域复用的方式,通过以不同的方式激活多个读出电路来针对跨多个读出电路的附加的读出操作执行时域复用。如果需要,该方法可以进一步包括:在与图像传感器像素的行相关联的附加的行时间期间执行附加的读出操作,以及相比于其中多个读出电路被激活以针对读出操作执行时域复用的方式,通过以不同的方式激活多个读出电路来针对跨多个读出电路的附加的读出操作执行时域复用。如果需要,可以以基于图像传感器像素的列的次序的线性进展或以伪随机进展跨行时间激活多个读出电路。

59.再又如,图像传感器可以包括具有分别布置在第一列和第二列中并且布置在同一行中的第一像素和第二像素的图像传感器阵列,包括使用第一列线耦接到第一像素并且被配置为在与针对第一像素和第二像素的读出操作相关联的行时间期间开始第一模拟-数字转换操作的第一模拟-数字转换器电路,并且包括使用第二列线耦接到第二像素并且被配置为在行时间期间开始第二模拟-数字转换操作的第二模拟-数字转换器电路。第一模拟-数字转换器电路和第二模拟-数字转换器电路可以分别在跨行时间的第一不同时间和第二不同时间切换到活动模式以开始第一模拟-数字转换操作和第二模拟-数字转换操作。

60.在一些配置中,第一模拟-数字转换操作和第二模拟-数字转换操作可以在跨行时间的第一非重叠时间段和第二非重叠时间段期间发生。在一些配置中,图像传感器可以进一步包括被配置为存储指示定时的数据的数据存储电路,第一模拟-数字转换器电路和第二模拟-数字转换器电路基于该定时被切换到活动模式。

61.根据一个实施方案,图像传感器可包括:布置成列和行的图像传感器像素;多个读出电路,所述多个读出电路各自耦接到所述图像传感器像素的对应列,所述多个读出电路被配置为在行时间期间执行读出操作;以及控制电路,该控制电路被配置为通过在行时间内的至少第一偏移时间段和第二偏移时间段期间激活多个读出电路,控制多个读出电路针对跨多个读出电路的读出操作执行时域复用。

62.根据另一个实施方案,读出操作可以以线性方式跨行时间发生。

63.根据另一个实施方案,读出操作可以以非线性方式跨行时间发生。

64.根据另一个实施方案,多个读出电路可以各自包括模拟-数字转换器电路,并且读出操作可以包括模拟-数字转换操作。

65.根据另一个实施方案,多个读出电路中的每一个读出电路可以在流水线操作模式下操作,并且读出操作可以包括与模拟-数字转换操作部分并行或部分偏移地执行的采样操作。

66.根据另一个实施方案,图像传感器可以进一步包括多个列路径,多个读出电路各自经由该多个列路径中的相应列路径耦接到图像传感器像素的对应列,并且行时间可以包括针对多个列路径上的像素信号的稳定时间。

67.根据另一个实施方案,多个读出电路可以被配置为在附加的行时间期间执行附加

的读出操作,并且控制电路可以被配置为控制多个读出电路以相比于其中多个读出电路被激活以针对读出操作执行时域复用的次序,通过以不同的次序激活多个读出电路来针对跨多个读出电路的附加的读出操作执行时域复用。

68.根据另一个实施方案,多个读出电路可以被配置为在与图像帧相关联的附加的行时间期间执行附加的读出操作,该图像帧与与行时间相关联的图像帧不同,并且控制电路可以被配置为控制多个读出电路以相比于其中多个读出电路被激活以针对读出操作执行时域复用的次序,通过以不同的次序激活多个读出电路来针对跨多个读出电路的附加的读出操作执行时域复用。

69.根据另一个实施方案,多个读出电路可以各自包括相关双采样电路,并且读出操作可以包括相关双采样操作。

70.根据另一个实施方案,模拟-数字转换操作的发生可以以均匀方式在时间上跨行时间分布。

71.根据另一个实施方案,图像传感器像素可以形成为拼接图像传感器阵列。

72.根据一个实施方案,操作具有布置成列和行的图像传感器像素的图像传感器的方法可以包括:在各自耦接到图像传感器像素的对应列的多个读出电路处接收来自图像传感器像素的行的像素信号;在与所述图像传感器像素的所述行相关联的行时间期间执行读出操作;以及通过在跨行时间的不同时间激活多个读出电路,针对跨多个读出电路的读出操作执行时域复用。

73.根据另一个实施方案,执行读出操作可以包括在行时间期间执行模拟-数字转换操作。

74.根据另一个实施方案,该方法可以进一步包括:在与图像传感器像素的附加的行相关联的附加的行时间期间执行附加的读出操作;以及相比于其中多个读出电路被激活以针对读出操作执行时域复用的方式,通过以不同的方式激活多个读出电路来针对跨多个读出电路的附加的读出操作执行时域复用。

75.根据另一个实施方案,该方法可以进一步包括:在与图像传感器像素的行相关联的附加的行时间期间执行附加的读出操作;以及相比于其中多个读出电路被激活以针对读出操作执行时域复用的方式,通过以不同的方式激活多个读出电路来针对跨多个读出电路的附加的读出操作执行时域复用。

76.根据另一个实施方案,可以以基于图像传感器像素的列的次序的线性进展跨行时间激活多个读出电路。

77.根据另一个实施方案,可以以伪随机进展跨行时间激活多个读出电路。

78.根据一个实施方案,图像传感器可以包括:图像传感器阵列,该图像传感器阵列具有分别布置在第一列和第二列中并且布置在同一行中的第一像素和第二像素;第一模拟-数字转换器电路,所述第一模拟-数字转换器电路使用第一列线耦接到所述第一像素并且被配置为在与针对所述第一像素和所述第二像素的读出操作相关联的行时间期间开始第一模拟-数字转换操作;以及第二模拟-数字转换器电路,该第二模拟-数字转换器电路使用第二列线耦接到第二像素并且被配置为在行时间期间开始第二模拟-数字转换操作。第一模拟-数字转换器电路和第二模拟-数字转换器电路可以分别在跨行时间的第一不同时间和第二不同时间切换到活动模式以开始第一模拟-数字转换操作和第二模拟-数字转换操

作。

79.根据另一个实施方案,第一模拟-数字转换操作和第二模拟-数字转换操作可以在跨行时间的第一非重叠时间段和第二非重叠时间段期间发生。

80.根据另一个实施方案,图像传感器可以进一步包括被配置为存储指示定时的数据的数据存储电路,第一模拟-数字转换器电路和第二模拟-数字转换器电路基于该定时被切换到活动模式。

81.前述内容仅仅是对本发明原理的例示性说明,本领域技术人员可以在不脱离本发明的范围和实质的前提下进行多种修改。上述实施方案可单个实施或以任意组合方式实施。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。