1.本发明的实施例涉及一种硅光子结构及其制造方法及一种晶片级系统。

背景技术:

2.扇出型晶片级封装可用于为将管芯(或芯片)安放在晶片上提供更集成的解决方案。扇出型晶片级封装是集成电路封装技术,以及标准晶片级封装(wafer-level packaging;wlp)解决方案的增强。与常规封装相比,扇出型晶片级封装可提供更小的封装覆盖面积以及改进的热性能和电气性能,且可在不增加管芯大小的情况下允许具有更多数目个触点。在当前解决方案中,wlp技术已演变成建立具有集成扇出型重布线层(integrated fan-out type redistribution layer;info rdl)和嵌入在例如有机层压体或硅的晶片材料中的管芯的封装。

3.扇出的关键部分是重布线层(redistribution layer;rdl)。rdl通常是将封装的一部分电连接到另一部分的铜金属连接线或布线层。rdl取决于用于连接到印刷电路板的引脚或焊料凸块。从成本和空间角度看且由于晶片级封装内的rdl基础架构的电内连的性能,基于传统扇出型重布线层的解决方案可能会受到限制。然而,rdl不是非常适合于支撑提供比由电内连提供的性能更高的性能的光学内连。因此,需要更高效方法以在包含一个或光学集成电路的晶片级封装内提供光学内连。

4.此背景部分中所公开的信息仅意图为下文所描述的本发明实施例的各种实施例提供上下文,且因此,此背景部分可包含不一定是现有技术信息的信息(即,本领域的普通技术人员已知的信息)。因此,在此背景部分中描述工作的范围内,当前署名的发明人的工作以及在提交时可能没有以其它方式取得现有技术的资格的描述的各方面既不明确也不隐含地被认为是针对本公开的现有技术。

技术实现要素:

5.在一些实施例中,硅光子结构(siph)包括电子集成电路(eic)、光子集成电路(pic)、至少一个聚合物波导(pwg)及集成扇出型重布线层(info rdl)。光子集成电路安置在所述电子集成电路的顶部上。至少一个聚合物波导安置在所述光子集成电路的顶部上且形成聚合物桥接层,其中至少一个所述聚合物波导中的每一者包括芯层及至少两个包覆层,所述芯层包括第一聚合物,至少两个所述包覆层包括包围所述芯层的第二聚合物。集成扇出型重布线层安置在两个或大于两个聚合物波导的顶部上。

6.在一些实施例中,晶片级系统包括晶片载体、多个管芯、聚合物波导以及集成扇出型重布线层。多个管芯安置在所述晶片载体上,其中所述多个管芯中的每一个包括至少一个光子集成电路和至少一个电子集成电路。聚合物波导耦合到所述至少一个光子集成电路以提供管芯间光学内连。集成扇出型重布线层安置在所述多个管芯中的每一个的顶部上。所述多个管芯在聚合物波导形成之前接合在所述晶片载体上。

7.在一些实施例中,使用聚合物波导制造硅光子结构的方法包括以下步骤:利用混

合式管芯接合将光子集成电路附接在电子集成电路的顶部上,以形成光子/电子集成电路封装;形成包括至少一个聚合物波导的聚合物波导桥接层,且将所述聚合物波导桥接层安放在所述光子集成电路的顶部上;将至少一个专用集成电路安放在所述光子/电子集成电路封装内;以及在所述聚合物波导桥接层的顶部上形成集成扇出型重布线层。

附图说明

8.当结合附图阅读时,根据以下详细描述最好地理解本公开的各方面。应注意,各种特征未必按比例绘制。实际上,为了清楚说明起见,可任意地增大或减小各种特征的尺寸和几何结构。

9.图1a示出根据一些实施例的包括光子集成电路(photonic integrated circuit;pic)、电子集成电路(electrical integrated circuit;eic)以及包覆层的硅光子(silicon photonic;siph)结构。

10.图1b示出根据本公开的一些实施例的图1a的siph结构,其在包覆层中具有用于第一组通孔的开口。

11.图1c示出根据本公开的一些实施例的图1b的siph结构,其中在包覆聚合物层的第一组通孔中形成薄的镀铜(cu)层。

12.图1d示出根据本公开的一些实施例的图1c的siph结构,其中第一组通孔填充有包覆聚合物层中的镀铜(cu)。

13.图1e示出根据本公开的一些实施例的图1d的siph结构,其中形成安置在包覆层的顶部上的芯层。

14.图1f示出根据本公开的一些实施例的图1e的siph结构,其中在芯层中形成第二组通孔且在芯层中的第二组通孔的开口中形成的薄的镀cu层。

15.图1g示出根据本公开的一些实施例的图1f的siph结构,其中重复图1a到图1d的步骤以形成聚合物波导(polymer waveguide;pwg)。

16.图1h示出根据本公开的一些实施例的根据图1g的siph结构,其中集成接合到玻璃载体的两个asic和管芯。

17.图2a示出根据本公开的一些实施例的根据图1h的siph结构,其中形成pwg桥接层。

18.图2b示出根据本公开的一些实施例的根据图2a的siph结构,其中形成安置在pwg桥接层的顶部上的集成扇出型重布线层(info rdl)。

19.图2c到图2d示出根据本公开的一些实施例的边缘耦合的实施例。

20.图2e、图2f、图2g以及图2h示出根据本公开的一些实施例的层间耦合的实施例。

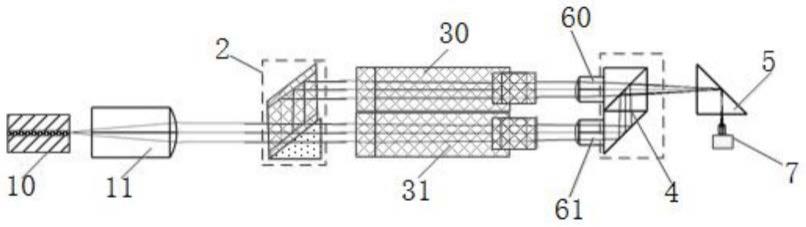

21.图2i示出根据本公开的一些实施例的反射棱镜。

22.图3a示出根据本公开的一些实施例的根据图2b的siph结构,其中光纤接口的实施例由光学透镜和siph光栅耦合器支撑。

23.图3b示出根据本公开的一些实施例的根据图2b的siph结构,其中光纤接口的另一实施例由光学透镜和siph光栅耦合器支撑。

24.图3c示出根据本公开的一些实施例的根据图2b的siph结构,其中光纤耦合到pwg桥接层。

25.图4a示出根据本公开的一些实施例的修改了电子集成电路的根据图3a的siph结

构。

26.图4b示出根据本公开的一些实施例的修改了电子集成电路的根据图3b的siph结构。

27.图4c示出根据本公开的一些实施例的修改了电子集成电路的根据图3c的siph结构。

28.图5示出根据本公开的一些实施例的pwg将pic连接在晶片载体上的晶片级系统。

29.图6示出根据本公开的一些实施例的通过使用聚合物波导制造光子/电子ic封装的示范性siph结构的示范性方法的流程图。

具体实施方式

30.下文参考附图描述本公开的各种示范性实施例,以使得本领域的普通技术人员能够制造和使用本公开。如本领域的普通技术人员将显而易见,在阅读本公开之后,可在不脱离本公开的范围的情况下对本文中所描述的实例进行各种改变或修改。因此,本公开不限于本文中所描述和示出的示范性实施例和应用。另外,本文中所公开的方法中的步骤的特定次序和/或层级仅为示范性方法。基于设计偏好,所公开的方法或工艺的步骤的特定次序或层级可在保持在本公开的范围内的情况下重新布置。因此,本领域的普通技术人员将理解,本文中所公开的方法和技术以样品次序呈现各种步骤或动作,且除非另外明确陈述,否则本公开不限于所呈现的特定次序或层级。另外,本公开可在各种实例中重复参考标号和/或字母。此重复是出于简化和清晰的目的,且本身并不指示所论述的各种实施例和/或配置之间的关系。

31.以下公开描述用于实施主题的不同特征的各种示范性实施例。下文描述组件和布置的特定实例以简化本公开。当然,这些组件和布置仅为实例且并不希望为限制性的。举例来说,应理解,当元件称为“连接到”另一元件或“耦合到”另一元件时,其可直接连接到另一元件或耦合到另一元件,或可存在一个或多个介入元件。此外,为易于描述,本文中可使用例如“在

…

之下(beneath)”、“在

…

下方(below)”、“下部的(lower)”、“底部(bottom)”、“在

…

下面(underneath)”、“在

…

之上(above)”、“上部的(upper)”等的空间相对术语来描述如图式中所示出的一个元件或特征与另一元件或特征的关系。除图式中所描绘的定向之外,空间相对术语意图涵盖器件在使用或操作中的不同定向。

32.根据一些实施例,半导体封装设计包含集成扇出(integrated fan out;info)、晶片级系统集成技术平台以及高密度重布线层(re-distribution layer;rdl)。在一些实施例中,包含硅穿孔(through-silicon via,tsv)以用于例如移动式高性能计算等的各种应用的高密度内连和性能。info平台为针对特定应用优化的2d和3d提供各种封装方案。

33.本文中所描述的实施例公开通过使用聚合物波导而集成的光子-电子ic封装的结构和工艺流程。根据各种实施例,利用由聚合物波导提供的光学内连,可在晶片级平台中实现实质上更高的通信性能和更致密的结构。具有聚合物波导的这些实施例可与info平台兼容。另外,聚合物波导可支撑晶片级系统中的层间光学耦合。根据各种实施例,用于层间耦合的技术包含凹面/凸块、光栅耦合器以及反射棱镜。

34.本文中描述了通过使用聚合物波导而集成的pic封装的示范性实施例。本文中所论述的示范性实施例包含以下硅光子(siph)、重布线层(rdl)、硅穿孔(tsv)、光子集成电路

(pic)、聚合物波导、光学折射率以及光刻的主题。下文简要地论述这些主题。

35.硅光子(siph)是硅集成电路与半导体激光器的组合。与传统电子器件相比,硅光子能够在更长距离上实现更快的数据传输。siph技术通常使用硅作为光信号传输的介质,且可以是用于制造光子集成电路(pic)的材料平台。可以亚微米精度将硅图案化成光子组件。siph的主要优点包含将光学器件和电子器件集成在同一ic内的潜力,以及其与现有互补金属氧化物半导体(complementary metal-oxide semiconductor;cmos)工艺在制造方面的兼容性。

36.光子集成电路(pic)或集成光路是通常与电子集成电路(eic)集成的电路。pic可基于来自eic的输入而产生光信号,通常在可见光谱或850纳米到1650纳米的近红外线内。与硅为主要材料的电子集成不同,系统光子集成电路已由各种材料系统制造,所述材料系统包含例如铌酸锂的电光晶体、硅上二氧化硅、绝缘体上硅、各种聚合物以及用于制备例如gaas和inp的半导体激光器的半导体材料。

37.在集成电路设计中,通孔是绝缘氧化层中的允许不同层之间的导电连接的小开口。硅穿孔(tsv)或芯片穿孔是完全穿过硅晶片或管芯的竖直电连接件。tsv是用作线接合芯片和倒装芯片的替代物以产生3d封装和3d集成电路的高性能内连技术。与诸如层叠式封装的替代物相比,内连线密度和器件密度可显著更高,且连接的长度可减小。

38.重布线层(rdl)为芯片上的额外金属层,所述额外金属层使得集成电路的输入/输出衬垫在芯片的其它位置可用,以用于在必要时提高对衬垫的接入。当制造集成电路时,其可具有线接合到封装的引脚的一组输入/输出衬垫。重布线层可以是芯片上的额外布线层,所述额外布线层能够从芯片上的不同位置接合出来,从而使芯片到芯片接合更简单。使用rdl的另一实例为用于在管芯周围扩散接触点以使得可施加焊料球,且可扩散安装的热应力。作为金属层,rdl支撑集成电路(ic)芯片上的许多位置之间的电连接。

39.根据各种实施例,光学透明聚合物波导(pwg)可用于将硅光子器件介接(interfacing)到光纤。传统地,将聚合物波导加工到硅光子晶片上或接合到芯片。聚合物波导通常是可在小外观尺寸上制造成复杂光学路线的光可图案化材料。聚合物波导可包括芯层和包覆层。包覆层的聚合物将与芯层的聚合物不同。根据这种不同,包覆层中的折射率可比芯层低,使得光信号在芯层中传输同时毗邻包覆层(或由包覆层围绕)。包覆层和芯层可具有2微米到10微米的厚度(或宽度)。另外,芯层可呈梯状以便支撑多模式的信号传输。如本文中所论述,“包覆层”等效于“包覆聚合物层”。类似地,术语“芯层”等效于“芯聚合物层”。

40.在光学器件中,材料的折射率(也称为折射率(refraction index/index of refraction))是描述光传播穿过材料的速度的无量纲数。其定义为n=c/v,其中c是光在真空中的速度,且v是光在介质中的相速度。举例来说,水的折射率为1.333,意指光在水中传播比在真空中慢1.333倍。增加折射率对应于降低光在材料中的速度。典型聚合物具有1.30到1.70的折射率,但对于特定应用通常需要更高的折射率。可基于1.3到2.0的折射率范围来设计聚合物波导。根据各种实施例,聚合物可改性有不同折射率以形成聚合物光波导的不同包覆层/芯结构。

41.根据各种实施例,光刻可用于图案化pwg的包覆层和芯层的层、图案化通孔的开口、图案化tsv及图案的开口,以将光信号引导到不同位置。利用光刻和光刻胶涂布,凹面/

凸块拓扑可形成于包覆聚合物层和芯聚合物层上。

42.根据一些实施例,图1a示出硅光子(siph)结构100,包含:光子集成电路(pic)102;电子集成电路(eic)104;以及第一包覆层106a;多个硅穿孔(tsv)108;第一金属接触件110,安置在第一钝化层114a中;第二金属接触件118,安置在第二钝化层114b中;以及第三钝化层116a,安置在第一钝化层114a中且包围第一金属接触件110;以及第四钝化层116b,安置在第二钝化层114b中且包围第二金属接触件118。如图1a中所绘示,eic 104安置在第一钝化层114a下方,所述第一钝化层114a继而安置在pic 102下方,所述pic 102继而安置在边缘耦合器111下方,所述边缘耦合器111继而安置在包覆层106下方。如图1a中所绘示,边缘耦合器111安置在第二钝化层114b的部分之间的pic 102上方,且将在下文进一步详细论述。

43.根据各种实施例,包覆层106a和包覆层106b可用作波导的包覆层,且eic 104和pic 102可分别为集成光子-电子ic封装提供电子功能和光子功能,如下文进一步详细描述。

44.在一些实施例中,tsv 108具有在1微米(μm)到3微米范围内的直径。举例来说,在一些实施例中,每一tsv 108具有2微米的直径。虽然图1a仅示出两个tsv 108、两个第一金属结构110以及两个第二金属结构118,但应理解,可在pic 102中形成任何期望数目个tsv 108、第一金属结构110以及第二金属结构118。每一tsv 108将金属结构110中的一个电耦合到金属结构118中的一个。在一些实施例中,tsv 108、金属结构110以及金属结构118可由金形成。tsv 108允许siph结构100的不同层中的两个或大于两个中的导电结构之间的导电连接,所述不同层例如但不限于pic 102、eic 104以及第一钝化层114a和第二钝化层114b。如下文进一步详细论述,根据各种实施例,在后续工艺步骤之后,tsv 108可促进eic 104与siph结构100的焊料凸块之间的电连接。

45.在一些实施例中,第一钝化层114a、第二钝化层114b、第三钝化层116a以及第四钝化层116b各自包含氮化硅材料。在一些实施例中,第三钝化层116a和第四钝化层116b中的氮化硅材料的密度小于第一钝化层114a和第二钝化层114b的氮化硅材料的密度。因此,通过分别用第三钝化层116a和第四钝化层116b包围金属结构110和金属结构118中的每一个,可释放邻近于金属结构110和金属结构118的机械应力。

46.图1b示出根据本公开的一些实施例的在对图1a的siph结构100执行其它处理以在第一包覆层106a中形成开口进而提供第一组通孔112和通孔113之后的siph结构110。光刻技术可用以将第一包覆层106a中的开口图案化以形成通孔112和通孔113,所述通孔112和通孔113暴露形成于第二钝化层114b中的对应金属结构118。

47.图1c示出根据本公开的一些实施例的在对图1b的siph结构110执行其它处理以分别在第一包覆层106a的通孔112和通孔113的开口中形成金属镀层122和金属镀123的薄层之后的siph结构120。在一些实施例中,金属镀层122和金属镀层123包含铜(cu)金属。如图1c中所绘示,其它处理包含在第一包覆层106a的顶部表面上形成第一图案化光阻(photo resist;pr)层124,以保护一些区免于刻蚀。在刻蚀以暴露通孔112和通孔113之后,执行晶种层溅镀以在通孔112和通孔113的底部表面和侧表面上形成薄的金属镀层。在一些实施例中,接着进行灰化工艺以从经蚀刻晶片去除第一pr涂层124的残余物。

48.图1d示出根据本公开的一些实施例的在对图1c的siph结构120执行其它处理以用

第一包覆层106a中的金属镀覆材料(例如,铜)完全填充通孔112和通孔113之后的siph结构130。在这个其它处理期间,从第一包覆层106a去除第一pr涂层124,接着再沉积第二pr涂层以分别在通孔112和通孔113上方形成第一pr区126和第二pr区127。

49.图1e示出根据本公开的一些实施例的在对图1d的siph结构130执行其它处理以形成安置在第一包覆层106a的顶部上的芯层107之后的siph结构140。如下文进一步详细描述,根据一些实施例,芯层107提供聚合物波导的芯层。为了支撑波导的设计,第一包覆层106a的折射率低于芯层107的折射率。可针对第一包覆层106a和芯层107选择聚合物,以便达成期望折射率关系。在于通孔112和通孔113上方再沉积第二pr涂层的情况下,减少或最小化芯层107与通孔112和通孔113之间的接触。在一些实施例中,可使芯聚合物和/或包覆聚合物改性以改变其相应折射率。在一些实施例中,可通过掺杂有金属离子和/或卤素离子或通过改变聚合物的固化概况(例如,时间、温度等)来修改每一聚合物的折射率。图1f示出根据本公开的一些实施例在对图1e的siph结构140执行其它处理以分别在芯层107中形成第二组通孔152和通孔153,且在第二组通孔152和通孔153的开口中的每一个中形成金属镀层142和金属镀层143的薄层之后的siph结构150。工艺包含:(1)第三pr涂层145沉积在芯层107的顶部上;(2)刻蚀第二组通孔上方的pr涂层145;接着(3)进行晶种层溅镀以在第二组通孔152和通孔153的开口中涂布金属层142和金属层143的薄层。

50.图1g示出根据本公开的一些实施例的在对图1f的siph结构150执行其它处理以通过重复如上文所论述的图1a到图1d的步骤来形成聚合物波导(pwg)165之后的siph结构160。如图1g中所绘示,可以与如上文关于图1a到图1d所描述的形成第一包覆层106a以及通孔112和通孔113相同的方式来形成第二包覆层106b和另一组通孔162和通孔163。通过这种方式,pwg 165分别由芯层107以及第一包覆层106a和第二包覆层106b形成,使得包覆层106a和包覆层106b毗邻(或包围)芯层107在下文中,第一包覆层106a和第二包覆层106b可统称为包覆层106。由于包覆层106中的折射率小于芯层107,因此光信号在由包覆层106引导的同时在芯层107内部传输。如图1g中所绘示,pwg 165具有为电信号提供电连接的多个金属填充通孔112、通孔152、通孔162、通孔113、通孔153、通孔163。有效地,通孔112、通孔152、通孔162、通孔113、通孔153、通孔163提供形成于pwg层之间的pwg穿孔,以提供层间电连接。

51.在一些实施例中,可基于包覆层106和芯层107两者的1.3到2.0的折射率范围和2微米到10微米的厚度(或宽度)来设计pgw 165。在一些实施例中,芯层107可呈梯状以便支撑多模式的信号传输。如上文所论述,上文所论述的工艺步骤形成pwg 165和穿过pwg 165提供电连接的多个通孔。

52.图1h示出根据本公开的一些实施例的在对图1g的siph结构160执行其它处理以集成管芯接合到玻璃载体174的两个asic 175和asic 176之后的siph结构170。pic 102和eic 104经由混合接合技术附接到一起,以最小化附接asic管芯的厚度以便提高siph结构170的产量。然而,附接asic管芯的厚度可影响晶片级产量。在一些实施例中,存在称作“取放”的info或cowos封装工艺,其中机器拾取管芯且将其放置在载体上,接着启动rdl形成、模制等工艺。如果管芯过薄,那么管芯可能在取放工艺期间断裂,因此较厚管芯可提高封装级产量。另外,在一些实施例中,可存在可基于附接asic的厚度来影响管芯产量的热考量。有效地,附接asic为封装的芯计算块。芯计算块可始终在产生大量热量的重载状态下开启。对于

较厚硅,管芯可充当器件层的局部“散热件”且可正面地影响产量。在一些实施例中,可在eic 104的背侧处添加支撑填充物172。在一些实施例中,支撑填充物172可充当散热器结构以消耗来自eic 104的热能。根据各种实施例,支撑填充物172可以是si或si3n4或sio2。在一些实施例中,支撑填充物由半透明材料制成,以使得光信号可传输穿过支撑填充物172。在一些实施例中,模制/mcg塑胶可以为pgw 165形成提供支撑。

53.如图1h中所绘示,多个(例如,六个)金属结构177和金属结构178分别安置在asic 175和asic 176的顶部上。siph结构170还包含形成于pwg 165中的通孔171和通孔173。在一些实施例中,通孔171由如上文所描述的通孔112、通孔152以及通孔162形成,且通孔173由如上文所描述的通孔113、通孔153以及通孔163形成。在图1h的左侧上存在两个其它对应组的pwg通孔和tsv,所述pwg通孔和tsv可以与上文所描述的对应结构相同的方式形成。前述工艺步骤将asic 175和asic 176安装在siph结构170中且将siph结构170接合到玻璃载体174。在一些实施例中,额外pwg可形成于pwg 165的顶部上。

54.图2a示出根据本公开的一些实施例的在对图1h的siph结构170执行其它处理步骤以形成pwg桥接层202之后的siph结构200。根据图2a,pwg桥接层202形成有安置在第一pwg 165的顶部上的第二pwg 205。根据图2a,pwg 165和pwg 205具有若干通孔。举例来说,通孔204和通孔206可提供从pwg桥接层202的顶部到第二钝化层114b,接着到tsv 108,接着到第一钝化层114a,且接着到eic 104的电连接。位于asic 175和asic 176的顶部上的通孔(例如,通孔207和通孔209)将asic 175和asic 176电连接到其它接触结构(未绘示)。总地来说,pwg 165和pwg 205与其相应通孔形成pwg桥接层202。

55.图2b示出根据本公开的一些实施例的在对图2a的siph结构200执行其它处理以形成安置在pwg桥接层202的顶部上的集成扇出型重布线层(info rdl)211之后的siph结构210。info 211包括与包覆层106相同的聚合物。info rdl支撑电信号且可用于连接到两个asic 175和176或连接穿过通孔的电信号。在siph结构210与其它导电结构(例如,导电凸块、衬垫或其它管芯的线、电路等(未绘示))之间提供电连接的多个导电凸块213制造于info rdl 211的顶部上。info rdl 211经由pwg桥接层202的顶部上的通孔(诸如通孔207和通孔209)为asic 175和asic 176提供电连接。在一些实施例中,在形成info rdl 211之后,玻璃载体174从asic 175和asic 176以及充填物172的底部剥离。因此,siph结构210为pic 102、eic 104、asic 175以及asic 176提供耦合以允许这些组件之间的内连。在完成前述工艺步骤之后,siph结构210通过使用聚合物波导来表示光子/电子ic封装的示范性实施例。

56.图2b还指示安置在边缘耦合器111内的边缘耦合器208的位置,所述边缘耦合器208可提供聚合物波导与硅波导之间的接口。将相对于图2c进一步论述边缘耦合。如前文所述,pwg桥接层202包括pwg 165和pwg 205。在pwg桥接层202内,可提供层间耦合,如将相对于图2e、图2f、图2g以及图2h论述。

57.图2c示出根据本公开的一些实施例的边缘耦合器208。根据图2b,指出边缘耦合器208在siph结构210中的位置。根据图2c,边缘耦合器208提供硅波导212与可以是如上文所论述的pwg 165的pwg 214之间的耦合。具有锥形件216的硅波导212在pwg 214中突出。利用硅波导212的尖的形状,光可“挤压”到pwg 214中。因此,利用边缘耦合器208,光可从硅波导212传送到pwg 214。边缘耦合器208具有与边缘耦合器111相同的功能。

58.图2d示出根据本公开的替代实施例的光栅耦合器220的实施例。光栅耦合器220将

光信号从硅波导222耦合到芯层107,即聚合物波导。芯层107由包覆层106包围。光栅耦合器220分别包含上部光栅结构226和下部光栅结构224,其中光的方向由硅波导222中的下部光栅结构224改变,且光由芯层107中的上部光栅结构226收集。在图2d中通过虚线228示出光的方向。在一些实施例中,光栅耦合器220由硅与聚合物材料的组合制造。

59.在比较边缘耦合器208与光栅耦合器220时,光栅耦合器220需要更少的空间但具有比边缘耦合器208更多的信号丢失。因此,在更高的性能和更少的信号丢失是重要的且设计支撑空间需求的情况下,边缘耦合可以是优选的。设计和选择可通过光信号的波长来判定。对于一些实施例,波长可以是800纳米、1310纳米或1510纳米。

60.图2e、图2f、图2g以及图2h示出根据本公开的一些实施例的聚合物波导内的层间耦合的实施例。本文中先前所描述的实施例支撑用于光信号传输的一个层。利用层间耦合,光信号可在若干聚合物层之间传送或耦合在若干聚合物层之间。

61.图2e示出多个包覆层106a、包覆层106b、包覆层106c与多个芯层107a和芯层107b之间的层间耦合230。聚合物层可在其表面上形成一些凹面/凸块拓扑,以便于将光信号232从一个pwg层传送到另一pwg层。如图2e中所绘示,光信号232传播穿过芯层107a且经由包覆层106b的相对较薄部分耦合到芯层107b。如图2e中进一步绘示,芯层107b在包覆层106b的相对较薄部分(比包覆层106b的其它部分薄)处朝向芯层107a向下弯曲和突出。包覆层106a和包覆层106c完成聚合物波导的结构,如图2e中所绘示。

62.图2f示出多个包覆层106a、包覆层106b以及包覆层106c与多个芯层107a和芯层107b之间的层间耦合240的类似实施例。聚合物层可在表面上形成一些凹面/凸块拓扑,以便于将光信号242从一个pwg层传送到另一pwg层。与图2e相比,图2f示出聚合物波导的包覆层和芯层的不同形状图案。光信号242的方向调整到聚合物波导中的形状图案。对于图2f,光信号242传播穿过芯层107a且经由包覆层106b的相对较薄部分耦合到芯层107b。在这一实施例中,芯层107a的一部分在包覆层106b的相对较薄部分处朝向芯层107b向上弯曲和突出。包覆层106a和包覆层106c完成聚合物波导的结构。

63.图2g示出根据本公开的一些实施例的用于聚合物波导内的层间耦合的光栅耦合器250。如所示出,光信号252传播穿过芯层107a到达与芯层107a相关联的下部光栅结构254。接着,改变光信号252的方向且引导其穿过包覆层106b到达芯层107b中的上部光栅结构256。芯层107b中的上部光栅结构256收集光信号252且改变光信号252的方向以允许传播穿过芯层107b。在一些实施例中,光栅耦合器250的所有元件由聚合物或包覆聚合物或芯聚合物制成。相比之下,根据一些实施例,图2d的光栅耦合器220由硅与聚合物的组合制造。

64.图2h示出具有反射棱镜的聚合物波导内的层间耦合结构260。可通过局部改变pwg中的折射率来形成反射棱镜,以在一方向上将光从一个层反射到另一层。可通过各种方法来修改折射率。举例来说,修改可以是改变掺杂在聚合物内部的金属或cu,或可以是改变制造工艺。总之,通过改变包覆层和芯层的层中的至少一个中的折射率而形成的反射棱镜允许光信号从一个pwg层反射到另一pwg层。

65.如图2h中所示出,光信号262沿着芯层107a向下传播且由第一棱镜264反射。光信号262接着传播穿过包覆层106b到达芯层107b,其中光信号262由第二棱镜266反射。接着引导光信号262沿着芯层107b向下传播。图2h中的其它包覆层包含包覆层106a和包覆层106c。

66.图2i示出根据本公开的一些实施例的反射棱镜270。反射棱镜270包括具有漏斗形

状的芯层107,其中包覆层106毗邻(或包围)漏斗形状的芯层107,且漏斗形状的芯层107的较窄端突出穿过包覆层材料。如图2i中所绘示,当漏斗形状的芯层107从第一宽度变窄到比第一宽度窄的第二宽度时,包覆层106对应地变得更厚。在一些替代实施例中,反射棱镜可由没有任何聚合物层的玻璃形成。

67.图3a、图3b以及图3c示出siph封装的光纤接口的三个实施例:(1)图3a——光传播穿过siph封装内的填充物;(2)图3b——光传播穿过pwg桥接层内的包覆层;以及(3)图3c——光纤直接耦合到pwg桥接层。在以下段落中进一步论述这些实施例。

68.根据一些实施例,图3a的siph结构300将光学封装与外部光源连接。根据本公开的一些实施例,siph结构300与图2b的siph结构210类似,其中光纤接口由光学透镜303a、光学透镜303b、siph光栅耦合器304a以及siph光栅耦合器304b支撑。光信号从光纤302a和光纤302b发射,且分别耦合到光学透镜303a和光学透镜303b。光信号从光学透镜303a和光学透镜303b投射穿过siph结构300的包含支撑填充物172、eic 104、钝化层114、pic 102的若干层,且分别耦合到siph光栅耦合器304a和siph光栅耦合器304b。siph光栅耦合器304a和siph光栅耦合器304b具有与如上文相对于图2d所论述的光栅耦合器220类似的信号功能。根据各种实施例,光学透镜303a和光学透镜303b由聚合物和/或硅形成。总之,来自光纤302a和光纤302b的光信号分别耦合到光学透镜303a和光学透镜303b,所述光学透镜303a和光学透镜303b引导相应光信号穿过支撑填充物172、eic 104、pic102,且接着分别到达siph光栅耦合器304a和siph光栅耦合器304b。

69.根据一些实施例,图3b的siph结构320将光学封装与外部光源连接。根据本公开的一些实施例,siph结构320与图2b的siph结构210类似,但添加了由光学透镜323a、光学透镜323b、siph光栅耦合器324a以及siph光栅耦合器324b支撑的光纤接口。光信号从光纤322a和光纤322b发射,且分别耦合到光学透镜323a和光学透镜323b。光信号从光学透镜323a和光学透镜323b投射穿过info rdl 211和pwg桥接层202,且分别耦合到siph光栅耦合器324a和siph光栅耦合器324b。siph光栅耦合器324a和siph光栅耦合器324b具有与如上文相对于图2d所论述的光栅耦合器220类似的功能。总之,光纤耦合到每一光学透镜323a和光学透镜323b,所述光学透镜323a和光学透镜323b引导光信号穿过info rdl 211,穿过聚合物桥接层202,分别到达siph光栅耦合器324a和siph光栅耦合器324b。

70.根据一些实施例,图3c的siph结构340将光学封装与外部光源连接。根据本公开的一些实施例,siph结构340与图2b的siph结构210类似,其中添加了耦合到pwg桥接层202的光纤342。光信号从光纤342发射且在pwg桥接层202的横向侧部分处直接耦合到pwg桥接层202。从光纤342到pwg 165,光信号可具有有源对准。在一些实施例中,机器可跟踪光强度以确保光纤的芯和pwg的芯在光学上对准。从pic 102到封装的横向侧处的另一芯片,光信号可从pwg 165耦合到pwg 205且从pwg 205耦合到pwg 165,且接着耦合到封装的横向侧(例如,图3c的siph结构340的右侧)上的另一芯片。在一些实施例中,可通过在图2e、图2f、图2g以及图2h中所公开的方法来实现pwg 165与pwg 205之间的耦合。

71.图4a示出根据本公开的一些实施例的与图3a的siph结构300类似但修改了电子集成电路的siph结构400。减小图3a的eic 104的长度,如图4a的eic 404a和eic 404b所示出。因此,eic 404a和eic 404b的大小可小于pic 102。如所示出,为了填充所得间隙,填充间隙402a和填充间隙402b分别安置成邻近于eic 404a和eic 404b。填充间隙402a和eic 404a的

长度与安置在填充间隙402a和eic 404a下方的pic 102的长度类似。填充间隙402b和eic 404b的尺寸与asic 175和asic 176的相对侧上的pic 102的尺寸类似。在一些实施例中,填充间隙402a和填充间隙402b可通过沉积填充有si/sio2/si3n4。在一些实施例中,与穿透eic 404a和eic 404b相比,光可更高效地穿透填充间隙402a和填充间隙402b。额外益处在于由于硅对温度敏感,因此填充间隙402a、填充间隙402b可充当eic或asic的散热件。

72.图4b示出根据本公开的一些实施例的与图3b的siph结构320类似但修改了电子集成电路的siph结构420。修改基本上与图4a的siph结构400进行的修改相同。减小eic 104的长度,如eic 404a和eic 404b所示出。分别邻近于eic 404a和eic 404b添加填充间隙402a和填充间隙402b。对于这一实施例,添加填充间隙402a和填充间隙402b不会影响光穿透,但作为eic或asic的散热物是有益的。

73.图4c示出根据本公开的一些实施例的与图3c的siph结构340类似但修改了电子集成电路的siph结构440。如相对于图3c所论述,光纤342直接耦合到pwg桥接层202。pwg桥接层202包括pwg 165和pwg 205。电子集成电路修改与根据图4a的siph结构400进行的修改基本上相同。减小eic 104的长度,如eic 404a和eic 404b所示出。对于这一实施例,添加填充间隙402a和填充间隙402b不会影响光穿透,但所述添加作为eic或asic的散热件是有益的。

74.图5示出根据本公开的一些实施例的利用一个或多个pwg将pic连接在晶片载体上的晶片级系统500。除芯片(或管芯)在形成pwg之前接合在载体上之外,方法利用与先前所描述的相同的工艺流程。根据各种实施例,载体可以是玻璃、硅、金属、聚合物、环氧模制化合物或金刚石。如所示出,芯片形成于晶片(例如12英寸的晶片)上以形成晶片上系统(system on wafer;sow)。如所示出,每一方形表示具有包含pic 502和eic 504的多个组件的芯片。每一芯片可基于pic和eic的设计和其它设计元素而包括不同功能。利用基于图2b的siph结构210的芯片,芯片通过pwg 506耦合。作为光学波导,与电连接相比,pwg 506提供更快通信,传输更长距离且具有更致密的结构。在空间和信号丢失问题方面,仅基于电连接的晶片级系统可能需要放大器或可避免使用pwg的其它组件。

75.图6示出根据本公开的一些实施例的通过使用聚合物波导来制造光子/电子ic封装的示范性siph结构的示范性方法的流程图600。下文所公开的示范性方法叙述用于制造如图2b的siph结构210的工艺流程步骤作为一个实例。示范性方法包括以下步骤:利用混合式管芯接合将pic 102附接在eic 104的顶部上。钝化层114a安置在pic 102与eic之间(步骤602);在pic 102中形成tsv以允许siph结构210的层(例如,包覆层106a和钝化层114a)之间的导电连接(步骤604);通过组合两个或大于两个pwg(例如,pwg 165和pwg 205)形成pwg桥接层202,且将两个或大于两个pwg安放在pic 102的顶部上(步骤606);在pwg桥接层202内形成通孔(步骤608);将asic安放在光子/电子ic封装内(步骤610);在pwg桥接层202的顶部上形成info rdl 211(步骤612);将支撑填充物附接在eic下方(步骤614);以及将支撑填充物和asic附接到载体,例如玻璃载体(步骤616)。

76.根据本公开的各种实施例,可改变流程图600中的步骤的次序。

77.在一个示范性实施例中,公开一种硅光子(siph)结构。这一实施例包括:电子集成电路(eic);光子集成电路(pic),安置在eic的顶部上;两个或大于两个聚合物波导(pwg),安置在pic的顶部上且形成聚合物桥接层,其中两个或大于两个pwg中的每一个包括芯层,所述芯层包括第一聚合物。至少两个包覆层包括毗邻芯层的第二聚合物。siph结构还包括

安置在两个或大于两个pwg顶部上的集成扇出型重布线层(info rdl)。如果基于第二聚合物的折射率小于第一聚合物的折射率,那么光信号传播穿过芯层,且可使第一聚合物和第二聚合物中的至少一个改性以改变其相应折射率。可通过光刻将第一聚合物的层和第二聚合物的层图案化以促进波导图案、通孔孔洞以及凹面/凸块拓扑的实施。siph结构包括形成于pwg层之间以提供层间电连接的pwg穿孔,以及在siph结构层之间提供电连接的硅通孔(tsv)。siph结构可更包括层间光信号耦合器,所述层间光信号耦合器能够操作以用于经由一个包覆层将光信号从一个芯层传送到另一芯层。层间光信号耦合器可制造有光栅耦合器,其中每一光栅结构形成于安放在一个包覆层之间的一个芯层和另一芯层中。层间光信号耦合器也可由制造有形成于第一聚合物的层和第二聚合物的层的表面上的凹面/凸块拓扑。层间光信号耦合器也可制造有通过改变两个或大于两个pwg中的至少一个中的折射率形成的反射棱镜。

78.在一些实施例中,用于所述两个或大于两个聚合物波导的聚合物设计用于1.3到2.0的折射率范围。在一些实施例中,所述第一聚合物和所述第二聚合物中的至少一个被修改以改变其相应折射率。在一些实施例中,通过光刻将所述第二聚合物和所述第一聚合物的层图案化以促进波导图案、通孔孔洞以及凹面/凸块拓扑的实施。在一些实施例中,所述硅光子结构更包括形成于两个或大于两个所述聚合物波导的层之间以提供层间电连接的聚合物波导穿孔。在一些实施例中,至少一个所述聚合物波导包括第一聚合物波导和形成于所述第一聚合物波导上方的第二聚合物波导,且所述硅光子结构更包括层间光信号耦合器,所述层间光信号耦合器能够操作以用于经由至少一个所述包覆层将光信号从所述第一聚合物波导的第一芯层传送到所述第二聚合物波导的第二芯层。在一些实施例中,所述层间光信号耦合器包括光栅耦合器,所述光栅耦合器具有形成于一个芯层中的第一光栅结构和形成于另一芯层中的第二光栅结构。在一些实施例中,所述层间光信号耦合器制造有形成于所述第一聚合物的所述层和所述第二聚合物的所述层的表面上的凹面/凸块拓扑。在一些实施例中,述层间光信号耦合器在两个或大于两个所述聚合物波导中制造有反射棱镜,其中所述反射棱镜通过改变所述第一聚合物波导和所述第二聚合物波导中的至少一个中的折射率而形成。在一些实施例中,所述硅光子结构更包括在所述硅光子结构的两个或大于两个层之间提供电连接的硅穿孔(tsv)。在一些实施例中,所述芯层具有漏斗形状,且所述包覆层毗邻所述漏斗形状的所述芯层,且所述漏斗形状的所述芯层的较窄端突出穿过所述第一包覆层以提供反射棱镜。在一些实施例中,所述硅光子结构更包括光学透镜和硅光子光栅耦合器,其中光纤耦合到引导光信号穿过支撑填充物、所述电子集成电路以及所述光子集成电路到达所述硅光子光栅耦合器的所述光学透镜。在一些实施例中,所述硅光子结构更包括光学透镜和硅光子光栅耦合器,其中光纤耦合到引导光信号穿过所述集成扇出型重布线层和所述聚合物桥接层到达所述硅光子光栅耦合器的所述光学透镜。在一些实施例中,所述光学透镜由聚合物和硅形成。在一些实施例中,所述硅光子结构更包括耦合到所述聚合物桥接层的光纤。

79.在另一实施例中,晶片级系统包括:晶片载体;多个管芯,安置在晶片上,其中多个管芯中的每一个包括至少一个光子集成电路(pic)和至少一个电子集成电路(eic);聚合物波导,耦合到至少一个pic以提供管芯间光学内连;以及集成扇出型重布线层(info rdl),安置在多个管芯中的每一个的顶部上。多个管芯在形成聚合物波导之前接合在晶片载体

上。晶片载体包括玻璃、硅、金属、聚合物、环氧模制化合物或金刚石。

80.在一些实施例中,所述晶片载体包括玻璃、硅、金属、聚合物、环氧模塑化合物和金刚石中的至少一种。

81.在又另一实施例中,一种使用聚合物波导制造siph结构的方法可包含以下步骤:利用混合式管芯接合将语音集成电路(pic)附接在电子集成电路(eic)的顶部上,其中无源层114a安置在pic 102与eic之间;在pic中形成硅穿孔(tsv)以允许包覆层与钝化层之间的导电连接;在pic的顶部上形成包括两个或大于两个pwg的聚合物波导(pwg)桥接层;在pwg桥接层的pwg内形成通孔;将asic安放在光子/电子ic封装内;在pwg桥接层的顶部上形成集成扇出型重布线层(info rdl);将支撑填充物附接在eic下方;以及将支撑填充物和asic附接到载体,例如玻璃载体。

82.在又另一实施例中,一种使用聚合物波导制造siph结构的方法可包含以下步骤:利用混合式管芯接合将光子集成电路(pic)附接在电子集成电路(eic)的顶部上,以形成光子/电子集成电路(ic)封装;形成包括至少一个聚合物波导(pwg)的聚合物波导桥接层,且将所述聚合物波导桥接层安放在所述光子集成电路的顶部上;将至少一个专用集成电路安放在所述光子/电子集成电路封装内;以及在所述聚合物波导桥接层的顶部上形成集成扇出型重布线层(info rdl)。

83.在一些实施例中,使用聚合物波导制造硅光子结构的方法更包括:在所述聚合物波导桥接层内形成通孔;以及在所述光子集成电路中形成硅穿孔(tsv),以允许硅光子结构层之间的导电连接。在一些实施例中,使用聚合物波导制造硅光子结构的方法更包括:在所述电子集成电路下方形成支撑填充物;以及将所述支撑填充物和所述至少一个专用集成电路附接到载体。

84.前文概述若干实施例的特征以使得本领域的普通技术人员可更好地理解本公开的方面。本领域的技术人员应了解,其可容易地将本公开用作设计或修改用于进行本文中所引入的实施例的相同目的和/或达成相同优点的其它工艺和结构的基础。本领域的技术人员还应认识到,这类等效构造并不脱离本公开的精神和范围,且其可在不脱离本公开的精神和范围的情况下在本文中作出各种改变、替代以及更改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。