1.本公开关于频率合成器,尤其涉及具有可调压控振荡器(voltage-controlled oscillator,vco)的频率合成器及方法。

背景技术:

2.无线局域网(wireless local area network,wlan)无线电收发器用来发送和接收无线电信号的射频合成器(radio frequency synthesizer)约涵盖4.8ghz至7.2ghz的范围。在零中频(zero intermediate frequency(zero-if))无线电收发器中,需要一种可以产生与无线电信号相同频率的时钟的频率合成器。因此,零中频无线局域网无线电收发器需要一个频率合成器,该频率合成器可以生成频率范围约为4.8ghz至7.2ghz的时钟。频率合成器通常以包含锁相回路(phase lock loo,pll)的时钟倍频器单元(clock multiplier unit,cmu)来实现。锁相回路的关键组件是压控振荡器,压控振荡器用来输出时钟,时钟的频率可调且在闭回路状态下控制,因此可以精确地决定时钟的频率。对压控振荡器而言,其可调范围越广,设计就越困难。

3.举例来说,美国专利10,404,316公开了一种利用频率合成器的零中频无线局域网无线电收发器,该频率合成器需要一个可调范围从7.68ghz至9.60ghz的压控振荡器。

4.因此需要一种频率合成器,该频率合成器降低了对压控振荡器的可调范围的要求,但仍可以满足零中频无线局域网无线电收发器所需的频率范围。

技术实现要素:

5.本发明的一实施例提供一种频率合成器,包含:一时钟倍频器单元,用来接收一第一时钟并根据一倍数输出一第二时钟;一比三分频电路,用来接收该第二时钟并输出一第三时钟;一第一一比二分频电路,用来接收该第二时钟并输出一第四时钟;一第二一比二分频电路,用来接收该第四时钟并输出一第五时钟;一第一多工器,用来接收该第三时钟及该第四时钟,并根据一第一选择信号输出一第七时钟;一第二多工器,用来接收该第三时钟及该第五时钟,并根据一第二选择信号输出一第八时钟;以及一混频器,用来接收该第七时钟及该第八时钟并输出一输出时钟。

6.本发明的另一实施例提供一种频率合成方法,包含:接收一第一时钟;根据一倍数,使用一时钟倍频器单元将该第一时钟倍频为一第二时钟;使用一比三分频电路将该第二时钟分频为一第三时钟;使用一第一一比二分频电路将该第二时钟分频为一第四时钟;使用一第二一比二分频电路将该第四时钟分频为一第五时钟;使用一第一多工器根据一第一选择信号在该第三时钟及该第四时钟之间进行选择来输出一第七时钟;使用一第二多工器根据一第二选择信号在包含该第三时钟及该第五时钟的多个时钟中进行选择来输出一第八时钟;以及通过使用一混频器混频该第七时钟与该第八时钟来产生一输出时钟。

附图说明

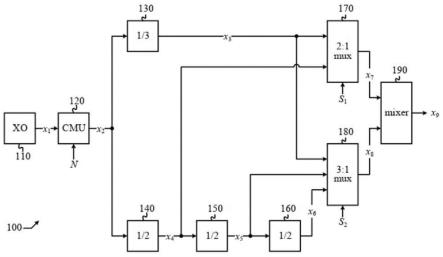

7.图1显示本公开一实施例的频率合成器的功能方框图;

8.图2显示一比二分频电路的示意图;

9.图3显示一比三分频电路的示意图;以及

10.图4显示本公开一实施例的频率合成方法的流程图。

11.符号说明

12.100:频率合成器

13.110:晶体振荡器(“xo”)

14.120:时钟倍频器单元(“cmu”)

15.130:一比三分频电路(“1/3”)

16.140、150、160:一比二分频电路(“1/2”)

17.170:二对一多工器(“2:1mux”)

18.180:三对一多工器(“3:1mux”)

19.190:混频器(“mixer”)

20.200:一比二分频电路

21.210:数据触发器

22.300:一比三分频电路

23.310、320、330:数据触发器

24.340、350:与非门

25.400:流程图

26.410、420、430、440、450、470、480、490:步骤

具体实施方式

27.本公开涉及频率合成器。虽然说明书描述了本公开中实施本发明的数个示例性的实施例,但是应当理解,本发明可以以多种方式实现,并且不限于以下描述的特定示例或是实作该些示例的任何特征的特定方式。在其他情况下,为了专注于讨论本公开的各个层面,不显示或描述众所周知的细节。

28.本技术领域技术人员理解本公开中所使用的与微电子有关的术语和基本概念,例如“电压”、“信号”、“时钟”、“频率”、“锁相回路”、“数据触发器(data flip flop)”、“边缘触发(edge trigger)”、“与非门(nand gate)”、“混频器(mixer)”、“逻辑信号”、“三态信号(ternary signal)”、“四相时钟”、“多工器”及“时钟倍频器单元(clock multiplier unit,cmu)”。这类的术语在微电子学的领域中使用,并且相关的概念对于本技术领域技术人员而言是显而易见的,因此这里将不进行详细说明。

29.本技术领域技术人员可以阅读包含诸如数据触发器及与非门等元件的电路的示意图,并且不需要关于在示意图中一个元件如何连接另一元件的详细描述。本技术领域技术人员亦了解诸如吉赫兹(giga-hertz,ghz)等单位,并且不需要进一步的说明。

30.一个电路是晶体管、电容器、电阻器及/或其他电子装置的集合,以某种方式互连以实现某种功能。

31.所谓的信号,指的是准位可变的电压,其准位承载某个信息,并且会随时间变化。

信号在某一时刻的准位表示该时刻该信号的状态。

32.逻辑信号是有两种状态的电压信号:低准位状态和高准位状态。低准位状态也称为“0”状态,而高准位也称为“1”状态。关于逻辑信号q,当人们说“q为高准位”或“q为低准位”时,意思是指“q处于高准位状态”或“q处于低准位状态”。同样,当人们说“q为1”或“q为0”时,意思是“q处于1的状态”或“q处于0的状态”。

33.当逻辑信号从低准位切换到高准位时,会呈现上升缘。当逻辑信号从高准位切换到低准位时,会呈现下降缘。

34.如果第一逻辑信号和第二逻辑信号总是处于相反的状态,则第一逻辑信号被称作是第二逻辑信号的反相或反相逻辑。也就是说,当第一逻辑信号为1时,第二逻辑信号为0;当第一逻辑信号为0时,第二逻辑信号为1。当第一逻辑信号是第二逻辑信号的反相逻辑时,意思是第一逻辑信号与第二逻辑信号互补。

35.三态信号是可以由两个逻辑信号表示的有三种状态的一个复合信号。

36.时钟是一种在低准位和高准位之间周期性地来回切换的逻辑信号。当时钟从低准位切换到高准位,然后再从高准位切换到低准位,即完成了一个周期。时钟的频率代表时钟在一秒内完成的周期数。

37.数据触发器(data flip-flop,dff)在标记为“d”的数据引脚上接收输入信号,并根据以楔形符号标记的触发引脚上的触发信号在标记为“q”的输出引脚上输出输出信号,以及在标记为“qb”的互补输出引脚上输出互补输出信号。输入信号,输出信号,互补输出信号和触发信号均为逻辑信号。对于正(负)缘触发的数据触发器而言,其在触发信号的上升(下降)缘时,将输入信号的状态载入(loaded)输出信号,而将输入信号的相反状态载入互补输出信号。数据触发器的预设是正缘触发的。当数据触发器为负缘触发时,在触发引脚上会放置一个小圆圈,以标示触发信号的逻辑反相。

38.多工器接收若干个输入,并根据选择信号在该若干个输入中进行选择来产生一输出,该选择信号具有若干个状态,分别对应到该若干个输入。二对一多工器接收两个输入,并根据选择信号产生一输出,该选择信号是逻辑信号,并且具有分别对应到该两个输入的两个状态。三对一多工器接收三个输入,并根据选择信号产生一输出,该选择信号是三态信号(ternary signal),并且具有分别与该三个输入相对应的三个状态。

39.图1显示本公开一实施例的频率合成器100的功能方框图。频率合成器100包含时钟倍频器单元(以“cmu”表示)120、一比三分频电路(以“1/3”表示)130、第一一比二分频电路(以“1/2”表示)140、第二一比二分频电路(以“1/2”表示)150、第三一比二分频电路(以“1/2”表示)160、二对一多工器(以“2:1mux”表示)170、三对一多工器(以“3:1mux”表示)180,以及混频器(以“mixer”表示)190。时钟倍频器单元120用来接收第一时钟x1并根据倍数(multiplication factor)n输出第二时钟x2。举例来说(但不以此为限),第一时钟x1由晶体振荡器(以“xo”表示)110产生。一比三分频电路130用来接收第二时钟x2并输出第三时钟x3。第一一比二分频电路140用来接收第二时钟x2并输出第四时钟x4。第二一比二分频电路150用来接收第四时钟x4并输出第五时钟x5。第三一比二分频电路160用来接收第五时钟x5并输出第六时钟x6。二对一多工器170用来接收第三时钟x3及第四时钟x4,并根据第一选择信号s1输出第七时钟x7。三对一多工器180用来接收第三时钟x3、第五时钟x5及第六时钟x6,并根据第二选择信号s2输出第八时钟x8。混频器190用来接收第七时钟x7及第八时钟x8,并

输出第九时钟x9。第九时钟x9即频率合成器100的输出。在一些实施例中(作为示例而非限制),频率合成器100的目的是使第九时钟x9是可调的(覆盖从4.80ghz到7.2ghz的(频率)范围),而无需时钟倍频器单元120具有宽广的可调(频率)范围。

40.一比二分频电路(例如一比二分频电路140、150及160)接收输入时钟并输出输出时钟,使得输出时钟的频率等于输入时钟的频率的一半。图2显示一比二分频电路的一范例的示意图,一比二分频电路200可以用来实现一比二分频电路140、150及160。一比二分频电路200包含一个数据触发器210,其具有数据引脚(标记为“d”)、输出引脚(标记为“q”)、互补输出引脚(标记为“qb”)以及触发引脚(以楔形符号标记)。数据触发器210以负反馈的方式配置,以根据输入时钟的触发来输出输出时钟。一比二分频电路200以及数据触发器(例如数据触发器210)的符号、功能、原理及电路实现方式为本技术领域技术人员所熟知,因此这里不再详细描述。

41.一比三分频电路(例如一比三分频电路130)接收输入时钟并输出输出时钟,使得输出时钟的频率等于输入时钟的频率的三分之一。图3显示一比三分频电路的一范例的示意图,一比三分频电路300可以用来实现一比三分频电路130。一比三分频电路300包含三个数据触发器310、320及330,以及与非门(nand gate)340与350。数据触发器310、数据触发器320以及与非门340实现了除以三的功能,该功能是现有技术中众所周知的,因此在此不进行详细描述。数据触发器330和与非门350用于使输出时钟具有50%的工作周期(非必须,但有帮助)。这些在现有技术中是众所周知的,因此这里不再详细描述。需注意的是,数据触发器330是负缘触发的(如在触发引脚上的小圆圈所示,表示逻辑反相),而数据触发器310及数据触发器320是正缘触发的。

42.令时钟x1、x2、x3、x4、x5、x6、x7、x8及x9的频率分别为f1、f2、f3、f4、f5、f6、f7、f8及f9。x1是由晶体振荡器110输出,其频率f1精准度高且稳定。晶体振荡器在现有技术中是众所周知的,因此这里不再详细描述。时钟倍频器单元120用来使x2的频率等于x1的频率乘以倍数n,即

43.f2=n

·

f1ꢀꢀ

(1)

44.在一个实施例中,倍数n是一个包含整数部分和小数部分的数字。在一个实施例中,时钟倍频器单元120是分数-n锁相回路(fractional-n pll),包含用来生成第二时钟x2的压控振荡器。第二时钟x2以闭回路方式被控制以追踪第一时钟x1的相位。分数-n锁相回路在现有技术中是众所周知的,因此这里不再详细描述。分数-n锁相回路的例子可以参阅美国专利7,498,856。

45.一比三分频电路130用来使x3的频率等于x2的频率的三分之一,即

46.f3=f2/3

ꢀꢀ

(2)

47.第一一比二分频电路140用来使x4的频率等于x2的频率的一半,即

48.f4=f2/2

ꢀꢀ

(3)

49.第二一比二分频电路150用来使x5的频率等于x4的频率的一半,即

50.f5=f4/2

ꢀꢀ

(4)

51.第三一比二分频电路160用来使x6的频率等于x5的频率的一半,即

52.f6=f5/2

ꢀꢀ

(5)

53.二对一多工器170执行时钟选择功能;第一选择信号s1为逻辑信号(可能的状态为

0或1)。当s1为0时,x3被选取;当s1为1时,x4被选取。即:

[0054][0055]

二对一多工器在现有技术中是众所周知的,因此这里不再详细描述。现有技术中已知有许多实现方式,本技术领域技术人员可以自行选择。

[0056]

三对一多工器180执行时钟选择功能;第二选择信号s2是一个三态信号(ternary signal)(可能的状态为0、1或2)。当s2为0时,x3被选取;当s2为1时,x5被选取;当s2为2时,x6被选取。即:

[0057][0058]

三对一多工器在现有技术中是众所周知的,因此这里不再详细描述。现有技术中已知有许多实现方式,本技术领域技术人员可以自行选择。

[0059]

混频器190执行x7和x8的频率混合,使得x9的频率等于x7的频率与x8的频率的和,即:

[0060]

f9=f7 f8ꢀꢀ

(8)

[0061]

基于方程式(2)、(3)、(4)、(5)、(6)、(7)及(8),f2与f9之间的关系可以根据s1和s2的状态建立如下表所示:

[0062][0063]

因此,f9的范围很广:可以低至11f2/24,以及高至5f2/6。

[0064]

混频器在现有技术中是众所周知的,因此这里不再详细描述。现有技术中已知有许多实施方式,本技术领域技术人员可以自行选择来实现混频器190。在一个实施例中,混频器190包含谐振电路(resonant tank),该谐振电路被调谐(tune)到期望的频率x9以抑制不想要的混合产物。此概念以及实施方式在现有技术中是众所周知的,因此这里不再详细描述。在一个实施例中,混频器190是单边带(single-sideband,ssb)混频器,并且x3、x4、x5、x6、x7及x8都是四相时钟。“单边带混频器”及“四相时钟”是本技术领域技术人员众所周知的,因此这里不再详细描述。在美国专利10,250,189中可以找到单边带混频器的实施方式,这也是使用谐振电路来抑制不想要的混合产物的一个例子。在一个实施例中,美国专利10,613,575中公开的正交时钟产生器被用于实现一比二分频电路140、150及160;在此情况下,

x4、x5及x6即为四相时钟。在一个实施例中,美国专利10,469,061所公开的正交时钟产生器被整合进一比三分频电路130中,使得x3可以是四相时钟。

[0065]

在一个实施例中(作为示例而非限制):频率合成器100被用于零中频无线局域网无线电收发器中,在该零中频无线局域网无线电收发器中,需要频率范围为4.80ghz至7.20ghz的时钟;f1是40mhz;倍数n介于192和216之间;f2介于7.680ghz与8.640ghz之间;f9介于4.80ghz与7.20ghz之间;以及s1和s2的状态列于下表:

[0066]

f9(ghz)f2(ghz)s1f7(ghz)s2f8(ghz)4.80~5.127.680~8.19213.840~4.09620.960~1.0245.12~5.767.680~8.64002.560~2.88002.560~2.8805.76~6.487.680~8.64013.840~4.32011.920~2.1606.48~7.207.776~8.64013.888~4.32002.592~2.880

[0067]

也就是说,通过适当地设置s1和s2的状态,f9可以覆盖从4.80ghz到7.20ghz的范围,而f2的范围从7.680ghz到8.640ghz。这意味着,当时钟倍频器单元120由包含压控振荡器的分数-n锁相回路实现时,对压控振荡器的可调范围的要求是从7.680ghz到8.640ghz。如此一来,相较于美国专利10,404,316的公开内容,本发明大大降低了对压控振荡器的可调范围的要求。

[0068]

请注意,某些无线电收发器可能不需要(f9的)介于4.80ghz与5.12ghz之间的频率范围。在这种情况下,不需要第六时钟x6及s2=2的状态,因此可以通过去除第三一比二分频电路160来简化频率合成器100,并且由于第六时钟x6可以从最初的选项中移除,所以三对一多工器180可以化简为二对一多工器,以及第二选择信号s2成为逻辑信号。换句话说,第三一比二分频电路160可视情况选择要不要有,取决于是否需要介于4.80ghz与5.12ghz之间的频率范围。

[0069]

如图4的流程图400所示,一种频率合成方法包含以下步骤:(步骤410)接收第一时钟;(步骤420)基于一个倍数,利用时钟倍频器单元将第一时钟倍频为第二时钟;(步骤430)使用一比三分频电路将第二时钟分频为第三时钟;(步骤440)使用第一一比二分频电路将第二时钟分频为第四时钟;(步骤450)使用第二一比二分频电路将第四时钟分频为第五时钟;(步骤470)通过使用第一多工器根据第一选择信号在第三时钟和第四时钟之间进行选择来输出第七时钟;(步骤480)通过使用第二多工器根据第二选择信号从多个时钟(包含第三时钟及第五时钟)中进行选择来输出第八时钟;(步骤490)通过使用混频器混频第七时钟与第八时钟来产生输出时钟。

[0070]

本领域技术人员将容易地观察到,在保持本公开的教导的同时,可以对装置和方法进行多种修改和变更。因此,以上的公开内容不应被解释为仅由权利要求的界限来限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。