半导体存储装置

1.【关联申请】

2.本技术享受以日本专利申请2021-27174号(申请日:2021年2月24日)为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的的全部内容。

技术领域

3.本发明的实施方式涉及半导体存储装置。

背景技术:

4.近年来,已知有能够通过将形成有存储单元阵列的芯片与形成有周边电路的芯片接合来形成的半导体存储装置。

技术实现要素:

5.实施方式提供芯片面积较小的半导体存储装置。

6.实施方式的半导体存储装置具备:第1基板;周边电路,设在第1基板上;层叠体,设在周边电路的上方,将多个第1导电层与多个第1绝缘层在第1方向上交替地层叠;第1柱,在第1方向上贯通层叠体内,包括半导体层,在半导体层与多个第1导电层的交点处形成存储单元;第2基板,设在层叠体及第1柱的上方,具有与半导体层电连接的第1区域和配置在第1区域的与第1方向交叉的第2方向上的第2区域;第2绝缘层,在第1方向上贯通第2基板内,在与第1方向及第2方向交叉的第3方向上延伸,将第1区域与第2区域电绝缘;以及第2导电层,具有在第1方向上贯通第2基板的第1部分、以及在第2基板的上方沿第2方向延伸且包括作为接合焊盘的区域的第2部分。第2部分在第1方向上与上述第2绝缘层重叠。

附图说明

7.图1是表示半导体存储装置的构成例的框图。

8.图2是表示存储单元阵列的电路构成的电路图。

9.图3是用来说明存储器1的第1例的示意图。

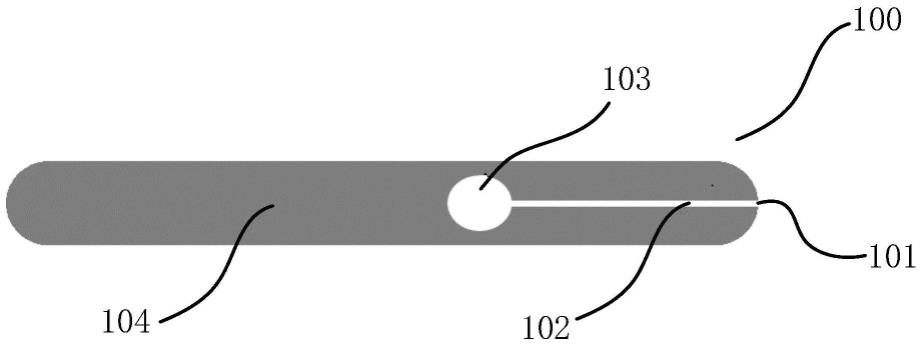

10.图4是表示芯片1b的构造例的俯视示意图。

11.图5是表示图4所示的芯片1b的一部分的俯视示意图。

12.图6是用来说明存储器1的第1例的截面构造例的剖视示意图。

13.图7是表示存储柱mp的构造例的剖视示意图。

14.图8~图18是用来说明存储器1的第1例的制造方法例的剖视示意图。

15.图19是表示存储器1的第2例中的芯片1b的一部分的俯视示意图。

16.图20是用来说明存储器1的第2例的截面构造例的剖视示意图。

17.图21是表示存储器1的第3例中的芯片1b的一部分的俯视示意图。

18.图22是用来说明存储器1的第3例的截面构造例的剖视示意图。

19.图23是表示存储器1的第4例中的芯片1b的一部分的俯视示意图。

20.图24是用来说明存储器1的第4例的截面构造例的剖视示意图。

21.图25是表示存储器1的第5例中的芯片1b的一部分的俯视示意图。

22.图26是用来说明存储器1的第5例的截面构造例的剖视示意图。

23.图27是表示存储器1的第6例中的芯片1b的一部分的俯视示意图。

24.图28是用来说明存储器1的第6例的截面构造例的剖视示意图。

25.图29是表示存储器1的第7例中的芯片1b的一部分的俯视示意图。

26.图30是用来说明存储器1的第7例的截面构造例的剖视示意图。

具体实施方式

27.以下,参照附图对实施方式进行说明。图中记载的各构成要素的厚度与平面尺寸的关系、各构成要素的厚度的比率等有与实物不同的情况。此外,在实施方式中,对于实质上相同的构成要素赋予相同的附图标记并适当省略说明。

28.图1是表示半导体存储装置的构成例的框图。半导体存储装置具备存储器1和存储器控制器2。

29.存储器1包括存储单元阵列10、命令寄存器11、地址寄存器12、定序器13、驱动器14、行解码器15和读出放大器16。

30.存储单元阵列10包括多个块blk(blk0~blk(l-1)(l是2以上的自然数))。块blk是非易失性地存储数据的多个存储晶体管mt的集合。

31.存储单元阵列10经由后述的多个位线bl与读出放大器16连接。存储单元阵列10如后述那样,包括多个字线wl,并经由它们与行解码器15连接。各存储晶体管mt(存储单元)与多个字线wl中的一个字线wl及多个位线bl中的一个位线bl连接。

32.命令寄存器11保持从存储器控制器2接收到的命令信号cmd。命令信号cmd例如包括使定序器13执行读出动作、写入动作及擦除动作的命令数据。

33.地址寄存器12保持从存储器控制器2接收到的地址信号add。地址信号add例如包括块地址ba、页地址pa及列地址ca。例如,块地址ba、页地址pa及列地址ca分别被用于块blk、字线wl及位线bl的选择。

34.定序器13对存储器1的动作进行控制。定序器13基于例如保持在命令寄存器11中的命令信号cmd对驱动器14、行解码器15及读出放大器16等进行控制,执行读出动作、写入动作及擦除动作等的动作。

35.驱动器14生成在读出动作、写入动作及擦除动作等中使用的电压。并且,驱动器14例如基于保持在地址寄存器12中的页地址pa,向与被选择的字线wl对应的信号线施加所生成的电压。

36.行解码器15基于保持在地址寄存器12中的块地址ba,选择对应的存储单元阵列10内的1个块blk。并且,行解码器15例如将向与所选择的字线wl对应的信号线施加的电压向被选择的块blk内的被选择的字线wl转送。

37.读出放大器16在写入动作中,根据从存储器控制器2接收到的写入数据dat,向各位线bl施加希望的电压。此外,读出放大器16在读出动作中,基于位线bl的电压判定存储在存储单元中的数据,将判定结果作为读出数据dat向存储器控制器2转送。

38.存储器1与存储器控制器2之间的通信例如支持nand接口标准。例如,存储器1与存

储器控制器2之间的通信使用命令锁存使能信号cle、地址锁存使能信号ale、写使能信号wen、读使能信号ren、就绪繁忙信号rbn及输入输出信号i/o。

39.命令锁存使能信号cle表示存储器1接收到的输入输出信号i/o是命令信号cmd。地址锁存使能信号ale表示接收到的信号i/o是地址信号add。写使能信号wen是向存储器1发出命令以进行输入输出信号i/o的输入的信号。读使能信号ren是向存储器1发出命令以进行输入输出信号i/o的输出的信号。

40.就绪繁忙信号rbn是向存储器控制器2通知存储器1是受理来自存储器控制器2的命令的就绪状态还是不受理命令的繁忙状态的信号。

41.输入输出信号i/o例如是8比特宽的信号,可以包括命令信号cmd、地址信号add、写入数据信号dat等的信号。

42.以上说明的存储器1及存储器控制器2也可以由它们的组合构成1个半导体存储装置。这样的半导体存储装置的例子包括例如sd卡那样的存储卡或固态硬盘驱动器(ssd)。

43.接着,对存储单元阵列10的电路构成例进行说明。图2是表示存储单元阵列10的电路构成的电路图。图2例示块blk0,但其他块blk的构成也相同。

44.块blk包括多个串单元su。各串单元su包括多个nand串ns。另外,图2图示了3个串单元su(su0~su2),但串单元su的数量没有被特别限定。

45.各nand串ns与多个位线bl(bl0~bl(n-1)(n是2以上的自然数))中的一个连接。各nand串ns包括存储晶体管mt、选择晶体管st1和选择晶体管st2。

46.存储晶体管mt包括控制栅极和电荷贮存层,非易失地保持数据。图2图示多个存储晶体管mt(mt0~mt(m-1)(m是2以上的自然数)),但存储晶体管mt的数量没有被特别限定。另外,各nand串ns也可以包括具有与存储晶体管mt的构造相同的构造、但不被用于数据的保持的虚设存储晶体管。

47.存储晶体管mt既可以是分别在电荷贮存层中使用绝缘膜的monos型,也可以是在电荷贮存层中使用导电体层的fg型。以下,在本实施方式中以monos型为例进行说明。

48.选择晶体管st1被用于各种动作时的串单元su的选择。选择晶体管st1的数量没有被特别限定。

49.选择晶体管st2被用于各种动作时的串单元su的选择。选择晶体管st2的数量没有被特别限定。

50.在各nand串ns中,选择晶体管st1的漏极与对应的位线bl连接。选择晶体管st1的源极与串联连接的存储晶体管mt的一端连接。串联连接的存储晶体管mt的另一端与选择晶体管st2的漏极连接。

51.在相同的块blk中,选择晶体管st2的源极与源极线sl连接。各串单元su的选择晶体管st1的栅极分别与对应的选择栅极线sgd连接。存储晶体管mt的控制栅极分别与对应的字线wl连接。选择晶体管st2的栅极与对应的选择栅极线sgs连接。

52.被分配了相同的列地址ca的多个nand串ns在多个块blk间与相同的位线bl连接。将源极线sl在多个块blk间连接。

53.(存储器1的第1例)

54.图3是用来说明存储器1的第1例的示意图。图3图示沿着芯片的表面方向的x轴方向、与x轴大致垂直的y轴方向、与x轴及y轴大致垂直地交叉的z轴方向。另外,存储器1的构

造并不限定于第1例。

55.图3所示的存储器1具备芯片1a和芯片1b。芯片1a和芯片1b被相互接合而形成chip bonding array(cba)构造。

56.芯片1b包括存储单元阵列10。在图3的例子中,存储器1是4平面结构,具有4个存储单元阵列10,但存储单元阵列10的数量(平面的数量)并不限定于图3所示的数量。

57.芯片1a包括命令寄存器11、地址寄存器12、定序器13、驱动器14、行解码器15、读出放大器16等周边电路110。图3图示芯片1b与存储单元阵列10的数量对应而具有4个周边电路110的例子,但周边电路110的数量只要与存储单元阵列10的数量对应即可,并不限定于图3所示的数量。各周边电路110控制对应的存储单元阵列10。各周边电路110从z方向观察与对应的存储单元阵列10重叠。

58.图4是表示芯片1b的构造例的俯视示意图,表示x-y平面。芯片1b具有包括存储单元阵列10的区域r1、设在区域r1的周围的区域r2以及将区域r1与区域r2电绝缘的绝缘分离体vz。如图4所示,绝缘分离体vz例如以将区域r1包围的方式设置。多个区域r1通过绝缘分离体vz被相互电绝缘。

59.图5是表示图4所示的芯片1b的一部分的俯视示意图,表示x-y平面。如图5所示,存储单元阵列10包括存储单元区域a1、虚设台阶区域a2和虚设单元区域a3。关于各个区域的说明在后面叙述。此外,在存储单元阵列10之上设有接合焊盘pd。

60.图6是用来说明存储器1的第1例的截面构造例的剖视示意图,图示沿着基板200的表面的x轴方向、沿着该表面与x轴大致垂直的y轴方向、以及与该表面大致垂直地交叉的z轴方向。

61.图6所示的芯片1a具有设在基板200上的场效应晶体管tr1及场效应晶体管tr2、导电层201、导电层202、导电层203、导电层205、导电层206和绝缘层207。

62.图6所示的芯片1b具备基板210、绝缘层211、导电层212、半导体层213、存储器层215、半导体层216、芯绝缘层217、插塞218、导电层219、导电层220、导电层221、导电层222、绝缘层231、绝缘层232、导电层233、绝缘层234、绝缘层235和绝缘层236。导电层212、半导体层213、存储器层215及半导体层216构成存储单元阵列10。区域r1及区域r2设在基板200的上方。

63.基板200例如是硅基板等的半导体基板。

64.场效应晶体管tr1设在存储单元阵列10的下方。场效应晶体管tr2设在插塞218的下方。场效应晶体管tr1、tr2分别是n沟道型晶体管或p沟道型晶体管。场效应晶体管tr1、tr2构成周边电路110中的某一个。场效应晶体管tr1、tr2分别被元件分离体sti分离。

65.导电层201构成接触插塞。导电层202构成配线层。导电层202的配线例如经由导电层201的接触插塞与场效应晶体管tr1或场效应晶体管tr2的栅极、源极、漏极中的某一个连接。导电层201及导电层202包含金属材料。

66.导电层203构成接触插塞。导电层204构成配线层。导电层204的配线例如经由导电层203的接触插塞而与导电层202的配线中的某一个连接。导电层203及导电层204包含金属材料。

67.导电层205构成接触插塞。导电层206构成包括连接焊盘的层。导电层206的连接焊盘例如经由导电层205的接触插塞而与导电层204的配线中的某一个连接。导电层205及导

电层206包含金属材料。

68.绝缘层207将场效应晶体管tr1与场效应晶体管tr2之间、配线之间绝缘。绝缘层207例如包含氧化硅。另外,场效应晶体管tr1及场效应晶体管tr2也可以经由未图示的其他配线层或接触插塞而与存储单元阵列10连接。

69.基板210具有在区域r1的层叠体20及存储柱mp的上方设置的基板部210a和在区域r2的上方设置的基板部210b。基板部210a及基板部210b通过绝缘分离体vz而相互被电绝缘。基板部210a例如与半导体层213电连接。基板部210b在基板部210a的y轴方向上配置。基板210例如是硅基板等的半导体基板。

70.多个绝缘层211的每一个及多个导电层212的每一个在z轴方向上被交替地层叠而形成层叠体20。层叠体20沿着y轴方向从存储单元区域a1延伸到虚设台阶区域a2为止。多个导电层212分别构成选择栅极线sgs、字线wl、选择栅极线sgd。绝缘层211例如包含氧化硅。导电层212包含金属材料。

71.半导体层213设在基板210上。半导体层213经由基板210而与未图示的源极线sl电连接。半导体层213例如是单晶硅层或多晶硅层。另外,并不限定于此,也可以在构成存储单元的沟道的半导体层(半导体层216)的侧面上形成与构成源极线sl的导电层之间的电连接。

72.在存储单元区域a1中,存储器层215、半导体层216及芯绝缘层217构成存储柱mp。存储柱mp设在存储单元区域a1的层叠体20内。存储单元区域a1是形成存储单元的区域,1个存储柱mp对应于1个nand串ns。

73.虚设台阶区域a2具有在从存储单元区域a1延伸的层叠体20的y轴方向的端部设置的台阶部stp。台阶部stp阶梯状地设有多个绝缘层211及多个导电层212的每一个。台阶部stp是与周边电路110电绝缘的虚设的台阶部。

74.虚设单元区域a3在y轴方向上设在存储单元区域a1与虚设台阶区域a2之间。在虚设单元区域a3中,存储器层215、半导体层216及芯绝缘层217构成与周边电路110电绝缘的虚设存储柱dmp。虚设存储柱dmp包括不与位线bl及字线wl连接的存储单元。虚设存储柱dmp在虚设单元区域a3中设在层叠体20内。虚设存储柱dmp设在存储柱mp与台阶部stp之间。虚设存储柱dmp具有与存储柱mp同样的构造。

75.存储柱mp及虚设存储柱dmp如图6所示,在z轴方向上贯通层叠体20内而延伸。存储柱mp及虚设存储柱dmp的各构成要素沿着z轴方向延伸。

76.图7是用来说明存储柱mp的构造例的剖视示意图,表示y-z截面。图7图示绝缘层211、导电层212、存储器层215、半导体层216和芯绝缘层217。另外,虚设存储柱dmp由于具有与存储柱mp同样的构造,所以适当援用存储柱mp的构造例的说明。

77.存储器层215具有块绝缘膜215a、电荷贮存膜215b和隧道绝缘膜215c。

78.块绝缘膜215a、隧道绝缘膜215c及芯绝缘层217例如包含氧化硅。电荷贮存膜215b例如包含氮化硅。半导体层216例如包含多晶硅。

79.更具体地讲,在z轴方向上将层叠体20贯通而形成与存储柱mp对应的孔。在孔的侧面上依次层叠有块绝缘膜215a、电荷贮存膜215b及隧道绝缘膜215c。并且,以侧面与隧道绝缘膜215c相接的方式形成半导体层216。

80.半导体层216沿着z轴方向将层叠体20贯通。半导体层216具有选择晶体管st1、选

择晶体管st2、存储晶体管mt的沟道区域。由此,半导体层216作为将选择晶体管st1、选择晶体管st2、存储晶体管mt的电流路径连接的信号线发挥功能。

81.芯绝缘层217设在半导体层216的内侧。芯绝缘层217沿着半导体层216延伸。

82.存储柱mp与构成各字线wl的导电层212的交点作为存储晶体管mt发挥功能。存储柱mp与构成各选择栅极线sgd的导电层212的交点作为选择晶体管st1发挥功能。存储柱mp与构成各选择栅极线sgs的导电层212的交点作为选择晶体管st2发挥功能。

83.插塞218设在基板200的上方的区域r2中。插塞218在z轴方向上延伸。插塞218将导电层233的连接部233a与周边电路110电连接。图6表示2个插塞218,但插塞218的数量并不限定于图6所示的数量。

84.导电层219构成接触插塞。导电层220构成配线层。导电层220的配线经由导电层219的接触插塞而与插塞218中的某一个电连接。此外,导电层220的配线层包括位线bl。位线bl经由导电层219的接触插塞而与存储柱mp中的某一个连接。导电层219及导电层220包含金属材料。

85.导电层221构成接触插塞。导电层222包括连接焊盘。导电层222的连接焊盘经由导电层221的接触插塞而与导电层220电连接。导电层221及导电层222包含金属材料。

86.导电层222的连接焊盘与导电层206的连接焊盘接合。由此,能够将例如存储柱mp与具有场效应晶体管tr1的周边电路110电连接,并且将插塞218与具有场效应晶体管tr1的周边电路110电连接。

87.绝缘层223将存储单元阵列10的各配线间绝缘。绝缘层223例如包含氧化硅。

88.绝缘层231设在基板210之上。绝缘层231例如包含氧化硅。

89.绝缘层232包括绝缘分离体vz。绝缘分离体vz设在区域r2中。绝缘分离体vz在z轴方向上贯通基板210内,在x轴方向上延伸,将基板部210a与基板部210b电绝缘。图6所示的绝缘分离体vz在z轴方向上与层叠体20不重叠。绝缘层232例如包含氧化硅。

90.导电层233构成图5所示的接合焊盘pd。导电层233隔着绝缘层232而设在基板210的上方。导电层233的配线包括连接部233a和焊盘部233b。

91.连接部233a在z轴方向上贯通基板210及绝缘层231而设在插塞218之上。由此,导电层233与插塞218电连接,并经由插塞218、导电层219、导电层220、导电层222、导电层206、导电层205、导电层204、导电层203、导电层202及导电层201与周边电路110电连接。图6所示的连接部233a及插塞218在z轴方向上不与层叠体20重叠。

92.焊盘部233b包括作为供接合线接合的接合焊盘pd的区域。焊盘部233b在从连接部233a起到虚设台阶区域a2及虚设单元区域a3的基板部210a的上方沿y轴方向延伸。焊盘部233b从绝缘层234、绝缘层235及绝缘层236露出。在图6中,焊盘部233b在z轴方向上与绝缘分离体vz重叠。

93.连接部233a及焊盘部233b由相同的材料形成。连接部233a及焊盘部233b例如包含铝等的金属材料。

94.绝缘层234、绝缘层235及绝缘层236依次被设置在导电层233的上方。绝缘层234、绝缘层235及绝缘层236构成钝化膜。绝缘层234例如包含氧化硅。绝缘层235例如包含氮化硅。绝缘层236例如包含聚酰亚胺。

95.如以上这样,存储器1的第1例具有在z轴方向上接合焊盘pd的焊盘部与存储单元

阵列10的虚设台阶区域a2及虚设单元区域a3重叠的构造。

96.在将接合焊盘pd设在区域r2侧的情况下,由于需要增大区域r2的面积,所以芯片面积变大。相对于此,在z轴方向上,通过使包括作为接合焊盘pd的区域的焊盘部233b与存储单元阵列10重叠,能够减小芯片面积。

97.此外,存储器1的第1例在供存储单元阵列10形成的基板210内具有绝缘分离体vz。绝缘分离体vz在z轴方向上与导电层233的焊盘部233b重叠。由此,即使是形成包括存储单元阵列10的多个区域r1的情况,也能够将该多个区域r1相互电绝缘并且抑制基板210的裂纹。此外,在形成多个接合焊盘pd的情况下,通过省略用来将多个接合焊盘pd相互电绝缘的绝缘分离体,由此能够抑制与绝缘分离体vz的干涉。

98.接着,对存储器1的第1例的制造方法例进行说明。图8至图18是用来说明存储器1的第1例的制造方法例的剖视示意图,表示y-z截面。

99.首先,如图8所示,分别准备晶片w1和晶片w2。晶片w1包括多个芯片1a。晶片w2包括多个芯片1b。图8所示的晶片w2的朝向与图6所示的晶片w2的朝向相反。

100.晶片w1通过在基板200上形成场效应晶体管tr1、场效应晶体管tr2等的晶体管,然后在基板200上形成导电层201、导电层202、导电层203、导电层205、导电层206及绝缘层207来制造。

101.晶片w2通过在基板210上形成半导体层213、层叠体20、存储柱mp、虚设存储柱dmp、插塞218、导电层219、导电层220、导电层221、导电层222及绝缘层223来制造。

102.接着,如图9所示,使晶片w2的朝向反转,将晶片w1与晶片w2贴合。在本说明书中,贴合表示在热处理前使晶片w1与晶片w2密接的处理。

103.然后,将晶片w1与晶片w2接合。在本说明书中,接合表示将晶片w1和晶片w2牢固地固定的处理。将晶片w1及晶片w2例如通过热处理而接合。导电层206及导电层222例如通过金属间的元素扩散、范德华力(van der waals force)、体积膨胀或熔融带来的再结晶化等被直接接合。进而,通过绝缘层207与绝缘层223之间的元素扩散、范德华力、脱水缩合或聚合物化等的化学反应带来的直接接合,或金属与绝缘层间的接合,能够将晶片w1与晶片w2接合。将这些接合也称作混合接合。另外,图9表示了晶片w1与晶片w2的界面(贴合面)s,但是有在热处理后不能明确地观察界面s的情况。

104.接着,如图10所示,将基板210部分地除去,由此将基板210加工得较薄。基板210例如可以通过湿式蚀刻而被部分地除去。优选的是以使基板210的阱区域残留的方式将基板210加工得较薄。

105.接着,如图11所示,在基板210之上形成绝缘层231。

106.接着,如图12所示,将基板210及绝缘层231部分地除去而形成开口h1和开口h2,由此使绝缘层223及插塞218部分地露出。开口h1设在图6所示的供连接部233a形成的区域中。开口h2设在图6所示的供绝缘分离体vz形成的区域中。通过开口h2,基板210被分割为包括基板部210a和基板部210b的多个区域。基板210及绝缘层231例如可以使用反应性离子蚀刻(rie)部分地除去。

107.接着,如图13所示,在开口h2处形成包括绝缘分离体vz的绝缘层232。绝缘层232例如形成在绝缘层231的表面及开口h1、h2内。进而,如图13所示,在绝缘层232之上,形成具有开口h1的抗蚀剂层241。开口h1使绝缘层232的一部分露出。

108.接着,如图14所示,将绝缘层232的露出部除去,使插塞218露出。绝缘层232的露出部例如可以使用rie除去。

109.接着,如图15所示,在绝缘层232之上形成导电层233,在导电层233之上形成抗蚀剂层242,将抗蚀剂层242部分地除去,在将形成连接部233a及焊盘部233b的区域覆盖的原状下使导电层233部分地露出。

110.接着,如图16所示,使用抗蚀剂层242作为掩模,将导电层233的露出部部分地除去。导电层233例如可以使用rie部分地除去。

111.接着,如图17所示,在导电层233之上,依次形成绝缘层234、绝缘层235、绝缘层236。

112.接着,如图18所示,将绝缘层234、绝缘层235及绝缘层236部分地除去,由此形成使供导电层233的焊盘部233b形成的区域露出的开口h3。绝缘层234、绝缘层235及绝缘层236例如可以使用rie部分地除去。

113.然后,将晶片w1及晶片w2通过切割(dicing)而切断为多个芯片。以使这些芯片包括1个芯片1a和1个芯片1b的方式进行切断。通过以上的工序,能够制造存储器1。以上是存储器1的第1例的制造方法例的说明。

114.(存储器1的第2例)

115.参照图19及图20对存储器1的第2例进行说明。图19是表示存储器1的第2例的芯片1b的一部分的俯视示意图,表示x-y平面。图20是用来说明存储器1的第2例的截面构造例的剖视示意图,图示沿着基板200的表面的x轴方向、沿着该表面与x轴大致垂直的y轴方向、以及与该表面大致垂直地交叉的z轴方向。另外,关于与第1例相同的部分,在这里省略说明,以下对与第1例不同的部分进行说明。

116.存储器1的第2例与存储器1的第1例相比,不同点在于:在z轴方向上焊盘部233b与虚设单元区域a3重叠、绝缘分离体vz与虚设台阶区域a2重叠。其以外的部分是与图6所示的存储器1同样的构造,所以这里省略说明,以下对不同的部分进行说明。

117.绝缘分离体vz在z轴方向上与台阶部stp重叠。绝缘分离体vz例如在存储器1的第1例的制造方法例中通过将图12所示的使绝缘层211部分地露出的开口h2以与台阶部stp重叠的方式形成、并在开口h2上形成绝缘层232而设置。

118.焊盘部233b从连接部233a延伸到虚设单元区域a3的上方。焊盘部233b从绝缘层234、绝缘层235及绝缘层236露出。

119.在存储器1的第2例中,具有在z轴方向上接合焊盘pd的焊盘部与存储单元阵列10的存储单元区域a1、虚设台阶区域a2及虚设单元区域a3重叠的构造。由此,能够减小芯片面积。此外,在存储器1的第2例中,将绝缘分离体vz以与虚设台阶区域a2重叠的方式形成。通过绝缘分离体vz,即使在形成包括存储单元阵列10的多个区域r1的情况下,也能够将该多个区域r1相互电绝缘并且抑制基板210的裂纹。此外,在形成多个接合焊盘pd的情况下,通过将用来将多个接合焊盘pd相互电绝缘的绝缘分离体省略,由此能够抑制与绝缘分离体vz的干涉。

120.另外,存储器1的第2例可以与存储器1的其他例适当组合。

121.(存储器1的第3例)

122.参照图21及图22对存储器1的第3例进行说明。图21是表示存储器1的第3例的芯片

1b的一部分的俯视示意图,表示x-y平面。图22是用来说明存储器1的第3例的截面构造例的剖视示意图,图示沿着基板200的表面的x轴方向、沿着该表面与x轴大致垂直的y轴方向、以及与该表面大致垂直地交叉的z轴方向。另外,关于与第1例相同的部分,在这里省略说明,以下对与第1例不同的部分进行说明。

123.存储器1的第3例与存储器1的第1例相比,不同点在于:在z轴方向上连接部233a将台阶部stp与虚设台阶区域a2重叠、焊盘部233b与存储单元区域a1重叠、绝缘分离体vz与虚设单元区域a3重叠、插塞218设在虚设台阶区域a2中。其以外的部分是与图6所示的存储器1同样的构造,所以这里省略说明,以下对不同的部分进行说明。

124.绝缘分离体vz在z轴方向上不与虚设存储柱dmp重叠。绝缘分离体vz例如在存储器1的第1例的制造方法例中,通过将图12所示的开口h2形成在虚设单元区域a3中、并在开口h2形成绝缘层232而设置。

125.插塞218在包括台阶部stp的虚设台阶区域a2中在z轴方向上贯通层叠体20内。另外,通过在插塞218的侧面上形成绝缘体,能够与层叠体20电绝缘。插塞218在虚设台阶区域a2中经由导电层219、导电层220、导电层222、导电层206、导电层205、导电层204、导电层203、导电层202及导电层201而与周边电路110电连接。

126.连接部233a在虚设台阶区域a2中设在插塞218上。连接部233a在z轴方向上与台阶部stp重叠。由此,导电层233与插塞218电连接,经由插塞218、导电层219、导电层220、导电层222、导电层206、导电层205、导电层204、导电层203、导电层202及导电层201与周边电路110电连接。

127.焊盘部233b从连接部233a延伸到存储单元区域a1的上方。焊盘部233b从绝缘层234、绝缘层235及绝缘层236露出。

128.在存储器1的第3例中,具有在z轴方向上接合焊盘pd的焊盘部与存储单元阵列10的存储单元区域a1及虚设单元区域a3重叠的构造。由此,能够减小芯片面积。此外,在存储器1的第3例中,将绝缘分离体vz以与虚设台阶区域a2重叠的方式形成。通过绝缘分离体vz,即使在形成包括存储单元阵列10的多个区域r1的情况下,也能够将该多个区域r1相互电绝缘并且抑制基板210的裂纹。此外,在形成多个接合焊盘pd的情况下,通过省略用来将多个接合焊盘pd相互电绝缘的绝缘分离体,能够抑制与绝缘分离体vz的干涉。

129.另外,存储器1的第3例可以与存储器1的其他例适当组合。

130.(存储器1的第4例)

131.参照图23及图24对存储器1的第4例进行说明。图23是表示存储器1的第4例的芯片1b的一部分的俯视示意图,表示x-y平面。图24是用来说明存储器1的第4例的截面构造例的剖视示意图,图示沿着基板200的表面的x轴方向、沿着该表面与x轴大致垂直的y轴方向、以及与该表面大致垂直地交叉的z轴方向。另外,关于与第1例相同的部分,在这里省略说明,以下对与第1例不同的部分进行说明。

132.存储器1的第4例与存储器1的第1例相比,不同点在于:在z轴方向上连接部233a与虚设台阶区域a2重叠、焊盘部233b与存储单元区域a1重叠、绝缘分离体vz不与虚设台阶区域a2重叠、并且插塞218设在虚设台阶区域a2中。其以外的部分是与图6所示的存储器1同样的构造,所以这里省略说明,以下对不同的部分进行说明。

133.插塞218在包括台阶部stp的虚设台阶区域a2中在z轴方向上贯通层叠体20。另外,

通过在插塞218的侧面形成绝缘体,由此能够与层叠体20电绝缘。插塞218在虚设台阶区域a2中经由导电层219、导电层220、导电层222、导电层206、导电层205、导电层204、导电层203、导电层202及导电层201而与周边电路110电连接。

134.连接部233a设在基板210的基板部210a与绝缘分离体vz之间。连接部233a在z轴方向上与台阶部stp重叠。连接部233a在虚设台阶区域a2中设在插塞218上。由此,导电层233与插塞218电连接,经由插塞218、导电层219、导电层220、导电层222、导电层206、导电层205、导电层204、导电层203、导电层202及导电层201而与周边电路110电连接。

135.焊盘部233b从连接部233a延伸到存储单元区域a1的上方。焊盘部233b从绝缘层234、绝缘层235及绝缘层236露出。

136.绝缘分离体vz在z轴方向上不与台阶部stp重叠。绝缘分离体vz例如在存储器1的第1例的制造方法例中通过将图12所示的开口h2以不与台阶部stp重叠的方式形成、并在开口h2上形成绝缘层232来设置。

137.在存储器1的第4例中,具有在z轴方向上接合焊盘pd的焊盘部与存储单元阵列10的存储单元区域a1及虚设单元区域a3重叠的构造。由此,能够减小芯片面积。此外,在存储器1的第4例中,形成为使连接部233a与虚设台阶区域a2重叠、使绝缘分离体vz不与虚设台阶区域a2重叠。通过绝缘分离体vz,即使在形成包括存储单元阵列10的多个区域r1的情况下,也能够将该多个区域r1相互电绝缘并且抑制基板210的裂纹。此外,在形成多个接合焊盘pd的情况下,通过省略用来将多个接合焊盘pd相互电绝缘的绝缘分离体,能够抑制与绝缘分离体vz的干涉。

138.另外,存储器1的第4例可以与存储器1的其他例适当组合。

139.(存储器1的第5例)

140.参照图25及图26对存储器1的第5例进行说明。图25是表示存储器1的第5例的芯片1b的一部分的俯视示意图,表示x-y平面。图26是用来说明存储器1的第5例的截面构造例的剖视示意图,图示沿着基板200的表面的x轴方向、沿着该表面与x轴大致垂直的y轴方向、以及与该表面大致垂直地交叉的z轴方向。另外,关于与第1例相同的部分,在这里省略说明,以下对与第1例不同的部分进行说明。

141.存储器1的第5例与存储器1的第1例相比,不同点在于:在z轴方向上连接部233a与虚设单元区域a3重叠、焊盘部233b与存储单元区域a1重叠、绝缘分离体vz与虚设台阶区域a2重叠。其以外的部分是与图6所示的存储器1同样的构造,所以这里省略说明,以下对不同的部分进行说明。

142.插塞218设在存储柱mp与台阶部stp之间。插塞218在虚设单元区域a3中在z轴方向上贯通层叠体20。另外,通过在插塞218的侧面上形成绝缘体,由此能够与层叠体20电绝缘。插塞218在虚设单元区域a3中经由导电层219、导电层220、导电层222、导电层206、导电层205、导电层204、导电层203、导电层202及导电层201而与周边电路110电连接。

143.连接部233a设在基板210的基板部210a与绝缘分离体vz之间。连接部233a在虚设单元区域a3中设在插塞218上。由此,导电层233与插塞218电连接,经由插塞218、导电层219、导电层220、导电层222、导电层206、导电层205、导电层204、导电层203、导电层202及导电层201与周边电路110电连接。

144.焊盘部233b从连接部233a延伸到存储单元区域a1的上方。焊盘部233b从绝缘层

234、绝缘层235及绝缘层236露出。

145.绝缘分离体vz在z轴方向上与台阶部stp重叠。绝缘分离体vz在例如存储器1的第1例的制造方法例中通过将图12所示的开口h2以与台阶部stp重叠的方式形成、并在开口h2上形成绝缘层232来设置。

146.在存储器1的第5例中,具有在z轴方向上接合焊盘pd的焊盘部与存储单元阵列10的存储单元区域a1重叠的构造。由此,能够减小芯片面积。此外,在存储器1的第5例中,形成为使连接部233a与虚设单元区域a3重叠、使绝缘分离体vz不与虚设台阶区域a2重叠。通过绝缘分离体vz,即使在形成包括存储单元阵列10的多个区域r1的情况下,也能够将该多个区域r1相互电绝缘并且抑制基板210的裂纹。此外,在形成多个接合焊盘pd的情况下,通过省略用来将多个接合焊盘pd相互电绝缘的绝缘分离体,由此能够抑制与绝缘分离体vz的干涉。

147.另外,存储器1的第5例可以与存储器1的其他例适当组合。

148.(存储器1的第6例)

149.参照图27及图28对存储器1的第6例进行说明。图27是表示存储器1的第6例的芯片1b的一部分的俯视示意图,表示x-y平面。图28是用来说明存储器1的第6例的截面构造例的剖视示意图,图示沿着基板200的表面的x轴方向、沿着该表面与x轴大致垂直的y轴方向、以及与该表面大致垂直地交叉的z轴方向。另外,关于与第1例相同的部分,在这里省略说明,以下对与第1例不同的部分进行说明。

150.存储器1的第6例与存储器1的第1例相比,不同点在于:连接部233a与虚设单元区域a3重叠、焊盘部233b与存储单元区域a1重叠、绝缘分离体vz与虚设单元区域a3重叠。其以外的部分是与图6所示的存储器1同样的构造,所以这里省略说明,以下对不同的部分进行说明。

151.插塞218设在存储柱mp与台阶部stp之间。插塞218在虚设单元区域a3中将层叠体20在z轴方向上贯通。另外,通过在插塞218的侧面上形成绝缘体,能够与层叠体20电绝缘。插塞218在虚设单元区域a3中经由导电层219、导电层220、导电层222、导电层206、导电层205、导电层204、导电层203、导电层202及导电层201而与周边电路110电连接。

152.连接部233a设在基板210的基板部210a与绝缘分离体vz之间。连接部233a在虚设单元区域a3中设在插塞218上。由此,导电层233与插塞218电连接,经由插塞218、导电层219、导电层220、导电层222、导电层206、导电层205、导电层204、导电层203、导电层202及导电层201而与周边电路110电连接。

153.焊盘部233b从连接部233a延伸到存储单元区域a1的上方。焊盘部233b从绝缘层234、绝缘层235及绝缘层236露出。

154.绝缘分离体vz在虚设单元区域a3中与层叠体20重叠并与台阶部stp不重叠。绝缘分离体vz在虚设单元区域a3中不与虚设存储柱dmp重叠。绝缘分离体vz例如在存储器1的第1例的制造方法例中通过将图12所示的开口h2以与台阶部stp重叠的方式形成、并在开口h2上形成绝缘层232来设置。

155.在存储器1的第6例中,具有在z轴方向上接合焊盘pd的焊盘部与存储单元阵列10的存储单元区域a1重叠的构造。由此,能够减小芯片面积。此外,在存储器1的第6例中,形成为使连接部233a与虚设单元区域a3重叠、使绝缘分离体vz不与虚设单元区域a3重叠。通过

绝缘分离体vz,即使在形成包括存储单元阵列10的多个区域r1的情况下,也能够将该多个区域r1相互电绝缘并且抑制基板210的裂纹。此外,在形成多个接合焊盘pd的情况下,通过省略用来将多个接合焊盘pd相互电绝缘的绝缘分离体,能够抑制与绝缘分离体vz的干涉。

156.另外,存储器1的第6例可以与存储器1的其他例适当组合。

157.(存储器1的第7例)

158.参照图29及图30对存储器1的第7例进行说明。图29是表示存储器1的第7例的芯片1b的一部分的俯视示意图,表示x-y平面。图30是用来说明存储器1的第7例的截面构造例的剖视示意图,图示沿着基板200的表面的x轴方向、沿着该表面与x轴大致垂直的y轴方向、以及与该表面大致垂直地交叉的z轴方向。另外,关于与第6例相同的部分,在这里省略说明,以下对与第6例不同的部分进行说明。

159.存储器1的第7例与存储器1的第6例相比,不同点在于:在z轴方向上焊盘部233b与绝缘分离体vz重叠、与基板部210b重叠。其以外的部分是与图26所示的存储器1同样的构造,所以这里省略说明,以下对不同的部分进行说明。

160.焊盘部233b从连接部233a延伸到区域r2。焊盘部233b从绝缘层234、绝缘层235及绝缘层236露出。

161.绝缘分离体vz在z轴方向上在虚设单元区域a3中与层叠体20及焊盘部233b重叠。绝缘分离体vz在虚设单元区域a3中不与虚设存储柱dmp重叠。绝缘分离体vz例如在存储器1的第1例的制造方法例中通过将图12所示的开口h2以与台阶部stp重叠的方式形成、并在开口h2上形成绝缘层232来设置。

162.在存储器1的第7例中,具有在z轴方向上接合焊盘pd的焊盘部与存储单元阵列10的虚设台阶区域a2及虚设单元区域a3重叠的构造。由此,能够减小芯片面积。此外,在存储器1的第7例中,形成为使连接部233a与虚设单元区域a3重叠、使绝缘分离体vz不与虚设单元区域a3重叠。通过绝缘分离体vz,即使在形成包括存储单元阵列10的多个区域r1的情况下,也能够将该多个区域r1相互电绝缘并且抑制基板210的裂纹。此外,在形成多个接合焊盘pd的情况下,通过省略用来将多个接合焊盘pd相互电绝缘的绝缘分离体,能够抑制与绝缘分离体vz的干涉。

163.另外,存储器1的第7例可以与存储器1的其他例适当组合。

164.对本发明的几个实施方式进行了说明,但这些实施方式是作为例子而提示的,并不意图限定发明的范围。这些新的实施方式能够以其他各种方式实施,在不脱离发明的主旨的范围内,能够进行各种省略、置换、变更。这些实施方式及其变形包含在发明的范围或主旨中,并且包含在权利要求书所记载的发明及其等同的范围内。

165.附图标记说明

[0166]1…

存储器;1a

…

芯片;1b

…

芯片;2

…

存储器控制器;10

…

存储单元阵列;11

…

命令寄存器;12

…

地址寄存器;13

…

定序器;14

…

驱动器;15

…

行解码器;16

…

读出放大器;20

…

层叠体;110

…

周边电路;200

…

基板;201

…

导电层;202

…

导电层;203

…

导电层;204

…

导电层;205

…

导电层;206

…

导电层;207

…

绝缘层;210

…

基板;210a

…

基板部;210b

…

基板部;211

…

绝缘层;212

…

导电层;213

…

半导体层;215

…

存储器层;215a

…

块绝缘膜;215b

…

电荷贮存膜;215c

…

隧道绝缘膜;216

…

半导体层;217

…

芯绝缘层;218

…

插塞;219

…

导电层;220

…

导电层;221

…

导电层;222

…

导电层;223

…

绝缘层;231

…

绝缘层;232

…

绝缘层;233

…

导电层;233a

…

连接部;233b

…

焊盘部;234

…

绝缘层;235

…

绝缘层;236

…

绝缘层;241

…

抗蚀剂层;242

…

抗蚀剂层;a1

…

存储单元区域;a2

…

虚设台阶区域;a3

…

虚设单元区域;add

…

地址信号;ale

…

地址锁存使能信号;ba

…

块地址;bl

…

位线;blk

…

块;blk0

…

块;ca

…

列地址;cle

…

命令锁存使能信号;cmd

…

命令信号;dat

…

数据;dmp

…

虚设存储柱;h1

…

开口;h2

…

开口;i/o

…

信号;mp

…

存储柱;mt

…

存储晶体管;ns

…

nand串;pa

…

页地址;pd

…

接合焊盘;r1

…

区域;r2

…

区域;rbn

…

就绪繁忙信号;ren

…

读使能信号;sgd

…

选择栅极线;sgs

…

选择栅极线;sl

…

源极线;st1

…

选择晶体管;st2

…

选择晶体管;sti

…

元件分离体;stp

…

台阶部;su

…

串单元;tr1

…

场效应晶体管;tr2

…

场效应晶体管;vz

…

绝缘分离体;w1

…

晶片;w2

…

晶片;wen

…

写使能信号;wl

…

字线。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。