技术特征:

1.一种半导体存储装置,具备:第1基板;周边电路,设在上述第1基板上;层叠体,设在上述周边电路的上方,将多个第1导电层与多个第1绝缘层在第1方向上交替地层叠而成;第1柱,将上述层叠体内在上述第1方向上贯通,包括半导体层,在上述半导体层与上述多个第1导电层的交点处形成存储单元;第2基板,设在上述层叠体及上述第1柱的上方,具有与上述半导体层电连接的第1区域和配置在上述第1区域的与上述第1方向交叉的第2方向上的第2区域;第2绝缘层,将上述第2基板内在上述第1方向上贯通,在与上述第1方向及上述第2方向交叉的第3方向上延伸,将上述第1区域与上述第2区域电绝缘;以及第2导电层,具有在上述第1方向上贯通上述第2基板的第1部分、以及在上述第2基板的上方在上述第2方向上延伸并且包括作为接合焊盘的区域的第2部分,上述第2部分在上述第1方向上与上述第2绝缘层重叠。2.如权利要求1所述的半导体存储装置,其中,上述层叠体包括台阶部,该台阶部设在上述第2方向的端部并且以阶梯状配置有上述多个第1导电层及上述多个第2导电层的每一个;上述半导体存储装置还具备第2柱,该第2柱将上述层叠体内在上述第1方向上贯通,设在上述第1柱与上述台阶部之间,并与上述周边电路电绝缘。3.如权利要求2所述的半导体存储装置,其中,上述第2绝缘层在上述第1方向上不与上述层叠体重叠。4.如权利要求2所述的半导体存储装置,其中,上述第2绝缘层在上述第1方向上与上述台阶部重叠。5.如权利要求2所述的半导体存储装置,其中,还具备插塞,该插塞在上述第1方向上延伸,并将上述第1部分与上述周边电路电连接,上述第1部分在上述第1方向上与上述台阶部重叠。6.一种半导体存储装置,具备:第1基板;周边电路,设在上述第1基板上;层叠体,设在上述周边电路的上方,将多个第1导电层与多个第1绝缘层在第1方向上交替地层叠而成;第1柱,将上述层叠体内在上述第1方向上贯通,包括半导体层,在上述半导体层与多个第1导电层的交点处形成存储单元;第2基板,设在上述层叠体及上述第1柱的上方,具有与上述半导体层电连接的第1区域和配置在上述第1区域的与上述第1方向交叉的第2方向上的第2区域;第2绝缘层,将上述第2基板内在上述第1方向上贯通,在与上述第1方向及上述第2方向交叉的第3方向上延伸,将上述第1区域与上述第2区域电绝缘;以及第2导电层,具有在上述第1方向上贯通上述第2基板的第1部分、以及在上述第2基板的上方在上述第2方向上延伸并且包括作为接合焊盘的区域的第2部分,

上述第1部分被配置在上述第1区域与上述第2绝缘层之间。7.如权利要求6所述的半导体存储装置,其中,上述层叠体包括台阶部,该台阶部设在上述第2方向的端部并且以阶梯状配置有上述多个第1导电层及上述多个第2导电层的每一个;上述半导体存储装置还具备第2柱,该第2柱将上述层叠体内在上述第1方向上贯通,设在上述第1柱与上述台阶部之间,并与上述周边电路电绝缘。8.如权利要求7所述的半导体存储装置,其中,还具备插塞,该插塞在上述第1方向上延伸,并将上述第1部分与上述周边电路电连接,上述第1部分在上述第1方向上与上述台阶部重叠;上述第2绝缘层在上述第1方向上不与上述台阶部重叠。9.如权利要求7所述的半导体存储装置,其中,还具备插塞,该插塞在上述第1方向上延伸,并将上述第1部分与上述周边电路电连接,上述插塞设在上述第1柱与上述台阶部之间,上述第2绝缘层在上述第1方向上与上述台阶部重叠。10.如权利要求7所述的半导体存储装置,其中,还具备插塞,该插塞在上述第1方向上延伸,并将上述第1部分与上述周边电路电连接,上述插塞设在上述第1柱与上述台阶部之间,上述第2绝缘层在上述第1方向上与上述层叠体重叠,并且不与上述台阶部重叠。11.如权利要求7所述的半导体存储装置,其中,还具备插塞,该插塞在上述第1方向上延伸,并将上述第1部分与上述周边电路电连接,上述插塞设在上述第1柱与上述台阶部之间,上述第2部分在上述第1方向上与上述第2区域重叠。

技术总结

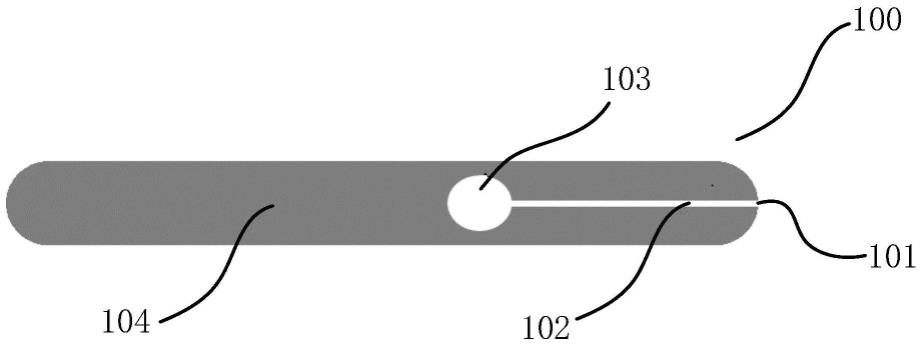

实施方式提供芯片面积较小的半导体存储装置,其具备:层叠体,设在第1基板上的周边电路的上方,将多个第1导电层和多个第1绝缘层在第1方向上交替地层叠而成;第1柱,在第1方向上贯通层叠体内,包括半导体层,在半导体层与多个第1导电层的交点处形成存储单元;第2基板,设在层叠体及第1柱的上方,具有与半导体层电连接的第1区域和配置在第1区域的第2方向上的第2区域;第2绝缘层,在第1方向上贯通第2基板内,在第3方向上延伸,将第1与第2区域电绝缘;及第2导电层,具有在第1方向上贯通第2基板的第1部分、及在第2基板的上方在第2方向上延伸并包括作为接合焊盘的区域的第2部分。第2部分在第1方向上与第2绝缘层重叠。在第1方向上与第2绝缘层重叠。在第1方向上与第2绝缘层重叠。

技术研发人员:和田秀雄

受保护的技术使用者:铠侠股份有限公司

技术研发日:2021.12.13

技术公布日:2022/8/29

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。