1.本发明是有关于一种存储器装置及其控制方法,且特别是有关于一种可作为存储器内运算器的存储器装置及其控制方法。

背景技术:

2.在人工智能日渐进步的今天,在集成电路中,提供具有高效率乘加运算能力的芯片,成为重要的课题。在现今的技术领中,通过设置存储器装置以执行乘加运算,成为一种主流。

3.在已知技术领域中,可针对存储器中所有的页数据进行数字的加总来产生运算结果。这种方式具有相对高的准确度,但需要相对长的运算时间。另外,已知技术领域也提供模拟方式以侦测源极在线的电流总和来获得运算结果。然而,这种方式虽可减少运算时间,但却无法提供高准确度的运算结果。

技术实现要素:

4.本发明提供一种存储器装置及其控制方法,可提升电流加总运算的准确度。

5.本发明的存储器装置包括存储单元阵列、电流侦测器以及控制器。存储单元阵列具有多个存储单元串。存储单元串耦接至共享源极线。电流侦测器在读取动作时侦测共享源极线或存储单元阵列的页缓冲器的电源端上的流通电流。控制器耦接存储单元串,用以:在编程动作中,针对对应逻辑0的多个第一存储单元以依据第一编程验证电压执行第一编程动作,并针对对应逻辑1的多个第二存储单元以依据第二编程验证电压执行第二编程动作,其中第一编程验证电压大于第二编程验证电压;以及,在读取动作时提供读取电压至存储单元串,基于读取电流参考值以感测流通电流。

6.本发明的存储器装置的控制方法包括:在读取动作时侦测共享源极线或存储单元阵列的页缓冲器的电源端上的流通电流,其中存储单元阵列具有多个存储单元串,存储单元串耦接至共享源极线;在编程动作中,针对对应逻辑0的多个第一存储单元以依据第一编程验证电压执行第一编程动作,并针对对应逻辑1的多个第二存储单元以依据第二编程验证电压执行第二编程动作,其中第一编程验证电压不同于第二编程验证电压;以及,在读取动作时提供读取电压至存储单元串,基于读取电流参考值以感测流通电流。

7.基于上述,使对应逻辑0以及逻辑1的存储单元分别执行不同程度的编程动作,以提升对应逻辑0以及逻辑1的存储单元的分布状态。如此一来,可提升感测到的存储单元阵列所提供的流通电流的准确度,进而提升运算结果的准确度。

附图说明

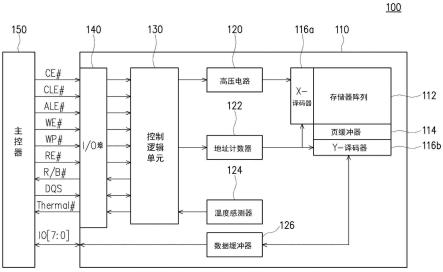

8.图1绘示本发明一实施例的存储器装置的示意图。

9.图2绘示本发明实施例的存储单元的编程动作的存储单元的阈值电压(threshold voltage)分布状态示意图。

10.图3绘示本发明实施例的存储器装置执行编程动作的动作流程图。

11.图4a以及图4b绘示本发明实施例的存储单元对应编程验证电压以及读取电压的电流-电压的关系图。

12.图5绘示本发明另一实施例的存储器装置的示意图。

13.图6a至图6d分别绘示本发明实施例的存储器装置中,电压调整器以及电流侦测器的实施方式的示意图。

14.图7a以及图7b绘示本发明实施例的存储器装置的不同实施架构的示意图。

15.【符号说明】

16.100、500、701、702:存储器装置

17.110、510、721-1、721-2:存储单元阵列

18.120、520、520-1~520-4、712、722-1、722-2:电流侦测器

19.130:控制器

20.140:页缓冲器

21.141:闩锁器

22.150:驱动器

23.210、220、221:分布状态

24.410:分布范围

25.550、550-1~550-4:电压调整器

26.710:存储单元阵列

27.bl1~bl4、mbl0~mbl2:位线

28.blsw1~blsw4:位线开关

29.csl、csl0、csl1:共享源极线

30.gnd:参考接地端

31.icell_1~icell_3:电流

32.ict:流通电流

33.idet:侦测信息

34.m1~m5:晶体管

35.midet:调整后侦测信息

36.ms1~ms4:存储单元串

37.op1、op2:放大器

38.pv_0、pv_1、pv1:编程验证电压

39.rd:读取电压

40.s310~s330:编程动作的步骤

41.vr1:参考电压

42.vr2、vb:偏压电压

43.vcsl:源极电压

44.w2、w1:宽度

45.wl:字线

具体实施方式

46.请参照图1,图1绘示本发明一实施例的存储器装置的示意图。存储器装置100包括存储单元阵列110、电流侦测器120、控制器130、页缓冲器140以及驱动器150。存储单元阵列110具有多个存储单元串ms1~ms4,其中存储单元串ms1~ms4可以为快闪存储单元串。存储单元串ms1~ms4可以二维方式进行排列。存储单元串ms1~ms4耦接至共享源极线csl。存储单元串ms1~ms4并通过字线wl耦接至驱动器150。驱动器150通过字线wl发送字线信号以控制存储单元串ms1~ms4上多个存储单元的存取动作。存储单元串ms1~ms4并分别耦接位线bl1~bl4。其中,页缓冲器140中具有闩锁器141以及多个位线开关blsw1~blsw4。位线开关blsw1~blsw4分别耦接至位线bl1~bl4,并受控于闩锁器141的多个输出。位线开关blsw1~blsw4依据其导通或断开状态,以分别传送多个输入信号至位线bl1~bl4。在本实施例中,存储器装置100可作为一存储器内运算器(in-memory computation device)。

47.在另一方面,电流侦测器120耦接至共享源极线csl,并用以在读取动作时侦测共享源极线csl上的流通电流。在本实施例中,存储单元串ms1~ms4可提供权重值,通过与所接收的输入信号执行乘加运算,并在共享源极线csl上产生运算结果。其中,电流侦测器120通过侦测共享源极线csl上的流通电流以获得上述的运算结果。其中,在读取动作中,存储单元串ms1~ms4上被读取的存储单元的字线可被施加读取电压(例如由控制器130提供),而电流侦测器120可以基于一预设的读取电流参考值以感测共享源极线csl上的流通电流。

48.值得一提的,电流侦测器120也可耦接至页缓冲器140的电源端,并通过侦测页缓冲器140的电源端上的电流,以获得上述的流通电流。如此,电流侦测器120同样可以获得存储器装置100所产生的运算结果。

49.值得注意的,控制器130耦接至存储单元串ms1~ms4。控制器130用以在针对存储单元串ms1~ms4中的存储单元执行编程动作中,可针对对应逻辑0的多个第一存储单元以依据第一编程验证电压执行第一编程动作,并针对对应逻辑1的多个第二存储单元以依据第二编程验证电压执行第二编程动作。其中,在本实施例中,第一编程验证电压不同于(例如大于)第二编程验证电压。在此请同步参照图1以及图2,其中图2绘示本发明实施例的存储单元的编程动作的存储单元的阈值电压(thresholdvoltage)分布状态示意图。在初始状态下,所有的存储单元为被擦除状态,并具有分布状态210。在执行存储单元的编程动作时,控制器130可先查找出所有存储单元中对应逻辑0的多个第一存储单元,并查找出所有存储单元中对应逻辑1的多个第二存储单元。接着,控制器130使对应逻辑0的多个第一存储单元,以依据第一编程验证电压pv_0执行第一编程动作。并且,控制器130并使对应逻辑1的多个第二存储单元,以依据第二编程验证电压pv_1执行第二编程动作。在第一编程动作以及第二编程动作完成后,对应逻辑0的第一存储单元具有分布状态220,对应逻辑1的第二存储单元则具有分布状态221。

50.在本实施例中,控制器130可以为具运算能力的处理器。或者,控制器130可以是通过硬件描述语言(hardware description language,hdl)或是其他任意本领域技术人员所熟知的数字电路的设计方式来进行设计,并通过现场可编程逻辑门阵列(fieldprogrammable gate array,fpga)、复杂可编程逻辑装置(complex programmable logic device,cpld)或是特殊应用集成电路(application-specific integrated circuit,asic)的方式来实现的硬件电路。

51.另一方面,电流侦测器120可依据读取电压rd以执行共同源极线csl上的流通电流的读取动作。

52.在此请注意,在本发明实施例中,不论是对应逻辑0的第一存储单元,或是对应逻辑1的第二存储单元,控制器130会依据不同的编程验证电压,施以不同程度的编程动作。如此一来,程化动作后,第一存储单元的分布状态220的宽度w1以及第二存储单元的分布状态221的宽度w2都可以被设定至一范围中。也就是说,存储单元串ms1~ms4上的各个存储单元所分别提供的电流大小可以有效的被集中,并使电流侦测器120可更为准确的读取流通电流。

53.以下请参照图3,图3绘示本发明实施例的存储器装置执行编程动作的动作流程图。在存储器装置执行编程动作时,在步骤s310中,控制器可进行写入数据的输入,并在步骤s320中,针对对应逻辑0的存储单元以及逻辑1的存储单元,执行不同程度的编程动作。步骤s330中,控制器可依据编程验证是否通过,以决定是否持续执行步骤s320。其中若步骤s330判断出编程验证未通过,则再次执行步骤s320;相对的,若步骤s330判断出编程验证已通过,则结束此次编程动作。

54.以下请参照图4a以及图4b,图4a以及图4b绘示本发明实施例的存储单元对应编程验证电压以及读取电压的电流-电压的关系图。在图4a、4b中,曲线的横轴为存储单元字符在线的偏压,曲线的纵轴则为存储单元产生的电流。在图4a中,对应逻辑1的存储单元中,当所提供的读取电压rd大于第二编程验证电压pv_1时,可以发现多个存储单元所提供的电流具有一个分布范围410,分布范围410可以例如介于80na(纳安培)-100na间。这个分布范围410会使得执行电流侦测动作时产生一定的误差。基于上述,本发明实施例中,可在针对对应逻辑1的存储单元执行编程电压中,使第二编程验证电压pv_1提高一个偏移值以获得偏移后的第二编程验证电压pv1,如图4b所述。其中偏移后的第二编程验证电压pv1不大于读取电压rd。

55.在图4b中,偏移后的第二编程验证电压pv1可与读取电压rd相等。且存储单元基于读取电压rd所产生的电流,可以例如集中于80na。进一步的,在读取动作中,电流侦测器可同步调高读取电流参考值一偏移值(例如由20na调高为80na)。如此一来,电流侦测器所执行的电流侦测动作的准确度可以进一步的被提升。

56.请参照图5,图5绘示本发明另一实施例的存储器装置的示意图。存储器装置500包括存储单元阵列510、电流侦测器520、电压调整器550以及多个感测放大器sa0~sa2。存储单元阵列510具有以三维方式进行排列的多个存储单元串ms1~ms3,存储单元串ms1~ms3的一端分别耦接至位线mbl0~mbl2;存储单元串ms1~ms3的另一端则共同耦接至共享源极线csl。另外,电流侦测器520以及电压调整器550均耦接至共享源极线csl。

57.在读取动作中,感测放大器sa0~sa2可分别提供多个偏压以施加在位线mbl0~mbl2上。同时,电压调整器550可提供另一偏压至共享源极线csl。此时,存储单元串ms1~ms3可分别对应产生电流icell_1~icell_3。电流icell_1~icell_3被提供至共享源极线csl以产生流通电流ict。电流侦测器520可针对流通电流ict进行侦测,并获得流通电流ict的电流大小。

58.在本实施例中,存储单元串ms1~ms3可以为与非门(nand)快闪存储单元串。

59.以下请参照图6a至图6d,图6a至图6d分别绘示本发明实施例的存储器装置中,电

压调整器以及电流侦测器的实施方式的示意图。以下以图5的实施例基础,在图6a中,电压调整器550-1以及电流侦测器520-1耦接至存储单元阵列510的共享源极线csl。电压调整器550-1包括放大器op1以及晶体管m1。放大器op1的正输入端耦接至共享源极线csl,放大器op1的负输入端接收参考电压vr1,放大器op1的输出端则耦接至晶体管m1的控制端。另外,晶体管m1的第一端耦接至共享源极线csl,晶体管m1的第二端耦接至参考接地端gnd。电压调整器550-1可依据参考电压vr1以产生源极电压vcsl,并将源极电压vcsl提供至共享源极线csl。在执行读取动作时,共享源极线csl上的流通电流ict流通晶体管m1。放大器op1并依据所正、负输入端上的源极电压vcsl以及参考电压vr1来在输出端产生一偏压电压vb,偏压电压vb可被提供至晶体管m1的控制端。

60.另外,电流侦测器520-1包括晶体管m2。晶体管m2的控制端接收偏压电压vb,晶体管m2的第二端耦接至参考接地端gnd。晶体管m2可镜射晶体管m1上的流通电流ict以在其第一端产生侦测信息idet。其中,在本实施方式中,通过使晶体管m2的通道宽长比为晶体管m1的通道宽长比的1/k倍,侦测信息idet上的电流值可以为流通电流ict的1/k倍。其中k为大于1的实数。

61.在图6b的实施方式中,电压调整器550-2以及电流侦测器520-2耦接至存储单元阵列510的共享源极线csl,并用以进行共享源极线csl上的流通电流ict的侦测动作。电压调整器550-2的电路架构与图6a实施方式中的电压调整器550-1的电路架构相同,这边不多赘述。关于电流侦测器520-2,于图6a不相同的,电流侦测器520-2另包括晶体管m3。其中晶体管m3的第二端耦接至晶体管m2的第一端,晶体管m3的控制端接收偏压电压vr2,且晶体管m3的第一端产生侦测信息idet。在本实施例中,侦测信息idet可以为一电流信号或一电压信号,没有特定的限制。

62.另外,在图6c的实施方式中,电压调整器550-3以及电流侦测器520-3耦接至存储单元阵列510的共享源极线csl,并用以进行共享源极线csl上的流通电流ict的侦测动作。电压调整器550-3的实施方式与电压调整器550-1的实施方式相同,以下不多赘述。在电流侦测器520-3方面,与电流侦测器520-2不相同的,本实施方式中的电流侦测器520-2另包括放大器op2,用以产生偏压电压vr2。其中,放大器op2的正输入端耦接至共同源极线csl,放大器op2的负输入端耦接至晶体管m3、m2的耦接端点上,放大器op2的输出端则产生偏压电压vr。

63.在图6d的实施方式中,电压调整器550-4以及电流侦测器520-4耦接至存储单元阵列510的共享源极线csl,并用以进行共享源极线csl上的流通电流ict的侦测动作。同样的,电压调整器550-4的实施方式与电压调整器550-1的实施方式相同,以下不多赘述。在电流侦测器520-4方面,与电流侦测器520-2不相同的,本实施方式中的电流侦测器520-4中另包括由晶体管m4、m5所构成的电流镜。电流镜用以镜射晶体管m3所提供的侦测信息idet,并产生调整后侦测信息midet。在本实施例中,调整后侦测信息midet可以为一电流信号或一电压信号,没有特定的限制。在本实施方式中,晶体管m4、m5所构成的电流镜的电流镜射比可以是1∶1,当调整后侦测信息midet为电流信号时,调整后侦测信息midet与流通电流ict的量值的比则可以是1∶k。

64.请参照图7a以及图7b,图7a以及图7b绘示本发明实施例的存储器装置的不同实施架构的示意图。在图7a中,存储器装置701中,存储单元阵列包括一存储器装置中的全部存

储单元阵列710。存储单元阵列710具有一共享源极线csl。电流侦测器712耦接至存储单元阵列710的共享源极线csl,并通过侦测共享源极线csl上的流通电流,以获得存储器装置701的乘加运算结果。

65.在图7b中,存储器装置702中,存储单元阵列721-1、721-2分别为一存储器装置中的两个部分存储单元阵列。存储单元阵列721-1、721-2分别具有共享源极线csl0、csll。电流侦测器722-1、722-2分别耦接至共享源极线csl0、csl1。电流侦测器722-1、722-2通过分别侦测共享源极线csl0、csl1上的流通电流来获得分别对应存储单元阵列721-1、721-2的乘加运算结果。

66.当然,上述实施例中,单一存储器装置可包括更多数量的存储单元阵列,图7a、7b的绘示仅只是说明用的范例,不用以限制本发明的保护范围。

67.本发明另一实施例提出一种存储器装置的控制方法。其中,在本实施例中,在一步骤中,存储器装置可在读取动作时侦测共享源极线或存储单元阵列的页缓冲器的电源端上的流通电流,其中,存储单元阵列具有多个存储单元串,存储单元串耦接至共享源极线。并在另一步骤中,存储器装置可在编程动作中,针对对应逻辑0的多个第一存储单元以依据第一编程验证电压执行第一编程动作,并针对对应逻辑1的多个第二存储单元以依据第二编程验证电压执行第二编程动作,其中第一编程验证电压不同于第二编程验证电压。另外,在另一步骤中,存储器装置可在读取动作时提供读取电压至存储单元串,基于读取电流参考值以感测流通电流。

68.关于上述动作的步骤的实施细节,在前述的实施例中已有详细的说明,在此不多赘述。

69.综上所述,本发明通过使对应逻辑0、1的存储单元分别执行不同程度的编程动作,以使对应逻辑0、1的存储单元的阈值电压的分布宽度可以限制在一定的预设数值下。如此一来,在执行存储单元的读取动作时,存储单元所提供的电流范围可以具有较高的均匀性,可提升读取动作的准确性。

70.至此,已经结合附图对本公开实施例进行了详细描述。

71.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。