基于sram阵列的多位同或运算的电路结构及方法

技术领域

1.本发明涉及静态随机存储器,特别是涉及基于sram阵列的多位同或运算的电路结构及方法。

背景技术:

2.现有技术可以在sram存内计算领域进行加法、减法以及乘法运算等,由于只能识别和卷积神经网络的需求,要输入量和权重值的乘累加,即为卷积神经网络的运算过程,应用于很多场合,但二进制的乘法在电路中一般在模拟域中实现,在位线上累积电压,通过adc将累加结果读出,线性度问题是一个巨大挑战,这就要求需要一个高精度的adc或者需要一个修正线性度的辅助电路,实现难度较大。因此急需一种高效、简洁,同时保证高精度的运算电路。

技术实现要素:

3.基于此,有必要针对在位线上累积电压,通过adc将累加结果读出导致电路复杂且精准度不够的问题,提供一种基于sram阵列的多位同或运算的电路结构及方法。

4.本发明采用以下技术方案实现:

5.基于sram阵列的多位同或运算的电路结构,其包括:

6.n

×

n个sram存储单元,呈阵列分布,所述sram存储单元包括三行sram单元,其中:

7.第一行8t-sram单元,晶体管t5和t6的栅极与字线wl电连接,节点q与晶体管t7的栅极电连接,节点qb与晶体管t8的栅极电连接;晶体管t7和t8的源极与计算字线cwl1电连接,晶体管t7的漏极电连接位线cbl,晶体管t8的漏极与位线cblb电连接,重置晶体管t9的源极和漏极分别连接位线cbl和cblb,重置晶体管t9的栅极电连接重置信号reset。

8.第二行8t-sram单元,晶体管t5和t6的栅极与字线wl电连接,节点q与晶体管t7的栅极电连接,节点qb与晶体管t8的栅极电连接;晶体管t7和t8的源极电连接与同或运算结果输出口节点out电连接,晶体管t7的漏极电连接第一行的位线cbl,晶体管t8的漏极电连接第一行的位线cblb;

9.第三行的7t-sram单元,晶体管t5和t6的栅极与字线wl电连接,晶体管t7的栅极与写字线wwl电连接,t7的源极与节点q电连接,t7的漏极与节点out电连接,晶体管t1和t3的源极与复写辅助单元电连接;

10.位于同一列的sram存储单元,所有的晶体管t5的源极与位线bl电连接,所有的晶体管t6的源极与位线blb电连接;

11.位于同一行的sram存储单元,所有的sram存储单元的第一行8t-sram单元和第二行8t-sram单元共用一个重置晶体管t9;所有的sram存储单元的第三行7t-sram单元共用一个复写辅助单元。

12.进一步的,所述复写辅助单元包括:

13.晶体管t8,t8的栅极电连接电源控制信号cd,t8的源极电连接vdd,t8的漏极电连

接t1的源极;

14.晶体管t9,t9的栅极电连接电源控制信号cs,t9的源极电连接vss,t9的漏极电连接t3的源极。

15.进一步的,位于同一行的sram存储单元,每行的所有sram单元共用字线wl,所有的第一行8t-sram单元共用计算字线cwl,所有的第三行7t-sram单元共用写字线wwl。

16.进一步的,所述sram单元包括nmos管t3~t6,pmos管t1~t2,t1~t4构成两个交叉耦合的反相器,一端电连接节点q,另一端电连接节点qb。

17.进一步的,所述基于sram阵列的多位同或运算的电路结构在运算过程中,预先开启重置信号reset,将位线cbl和cblb以及节点out置“0”,随后关闭重置信号reset,激活计算字线cwl。

18.在其中一个实施例中,假设所述sram存储单元内,第一行的8t-sram单元存储的数据是“1”,第二行的8t-sram单元存储的数据是“1”;

19.第一行的8t-sram单元的晶体管t7被激活,晶体管t8关闭,计算字线cwl通过晶体管t7向位线cbl放电,位线cbl电压提高,位线cblb保持为“0”;

20.第二行的8t-sram单元的晶体管t7导通,晶体管t8关闭,位线cbl通过晶体管t7向节点out放电;

21.节点out通过第一行以及第二行8t-sram单元的晶体管t7充电,输出结果为“1”。

22.在其中一个实施例中,假设所述sram存储单元内,第一行的8t-sram单元存储的数据是“1”,第二行的8t-sram单元存储的数据是“0”;

23.第一行的8t-sram单元的晶体管t7被激活,晶体管t8关闭,计算字线cwl通过晶体管t7向位线cbl放电,位线cbl电压提高,位线cblb保持为“0”;

24.第二行的8t-sram单元的晶体管t8导通,晶体管t7关闭,位线cbl不能向节点out放电,节点out的输出结果为“0”。

25.在其中一个实施例中,假设所述sram存储单元内,第一行的8t-sram单元存储的数据是“0”,第二行的8t-sram单元存储的数据是“0”;

26.第一行的8t-sram单元的晶体管t8被激活,晶体管t7关闭,计算字线cwl通过晶体管t8向位线cblb放电,位线cblb电压升高,位线cbl保持为“0”;

27.第二行的8t-sram单元的晶体管t8导通,晶体管t7关闭,位线cblb通过晶体管t8向节点out放电;

28.节点out通过第一行以及第二行8t-sram单元的晶体管t8充电,输出结果为“1”。

29.在其中一个实施例中,假设所述sram存储单元内,第一行的8t-sram单元存储的数据是“0”,第二行的8t-sram单元存储的数据是“1”;

30.第一行的8t-sram单元的晶体管t8将被激活,晶体管t7关闭,计算字线cwl通过晶体管t8向位线cblb放电,位线cblb电压升高,位线cbl保持为“0”;

31.第二行的8t-sram单元的晶体管t7导通,晶体管t8关闭,位线cblb不能向节点out放电,节点out的输出结果是“0”。

32.本发明还包括基于sram阵列的多位同或运算的电路结构的运算方法,所述基于sram阵列的多位同或运算的电路结构为如前述的基于sram阵列的多位同或运算的电路结构,其特征在于,所述运算方法包括以下步骤:

33.通过sram存储单元中的重置信号reset和计算字线cwl对位线cbl、cblb以及节点out进行置零操作;

34.计算位线cbl、cblb置零后,关闭重置信号reset,激活计算字线cwl,令第一行的8t-sram单元和第二行的8t-sram单元计算,计算结果暂存于节点out内;

35.调整写字线wwl时序,令电源控制信号cd为高电平、电源控制信号cs为低电平,对暂存在节点out内的计算结果进行复写,将复写的结果存储到第三行的7t-sram单元内。

36.本发明提供的技术方案,具有如下有益效果:

37.1、能够正确完成数字域多位同或运算,相对于模拟域的计算,数字域计算具有更高的准确度,并且不需要较为复杂的a/d电路,很大程度上减少电路的面积问题和电路的复杂性。

38.2、实现同或计算后,将结果存储到另一行的7t-sram单元内,不会破坏原有参与计算的存储数据。

39.3、电路参与计算的每行8t-sram单元都采用共用,实现计算时可以多位一起计算,极大提高电路的并行度。

附图说明

40.图1为本发明基于sram阵列的多位同或运算的电路结构的结构示意图;

41.图2为图1中sram存储单元第一行和第二行的sram单元结构示意图;

42.图3为图1中sram存储单元的结构示意图;

43.图4为图2中两行sram单元同或运算的电路时序波形示意图;

44.图5为图1计算过程的工作波形图。

具体实施方式

45.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步地详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

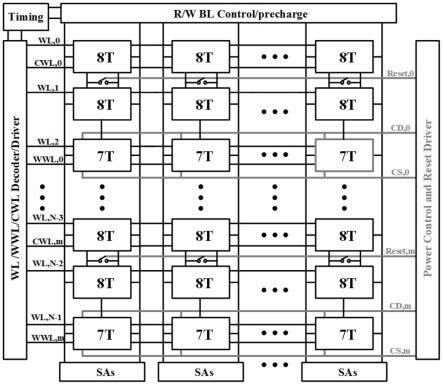

46.如图1所示,本实施例提供一种基于sram阵列的多位同或运算的电路结构,包括n

×

n个阵列分布的sram存储单元,m个重置信号组(resets)、m个计算字线组(cwls)、m个写字线(wwls)组和m个电源控制信号(cds和css)。另外,整个电路结构还需要由字线wl驱动。

47.如图2和图3所示,sram存储单元包括三行sram存储单元,其中:第一行8t-sram单元,晶体管t5和t6的栅极与字线wl电连接,节点q与晶体管t7的栅极电连接,节点qb与晶体管t8的栅极电连接;晶体管t7和t8的源极与计算字线cwl电连接,晶体管t7的漏极电连接位线cbl,晶体管t8的漏极与位线cblb电连接,重置晶体管t9的源极和漏极分别连接位线cbl和cblb,重置晶体管t9的栅极电连接重置信号reset。第二行8t-sram单元,晶体管t5和t6的栅极与字线wl电连接,节点q与晶体管t7的栅极电连接,节点qb与晶体管t8的栅极电连接;晶体管t7和t8的源极电连接与同或运算结果输出口节点out电连接,晶体管t7的漏极电连接第一行的位线cbl,晶体管t8的漏极电连接第一行的位线cblb;第三行的8t-sram单元,晶体管t5和t6的栅极与字线wl电连接,晶体管t7的栅极与写字线wwl电连接,t7的源极与节点q电连接,t7的漏极与节点out电连接,晶体管t1和t2的源极与复写辅助单元电连接,

48.位于同一列的sram存储单元,所有的晶体管t5的源极与位线bl电连接,所有的晶体管t6的源极与位线blb电连接。位于同一行的sram存储单元,所有的sram存储单元的第一行8t-sram单元和第二行8t-sram单元共用一个重置晶体管t9;所有的sram存储单元的第三行7t-sram单元共用一个复写辅助单元。

49.如图3所示,第一行包括6t-sram单元、晶体管t7和t8,组成8t-sram单元;第二行包括6t-sram单元、晶体管t7和t8,组成8t-sram单元;第三行包括6t-sram单元和晶体管t7,组成7t-sram单元。重置晶体管t9作为开关控制两条位线导通和断开,从而可以实现在计算前对计算位线cbl、cblb置“0”,为第一行和第二行的计算做好准备工作,另外还可以重置上一周期计算的残留电荷。两个参与运算的数据分别存储在第一行和第二行的q节点内。

50.t1-t6是传统的6t-sram单元,t1~t2为pmos管,t3~t6为nmos管,t1~t4构成两个交叉耦合的反相器,一端电连接节点q,另一端电连接节点qb,参与计算的两行为两行8t-sram单元的q节点,产生的结果是基于数字域的逻辑“1”和逻辑“0”。

51.如图3所示,在上述中同或运算的结果将会存在out节点,通过复写辅助单元将节点out结果写到第三行的7t-sram单元中。

52.复写的目标是sram存储单元中第一行和第二行进行同或运算的结果。复写的位置的sram存储单元中第三行7t-sram单元。晶体管t8和晶体管t9是复写行一行共用的,既复写过程是一行中所有列7t-sram单元一起完成的。

53.晶体管t7是复写传输管,晶体管t7通过写字线wwl控制,t7的源极电连接第三行7t-sram单元的q节点,t7的漏极连接上述两行运算的输出节点out。

54.通过调节写字线wwl的时序,可以将out节点的结果写入第三行7t-sram单元中。

55.由于6t-sram单元的特性,在不添加复写辅助单元的时候,单端写入是不能将数据写到6t-sram单元中的。这是由于6t-sram单元中存在反向耦合结构,q节点和qb节点将会互相保持,难以通过单端写入破坏其中的数据。

56.因此添加晶体管t8和晶体管t9,在写字线wwl开启的同时,激活晶体管t8和晶体管t9,也就是cd信号在这一个短的瞬间是高电平,cs信号在这一个短的瞬间是低电平。此时,6t-sram单元中的反向耦合结构将被破坏,单端写入就可以实现,晶体管t8的一端源极连接着vdd,另一端漏极连接着q节点一端反相器的vdd,因此通过晶体管t8可以控制6t-sram中一个反相器的电源电压vdd。

57.晶体管t9的一端源极连接着vss,另一端漏极连接着q节点一端反相器的vss,因此通过晶体管t8可以控制6t-sram单元中一个反相器的vss。

58.需要注意的是,cd信号和cs信号的开启需要要求一个很短的时间,在这短时间内要完成计算结果的复写过程。

59.在计算前需要调整控制信号的时序,让时序符合电路设计的理论要求,同时电路分析使用线负载模型,因此涉及到电压上及下降均是由于电容充电和放电导致。

60.如图4所示为本发明实施例进行两行同或运算的电路时序波形示意图,以一个sram存储单元为例,在运算过程中,重置信号reset需要在计算字线cwl信号前开启,将cbl和cblb以及节点out置“0”,在重置信号reset关闭之后,cwl才能激活,保证cbl和cblb以及out充分放电。

61.假设在重置完成,计算字线激活以后,第一行8t-sram单元中存储的数据是“1”,第

二行8t-sram单元中存储的数据是“1”,第一行中的晶体管t7将被激活,晶体管t8不会打开,计算字线通过t7向cbl放电,由于位线电容(电路的线负载电容,仿真时加一段加在cbl和cblb上,另一端接地),cbl电压升高,cblb保持为零,同时第二行8t-sram单元的q节点下的晶体管t7(和第一行的位置一样)将会导通,晶体管t8关闭,由于晶体管t7的漏极连接着cbl,此时cbl将会通过第二行的晶体管t7向节点out放电,由于电容的存在,节点out的将会通过两个导通的晶体管t7充电。逻辑上结果为“1”。

62.假设在重置完成,计算字线激活以后,第一行8t-sram单元中存储的数据是“1”,第二行8t-sram单元中存储的数据是“0”,第一行中的晶体管t7将被激活,晶体管t8不会打开,计算字线通过t7向cbl放电,由于位线电容,cbl电压升高,cblb保持为零,同时第二行8t-sram单元的q节点下的晶体管t8(和第一行的位置一样)将会导通,晶体管t7关闭,由于晶体管t7的漏极连接着cbl,晶体管t8的漏极连接着cblb。此时cbl上的逻辑电压为“1”,cblb上电压为“0”,即使第二行的晶体管t8导通,但是第二行的晶体管t7是闭合的,导致cbl的上电压并不能向节点out放电,因此节点out的电压依然是“0”。

63.假设在重置完成,计算字线激活以后,第一行8t-sram单元中存储的数据是“0”,第二行8t-sram单元中存储的数据是“0”,第一行中的晶体管t8将被激活,晶体管t7不会打开,计算字线通过t8向cblb放电,由于位线电容,cblb电压升高,cbl保持为零,同时第二行8t-sram单元的q节点下的晶体管t8(和第一行的位置一样)将会导通,晶体管t7关闭,由于晶体管t8漏极连接着cblb,此时cblb将会通过第二行的晶体管t8向out节点放电,由于电容的存在,out节点的将会通过两个导通的晶体管t8充电。逻辑上结果为“1”。

64.假设在重置完成,计算字线激活以后,第一8t-sram单元中存储的数据是“0”,第二行8t-sram单元中存储的数据是“1”,第一行中的晶体管t8将被激活,晶体管t7不会打开,计算字线通过t8向cblb放电,由于位线电容,cblb电压升高,cbl保持为零,同时第二行8t-sram单元的q节点下的晶体管t7(和第一行的位置一样)将会导通,晶体管t8关闭,由于晶体管t7的漏极连接着cbl,晶体管t8漏极连接着cblb。此时cblb线上的逻辑电压为“1”,cbl上电压为“0”,即使第二行的晶体管t7导通,但是第二行的晶体管t8是闭合的,导致cblb的上电压并不能向节点out放电,因此节点out的电压依然是“0”。

65.下表为本实施例同或计算的真值表,如表所示,q1和q1b代表第一行8t-sram单元内存储的数据。q2和q2b代表第二行8t-sram单元内存储的数据,q3和q3b代表第三行7t-sram单元内存储的数据。从真值表中可以看出,计算结果完成后,在第三行q节点存储的是前两行同或的结果,第三行qb节点存储的是前两行异或的结果。

66.同或计算真值表

67.68.如图5所示为本发明实施例在计算过程实际工作波形图,在计算字线开启激活期间,需要完成计算并写到sram单元内,图中表示电压的实际变化情况。前述提及,节点out的逻辑电压“1”,但不是电源电压vdd,比vdd低两个晶体管的阈值电压大小。但并不影响计算结果的正确性。节点out为逻辑电压“1”的电压变化是受计算字线cwl所控制的。且高电平并不能达到vdd的值。图中q3和q3b表示第三行sram单元中从原本存储的数据变成计算结果的过程。可以看出,由于计算结果和原本sram单元中存储的数据相异,sram单元中的数据就会被改写。

69.综上所述,通过sram存储单元能够正确完成多位同或运算,同时可以在不破坏原计算数据将同或的结果回存到第三行,同或结果通过一个传输管写进非参与计算的另一行,不破坏原有输出值。并且一行中的所有列是同时运算的,提高电路的并行度和吞吐量,电路结构实现简单,无复杂的外围电路。

70.在前述基于sram阵列的多位同或运算的电路结构的基础上,提供一种基于sram阵列的多位同或运算的电路结构的运算方法,包括以下步骤:

71.s1:通过sram存储单元中的重置信号reset和计算字线cwl对位线cbl、cblb以及节点进行置零操作;

72.s2:计算位线cbl、cblb置零后,关闭重置信号reset,激活计算字线cwl,令第一行的8t-sram单元和第二行的8t-sram单元计算,计算结果暂存于节点out内;

73.s3:调整写字线wwl时序,令电源控制信号cd为高电平、电源控制信号cs为低电平,对暂存在节点out内的计算结果进行复写,将复写的结果存储到第三行的7t-sram单元内。

74.以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

75.以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。