1.本发明涉及集成电路的形式验证领域,特别涉及一种集成电路形式验证方法、系统及存储介质。

背景技术:

2.在集成电路形式验证工具中,比较点匹配是非常重要的环节。通过比较点匹配,时序电路的等价性验证问题可以转换为组合电路的等价性验证问题,避免了复杂状态方程等的处理,同时,比较点匹配可以实现电路的划分,将更小的逻辑锥单元进行验证,可以更快地得到验证结果。

3.然而,在形式验证工具中,进行比较点匹配时会遇到各种各样的问题,其中,最典型的一个问题是参考设计中待匹配的比较点是一个dff,而实现设计中待匹配的比较点是两个主从结构的d-latch,对于两个功能等价的设计,按照常规一对一的比较点匹配,验证的结果肯定是不等价的,对于形式验证工具而言,验证的准确度也会降低,示意图如图1所示。

4.因此,解决待验证电路中dff与d-latch的比较点匹配问题,对于提高形式验证工具的准确性是非常必要的。

技术实现要素:

5.本发明的目的是针对现有技术的待验证电路中dff与d-latch的比较点匹配问题,本发明提出一种集成电路形式验证方法、系统及计算机存储介质。

6.本发明实施例中,提供了一种集成电路形式验证方法,其包括:

7.在实现设计中遍历两个主从结构的d-latch;

8.将实现设计中两个主从结构的d-latch转换为dff;

9.采用转换得到的dff与参考设计中的dff进行比较点匹配。

10.本发明实施例中,在实现设计中遍历两个主从结构的d-latch,包括:

11.在实现设计中依序搜索d-latch,并将搜索到的d-latch设为从latch;

12.判断从latch是否接入了有效的set信号或者reset信号,

13.是则不能作为从latch,继续搜索下一个d-latch;

14.否则获取从latch的d输入端的instance,判断其是否为d-latch、类型为主latch且其clock端输入信号与从latch的clock端输入信号相反,若是,则两个相邻的d-latch为两个主从结构的d-latch,否则两个相邻的d-latch不是两个主从结构的d-latch。

15.本发明实施例中,通过从latch的set/reset端是否为接入高电平来判断从latch是否接入了有效的set/reset信号,是则接入了有效的set/reset信号,否则没有接入。

16.本发明实施例中,将实现设计中两个主从结构的d-latch转换为dff,包括:

17.将所述两个主从结构的d-latch从网表中移除,并采用一个新的dff来替换所述两个主从结构的d-latch,其中,所述新的dff的输入端替换所述主latch的输入端,所述新的

dff的输出端替换所述从latch的输出端。

18.本发明实施例中,还提供了一种集成电路形式验证系统,其对dff与d-latch进行匹配验证时,采用上述的集成电路形式验证方法。

19.本发明实施例中,还提供了一种计算机存储介质,其存储有计算机程序,当所述计算机程序被执行时,实现上述的集成电路形式验证方法。

20.与现有技术相比较,采用本发明的集成电路形式验证方法,先将实现设计中两个主从结构的d-latch转换为dff,然后在采用转换得到的dff与参考设计中的dff进行比较点匹配,从而防止出现d-latch与dff不匹配的问题,可以显著提高形式验证的准确性。

附图说明

21.图1是参考设计与实现设计中dff与主从d-latch示意图。

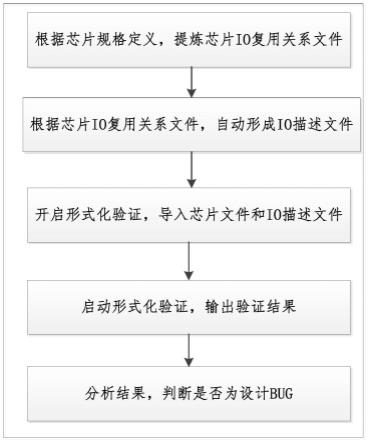

22.图2是本发明实施例的集成电路形式验证方法的流程图。

23.图3是本发明实施例的参考设计与实现设计中dff与主从d-latch匹配示意图。

具体实施方式

24.如图2所示,本发明实施例中,提供了一种集成电路形式验证方法,其包括步骤s1-s3。下面分别进行说明。

25.步骤s1:在实现设计中遍历两个主从结构的d-latch。

26.需要说明的是,在采用形式验证工具进行比较点匹配时,如果遇到匹配失败的情况,形式验证工具会反馈出不匹配的比较点。如果是dff与d-latch不匹配的情况,则需要找出不匹配的d-latch,并对其进行转换。当然,为了避免这种情况的发生,也可以在进行比较验证前,主动找出两个主从结构的d-latch,并将其转换为dff。

27.具体的,本发明实施例中,在实现设计中遍历两个主从结构的d-latch,包括:

28.在实现设计中依序搜索d-latch,并将搜索到的d-latch设为从latch;

29.判断从latch是否接入了有效的set信号或者reset信号;

30.是则不能作为从latch,继续搜索下一个d-latch;

31.否则获取从latch的d输入端的instance(实例),判断其是否为d-latch、类型为主latch(prim_dlatchrs)且其clock端输入信号与从latch的clock端输入信号相反,若是,则两个相邻的d-latch为两个主从结构的d-latch,否则两个相邻的d-latch不是两个主从结构的d-latch。

32.需要说明的是,从latch是与主latch的信号同步传输的,不能通过set/reset信号再控制自己的传输,因此,从latch不能接入set/reset有效信号。在一般情况下,d-latch是带有set/reset端进行复位和置位的,判断是否接入有效set/reset信号,就是看这两个端口有没有接入高电平,如果接入高电平,则接入了有效的set/reset信号,否则没有接入。如图3所示,本发明实施例中的从latch的set端没有接入高电平,因此没有接入有效set/reset信号。

33.还需要说明的是,对于两个主从结构的d-latch来说,从latch的d输入端的instance必须是d-latch,并且两个d-latch的clock端输入信号是相反的,如果不满足这些条件,则说明相连的两个d-latch并不是主从结构的d-latch。

34.步骤s2:将实现设计中两个主从结构的d-latch转换为dff。

35.具体的,如图3所示,将实现设计中两个主从结构的d-latch转换为dff,包括:

36.将所述两个主从结构的d-latch从网表(netlist)中移除,并采用一个新的dff来替换所述两个主从结构的d-latch,其中,所述新的dff的输入端替换所述主latch的输入端,所述新的dff的输出端替换所述从latch的输出端。

37.步骤s3:采用转换得到的dff与参考设计中的dff进行比较点匹配。

38.经过步骤s2将实现设计中两个主从结构的d-latch转换为dff后,就可以进入步骤s3,将转换后的dff直接与参考设计中的dff进行比较点匹配,从而防止出现d-latch与dff不匹配的问题。

39.本发明实施例中,还提供了一种集成电路形式验证系统,其对dff与d-latch进行匹配验证时,采用上述的集成电路形式验证方法。

40.本发明实施例中,还提供了一种计算机存储介质,其存储有计算机程序,当所述计算机程序被执行时,实现上述的集成电路形式验证方法。作为一个具体的实施例。

41.综上所述,采用本发明的集成电路形式验证方法,先将实现设计中两个主从结构的d-latch转换为dff,然后在采用转换得到的dff与参考设计中的dff进行比较点匹配,从而防止出现d-latch与dff不匹配的问题,可以显著提高形式验证的准确性。

42.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。