技术特征:

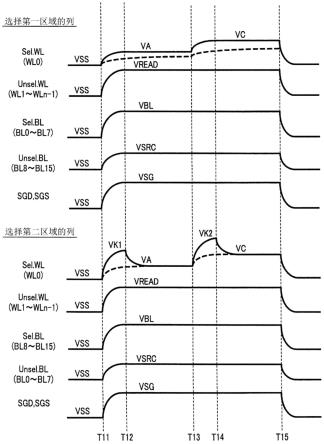

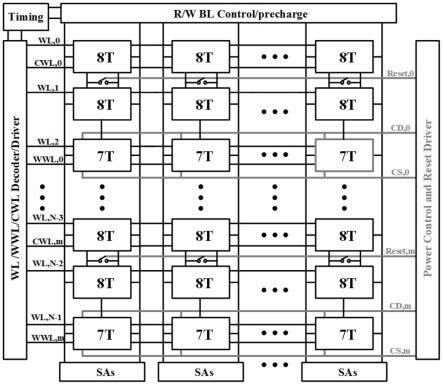

1.一种半导体存储装置,其特征在于包括:第一存储单元,电连接在第一位线及第一字线;第二存储单元,电连接在第二位线及所述第一字线;以及第一电路,构成为对所述第一字线供给电压;其中在读出包含所述第一存储单元及所述第二存储单元的存储单元的页面的读出动作中,当在第一时间段期间将所述第一存储单元选为读出目标时,所述第一电路:对所述第一字线供给第一电压,在供给所述第一电压之后对所述第一字线供给比所述第一电压小的第二电压,以及在供给所述第二电压之后对所述第一字线供给比所述第二电压大的第三电压;且在读出包含所述第一存储单元及所述第二存储单元的存储单元的所述页面的所述读出动作中,当在与所述第一时间段不同的第二时间段期间将所述第二存储单元选为所述读出目标时,所述第一电路:对所述第一字线供给所述第一电压,在供给所述第一电压之后对所述第一字线供给比所述第二电压小的第四电压,在供给所述第四电压之后对所述第一字线供给所述第二电压,以及在供给所述第二电压之后对所述第一字线供给比所述第三电压大的第五电压。2.根据权利要求1所述的半导体存储装置,其特征在于:所述第一电压、所述第四电压及所述第五电压不是读出电压,且所述第二电压及所述第三电压是读出电压。3.根据权利要求1所述的半导体存储装置,其特征在于:从所述第一电路至所述第一存储单元为止的距离,比从所述第一电路至所述第二存储单元为止的距离近。4.根据权利要求1所述的半导体存储装置,其特征在于:在读出所述存储单元的所述页面的所述读出动作中,当在所述第二时间段期间将所述第二存储单元选为所述读出目标时,所述第一电路在供给所述第四电压之后立即对所述第一字线供给所述第二电压。5.根据权利要求4所述的半导体存储装置,其特征在于:在读出所述存储单元的所述页面的所述读出动作中,当在所述第二时间段期间将所述第二存储单元选为所述读出目标时,所述第一电路在供给所述第五电压之后立即对所述第一字线供给所述第三电压。6.根据权利要求5所述的半导体存储装置,其特征在于:在读出所述存储单元的所述页面的所述读出动作中,当在所述第一时间段期间将所述第一存储单元选为所述读出目标时,所述第一电路:在供给所述第一电压之后立即对所述第一字线供给所述第二电压,以及在供给所述第二电压之后立即对所述第一字线供给所述第三电压;且在读出所述存储单元的所述页面的所述读出动作中,当在所述第二时间段期间将所述第二存储单元选为所述读出目标时,所述第一电路:在供给所述第一电压之后立即对所述第一字线供给所述第四电压,以及在供给所述第二电压之后立即对所述第一字线供给所述第五电压。

7.根据权利要求1所述的半导体存储装置,其特征在于还包括:第三存储单元,电连接在第三位线及所述第一字线,所述第三位线位于所述第一位线与所述第二位线之间;以及第四存储单元,电连接在第四位线及所述第一字线,所述第二位线位于所述第三位线与所述第四位线之间;其中在读出所述存储单元的所述页面的所述读出动作中,当在所述第一时间段期间将所述第一存储单元选为所述读出目标时,所述第一电路:对所述第一位线供给第六电压,以及对所述第三位线、所述第二位线及所述第四位线供给第七电压;且在读出所述存储单元的所述页面的所述读出动作中,当在所述第二时间段期间将所述第二存储单元选为所述读出目标时,所述第一电路:对所述第二位线供给所述第六电压,以及对所述第一位线、所述第三位线及所述第四位线供给所述第七电压。8.根据权利要求1所述的半导体存储装置,其特征在于:所述第一位线与所述第二位线相邻。9.根据权利要求1所述的半导体存储装置,其特征在于:所述第一存储单元沿所述第一字线位于所述第一电路与所述第二存储单元之间。10.一种半导体存储装置,其特征在于包括:第一存储单元,电连接在第一位线及第一字线;第二存储单元,电连接在第二位线及所述第一字线;以及第一电路,构成为对所述第一字线供给电压,其中在读出包含所述第一存储单元及所述第二存储单元的存储单元的页面的读出动作中,当在第一时间段期间将所述第一存储单元选为读出目标时,所述第一电路:对所述第一字线供给第一电压,在供给所述第一电压之后对所述第一字线供给比所述第一电压小的第二电压,以及在供给所述第二电压之后立即对所述第一字线供给比所述第二电压小的第三电压;且在读出包含所述第一存储单元及所述第二存储单元的存储单元的所述页面的所述读出动作中,当在与所述第一时间段不同的第二时间段期间将所述第二存储单元选为所述读出目标时,所述第一电路:对所述第一字线供给所述第一电压,在供给所述第一电压之后对所述第一字线供给比所述第二电压小的第四电压,在供给所述第四电压之后对所述第一字线供给所述第二电压,以及在供给所述第二电压之后对所述第一字线供给比所述第三电压小的第五电压。11.根据权利要求10所述的半导体存储装置,其特征在于:所述第一电压、所述第四电压及所述第五电压不是读出电压,且所述第二电压及所述第三电压是读出电压。12.根据权利要求10所述的半导体存储装置,其特征在于:从所述第一电路至所述第一存储单元为止的距离,比从所述第一电路至所述第二存储单元为止的距离近。

13.根据权利要求10所述的半导体存储装置,其特征在于:在读出所述存储单元的所述页面的所述读出动作中,当在所述第二时间段期间将所述第二存储单元选为所述读出目标时,所述第一电路在供给所述第四电压之后立即对所述第一字线供给所述第二电压。14.根据权利要求13所述的半导体存储装置,其特征在于:在读出所述存储单元的所述页面的所述读出动作中,当在所述第二时间段期间将所述第二存储单元选为所述读出目标时,所述第一电路在供给所述第五电压之后立即对所述第一字线供给所述第三电压。15.根据权利要求14所述的半导体存储装置,其特征在于:在读出所述存储单元的所述页面的所述读出动作中,当在所述第一时间段期间将所述第一存储单元选为所述读出目标时,所述第一电路:在供给所述第一电压之后立即对所述第一字线供给所述第二电压,以及在供给所述第二电压之后立即对所述第一字线供给所述第三电压;且在读出所述存储单元的所述页面的所述读出动作中,当在所述第二时间段期间将所述第二存储单元选为所述读出目标时,所述第一电路:在供给所述第一电压之后立即对所述第一字线供给所述第四电压,以及在供给所述第二电压之后立即对所述第一字线供给所述第五电压。16.根据权利要求10所述的半导体存储装置,其特征在于还包括:第三存储单元,电连接在第三位线及所述第一字线,所述第三位线位于所述第一位线与所述第二位线之间;以及第四存储单元,电连接在第四位线及所述第一字线,所述第二位线位于所述第三位线与所述第四位线之间;其中在读出所述存储单元的所述页面的所述读出动作中,当在所述第一时间段期间将所述第一存储单元选为所述读出目标时,所述第一电路:对所述第一位线供给第六电压,以及对所述第三位线、所述第二位线及所述第四位线供给第七电压;且在读出所述存储单元的所述页面的所述读出动作中,当在所述第二时间段期间将所述第二存储单元选为所述读出目标时,所述第一电路:对所述第二位线供给所述第六电压,以及对所述第一位线、所述第三位线及所述第四位线供给所述第七电压。17.根据权利要求10所述的半导体存储装置,其特征在于:所述第一位线与所述第二位线相邻。18.根据权利要求10所述的半导体存储装置,其特征在于:所述第一存储单元沿所述第一字线位于所述第一电路与所述第二存储单元之间。19.一种半导体存储装置,其特征在于包括:第一存储单元,电连接在第一字线及第一位线;第二存储单元,电连接在所述第一字线及第二位线;第三存储单元,电连接在所述第一字线及与所述第一位线相邻的第三位线;第四存储单元,电连接在所述第一字线及与所述第二位线相邻的第四位线;以及

第一电路,构成为:在读出动作中在将所述第一存储单元选为读出目标的情况下,对所述第一字线供给第一电压,在读出动作中在将所述第二存储单元选为读出目标的情况下,对所述第一字线供给比所述第一电压大的第二电压,且接着在之后立即对所述第一字线供给所述第一电压,在读出动作中在将所述第三存储单元选为读出目标的情况下,对所述第一字线供给所述第一电压,在读出动作中在将所述第四存储单元选为读出目标的情况下,对所述第一字线供给所述第二电压,且接着在之后立即对所述第一字线供给所述第一电压;其中在所述读出动作中,所述第一电路:在将所述第一存储单元选为所述读出目标的情况下,在对所述第一字线供给所述第一电压之后立即对所述第一字线供给比所述第一电压大的第五电压,以及在将所述第二存储单元选为所述读出目标的情况下,在对所述第一字线供给所述第一电压之后立即对所述第一字线供给比所述第二电压大的第六电压。20.根据权利要求19所述的半导体存储装置,其特征在于:所述第二电压及所述第六电压不是读出电压,所述第一电压及所述第五电压是读出电压。21.根据权利要求19所述的半导体存储装置,其特征在于:从所述第一电路至所述第一存储单元为止的距离,比从所述第一电路至所述第二存储单元为止的距离近。22.根据权利要求19所述的半导体存储装置,其特征在于:在所述读出动作中,在将所述第一存储单元选为所述读出目标的情况下,所述第一电路对所述第一位线供给第三电压且对所述第二位线、所述第三位线及所述第四位线供给比所述第三电压小的第四电压。23.根据权利要求22所述的半导体存储装置,其特征在于:在所述读出动作中,在将所述第二存储单元选为所述读出目标的情况下,所述第一电路对所述第二位线供给所述第三电压且对所述第一位线、所述第三位线及所述第四位线供给所述第四电压。24.根据权利要求19所述的半导体存储装置,其特征在于:所述第一电压是读出电压。25.根据权利要求19所述的半导体存储装置,其特征在于:所述第一电压是处于第一电压电平的读出电压,且所述第五电压是处于比所述第一电压电平高的第二电压电平的读出电压。26.根据权利要求19所述的半导体存储装置,其特征在于:响应于包含用来设定读出单位大小的第一指令的指令序列而执行读出动作。27.一种半导体存储装置,其特征在于包括:第一存储单元,电连接在第一字线及第一位线;第二存储单元,电连接在所述第一字线及第二位线;第三存储单元,电连接在所述第一字线及与所述第一位线相邻的第三位线;

第四存储单元,电连接在所述第一字线及与所述第二位线相邻的第四位线;以及第一电路,构成为:在读出动作中在将所述第一存储单元选为读出目标的情况下,对所述第一字线供给第一电压,在读出动作中在将所述第二存储单元选为读出目标的情况下,对所述第一字线供给比所述第一电压大的第二电压,且接着在之后立即对所述第一字线供给所述第一电压,在读出动作中在将所述第三存储单元选为读出目标的情况下,对所述第一字线供给所述第一电压,在读出动作中在将所述第四存储单元选为读出目标的情况下,对所述第一字线供给所述第二电压,且接着在之后立即对所述第一字线供给所述第一电压;其中响应于包含用来设定读出单位大小的第一指令及用来指定平面及读出区域的第一地址的第一指令序列而执行读出动作。28.根据权利要求27所述的半导体存储装置,其特征在于:所述第二电压不是读出电压,且所述第一电压是读出电压。29.根据权利要求27所述的半导体存储装置,其特征在于:所述读出单位大小是平面中的存储单元阵列的所有位线的四分之一。30.根据权利要求27所述的半导体存储装置,其特征在于:所述第一指令序列还包含请求第二地址的输入的第二指令,所述第二地址指定用来读出数据的地址。31.根据权利要求30所述的半导体存储装置,其特征在于:所述第二地址包含所述第一存储单元、所述第二存储单元、所述第三存储单元及所述第四存储单元中的一个。32.根据权利要求30所述的半导体存储装置,其特征在于:所述第一指令序列还包含用来请求所述读出动作的执行的第三指令。33.根据权利要求30所述的半导体存储装置,其特征在于:所述第二地址包含两个读出区域的一个中的所述位线的一半,所述两个读出区域位于所述平面中的存储单元阵列中。34.根据权利要求30所述的半导体存储装置,其特征在于:所述第二地址包含三个或更多个读出区域的一个中的所述位线的一半,所述三个或更多个读出区域位于所述平面中的存储单元阵列中。35.一种半导体存储装置,其特征在于包括:第一存储单元,电连接在第一字线及第一位线;第二存储单元,电连接在所述第一字线及第二位线;第三存储单元,电连接在所述第一字线及与所述第一位线相邻的第三位线;第四存储单元,电连接在所述第一字线及与所述第二位线相邻的第四位线;以及第一电路,构成为:在读出动作中在将所述第一存储单元选为读出目标的情况下,对所述第一字线供给第一电压,在读出动作中在将所述第二存储单元选为读出目标的情况下,对所述第一字线供给比

所述第一电压大的第二电压,且接着在之后立即对所述第一字线供给所述第一电压,在读出动作中在将所述第三存储单元选为读出目标的情况下,对所述第一字线供给所述第一电压,在读出动作中在将所述第四存储单元选为读出目标的情况下,对所述第一字线供给所述第二电压,且接着在之后立即对所述第一字线供给所述第一电压;其中所述半导体存储装置响应于包含用来变更所述半导体存储装置的参数的第四指令的第二指令序列而开始设置特征动作。36.根据权利要求35所述的半导体存储装置,其特征在于:所述第二电压不是读出电压,且所述第一电压是读出电压。37.根据权利要求35所述的半导体存储装置,其特征在于:所述第二指令序列还包含用来指定与欲变更的读出动作参数对应的地址的第三地址。38.根据权利要求37所述的半导体存储装置,其特征在于:所述第二指令序列还包含用于所述欲变更的读出动作参数的值。39.根据权利要求38所述的半导体存储装置,其特征在于:所述读出动作参数是读出单位大小。40.根据权利要求39所述的半导体存储装置,其特征在于:所述读出单位大小是所述平面中的存储单元阵列的所有位线的四分之一。41.根据权利要求35所述的半导体存储装置,其特征在于:在所述设置特征动作结束之后,响应于包含请求第二地址的输入的第二指令的第三指令序列而开始所述读出动作,所述第二地址用来指定用来读出数据的地址。42.根据权利要求41所述的半导体存储装置,其特征在于:所述第二地址包含所述第一存储单元、所述第二存储单元、所述第三存储单元及所述第四存储单元中的一个。43.根据权利要求41所述的半导体存储装置,其特征在于:所述第二地址包含两个读出区域的一个中的所述位线的一半,所述两个读出区域位于平面中的存储单元阵列中。44.根据权利要求41所述的半导体存储装置,其特征在于:所述第二地址包含三个或更多个读出区域的一个中的所述位线的一半,所述三个或更多个读出区域位于平面中的存储单元阵列中。45.一种半导体存储装置,其特征在于包括:第一存储单元,电连接在第一位线及第一字线;第二存储单元,电连接在第二位线及所述第一字线;以及第一电路,构成为对所述第一字线供给电压;其中在读出包含所述第一存储单元及所述第二存储单元的存储单元的页面的读出动作中,当在第一时间段期间将所述第一存储单元选为读出目标时,所述第一电路:对所述第一字线供给第一电压,在供给所述第一电压之后对所述第一字线供给比所述第一电压大的第二电压,在供给所述第二电压之后立即对所述第一字线供给比所述第二电压小的第三电压;且在读出包含所述第一存储单元及所述第二存储单元的存储单元的所述页面的所述读

出动作中,当在与所述第一时间段不同的第二时间段期间将所述第二存储单元选为所述读出目标时,所述第一电路:对所述第一字线供给所述第一电压,在供给所述第一电压之后对所述第一字线供给所述第二电压,在供给所述第二电压之后立即对所述第一字线供给比所述第三电压小的第四电压,以及在供给所述第四电压之后立即对所述第一字线供给所述第三电压。46.根据权利要求45所述的半导体存储装置,其特征在于:所述第一电压、所述第二电压及所述第四电压不是读出电压,且所述第三电压是读出电压。47.根据权利要求45所述的半导体存储装置,其特征在于:从所述第一电路至所述第一存储单元为止的距离,比从所述第一电路至所述第二存储单元为止的距离近。48.根据权利要求45所述的半导体存储装置,其特征在于:在读出所述存储单元的所述页面的所述读出动作中,当在所述第一时间段期间将所述第一存储单元选为所述读出目标时,所述第一电路在供给所述第三电压之后立即对所述第一字线供给比所述第三电压小的第五电压。49.根据权利要求48所述的半导体存储装置,其特征在于:在读出所述存储单元的所述页面的所述读出动作中,当在所述第二时间段期间将所述第二存储单元选为所述读出目标时,所述第一电路:在供给所述第三电压之后立即对所述第一字线供给比所述第五电压小的第六电压,以及在供给所述第六电压之后立即对所述第一字线供给所述第五电压。50.根据权利要求49所述的半导体存储装置,其特征在于:所述第六电压不是读出电压,且所述第五电压是读出电压。51.根据权利要求48所述的半导体存储装置,其特征在于:所述第三电压是处于第一电压电平的读出电压,且所述第五电压是处于比所述第一电压电平低的第二电压电平的读出电压。52.根据权利要求45所述的半导体存储装置,其特征在于还包括:第三存储单元,电连接在第三位线及所述第一字线,所述第三位线位于所述第一位线与所述第二位线之间;以及第四存储单元,电连接在第四位线及所述第一字线,所述第二位线位于所述第三位线与所述第四位线之间;其中在读出所述存储单元的所述页面的所述读出动作中,当在所述第一时间段期间将所述第一存储单元选为所述读出目标时,所述第一电路:对所述第一位线供给第七电压,以及对所述第二位线、所述第三位线及所述第四位线供给第八电压;且在读出所述存储单元的所述页面的所述读出动作中,当在所述第二时间段期间将所述

第二存储单元选为所述读出目标时,所述第一电路:对所述第二位线供给所述第七电压,以及对所述第一位线、所述第三位线及所述第四位线供给所述第八电压。53.根据权利要求52所述的半导体存储装置,其特征在于:所述第一位线与所述第三位线彼此相邻。54.根据权利要求52所述的半导体存储装置,其特征在于:所述第二位线与所述第四位线彼此相邻。55.根据权利要求45所述的半导体存储装置,其特征在于:沿所述第一字线,所述第一存储单元位于所述第一电路与所述第二存储单元之间。56.根据权利要求45所述的半导体存储装置,其特征在于还包括:第三存储单元,电连接在第三位线及所述第一字线,所述第三位线与所述第一位线相邻;以及第四存储单元,电连接在第四位线及所述第一字线,所述第四位线与所述第二位线相邻;其中在读出包含所述第三存储单元及所述第四存储单元的所述存储单元的所述页面的所述读出动作中,当在与所述第一及所述第二时间段不同的第三时间段期间将所述第三存储单元选为所述读出目标时,所述第一电路:对所述第一字线供给所述第一电压,在供给所述第一电压之后对所述第一字线供给所述第二电压,在供给所述第二电压之后立即对所述第一字线供给所述第三电压;且在读出包含所述第三存储单元及所述第四存储单元的存储单元的所述页面的所述读出动作中,当在与所述第一、所述第二及所述第三时间段不同的第四时间段期间将所述第四存储单元选为所述读出目标时,所述第一电路:对所述第一字线供给所述第一电压,在供给所述第一电压之后对所述第一字线供给所述第二电压,在供给所述第二电压之后立即对所述第一字线供给所述第四电压,以及在供给所述第四电压之后立即对所述第一字线供给所述第三电压。57.根据权利要求56所述的半导体存储装置,其特征在于:从所述第一电路至所述第一存储单元为止的距离,比从所述第一电路至所述第二存储单元为止的距离近。58.根据权利要求45所述的半导体存储装置,其特征在于:响应于包含用来设定读出单位大小的第一指令的指令序列而执行读出动作。59.根据权利要求45所述的半导体存储装置,其特征在于:响应于包含用来设定读出单位大小的第一指令及指定平面及读出区域的第一地址的指令序列而执行读出动作。60.根据权利要求59所述的半导体存储装置,其特征在于:所述读出单位大小是平面中的存储单元阵列的所有位线的四分之一。61.根据权利要求45所述的半导体存储装置,其特征在于:所述半导体存储装置响应于包含用来变更所述半导体存储装置的参数的指令的指令

序列而开始设置特征动作。62.根据权利要求61所述的半导体存储装置,其特征在于:所述指令序列还包含指定与欲变更的读出动作参数对应的地址的地址及用于所述欲变更的读出动作参数的值,且所述读出动作参数是读出单位大小。63.根据权利要求62所述的半导体存储装置,其特征在于:所述读出单位大小是所述平面中的存储单元阵列的所有位线的四分之一。64.根据权利要求61所述的半导体存储装置,其特征在于:在所述设置特征动作结束之后,响应于包含请求第二地址的输入的指令的另一指令序列而开始所述读出动作,所述第二地址指定用来读出数据的地址。

技术总结

本发明的实施方式提供一种意在缩短读出时间的半导体存储装置。半导体存储装置具备:第一存储单元(MT),电连接在第一位线(BL)及第一字线(WL);第二存储单元(MT),电连接在第二位线(BL)及所述第一字线;以及第一电路(42),对所述第一字线施加电压。所述第一电路在所述第一存储单元的读出中,对所述第一字线供给第一电压(VA),在所述第二存储单元的读出中,对所述第一字线供给比所述第一电压大的第二电压(VK1)。压(VK1)。压(VK1)。

技术研发人员:清水麻衣 加藤光司 鎌田义彦 酒向万里生

受保护的技术使用者:铠侠股份有限公司

技术研发日:2017.07.27

技术公布日:2022/8/12

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。