具有改善的电力输送的嵌入式多管芯互连桥

1.本技术为分案申请,其原申请是于2018年1月22日向中国专利局提交的专利申请,申请号为201810058578.0,发明名称为“具有改善的电力输送的嵌入式多管芯互连桥”。

技术领域

2.本公开总体上涉及集成电路封装,并且更具体而言,涉及具有连接多于一个集成电路管芯的嵌入式多管芯互连桥(emib)的集成电路封装。

背景技术:

3.集成电路封装通常包括集成电路管芯和在上面安装管芯的基底。管芯可以通过接合线或者焊接凸点耦合至基底。因而,来自集成电路管芯的信号可以通过接合线或者焊接凸点传输至基底。

4.随着对集成电路技术的需求不断地超越持续降低的器件尺寸所能够给予的增益,越来越多的应用需要集成度已经超过了在单个硅管芯中可能达到的集成度的封装解决方案。在为了满足这种需求的尝试中,可以将多于一个管芯置于单个集成电路封装(即,多芯片封装)内。由于不同类型的器件迎合不同类型的应用的需求,因而在一些系统中可能需要更多的管芯来满足高性能应用的需要。相应地,为了获得更高的性能和更高的密度,集成电路封装可以包括沿同一平面横向布置的多个管芯。

5.emib是有时被嵌入到多芯片封装的基底中的小硅管芯,并且用于对该多芯片封装内的集成电路管芯进行互连。传统上,这些emib与其它内插器技术(例如,硅内插器)相比具有有限的电力输送能力。

6.在该语境下,出现了文中描述的实施例。

技术实现要素:

7.一种集成电路封装可以包括封装基底以及安装在所述封装基底上的一个或多个集成电路管芯。所述封装基底可以包括嵌入所述封装基底内的嵌入式多管芯互连桥(emib)。emib是可以用于将多芯片封装中的两个集成电路互连的硅管芯。安装在所述封装基底上的集成电路管芯可以通过所述emib相互通信。所述emib可以具有面对所述集成电路管芯的正面以及与所述正面相对的背面。所述封装基底可以包括从所述emib的背面电耦合至所述emib并向所述emib供应电力的导电路径。所述封装基底可以被安装在印刷电路板上,所述印刷电路板通过所述导电路径向所述emib提供电力。

8.所述封装基底还可以包括在上面安装所述emib的导电层(例如,背面导体)。所述导电路径可以连接至所述导电层,并且可以通过所述导电层向所述emib提供电力。在将emib安装到所述导电层上之前可以将图案化的粘合层施加到所述导电层上,并且所述图案化的粘合层可以包括容纳形成于所述emib的背面的导电焊盘(例如,接触焊盘)的开口。换言之,一旦emib被安装到所述导电层上,那么所述图案化的粘合层就可以横向围绕形成于所述emib的背面的导电焊盘。可以在所述emib的正面形成附加接触焊盘。

9.所述封装基底可以包括直接连接至形成于所述emib的正面的接触焊盘的第一过孔,并且可以包括通过所述导电层耦合至形成于所述emib的背面的接触焊盘的第二过孔。所述第二过孔可以具有大于所述第一过孔的直径的直径。

10.所述emib可以包括耦合至集成电路管芯的导电布线迹线(例如,互连)。形成于所述emib中的微过孔可以耦合在形成于所述emib的背面的导电焊盘的其中之一与所述导电布线迹线之间。电源电压信号或数据信号可以通过所述微过孔被提供到所述导电布线迹线。

11.所述emib可以包括从所述emib的背面延伸至所述emib的正面的多个穿硅过孔。这些穿硅过孔可以用于通过所述emib将电源信号或者数据信号从所述导电路径传送至所述集成电路管芯。

12.所述导电层可以包括相互电隔离的多个导电区域。所述导电层的每个区域可以接收与所述导电层的每个其它区域不同的电源电压信号或数据信号。

13.制作集成电路封装可以包括多个处理步骤。可以形成第一电介质层。可以通过第一电介质层形成过孔。可以在第一电介质层上形成与所述过孔直接物理接触的导电层。形成导电层可以涉及形成相互电隔离的多个导电区域。可以将硅管芯(例如,emib)安装在所述导电层上。可以形成覆盖所述硅管芯的附加电介质层。可以将第一集成电路管芯安装在所述附加电介质层上。可以将第二集成电路管芯安装在所述附加电介质层上。所述硅管芯可以包括将所述第一集成电路管芯耦合至所述第二集成电路管芯的导电布线迹线。

14.在形成所述附加电介质层之前,可以将第二电介质层形成在所述第一电介质层上。可以在所述第二电介质层中形成直接处于所述导电层之上的腔。将硅管芯安装在所述导电层上可以包括将硅管芯插入到所述腔中。可以将图案化的粘合层形成在所述硅管芯与所述导电层之间。所述图案化的粘合层可以包括容纳形成在所述硅管芯的底表面上的接触焊盘的多个开口。

15.通过附图和下面的具体实施方式,本发明的其它特征、其性质和各种优点将会更加显而易见。

附图说明

16.图1是根据实施例的可操作用于相互通信的集成电路装置的例示性系统的示图。

17.图2是根据实施例的例示性多芯片封装的示图。

18.图3是根据实施例的包括使用嵌入式多管芯互连桥(emib)耦合到一起的两个管芯的例示性多芯片封装的截面侧视图。

19.图4是根据实施例的包括使用emib耦合到一起的两个管芯的例示性多芯片封装的顶视图。

20.图5是根据实施例的包括具有穿硅过孔的emib的例示性多芯片封装的截面侧视图。

21.图6是根据实施例的具有内部微过孔的例示性emib的截面侧视图。

22.图7a是根据实施例的被水平地分成相互电隔离的三个电压区域的用于emib的例示性背面导体的顶视图。

23.图7b是根据实施例的被竖直地分成三个电压区域的用于emib的例示性背面导体

的顶视图。

24.图7c是根据实施例的被分成三个电压区域和两个信号区域的例示性导电背面导体的顶视图,这些区域全部相互电隔离。

25.图8是示出根据实施例的用于形成包括具有改善的电力输送能力的emib的封装基底的例示性步骤的流程图。

具体实施方式

26.本发明的实施例涉及集成电路,并且更具体而言,涉及在多芯片封装中通过嵌入式多管芯互连桥来改善电力输送的方式。

27.随着集成电路制造技术向更小的工艺节点缩放,在单个集成电路管芯上设计整个系统(有时称为片上系统)变得越来越有挑战性。设计用于在使泄漏和功耗最小化的同时支持预期性能水平的模拟和数字电路可能极为耗时而且成本高昂。

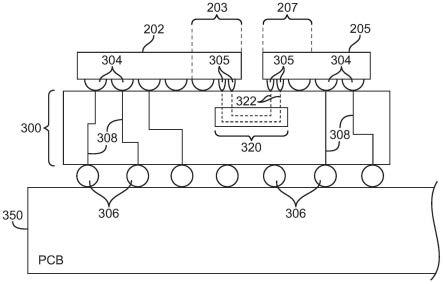

28.单管芯封装的一种替代方案是将多个管芯置于单个封装内的布置。包含多个互连的管芯的这种类型的封装有时可以被称为封装内系统(sip)、多芯片模块(mcm)或多芯片封装。将多个芯片(管芯)置于单个封装中可以允许使用最适当的技术工艺来实施每个管芯(例如,可以使用28nm技术节点实施存储器芯片,而可以使用45nm技术节点实施射频模拟芯片),可以提高管芯到管芯接口的性能(例如,在单个封装内将信号从一个管芯驱动到另一管芯明显比将信号从一个封装驱动到另一封装更容易,从而降低了相关联的输入-输出缓冲器的功耗),可以释放输入-输出引脚(例如,与管芯到管芯连接相关联的输入-输出引脚要比与封装到板连接相关联的引脚小得多),并且可以有助于简化印刷电路板(pcb)设计(即,在正常系统操作期间在上面安装多芯片封装的pcb的设计)。

29.为了促进多芯片封装上的两个芯片之间的通信,所述封装可以包括intel公司设计并且取得了专利的嵌入式多管芯互连桥(emib)。emib是嵌入在多芯片封装的下层基底中并且在封装内的管芯之间提供专用的超高密度互连的小硅管芯。emib一般包括最小长度的导线,这样有助于显著降低负载,并且直接提升性能。

30.emib解决方案相对于使用硅内插器的其它多芯片封装方案可以具有优势,后者易于出现诸如挠曲等问题,并且需要在内插器上和内形成相对较大数量的微凸点和穿硅过孔(tsv),因而降低了总成品率,并且提高了制造复杂性和成本。能够使用内插器集成的管芯的数量也受限于emib技术所支持的管芯的数量。

31.上文描述的emib技术可以被用作系统中的一个或多个集成电路管芯之间的接口。图1是互连的电子装置的例示性系统100的示图。互连的电子装置的系统可以具有诸如装置a、装置b、装置c、装置d等多个电子装置、以及互连资源102。诸如导电线和总线、光互连基础设施、或者具有可选的中间开关电路的有线和无线网络的互连资源102可以用于从一个电子装置向另一电子装置发送信号,或者从一个电子装置向多个其它电子装置广播信息。例如,装置b中的发射器可以向装置c中的接收器发送数据信号。类似地,装置c可以使用发射器向装置b中的接收器发送数据。

32.电子装置可以是与其它电子装置进行通信的任何适当类型的电子装置。这种电子装置的示例包括基本电子部件和电路,例如,模拟电路、数字电路、混合信号电路、形成于单个封装内的电路、容纳在不同封装内的电路、在印制电路板(pcb)上互连的电路等。

33.如图2所示,多芯片封装200可以包括主管芯202、收发器管芯204、存储器管芯206以及附加辅助管芯208。例如,主管芯202可以是中央处理单元(cpu)、图形处理单元(gpu)、专用集成电路(asic)、可编程逻辑器件(pld)或者任何其它期望的处理器或逻辑器件。诸如收发器管芯204、存储器管芯206和辅助管芯208的次级集成电路管芯可以耦合至主管芯202,并且可以与主管芯202通信。例如,存储器管芯206可以是可擦可编程只读存储器(eprom)芯片、非易失性存储器(例如,3d xpoint)芯片、易失性存储器(例如,高带宽存储器)芯片或者任何其它适当存储器器件。辅助管芯208可以包括附加存储器管芯、收发器管芯、可编程逻辑器件以及任何其它适当的集成电路器件。

34.emib可以嵌入在多芯片封装中,以连接封装上的两个相邻的集成电路管芯。如图3所示,主管芯202和次级管芯205可以使用焊接凸点304和焊接微凸点305安装到封装基底300上。封装基底300可以使用焊接(例如,焊接球、焊接凸点)306安装到印刷电路板(pcb)350上。术语焊接“球”或焊接“凸点”有时可以互换使用。可以通过焊接球306、封装300中的封装过孔308以及焊接凸点304在pcb 350与管芯202和205之间传递信号(例如,数据信号和电源电压信号)。

35.主管芯202可以使用嵌入在封装基底300中的emib 320耦合至次级管芯205。在主管芯202与次级管芯205之间传送的信号可以通过互连(例如,导电路径)322和微凸点305来传送。emib 320可以具有面向主管芯202和次级管芯205的正面,并且可以具有面向封装基底300的背面。传统上,emib形成在固态电浮导电板上,以实现结构支撑。因此,难以向与主管芯202和次级管芯205的区域203和207重叠的微凸点305提供电力,因为由于背面布线受到导电板的阻挡而不能从pcb通过emib向区域203和207竖直地输送电力。

36.图4示出了区域203和207中的封装基底300的顶视图,并且图示了向区域203和207中的微凸点阵列进行电源信号和接地信号输送的可能手段。区域203和207中的两个微凸点阵列可以与形成在封装基底300中的emib 320重叠。每个微凸点阵列(例如)可以对应于集成电路管芯(例如,图3的主管芯202和次级管芯205)的边缘。可以将三个不同的电压信号施加至封装基底300的焊盘:(1)公共电压信号vss(例如,接地电源电压信号),(2)用于区域207的(例如,用于图3中的次级管芯205的)电源电压信号vcc1以及用于区域203的(例如,用于图3的主管芯202的)电源电压信号vcc2。应当指出,区域203中的微凸点的一部分也可以接收电源电压信号vcc1。

37.这些电源电压信号和公共电压信号可以被输送至区域203和207中的外围微凸点,而不产生例外的功率效率损失。例如,电压信号vss、vcc1和vcc2可以使用形成于封装基底的顶层中的导体(例如,铜迹线)被输送至处于区域203和207的微凸点阵列的边缘的微凸点。

38.此外,区域203和207的微凸点阵列的中央(例如,不处于外围)的微凸点可以通过在封装基底的顶层中形成被布置为跨越给定微凸点阵列竖直延伸的导体(例如,铜迹线)而将电压信号vss、vcc1和vcc2布线至这些微凸点。只有处于这些导体之一的路径中的微凸点可以接收由该导体运送的相应电压信号。然而,使这些导体之一扩展以覆盖微凸点阵列的整个宽度可能不期望地导致功率效率损失。因此,为处于区域203和207的微凸点阵列的中央的微凸点提供替代的电力输送手段将是有利的。

39.针对上文描述的顶侧微凸点电力输送的一种替代方案是从背面竖直地通过封装

基底和emib将电源信号和接地信号从pcb输送至所述微凸点。如图5所示,可以使用焊接凸点(例如,受控塌陷芯片连接(c4)凸点)304和微凸点305将主管芯202安装到封装基底300上。应当指出,焊接凸点304的间距宽度可以大于微凸点305的间距宽度,使得微凸点305具有比焊接凸点304更大的连接密度。微凸点305的直径一般也比c4凸点304的直径小(例如,凸点305可以至少小二倍、至少小四倍,等等)。

40.可以通过形成于封装基底300的布线层351-1、351-2、351-3和351-4中的过孔504和迹线502从印刷电路板(例如,图3的pcb 350)向焊接凸点304提供信号(例如,数据信号或者电源电压信号)。如果希望,那么封装基底可以包括附加的层(例如,封装基底中的层的数量不限于4)。

41.可以通过过孔505和迹线503从emib 320向微凸点305提供信号(例如,数据信号或电源电压信号)。提供给微凸点305的信号可以接收自耦合到emib 302的另一芯片,或者可以接收自在上面安装封装基底300的pcb(例如,图3的pcb 350)。应当指出,过孔505小于过孔504和过孔504'。

42.可以在封装基底300的制造期间使用粘合层514将emib 320安装在封装基底300的层351-2中的背面导体(例如,导电层或者铜导电层)510上。可以包括与emib 320相邻的腔512,以对emib 320与封装基底300之间的热膨胀系数之间的差异负责,这可以减少置于emib 320上的热应力。

43.emib 320可以包括穿硅过孔(tsv),所述穿硅过孔从emib 320的正面竖直地延伸到emib 320的背面,以将形成于emib 320的正面的接触焊盘516连接至形成于emib 320的背面的接触焊盘518。可以对粘合层514进行图案化以容纳接触焊盘518,以确保接触焊盘518与背面导体510电接触。换言之,粘合层514可以横向围绕emib 320的接触焊盘518,而不介入在接触焊盘518与背面导体510之间。

44.根据实施例,背面导体510可以通过过孔504'和迹线502'接收来自pcb(例如,图3的pcb 350)的电源电压信号和/或数据信号,并且可以将这些信号提供到emib 320的接触焊盘518。应当指出,过孔504'可以具有大于过孔505的直径的直径。具有较大直径允许过孔504'运送比借助于具有相对较小的直径的过孔所能够实现的更高的功率。

45.通过经由背面导体510、过孔504'和迹线502'从pcb向emib 320提供信号,并且通过emib 320中的tsv 520向一个或两个电路管芯提供电力,可以通过emib 320实现竖直配电。

46.常规emib布置缺乏这种背面竖直配电路径,而是局限于在通过emib连接的芯片之间通过emib自身或者通过将电力布线至emib周围的这些芯片而传送电力。与耦合至emib 320的竖直配电路径相比,这两种常规配电选项都由于需要较小规格的迹线或者较长的迹线来实施电力输送而不利地降低了包含emib的系统的功率效率。

47.因而,就功率效率而言,耦合在pcb与emib 320的背面之间的包括背面导体510、过孔504'和迹线502'的竖直配电路径相对于这些常规emib布置是更有利的。

48.还可以将信号从pcb提供到emib 320的内部互连。如图6中所示,emib 320可以包括互连(例如,导电布线迹线)602和604。接触焊盘518-1和518-2可以接收电源电压信号、接地电压信号或者数据信号(例如,来自图5的背面导体510),并且可以将这些信号传送至emib微过孔606和608。微过孔606可以包括介入在互连602与接触焊盘518-1之间的部分,以

使由接触焊盘518-1接收的信号可以被传送至互连602。微过孔606还可以包括介入在互连602与接触焊盘516-1之间的部分,以使由接触焊盘518-1接收的信号还可以被传送至接触焊盘516-1,继而被传送到与接触焊盘516-1耦合的任何微凸点。

49.微过孔608可以仅从接触焊盘518-2延伸至互连604。接触焊盘518-2可以通过微过孔608将所接收的信号传送至互连604。任选地,可以将附加的微过孔608'介入在互连602与互连604之间,和/或可以介入在接触焊盘516-2与互连602之间。该布置允许由接触焊盘518-2接收的信号被传送至互连602和604中的每者以及接触焊盘516-2,并由此被传送至与接触焊盘516-2耦合的任何微凸点。

50.如果希望,可以将图5的背面导体510分成相互电隔离的多个区域,其中,每个区域可以从pcb接收不同的电源电压信号、接地电压信号或者数据信号。下文将结合图7a-图7c描述背面导体510的一些可能布置。

51.如图7a所示,背面导体510可以被水平地分成相互电隔离的区域700、702和704。电源电压信号vcc1可以被施加至区域702。公共(例如,接地)电源电压信号vss可以被施加至区域700。电源电压信号vcc2可以被施加至区域704。背面导体510的该布置允许将三种不同类型的电源/接地电压信号施加至通过附接至背面导体510的emib(例如,emib 320)相互连接的两个芯片中的任一者的微凸点上。

52.如图7b所示,背面导体510可以被竖直地分成相互电隔离的区域710、712和714。电源电压信号vcc2可以被施加至区域712。公共(例如,接地)电源电压信号vss可以被施加至区域710。电源电压信号vcc3可以被施加至区域714。背面导体510的该布置允许将电源电压信号vcc2施加至通过附接到背面导体510的emib(例如,emib 320)相互连接的两个芯片的其中之一的微凸点,允许将电源电压信号vcc3施加至两个芯片中的另一芯片的微凸点,并且允许将公共信号vss施加至两个芯片中的任一个或两者。

53.如图7c所示,背面导体510可以被分成三个竖直分开的区域,每个区域相互电隔离,与图7b的布置类似。每个竖直分开的区域可以接收电源电压信号vcc1、电源电压信号vcc2和公共信号vss之一。背面导体510还可以包括相互电隔离并且与所述三个竖直分开的区域电隔离的两个水平区域750和752。数据信号sig1可以被施加至区域750,并且数据信号sig2可以被施加至区域752。通过这种方式,也可以将数据信号传送至安装在背面导体510上的emib(例如,emib 320)。

54.图7a-图7c所示的背面导体510的布置只是例示性的。如果希望,背面导体510可以包括任何数量的区域,这些区域相互电隔离,并且每个区域接收不同的电源电压信号或数据信号(例如,来自印刷电路板)。

55.图8示出了在制造图5的封装基底300时执行的例示性步骤。

56.在步骤800,可以形成第一电介质层351-1。在该步骤,还可以形成层351-1中的过孔504和504'以及迹线502和502'。

57.在步骤802,可以形成第二电介质层351-2,在该步骤,还可以在层351-2中形成过孔504、迹线502以及背面导体510。如上文联系图7a-图7c所描述的,背面导体510可以被形成为具有多个区域,这些区域相互电隔离并且每个区域接收不同的电源电压信号或者数据信号。

58.在步骤804,可以形成第三电介质层351-3。在该步骤,可以在层351-3中形成过孔

504和迹线502。

59.在步骤806,可以在第二电介质层351-2和第三电介质层351-3中形成腔(例如,使用光刻蚀刻、研磨或钻孔)。腔可以与背面导体510重叠,并且可以延伸穿过层351-2和351-3,以暴露背面导体510。

60.在步骤808,可以在腔内对粘合层514图案化,从而在粘合层514中形成开口以容纳emib 320的接触焊盘518。

61.在步骤810,可以将emib 320置于所述腔内的图案化的粘合剂上,由此可以将emib 320安装在背面导体510上。应当指出,在将emib 320置于所述腔中之前(例如,在emib 320的制造期间),可能已经在emib 320内形成了任何tsv或内部emib微过孔。

62.在步骤812,可以形成包括电介质层851-4在内的剩余电介质层以及电介质层851-3的设置在emib 320之上的部分。在该步骤,还可以形成过孔504和505以及迹线(例如,过孔焊盘)502和503。

63.任选地,可以省略步骤804,并且可以在步骤812期间形成整个的层851-3。在该任选情况下,只需在步骤806期间在第二电介质层851-2中形成所述腔。

64.到目前为止已经关于集成电路描述了实施例。文中描述的方法和设备可以被并入任何适当的电路中。例如,可以将它们并入很多类型的器件中,例如,可编程逻辑器件、专用标准产品(assp)和专用集成电路(asic)。可编程逻辑器件的示例包括可编程阵列逻辑(pal)、可编程逻辑阵列(pla)、现场可编程逻辑阵列(fpla)、电可编程逻辑器件(eplad)、电可擦可编程逻辑器件(eepld)、逻辑单元阵列(lca)、复杂可编程逻辑器件(cpld)和现场可编程门阵列(fpga),这里只是举出了几个示例。

65.上文仅用于对本发明的原理进行例示,并且本领域技术人员可以做出各种修改。上述实施例可以单独实施,或者可以按照任意组合实施。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。