用于实现基4 booth乘法器的32位加法器及其实现方法、运算电路及芯片

技术领域

1.本技术实施例涉及电路领域,尤其涉及一种用于实现基4 booth乘法器的32位加法器及其实现方法、运算电路及芯片。

背景技术:

2.基4 booth乘法器是数字电路设计中常用电路之一,例如,基4 booth乘法器常常用于中央处理器(central processing unit,cpu)、图形处理器(graphics processing unit,gpu)等复杂逻辑芯片,也常常用于微控制单元(microcontroller unit,mcu)、现场可编程门阵列(field programmable gate array,fpga)等综合性设计芯片。一般地,乘法运算可以分为三个步骤:部分积生成、部分积压缩至两行向量、最后将两行向量再相加。在部分积生成中,通常采用基4-booth编码,基4-booth编码可使乘法器的部分积数量减少一半。

3.因此,如何基于基4-booth编码中部分积得到最终的计算结果,进而提升基4-booth编码乘法器整体性能,成为亟待解决的技术问题。

技术实现要素:

4.有鉴于此,本技术实施例提供了一种用于实现基4 booth乘法器的32位加法器及其实现方法、运算电路及芯片,用以克服上述全部或部分技术缺陷。

5.第一方面,本技术实施例提供了一种用于实现基4 booth乘法器的32位加法器,其包括:

6.多路进位保存加法器用于确定8组带有基4 booth乘法进位权重的16比特的部分积在第0-31个比特位上对应的比特位,并对第0-31个比特位上的部分积分别进行压缩,输出32比特的2组数据,所述多路进位保存加法器在第0-31个比特位上用于压缩的进位保存加法器的数量为对应比特位上部分积的数量与符号位的数量之和减2;

7.带进位链的进位加法器,用于将所述32比特的2组数据进行相加求和,所述带进位链的进位加法器包括:

8.n个进位模块,每个进位模块对应所述32比特的2组数据的多个比特位,其中,第n个进位模块与第n-1个进位模块连接,以用于接收所述第n-1进位模块输出的级间进位参数,所述被乘数和所述乘数为16位二进制数,n为小于或者等于5的整数,n为大于1且小于或等于n的整数;每个进位模块包括预处理单元和多个进位计算单元,一个进位计算单元对应所述32比特的2组数据的一个比特位;其中,所述部分积用于表征乘数的第i 1个比特位、第i个比特位和第i-1个比特位与被乘数基于基4 booth乘法的乘积;i为大于或等于0且小于或等于15的整数;

9.其中,所述第n个进位模块包含的预处理单元,用于对对应的所述32比特的2组数据中的多个比特位进行预处理;

10.所述第n个进位模块包含的多个进位计算单元,用于根据所述预处理的结果和所

述第n-1个进位模块的级间进位参数进行运算,生成所述第n个进位模块对应的每个比特位的进位输出和所述第n个进位模块的级间进位参数;

11.求和模块,所述求和模块与所述n个进位模块电连接,以用于所述32比特的2组数据的符号位选通控制信号为有效位时,将所述32比特的2组数据进行处理,所述处理包括:将所述32比特的2组数据的部分积的最高比特位取反、对第一个部分积的最高比特位加1、以及在所有部分积的最高位前增加1个比特数,且所述比特数取值为1;以及用于根据处理后的所述所述32比特的2组数据中的每个比特位、以及对应的进位输出进行运算,得到对应的求和结果;其中,符号位选通控制信号用于表征部分积为被乘数乘以负数倍。

12.第二方面,本技术提供了一种用于实现基4 booth乘法器的32位加法器的实现方法,其包括:

13.接收8组带有基4 booth乘法进位权重的16比特的部分积;所述部分积用于表征乘数的第i 1个比特位、第i个比特位和第i-1个比特位与被乘数基于基4 booth乘法的乘积;i为大于或等于0且小于或等于15的整数;

14.确定8组带有基4 booth乘法进位权重的16比特的部分积在第0-31个比特位上对应的比特位,并对第0-31个比特位上的部分积分别进行压缩,输出32比特的2组数据;所述多路进位保存加法器在第0-31个比特位上用于压缩的进位保存加法器的数量为对应比特位上部分积的数量与符号位的数量之和减2;

15.将压缩得到的所述32比特的2组数据按照比特位从低到高的顺序划分为n个数据组,每个数据组包括32比特的2组数据中的多个比特位,n为小于或者等于5的整数;其中,所述部分积用于表征乘数的第i 1个比特位、第i个比特位和第i-1个比特位与被乘数基于基4 booth乘法的乘积;i为大于或等于0且小于或等于15的整数;

16.对所述每个数据组包含的多个比特位进行预处理;

17.计算所述每个数据组包含的多个比特位的进位输出,其中,对于n个数据组中的第n个数据组,根据所述第n个数据组的预处理结果和第n-1个数据组的级间进位参数进行运算,生成所述第n个数据组对应的每个比特位的进位输出和所述第n个进位模块的级间进位参数,n为大于1且小于或等于n的整数;

18.在所述32比特的2组数据的符号位选通控制信号为有效位时,将所述32比特的2组数据的部分积进行处理,所述处理包括:将所述32比特的2组数据中部分积的最高比特位取反、对第一个部分积的最高比特位加1、以及在所有部分积的最高位前增加1个比特数,且所述比特数取值为1;其中,符号位选通控制信号用于表征部分积为被乘数乘以负数倍;

19.根据处理后的所述32比特的2组数据中的每个比特位、以及对应的进位输出进行运算,得到对应的求和结果。

20.第三方面,本技术提供了一种运算电路,所述运算电路包括根据第一方面任一实施例提供的加法器。

21.第四方面,本技术提供了一种芯片,所述芯片包括根据第二方面任一实施例提供的运算电路。本技术实施例提供了一种用于实现基4 booth乘法器的32位加法器及其实现方法、运算电路和芯片,由于多路进位保存加法器用于用于确定8组带有基4 booth乘法进位权重的16比特的部分积在第0-31个比特位上对应的比特位,并对第0-31个比特位上的部分积分别进行压缩,输出32比特的2组数据;带进位链的进位加法器,用于将所述32比特的2

组数据进行相加求和,所述带进位链的进位加法器包括包括n个进位模块,每个进位模块对应32比特的2组数据中的多个比特位,且每个进位模块包括预处理单元和多个进位计算单元,第n个进位模块包含的预处理单元用于对对应的32比特的2组数据中的多个比特位进行预处理,第n个进位模块包含的多个进位计算单元,用于根据预处理的结果和第n-1个进位模块的级间进位参数进行运算,生成第n个进位模块对应的每个比特位的进位输出和第n个进位模块的级间进位参数,这使得在获取到第n-1个进位模块输出的级间进位参数时,第n个进位模块中的每个进位计算单元可以直接利用预处理结果和第n-1个进位模块输出的级间进位参数并行计算对应的每个比特位的进位输出,由此基本上实现了并行计算部分积中每个比特位的进位输出,以用于求和运算,由此可以缩短整个计算过程的时长,提高计算速度。

附图说明

22.后文将参照附图以示例性而非限制性的方式详细描述本技术实施例的一些具体实施例。附图中相同的附图标记标示了相同或类似的部件或部分。本领域技术人员应该理解,这些附图未必是按比值绘制的。附图中:

23.图1为本技术实施例提供的一种用于实现基4 booth乘法器的32位加法器用于对16比特的8组数据求和的原理示意图;

24.图2为本技术实施例提供的一种用于实现基4 booth乘法器的32位加法器中多路进位保存加法器的结构示意图;

25.图3为本技术实施例提供的一种用于实现基4 booth乘法器的32位加法器中带进位链的进位加法器的结构示意图;

26.图4为本技术实施例提供的一种用于实现基4 booth乘法器的32位加法器中带进位链的进位加法器的进位模块中的第一预处理单元的电路示意图;

27.图5为本技术实施例提供的一种用于实现基4 booth乘法器的32位加法器中带进位链的进位加法器的进位模块中的第二预处理单元的电路示意图;

28.图6为本技术实施例提供了一种用于实现基4 booth乘法器的64位加法器中带进位链的进位加法器的进位链的示意图;

29.图7为本技术实施例提供的一种用于实现基4 booth乘法器的32位加法器的实现方法的示意性流程图。

具体实施方式

30.下面结合本发明实施例附图进一步说明本发明实施例具体实现。

31.实施例一

32.图1为本技术实施例提供的一种用于实现基4 booth乘法器的32位加法器用于对16比特的8组数据求和的原理示意图。其中,每一数据均为部分积,用于表征乘数的第i 1个比特位、第i个比特位和第i-1个比特位与被乘数基于基4 booth乘法的乘积;i为大于或等于0且小于或等于15的整数。具体地,多路进位保存加法器,用于确定8组带有基4 booth乘法进位权重的16比特的部分积在第0-31个比特位上对应的比特位。由于8组部分积的进位权重不同,因此根据各进位权重进行排位后,形成如图1所示的错位排列形式。多路进位保

存加法器对第0-31个比特位上的部分积分别进行压缩,输出32比特的2组数据,所述多路进位保存加法器在第0-31个比特位上用于压缩的进位保存加法器的数量为对应比特位上部分积的数量与符号位的数量之和减2。

33.图2为本技术实施例提供的一种用于实现基4 booth乘法器的32位加法器中多路进位保存加法器的结构示意图。多路进位保存加法器用于将16比特的8组数据实现8-2数据压缩,输出32比特的2组数据,所述32位加法器的每一比特位上对应的进位保存加法器的数量为对应比特位上部分积的数量与符号位的数量之和减2。比如对于,对于第14-18比特位对应的进位保存加法器的数量为7个。

34.图3为本技术实施例提供的一种用于实现基4 booth乘法器的32位加法器中带进位链的进位加法器的结构示意图。本实施例的带进位链的进位加法器可以为独立的硬件电路结构,也可以为芯片或微处理器等其他器件的基础电路单元结构。如图3所示,本技术实施例提供的用于实现基4 booth乘法器的32位加法器中带进位链的进位加法器包括n个进位模块10,n为小于或者等于5的整数。每个进位模块对应32比特的2组数据中的多个比特位,其中,32比特的2组数据为16位二进制数。例如,一个进位模块可以对应32比特的2组数据中的2个比特位、3个比特位或更多个比特位等。应理解,n个进位模块10中的每个进位模块对应的32比特的2组数据中的比特位的数量可以相同,也可以不同。其中,所述部分积用于表征乘数的第i 1个比特位、第i个比特位和第i-1个比特位与被乘数基于基4 booth乘法的乘积;i为大于或等于0且小于或等于15的整数。

35.其中,第n个进位模块与第n-1个进位模块连接,以用于接收第n-1进位模块输出的级间进位参数,由此,基于第n-1个进位模块输出的级间进位参数,计算第n个进位模块的级间进位参数和第n个进位模块对应的每个比特位的进位输出。其中,n为大于1且小于或等于n的整数。

36.每个进位模块包括预处理单元和多个进位计算单元,一个进位计算单元对应32比特的2组数据的一个比特位。

37.本实施例中,第n个进位模块包含的预处理单元,用于对对应的32比特的2组数据中的多个比特位进行预处理。

38.可选地,在本技术的一种实现方式中,预处理结果包括:组内进位生成信号和组内进位传播信号。第n个进位模块包含的预处理单元,具体用于:对对应的32比特的2组数据中的每个比特位进行运算,生成每个比特位对应的进位生成信号和进位传播信号;基于对应的至少一个比特位的进位生成信号和进位传播信号分别生成每个比特位的组内进位生成信号和组内进位传播信号。

39.具体地,对对应的32比特的2组数据中的每个比特位进行逻辑与运算,生成每个比特位的进位生成信号,进位生成信号为32比特的2组数据中的对应比特位的逻辑与值运算结果。对对应的32比特的2组数据中的每个比特位进行逻辑或运算,生成每个比特位的进位传播信号,进位传播信号为32比特的2组数据中的对应比特位的逻辑或值运算结果。为了便于电路实现时的整体化布局,在本技术实施例中,有时也将每个比特位的进位生成信号进行逻辑非运算的结果称为进位生成信号。类似地,将每个比特位的进位传播信号进行逻辑非运算的结果称为进位传播信号。

40.在得到第n个进位模块对应的每个比特位的进位生成信号和进位传播信号之后,

第n个进位模块包含的预处理单元还可以对相邻的多个比特位的进位生成信号进行逻辑或运算,生成组内进位生成信号,第n个进位模块包含的预处理单元还可以对相邻的多个比特位的进位传播信号进行逻辑与运算,生成组内进位传播信号。为了便于电路实现时的整体化布局,在本技术实施例中,有时也将组内进位生成信号进行逻辑非运算的结果称为组内进位生成信号。类似地,将组内进位传播信号进行逻辑非运算的结果称为组内进位传播信号。

41.例如,对于第一加数a和第二加数b中的第i个比特位,第i个比特位的进位生成信号gi=ai·bi

,第i个比特位的进位传播信号pi=ai bi。如上所述,为了便于电路实现时的整体化布局,第i个比特位的进位生成信号和进位传播信号有时也分别被表示为或第j个比特位到第i个比特位的组内进位产生信号g

i:j

=gi g

i 1

…

gi,第j个比特位到第i个比特位的组内进位传播信号p

i:j

=pi·

p

i 1

·

…

·

pi。如上所述,为了便于电路实现时的整体化布局,第j个比特位到第i个比特位的组内进位产生信号和进位传播信号有时也可以被表示为和

42.此外,g

i:j

=g

i:k

g

k-1:j

,并且,p

i:j

=p

i:k

·

p

k-1:j

,其中,k为按照比特位从低到高的顺序位于第j个比特位到第i个比特位之间的任一比特位。

43.本实施例中,第n个进位模块包含的多个进位计算单元,用于根据预处理的结果和第n-1个进位模块的级间进位参数进行运算,生成第n个进位模块对应的每个比特位的进位输出和第n个进位模块的级间进位参数。

44.可选地,在本技术的一种实施例中,第n个进位模块包含的每个进位计算单元,具体用于根据对应的比特位的组内进位生成信号和组内进位传播信号以及第n-1个进位模块的级间进位参数进行运算,生成对应的比特位的进位输出。

45.对于第n个进位模块对应的多个比特位中的最高位,该最高比特位对应的进位计算单元,还用于将在第n个进位模块对应的最高位的进位输出的计算中得到的进位参数,作为第n个进位模块的级间进位参数。

46.其中,进位参数是在每个比特位的进位输出的计算过程中得到中间量,进位参数与进位输出之间存在预设关系。每个比特位的进位输出可以基于该比特位的进位参数与该比特位的进位传播信号进行运算得到,具体地,每个比特位的进位输出为该比特位的进位参数与该比特位的进位传播信号的逻辑与运算结果。例如,若第i个比特位的进位输出为ci,第i个比特位的进位传播信号为pi,第i个比特位的进位参数为cpi,则预设关系为:ci=pi·

cpi。

47.若第n-1个进位模块对应的多个比特位中的最高位为第(k-1)个比特位,则在第n-1个进位模块中的多个进位计算单元在计算第(k-1)个比特位的进位输出c

k-1

时得到进位参数cp

k-1

,作为第n-1个级间进位参数。若第n个进位模块的预处理单元输出结果中包括组内进位生成信号g

i:k

和组内进位生成信号p

i-1:k

,则第i个比特位的进位输出为ci=g

i:k

p

i:k-1

·

cp

k-1

。此外,由于p

i:k-1

·

cp

k-1

=p

i:k

·

p

k-1

·

cp

k-1

,因此,ci=g

i:k

p

i:k

·ck-1

也成立。

48.由于g

i:k

和p

i:k

可以通过预处理单元处理得到,因此,第n个进位模块中与第i个比

特位对应的进位计算单元在得到第n-1个进位模块的级间进位参数c

k-1

时,可以通过简单的逻辑运算,得到第i个比特位的进位输出或进位参数。此外,由于第n个进位模块中的预处理单元可以对第n个进位模块对应的多个比特位进行预处理得到对应的多个组内进位生成信号和组内进位传播信号第n个进位模块中的多个进位计算单元可以,基于对应的组内进位生成信号和组内进位传播信号并行计算每个比特位的进位输出,由此提高进位计算的效率。

49.应理解,为了便于电路实现时的整体化布局,进位参数cp

k-1

和进位输出c

k-1

有时也被表示为和

50.本技术实施例中,由于第n个进位模块包含的预处理单元对对应的32比特的2组数据中的多个比特位进行预处理,第n进位模块包含的多个进位计算单元,用于根据预处理的结果和第n-1个进位模块的级间进位参数进行运算,生成第n个进位模块对应的每个比特位的进位输出和第n个进位模块的级间进位参数,这使得在获取到第n-1个进位模块输出的级间进位参数时,第n个进位模块中的每个进位计算单元即可以直接利用预处理结果和第n-1个进位模块输出的级间进位参数并行计算对应的每个比特位的进位输出,由此基本上实现了并行计算16位二进制数据中每个比特位的进位输出。

51.此外,如图3所示,用于实现基4 booth乘法器的32位加法器中多路进位保存加法器还包括求和模块,该求和模块与n个进位模块电连接,以用于在32比特的2组数据的符号位选通控制信号为有效位时,将32比特的2组数据进行处理,所述处理包括:将被乘数和乘数的所有部分积的最高比特位取反、对第一个部分积的最高比特位加1、以及在所有部分积的最高位前增加1个比特数,且所述比特数取值为1;以及用于根据处理后的所述32比特的2组数据中的每个比特位、以及对应的进位输出进行运算,得到对应的求和结果;其中,符号位选通控制信号用于表征部分积为被乘数乘以负数倍。

52.例如,对于第一加数a和第二加数b中的第i个比特位,可以根据以下求和公式,得到第i个比特位的求和结果。该公式为:

53.其中,c

i-1

为第一加数a和第二加数a中的第i-1个比特位的进位输出。

54.本实施例中,由于基本上并行计算16位二进制数据中每个比特位的进位输出,因此,可以基本上并行地计算16位二进制数据中每个比特位的求和结果,由此可以缩短整个计算过程的时长,提高计算速度。

55.可选地,在本技术的一种实施例中,第n个进位模块对应的32比特的2组数据中的比特位的数量等于或大于第n-1个进位模块对应的32比特的2组数据中的比特位的数量。

56.由于第n个进位模块对应的每个比特位的进位输出的计算依赖于第n-1个进位模块的级间进位参数,因此,第n个进位模块中的每个进位计算单元的进位运算时间相对于第n-1个进位模块中的每个进位计算单元的进位运算时间具有一定的逻辑时延。通过使第n个进位模块对应的32比特的2组数据中的比特位的数量等于或大于第n-1个进位模块对应的32比特的2组数据中的比特位的数量,可以充分利用这一逻辑延时进行组内进位生成信号和组内进位传播信号的计算,避免第n个进位模块在计算时等待第n-1个进位模块的级间进位参数的情况出现,有利于进一步减小运算所耗费的时间。

57.可选地,在本技术的一种实施例中,n等于5,第1个进位模块对应32比特的2组数据的第0比特位至第3比特位,所述第2个进位模块对应32比特的2组数据的第4比特位至第7比特位,所述第3个进位模块对应32比特的2组数据的第8比特位至15比特位,所述第4个进位模块对应32比特的2组数据的第16比特位至23比特位,所述第5个进位模块对应32比特的2组数据的第24比特位至31比特位。由此,使得加法器的布局较为集中,面积较小,有利于整体结构化布局。

58.应当理解,在本实施例中,进位模块的数量n可以为2个、4个、或者更多个,并且每个进位模块对应的具体比特位可以根据需要进行设置,本实施例对此不做限定。

59.实施例二

60.基于实施例一提供的用于实现基4 booth乘法器的32位加法器,进一步,本实施例提供了图3所示的用于实现基4 booth乘法器的32位加法器中多路进位保存加法器中的一个进位模块的结构示意图。应理解,该进位模块可以为实施例一中的n个进位模块中的任一进位模块,为了便于描述,下文中将该进位模块称为第n个进位模块。在本实施例中,第n个进位模块包含的预处理单元包括交替布置的至少一个第一预处理单元和至少一个第二预处理单元。

61.本实施例中,第一预处理单元用于对对应的32比特的2组数据中的第i个比特位和第i-1个比特位进行运算,生成第一预处理结果,第一预处理结果指示第i个比特位和第i-1个比特位的进位生成信号的逻辑或运算结果,i为奇数。

62.可选地,在本技术的一种具体的实现方式中,如图4所示,第一预处理单元包括:第一与门201、第二与门202和第一或非门203,第一与门201的第一输入端和第二输入端分别接收第i个比特位,第一与门201的输出端连接至第一或非门203的第一输入端;第二与门202的第一输入端和第二输入端分别接收第i-1个比特位,第二与门202的输出端连接至第一或非门203的第二输入端,第一或非门203的输出端输出第一预处理结果。例如,若第一加数为a,第二加数为b,则第一预处理结果为其中,gi和g

i-1

为第i个比特位的进位生成信号和第i-1个比特位的进位生成信号。

63.应理解,第一预处理单元也可以直接由与或非门这种结构实现,本实施例对此不做限定。

64.本实施例中,第二预处理单元用于对对应的32比特的2组数据中的第j个比特位和第j-1个比特位进行运算,生成第二预处理结果,第二预处理结果指示第j个比特位和第j-1个比特位的进位传播信号的逻辑与运算结果,j为偶数。

65.可选地,在本技术的一种具体的实现方式中,如图5所示,第二预处理单元包括:第一或门301、第二或门302和第一与非门303,第一或门301的第一输入端和第二输入端分别接收第j个比特位,第一或门301的输出端连接至第一与非门的第一输入端;第二或门302的第一输入端和第二输入端分别接收第j-1个比特位,第二或门302的输出端连接至第一与非门303的第二输入端,第一与非门303的输出端输出第二预处理结果。例如,若第一加数为a,第二加数为b,则第一预处理结果为其中,pj和p

j-1

为第j个比特位的进位传播信号和第j-1个比特位的进位传播信号。

66.应理解,第二预处理单元也可以直接由或与非门这种结构实现,本实施例对此不

做限定。

67.相应地,第n个进位模块包含的多个进位计算单元,用于基于至少一个第一预处理结果和至少一个第二预处理结果以及第n-1个进位模块的级间进位参数得到对应的比特位的进位输出。

68.可选地,在本技术的一个实施例中,第n个进位模块包含的预处理单元还包括第三预处理单元和第四预处理单元,第三预处理单元分别对至少一个第一预处理单元输出的第一预处理结果和至少一个第二预处理单元输出的第二预处理结果中的相邻至少两个进行运算,以生成对应的第三预处理结果和第四预处理结果,第三预处理结果指示对应的相邻多个比特之间的进位参数,第四预处理结果指示对应的相邻多个比特的进位传播信号的逻辑与运算结果。第n个进位模块包含的多个进位计算单元,用于基于第三预处理结果和第四预处理结果以及第n-1个进位模块的级间进位参数得到对应的比特位的进位输出。

69.例如,第三预处理单元对第一预处理结果和以及第二预处理结果进行运算,生成指示第4个比特位至第7个比特位之间的进位参数第四预处理单元对基于第二预处理结果和第二预处理结果进行运算,生成指示第3个比特位至第6个比特位的进位生成信号的逻辑或运算结果,即一个组内进位传播信号(也即,pan_6_3)。对应的进位计算单元可以基于第三预处理结果gon_7_4和第四预处理结果pan_6_3,结合第n-1个进位模块的级间进位参数得到第7个比特位的进位输出。

70.可选地,在本技术的一种实施例中,第n个进位模块包含的多个进位计算单元包括与第i个比特位对应的第一进位计算单元,第一进位计算单元包括第三或门、第三与门和第二或非门;

71.第三或门的第一输入端连接至对应的第二预处理单元的输出端,第三或门的第二输入端连接至第n-1个进位模块输出的级间进位参数,第三或门的输出端连接至第三与门的第一输入端,第三与门的第二输入端连接至对应的第一预处理单元的输出端,第三与门的输出端输出第i个比特的进位参数;

72.第三与门的输出端连接至第二或非门的第一输入端,第二或非门的第二输入端接收第i个比特位的进位传播信号,第二或非门的输出端连接至求和模块,以向求和模块输出第i个比特位的进位输出。

73.可选地,在本技术的一种实施例中,多个进位计算单元还包括第j个比特位对应的第二进位计算单元,第二进位计算单元包括第四或门和第二与非门。

74.第四或门的第一输入端连接至对应的第二预处理单元的输出端,第四或门的第二输入端连接至第n-1个进位模块输出的级间进位参数或第j-1个比特位的进位参数,第四或门的输出端连接至第二与非门的第一输入端,第二与非门的第二输入端接收第j个比特位对应的进位生成信号,第二与非门的输出端连接至求和模块,以向求和模块输出第j个比特位的进位输出。

75.本实施例中,由于每个进位模块中的第一预处理单元、第二预处理单元、第三预处

理单元和第四预处理单元对每个进位模块对应的32比特的2组数据中的多个比特位进行预处理,每个进位模块包含的多个进位计算单元,这使得每个进位模块在获取到前一进位模块输出的级间进位参数时,每个进位模块中的多个进位计算单元即可以直接利用预处理结果和前一进位模块输出的级间进位参数并行计算对应的每个比特位的进位输出,由此基本上实现了并行计算16位二进制数据中每个比特位的进位输出。

76.如图6所示,第1个进位模块对应32比特的2组数据的第0比特位至第3比特位,所述第2个进位模块对应32比特的2组数据的第4比特位至第7比特位,所述第3个进位模块对应32比特的2组数据的第8比特位至15比特位,所述第4个进位模块对应32比特的2组数据的第16比特位至23比特位,所述第5个进位模块对应32比特的2组数据的第24比特位至31比特位。

77.此外,通过有规律地布置第一预处理单元、第二预处理单元、第三预处理单元、第四预处理单元、第一进位计算单元和第二进位计算单元,可以在提高用于实现基4 booth乘法器的32位加法器的计算速度的同时,减少用于实现基4 booth乘法器的32位加法器的占用面积,并且使得布线较为集中,有利于整体结构化布局。

78.需要指出的是,图6仅是用于说明本实施实施例提供的用于实现基4 booth乘法器的64位加法器中多路进位保存加法器的进位链的一种具体示例,根据实际需要,进位模块的数量可以为2个、4个、或者更多个,并且每个进位模块对应的具体比特位可以根据需要进行设置,本实施例对此不做限定。

79.实施例三

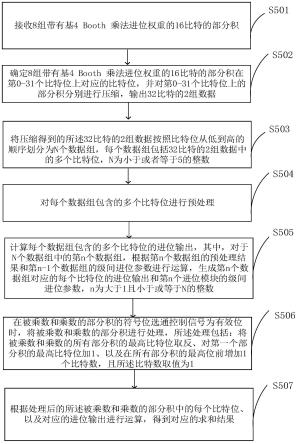

80.基于上述实施例提供的用于实现基4 booth乘法器的32位加法器,本技术实施例提供一种用于实现基4 booth乘法器的32位加法器的实现方法。图7为本技术实施例提供的一种用于实现基4 booth乘法器的32位加法器的实现方法的流程图。如图7所示,该用于实现基4 booth乘法器的32位加法器的实现方法包括:

81.s501、接收8组带有基4 booth乘法进位权重的16比特的部分积;所述部分积用于表征乘数的第i 1个比特位、第i个比特位和第i-1个比特位与被乘数基于基4 booth乘法的乘积;i为大于或等于0且小于或等于15的整数;

82.s502、确定8组带有基4 booth乘法进位权重的16比特的部分积在第0-31个比特位上对应的比特位,并对第0-31个比特位上的部分积分别进行压缩,输出32比特的2组数据;所述多路进位保存加法器在第0-31个比特位上用于压缩的进位保存加法器的数量为对应比特位上部分积的数量与符号位的数量之和减2;

83.s503、将压缩得到的所述32比特的2组数据按照比特位从低到高的顺序划分为n个数据组,每个数据组包括32比特的2组数据中的多个比特位,n为小于或者等于5的整数;其中,所述部分积用于表征乘数的第i 1个比特位、第i个比特位和第i-1个比特位与被乘数基于基4 booth乘法的乘积;i为大于或等于0且小于或等于15的整数;

84.s504、对每个数据组包含的多个比特位进行预处理;

85.s505、计算所述每个数据组包含的多个比特位的进位输出,其中,对于n个数据组中的第n个数据组,根据所述第n个数据组的预处理结果和第n-1个数据组的级间进位参数进行运算,生成所述第n个数据组对应的每个比特位的进位输出和所述第n个进位模块的级间进位参数,n为大于1且小于或等于n的整数;

86.s506、在32比特的2组数据的符号位选通控制信号为有效位时,将32比特的2组数据进行处理,所述处理包括:将被乘数和乘数的所有部分积的最高比特位取反、对第一个部分积的最高比特位加1、以及在所有部分积的最高位前增加1个比特数,且所述比特数取值为1;其中,符号位选通控制信号用于表征部分积为被乘数乘以负数倍;

87.s507、根据处理后的所述32比特的2组数据中的每个比特位、以及对应的进位输出进行运算,得到对应的求和结果。

88.本技术实施例提供的用于实现基4 booth乘法器的32位加法器的实现方法,用于实现前述装置实施例中的用于实现基4 booth乘法器的32位加法器,并具有相应的装置实施例的有益效果,此处不再赘述。

89.实施例四

90.本技术实施例提供了一种运算电路,该运算电路包括根据前述实施例一和二中任一项提供的用于实现基4 booth乘法器的32位加法器。其原理与效果类似,此处不再赘述。

91.实施例五

92.本技术实施例提供了一种芯片,该芯片包括根据前述实施例四提供的运算电路。其原理与效果类似,此处不再赘述。

93.本说明书中的各个实施例均采用递进的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的都是与其他实施例的不同之处。尤其,对于系统实施例而言,由于其基本相似于方法实施例,所以描述的比较简单,相关之处参见方法实施例的部分说明即可。

94.以上所述仅为本技术的实施例而已,并不用于限制本技术。对于本领域技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本技术的权利要求范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。