1.本发明涉及接收器、系统和接收器的操作方法。

背景技术:

2.包括射频识别(rfid)系统和具有高传输功率的蜂窝系统的无线电通信设备是已知的。如果rfid系统和蜂窝系统的频段相同,则从蜂窝系统接收传输信号的rfid系统的无线电段(radio section)通过传输信号驱动,使得杂散发射增加。因此,在无线电段的电源电路中设置谐振电路,该谐振电路将谐振频率改变为处于在接收蜂窝系统的传输信号时的频段之外(例如,参见专利文献1)。此外,已知具有交错式整流器或匹配设备的无线电功率接收器(例如,参见专利文献2和3)。

3.在rfid标签等中,存在通过天线接收到的无线电信号被转换为多种类型的功率以操作多种类型的内部电路的情况。然而,尚未提出针对天线输入功率来优化多种类型的功率中的每一种的功率效率的方法。例如,如果多种类型的功率的功率效率存在差异,则在功率效率低的一侧缩短能够接收功率以操作对应的内部电路的通信距离。

4.在一个方面中,本公开的目的是优化接收器中多种类型的功率中的每一种的功率效率,该接收器将通过天线接收到的无线电信号转换为多种类型的功率。

5.[相关技术文献]

[0006]

[专利文献]

[0007]

[专利文献1]日本特开第2015-39235号公报

[0008]

[专利文献2]国际专利申请的第2019-530395号日本国家公开

[0009]

[专利文献3]日本特开第2019-47205号公报

技术实现要素:

[0010]

根据实施例的一个方面,一种接收器包括:第一匹配电路,其被配置为根据天线接收到的无线电信号通过分支点(branch point)接收天线输入功率,并将接收到的天线输入功率的一部分作为第一输入功率输入到第一电路,该天线输入功率是从天线输入的,且该第一匹配电路的阻抗随着天线输入功率的增大而减小;以及第二匹配电路,其被配置为通过分支点接收天线输入功率并将接收到的天线输入功率的另一部分作为第二输入功率输入到第二电路,该第二匹配电路的阻抗随着天线输入功率的增大而增大。

[0011]

在一个方面中,根据本公开,可以优化接收器中的多种类型的功率中的每一种功率的功率效率,该接收器将通过天线接收到的无线电信号转换为多种类型的功率。

附图说明

[0012]

图1是示出根据实施例的包括接收器的系统的示例的框图;

[0013]

图2是示出图1中的接收器的阻抗特性和功率特性的示例的图;

[0014]

图3是示出根据另一实施例的包括接收器的系统的示例的框图;

[0015]

图4是示出图3中的rp2和rp3的功率特性和史密斯圆图的示例的图;

[0016]

图5是示出图3中的p2l和p3l的功率特性和功率效率以及z2l和z3l的史密斯圆图的示例的图;

[0017]

图6是示出图3中的z2、z3、z23和z1的史密斯圆图的示例的图;

[0018]

图7是示出包括另一个接收器的系统的示例的框图;

[0019]

图8是示出图7中的p2l和p3l的功率特性和功率效率以及z2l和z3l的史密斯圆图的图;

[0020]

图9是示出图7中的z2、z3、z23和z1的史密斯圆图的示例的图;

[0021]

图10是示出包括另一个接收器的系统的另一个示例的框图;

[0022]

图11是示出图10中的rp2和rp3的功率特性和史密斯圆图的示例的图;

[0023]

图12是示出图10中的p2l和p3l的功率特性和功率效率以及z2l和z3l的史密斯圆图的图;以及

[0024]

图13是示出图10中的z2、z3、z23和z1的史密斯圆图的示例的图。

具体实施方式

[0025]

下面将参考附图描述实施例。

[0026]

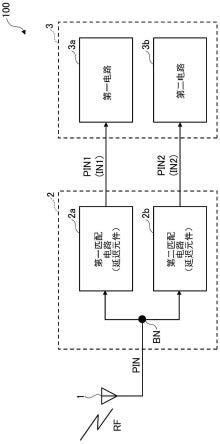

图1示出了根据实施例的包括接收器的系统的示例。图1中所示的系统100包括天线1、接收器2和电路部分3。电路部分3包括第一电路3a和第二电路3b,并且安装在例如大规模集成电路(lsi)上。天线1和接收器2通过引线连接,并且接收器2通过引线连接到第一电路3a和第二电路3b中的每一个。例如,接收器2和电路部分3安装到容纳在系统100的壳体中的布线板上。天线1可以并入布线板中或安装在布线板上。通过将天线1并入布线板中,可以减小系统100的尺寸。

[0027]

例如,系统100是射频识别(rfid)标签,但系统100不限于此。包括第一电路3a和第二电路3b的电路部分3被安装在用于rfid的lsi芯片上。

[0028]

天线1接收从rfid标签的读取器/写入器发送的高频无线电信号rf,并根据接收到的无线电信号rf向接收器2输出天线输入功率pin。接收器2包括并联连接的第一匹配电路2a和第二匹配电路2b,它们通过分支点bn与天线1连接。

[0029]

第一匹配电路2a包括延迟元件并且具有执行阻抗匹配的功能。第一匹配电路2a将通过分支点bn输入的天线输入功率pin的一部分作为第一输入功率pin1(第一高频输入信号in1)输入到第一电路3a。第一电路3a响应于接收到第一输入功率pin1而工作。第一匹配电路2a包括π型电路、t型电路或分布式元件电路,并且被设计为随着天线输入功率pin的增大而减小阻抗。

[0030]

第二匹配电路2b包括延迟元件并且具有执行阻抗匹配的功能。第二匹配电路2b将通过分支点bn输入的天线输入功率pin的另一部分作为第二输入功率pin2(第二高频输入信号in2)输入到第二电路3b。第二电路3b响应于接收到第二输入功率pin2而工作。第二匹配电路2b包括π型电路、t型电路或分布式元件电路,并且被设计为随着天线输入功率pin的增大而增大阻抗。

[0031]

第一匹配电路2a的延迟元件的延迟量与第二匹配电路2b的延迟元件的延迟量彼此不同。这允许第一输入信号in1和第二输入信号in2的相位彼此偏移。例如,第一匹配电路

2a的延迟元件的延迟量被设置为0

°

,且第二匹配电路2b的延迟元件的延迟量被设置为 90

°

或 45

°

。也就是说第二输入信号in2的相位相对于第一输入信号in1的相位被延迟了例如90

°

或45

°

。这里,延迟量由天线1接收到的无线电信号rf的相位来表示。例如,第一匹配电路2a和第二匹配电路2b的延迟元件的延迟量小于无线电信号rf的一个周期。

[0032]

第一匹配电路2a的延迟元件的延迟量可以被设置为0

°

,且第二匹配电路2b的延迟元件的延迟量可以被设置为-90

°

或-45

°

。另外,第一匹配电路2a的延迟元件的延迟量可以被设置为-45

°

,且第二匹配电路2b的延迟元件的延迟量可以被设置为 45

°

。此外,第一匹配电路2a的延迟元件的延迟量可以被设置为 45

°

,且第二匹配电路2b的延迟元件的延迟量可以被设置为-45

°

。

[0033]

第一匹配电路2a和第二匹配电路2b的延迟元件的延迟量被设置为考虑了天线1的阻抗以及第一电路3a侧和第二电路3b侧上的阻抗的频率特性而获得的预定通信特性的值。在这种情况下,可以在考虑第一匹配电路2a和第二匹配电路2b的简化的情况下,设置第一匹配电路2a和第二匹配电路2b的延迟元件的延迟量。

[0034]

图2示出了图1的接收器2的阻抗和功率特性的示例。即,图2示出了接收器2的操作方法的示例。如在图2的左侧的阻抗特性所示,从分支点bn向lsi看的第一匹配电路2a的阻抗与天线输入功率pin近似成反比。从分支点bn向lsi看的第二匹配电路2b的阻抗与天线输入功率pin近似成正比。即,第一匹配电路2a的阻抗随着天线输入功率pin的增大而减小,而第二匹配电路2b的阻抗随着天线输入功率pin的增大而增大。

[0035]

当天线输入功率pin较小时,第一匹配电路2a的阻抗为高,而第二匹配电路2b的阻抗为低,使得大部分天线输入功率pin作为第二输入功率pin2(pin1《pin2)被供应给第二电路3b。当天线输入功率pin较大时,第一匹配电路2a的阻抗为低,而第二匹配电路2b的阻抗为高,使得大部分天线输入功率pin作为第一输入功率pin1(pin1》pin2)被供应给第一电路3a。因此,如图2右侧所示,当天线输入功率pin超过功率值pinmin2时,第二输入功率pin2超过第二电路3b可以工作的最小功率pin2min,并且第二电路3b可以开始工作。此时,由于第一匹配电路2a的阻抗为高,并且第一输入功率pin1低于第二输入功率pin2,所以第一输入功率pin1未达到第一电路3a可以工作的最小功率pin1min。因此,第一电路3a不工作。因此,大部分天线输入功率pin可用于第二电路3b的操作以提高功率效率。

[0036]

当天线输入功率pin超过功率值pinminl时,第一输入功率pinl超过第一电路3a可以工作的最小功率pinlmin,且第一电路3a可以开始工作。此时,第二匹配电路2b的阻抗为高,并且第二输入功率pin2的增加已经达到峰值。因此,可以防止额外的第二输入功率pin2被供应给第二电路3b。因此,所需的最小第二输入功率pin2可以被供应给第二电路3b,而剩余的功率可以被用于第一电路3a的操作,以提升功率效率。

[0037]

如上所述,在本实施例中,根据天线输入功率pin输入的第一输入功率pinl和第二输入功率pin2可以接近理想的功率分配特性。使第一匹配电路2a和第二匹配电路2b的延迟元件的延迟量(相位)彼此不同,使得第一匹配电路2a的阻抗和第二匹配电路2b的阻抗相对于天线输入功率pin的变化特性可以相互反转(reverse)。

[0038]

即,第一匹配电路2a的阻抗可以随着天线输入功率pin的增大而减小,而第二匹配电路2b的阻抗可以随着天线输入功率pin的增大而增大。因此,如图2中所述,可以根据天线输入功率pin适当地设置供应给第一电路3a的第一输入功率pin1和供应给第二电路3b的第

二输入功率pin2。因此,可以根据接收器2中的天线输入功率pin的大小适当分配第一输入功率pin1和第二输入功率pin2,从而优化多种类型的功率中的每一种功率的功率效率,其中该接收器2将通过天线1接收的无线电信号rf转换为多种类型的功率。

[0039]

图3示出了在另一个实施例中包括接收器的系统的示例。对于与图1中的元件基本相同的元件,将省略详细描述。图3中所示的系统102包括天线10、接收器20、lsi 30和电子纸40。电子纸40是电子设备的示例。

[0040]

接收器20包括平衡不平衡变换器(balun,平衡-不平衡转换器)21和匹配电路22、23和24。lsi 30包括第一电路31和第二电路32。系统102例如是rfid无电池电子纸标签,但不限于此。lsi 30是用于rfid的lsi芯片。

[0041]

接收器20从天线10接收无线电信号rf作为不平衡信号。平衡不平衡变换器21被设置在天线10与匹配电路22之间,并且将从天线10接收到的不平衡信号转换为平衡信号并将平衡信号输出到匹配电路22。

[0042]

匹配电路22被设置在平衡不平衡变换器21与分支点bn 和bn-之间,以执行平衡不平衡变换器21与分支点bn 和bn-之间的阻抗匹配。例如,匹配电路22作为π型电路包括元件22a、22b、22c和22d。元件22a、22b、22c和22d中的至少一个包括延迟元件。

[0043]

匹配电路23被设置在分支点bn 和bn-与lsi 30的第一电路31之间,以执行分支点bn 和bn-与第一电路31之间的阻抗匹配。例如,匹配电路23作为π型电路包括元件23a、23b、23c和23d。元件23a、23b、23c和23d中的至少一个包括延迟元件。匹配电路23将通过匹配电路22接收到的天线输入功率的一部分作为第一输入功率输出到第一电路31。这里,元件23d中所示的x符号表示没有在本实施例中实施元件23d。在稍后将描述的图7和图10中,没有实施具有x符号的元件。

[0044]

匹配电路24被设置在分支点bn 和bn-与lsi 30的第二电路32之间,以执行分支点bn 和bn-与第二电路32之间的阻抗匹配。例如,匹配电路24作为π型电路包括元件24a、24b、24c和24d。元件24a、24b、24c和24d中的至少一个包括延迟元件。匹配电路24将通过匹配电路22接收到的天线输入功率的另一部分作为第二输入功率输出到第二电路32。图3中所示的符号p(pb、p1、p23、p2、p3、p2l和p3l)表示功率。图3中所示的符号z(zb、z1、z23、z2、z3、z2l和z3l)表示朝向箭头的方向看的阻抗,将参考图4至图6对其进行描述。将参考图5和图6描述功率p2l和p3l以及阻抗z1、z23、z2、z3、z2l和z3l。

[0045]

这里,图3中所示的匹配电路22、23和24中的元件是示例,并且可以添加或删除元件。匹配电路22、23、24可以包括t型电路(其包括延迟元件)或分布式元件电路(其包括延迟元件)来代替π型电路。匹配电路22是第三匹配电路的示例。匹配电路23是第一匹配电路的示例。匹配电路24是第二匹配电路的示例。

[0046]

第一电路31包括电源电压生成电路psl,其根据从匹配电路23接收到的第一输入功率(p2l)生成使电子纸40工作的第一电源电压。第一电路31被表示为包括输入电容器cp2和输入电阻器rp2的等效电路。第二电路32包括电源电压生成电路ps2、通信电路rf-com、逻辑电路lg和fram(注册商标)。第二电路32被表示为包括输入电容器cp3和输入电阻器rp3的等效电路。

[0047]

fram是电可重写非易失性存储器的示例。电源电压生成电路ps2根据从匹配电路24接收到的第二输入功率(p3l)生成使通信电路rf-com、逻辑电路lg和fram工作的第二电

源电压。如果通信电路rf-com、逻辑电路lg和fram中使用的第二电源电压的类型不同,则电源电压生成电路ps2可以具有生成多种类型的第二电源电压的功能。

[0048]

通信电路rf-com执行通过天线10接收无线电信号rf的接收过程和从天线10发送无线电信号rf的发送过程。通信电路rf-com传送包括在由天线10接收到的无线电信号rf中的信息并且是提取要显示在电子纸40上的显示信息的提取器的示例。

[0049]

逻辑电路lg将从通信电路rf-com接收到的显示信息写入fram。逻辑电路lg生成控制信号以操作电子纸40,从fram读取要显示在电子纸40上的显示信息,并将控制信号和显示信息输出到电子纸40。另外,逻辑电路电路lg将要从天线10发送的发送信息输出到通信电路rf-com。逻辑电路lg是控制电路的示例。

[0050]

电子纸40响应于从电源电压生成电路ps1接收到第一电源电压而工作,并且根据从逻辑电路lg接收到的控制信号来执行重写电子纸40的显示的操作。

[0051]

通信电路rf-com、逻辑电路lg和fram能够工作的第二电源电压的最小值低于电子纸40能够工作的第一电源电压的最小值。因此,即使rfid标签与读取器/写入器的距离较大,天线输入功率较低,而且无法生成电子纸40的重写操作所需的第一电源电压,但是通过使第二电路32工作,可以从读取器/写入器读取rfid标签的电子产品代码(epc),并且可以从长距离标识附着有rfid标签的物品。

[0052]

这里,系统102可以包括另一个电子设备而不是电子纸40。在这种情况下,lsi 30从第一电路31输出使电子设备工作的第一电源电压并从第二电路32输出控制电子设备的操作的控制信号。

[0053]

图4至图6示出了图3的接收器20和lsi 30的电特性的示例。在下文中,例如,无线电信号rf的频率是920mhz,重写电子纸40的显示的重写操作可以被执行的最小功率是 20dbm,且第二电路32(通信电路rf-com、逻辑电路lg和fram)可以工作的最小功率是-20dbm。

[0054]

例如,lsi 30的第一电路31的输入电容器cp2被设置为3pf,且lsi 30的第二电路32的输入电容器cp3被设置为1pf。由于第一电路31的输入电阻器rp2和第二电路32的输入电阻器rp3依赖于功率,所以在图4中示出相应的功率特性。

[0055]

匹配电路22的电路常数对于元件22a是7.5nh,对于元件22b和22c是1.4nh,且对于元件22d是3.3pf。这实现了天线10和平衡不平衡变换器21侧的50ω与分支点bn 和bn-侧的100ω之间的匹配,以及13.4

°

的延迟。

[0056]

匹配电路23的电路常数对于元件23a是10nh,对于元件23b和23c是0ω,并且没有实施元件23d。这实现了分支点bn 和bn-侧的100ω与第一电路31侧的100ω//3pf(cp2)之间的匹配,以及0

°

的延迟。

[0057]

匹配电路24的电路常数对于元件24a是100nh,对于元件24b和24c是0.6pf,且对于元件24d是23nh。这实现了分支点bn 和bn-侧的100ω与第二电路32侧的3.5kω//1pf(cp3)之间的匹配,以及-90

°

的延迟。

[0058]

图4示出了图3的输入电阻器rp2和rp3的功率特性和史密斯圆图的示例。输入电阻器rp2和rp3由于它们的不同应用在功率依赖性方面彼此不同并且史密斯圆图彼此不同。

[0059]

图5是示出图3中的p2l和p3l的功率特性和功率效率以及z2l和z3l的史密斯圆图的示例的图。即,图5示出了接收器20的操作方法的示例。如z2l的史密斯圆图所示,由于输

入电容器cp2,阻抗z2l具有向下倾斜的特性。如z3l的史密斯圆图所示,在应用上与阻抗z2l不同的阻抗z3l在特性上也与阻抗z2l不同。

[0060]

在作为电子纸40的工作功率的功率p2l的功率特性中,可以在功率pm≥ 20dbm(即功率p2l≥ 20dbm)下执行电子纸40的重写操作,并且电子纸40的重写操作大约可在理论限制值下工作。在此,功率pm为天线10的最大可用功率(最佳匹配条件下可供应的最大功率)。

[0061]

在作为第二电路32的工作功率的功率p3l的功率特性中,第二电路32的逻辑电路lg等以功率pm≥-20dbm(即功率p3l≥-20dbm)被使能,并且大约可在理论限制值下工作。

[0062]

这允许功率p2l的功率效率在第二电路32的逻辑电路lg等开始工作的功率p3l=-20dbm附近为0%,如p2l和p3l的功率效率所示。因此,几乎所有的天线输入功率都可以用于操作第二电路32的逻辑电路lg等。

[0063]

此外,这允许功率p3l的功率效率在电子纸40开始工作的功率p2l= 20dbm附近为5%或更小。因此,大部分天线输入功率可以用于操作电子纸40,并且可以防止将不必要的功率p3l供应给第二电路32的逻辑电路lg等。因此,可以针对多个功率状态(电子纸40的重写操作的 20dbm和第二电路32的-20dbm)中的每一个优化功率效率。

[0064]

这里,通过部分地集成图3的匹配电路22、23和24,可以减少匹配电路的元件数量,并且可以减小接收器20的电路尺寸。因此,可以通过减少组件的数量来提高系统102的可靠性,并且可以降低系统102的成本。

[0065]

例如,可以不实施匹配电路22的元件22d、匹配电路23的元件23a和匹配电路24的元件24a。这是因为元件22d(3.3pf, 19.08ms)、元件23a(100nh,-j1.73 ms)和元件24a(10nh,-j17.30 ms)的组合并联导纳为 j0.05ms(约为0),并且几乎没有改变特性。

[0066]

图6示出了图3的z2、z3、z23和zl的史密斯圆图的示例。如z2的史密斯圆图所示,阻抗z2被调整为在 20dbm下匹配100ω并且随着功率减小而具有更大的阻抗。这里,匹配100ω而不是匹配50ω的原因是为了简化匹配电路23的电路。

[0067]

如z3的史密斯圆图所示,由于-90

°

的延迟,阻抗z3通过阻抗匹配而被调整为在-20dbm下匹配到100ω并且随着功率的增大而具有更大的阻抗。

[0068]

如z23的史密斯圆图所示,阻抗z23被调整为在 20dbm和-20dbm下匹配100ω。如z1的史密斯圆图所示,阻抗z1被调整为在 20dbm和-20dbm下匹配50ω,即天线10侧的阻抗。

[0069]

如上所述,在本实施例中,可以获得与上述实施例基本相同的效果。例如,可以使根据天线输入功率的功率p2l和p3l达到理想的功率分配特性。通过允许匹配电路23和24的延迟元件的延迟量(相位)彼此不同,阻抗z2l和z3l相对于天线输入功率的变化的特性可以彼此反转地设置。即,阻抗z2l可以随着天线输入功率增大而减小,且阻抗z3l可以随着天线输入功率增大而增大。

[0070]

因此,如图5中所述,可以根据天线输入功率适当地设置供应给第一电路31的功率p2l和供应给第二电路32的功率p3l。因此,在将通过天线10接收到的无线电信号rf转换成多种类型的功率的接收器20中,可以根据天线输入功率的幅度来适当地分配功率p2l和p3l,从而针对多种类型的功率中的每一种来优化功率效率。

[0071]

与常规方法相比,用于获得使匹配电路23工作的功率p2l的最小功率( 20dbm)的最大可用功率pm可以被降低。因此,例如,如果系统102(rfid标签)被附着到货架或物品,则通过读取epc来标识物品的读取器/写入器与系统102之间的距离可以变得更长(例如,比常

规方法长三到十倍)。

[0072]

因此,可以增加向读取器/写入器发送信息的系统102的数量。这里,系统102可以包括另一个电子设备而不是电子纸40。

[0073]

图7示出了包括另一个接收器的系统的示例。与图3中相同的元件由相同的附图标记表示并且省略详细描述。图7中所示的系统104包括天线10、接收器20a、lsi 30和电子纸40。接收器20a具有与图3中的接收器20的配置基本相同的配置,不同之处在于包括匹配电路24a而不是图3中的接收器20的匹配电路24。在匹配电路24a中,没有实施元件24a和24d并且元件24b和24c被设置为16pf。

[0074]

图8和图9示出了图7中的接收器20a的电特性的示例。如在上述实施例中,无线电信号rf的频率是920mhz,电子纸40的重写操作可以被执行的最小功率是 20dbm,且第二电路32(通信电路rf-com、逻辑电路lg和fram)可以工作的最小功率是-20dbm。

[0075]

如图3所示,图7中第一电路31的输入电容器cp2被设置为3pf,且第二电路32的输入电容器cp3被设置为1pf。输入电阻器rp2和rp3具有功率依赖性,与图3中的输入电阻器rp2和rp3一样。因此,输入电阻器rp2和rp3的功率特性和史密斯圆图与图4中的相同。

[0076]

匹配电路22的电路常数与上述实施例基本相同,并且电路常数对于元件22a为7.5nh,对于元件22b和22c为1.4nh,且对于元件22d为3.3pf。这实现了天线10和平衡不平衡变换器21侧的50ω与分支点bn 和bn-侧的97-j17ω之间的匹配,以及13.4

°

的延迟。

[0077]

如在上述实施例中一样,匹配电路23的电路常数对于元件23a是10nh,对于元件23b和23c是0ω,且没有实施元件23d。这实现了分支点bn 和bn-侧的100ω与第一电路31侧的100ω//3pf(cp2)之间的匹配,以及0

°

的延迟。匹配电路24的电路常数对于元件24b和24c是1pf,并且没有实施元件24a和24d。这减小了第二电路32侧的耦合量。

[0078]

图8示出了图7中的p2l和p3l的功率特性和功率效率以及z2l和z3l的史密斯圆图的示例。z2l和z3l的史密斯圆图与图6中的相同。功率p2l的功率特性与图5中的基本相同,因此电子纸40的重写操作可以在功率pm≥ 20dbm(即功率p2l≥ 20dbm)下执行,并且可在理论限制值下工作。

[0079]

综上所述,第二电路32的逻辑电路lg等的操作在pm≥0dbm(即,p3l≥-20dbm)下被使能。因此,最大可用功率pm相对于理论限制降低了近20db。因此,在图7的系统104中,为了使第二电路32的逻辑电路lg等工作,需要比图3的系统102的天线输入功率大的天线输入功率。因此,通过读取epc来标识物品的读取器/写入器与系统104之间的距离变得比上述实施例的距离短了(例如,三分之一至十分之一)。

[0080]

图9示出了图7中z2、z3、z23和zl的史密斯圆图的示例。z2的史密斯圆图与图6中的相同。如z3的史密斯圆图所示,无论功率如何,阻抗z3被调整为高的阻抗,以减小耦合量。

[0081]

如z23的史密斯圆图所示,阻抗z23在 20dbm下被调整为大约100ω。如z1的史密斯圆图所示,阻抗z1被调整为在 20dbm下匹配50ω,即,天线10侧的阻抗。

[0082]

图10示出了包括另一个接收器的系统的另一个示例。与图3中相同的元件由相同的附图标记表示并且省略详细描述。图10中所示的系统106包括天线10、接收器20b、lsi 30b和电子纸40。接收器20b具有与图3中的接收器20的配置基本相同的配置,不同之处在于包括匹配电路22b和24b而不是图3中的匹配电路22和24。

[0083]

lsi 30b具有与图3中的lsi 30的配置基本相同的配置,不同之处在于包括第二电

路32b而不是图3中的第二电路32。第二电路32b具有与图3中的第二电路32的配置基本相同的配置,不同之处在于输入电容器cp3与图3中的输入电容器cp3不同。

[0084]

图11至图13示出了图10的接收器20b的电特性的示例。在下文中,例如,无线电信号rf的频率是920mhz,重写电子纸40的显示的重写操作可以被执行的最小功率是 20dbm,且第二电路32(通信电路rf-com、逻辑电路lg和fram)可以工作的最小功率是-20dbm。

[0085]

例如,lsi 30b的第一电路31的输入电容器cp2被设置为3pf,且lsi30b的第二电路32b的输入电容器cp3被设置为3pf。电源电压生成电路ps1和电源电压生成电路ps2具有相同的特性。第一电路31的输入电阻器rp2和第二电路32的输入电阻器rp3依赖于功率并且彼此相同。输入电阻器rp2和rp3的功率特性如图11所示。

[0086]

匹配电路22b的电路常数对于元件24b和24c是0ω,并且没有实施元件22a和22d。这实现了天线10和平衡不平衡变换器21侧的50ω与分支点bn 和bn-侧的50ω之间的匹配,以及0

°

的延迟。

[0087]

匹配电路23的电路常数与图3中的匹配电路23的电路常数基本相同,且对于元件23a为10nh,对于元件23b和23c为0ω,并且没有实施元件23d。这实现了分支点bn 和bn-侧的100ω与第一电路31侧的100ω//3pf(cp2)之间的匹配,以及0

°

的延迟。

[0088]

匹配电路23和匹配电路24b除了延迟之外具有相同的特性,仅将100ω转换为100ω,并且除了抵消输入电容器cp2和输入电容器cp3的导纳之外基本上没有匹配功能。

[0089]

图11示出了图10中的输入电阻器rp2和rp3的功率特性和史密斯圆图的示例。输入电阻器rp2和rp3的功率特性彼此相同,并且输入电阻器rp2和rp3的史密斯圆图彼此相同。

[0090]

图12示出了图10中的p2l和p3l的功率特性和功率效率和z2l和z3l的史密斯圆图的示例。在作为电子纸40的工作功率的功率p2l的功率特性中,电子纸40的重写操作可以在功率pm≥ 30dbm(即,功率p2l≥ 20dbm)下执行。在作为第二电路32b的工作功率的功率p3l的功率特性中,第二电路32b的逻辑电路lg等可以在功率pm≥-15dbm(即,功率p3l≥-20dbm)下被执行。如p2l和p3l的功率效率所示,最佳功率效率被限制为特定功率条件(在此示例中,约为0dbm)。这里,如z2l和z3l的史密斯圆图所示,阻抗z2l和阻抗z3l具有相同的特性。

[0091]

图13示出了图10中z2、z3、z23和zl的史密斯圆图的示例。如z2的史密斯圆图所示,当功率p2l为-3dbm时(当p2l和p3l组合时为0dbm),阻抗z2被调整为匹配100ω,并且随着功率减小,阻抗变大。

[0092]

如z3的史密斯圆图所示,当功率p3l为-3dbm时(当p2l和p3l组合时为0dbm),阻抗z3被调整为匹配100ω,并且随着功率增大,阻抗变大。z23和z1的史密斯圆图彼此相同,且阻抗z23和阻抗z1被调整为在 0dbm下匹配50ω(2个100ω并联)。

[0093]

以上详细描述使实施例的特征和优点变得清楚。在不脱离本发明的精神和范围的情况下,权利要求旨在包括这些实施例的特征和优点。此外,本领域普通技术人员可以很容易地进行任何改进和修改。因此,并不旨在将发明实施例的范围限制为上述实施例,而是可以基于包括在实施例中公开的范围内的适当修改和等同物。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。