一种实现双bmc切换升级的系统、方法

技术领域

1.本发明涉及服务器升级管理技术领域,具体提供一种实现双bmc切换升级的系统、方法。

背景技术:

2.伴随云计算应用的发展,信息化逐渐覆盖到社会的各个领域。所需要的服务器的算力能力也越来越强,越来越多的企业需要用服务器来做机器学习,对ai程序进行训练。这里就要用到一种专业的计算模块,因此也就出现了ai服务器,而ai服务器普遍采用cpu gpu的异构架构,这种异构服务器,为了实现灵活组网和灵活管理,通常会采用双bmc架构,来实现对异构服务器的灵活配置管理。

3.异构服务器中需要升级管理的器件也比以前单cpu的形态多了很多,如果采用在s0状态下升级,会在无形中增加很多时间成本和物质成本,因此如果异构服务器能在s5状态下升级会节约很多时间。

4.当使用mctp(management component transport protocol,管理组件传输协议)时,从bmc也要求支持mctp组件管理协议,这种情况下,从bmc的pcie rc端口的就绪时间也由从bmc的ep端口就绪时间来决定,而主bmc的pcie ep端口即vga的就绪时间是s0(正常工作状态)状态下才会就绪,即整个异构服务器pcie通道的生效时间通常在s0状态下即整个设备完全上电后才会生效。这种情况下就导致按照现有的拓扑,在s5(关机状态)状态下,主bmc到从bmc的pcie通路是不通的,只能通过i2c慢速通路升级,而要给gpu模块通过pcie高速通路实现快速升级,只能在整个设备上电后即s0状态下才可以通过pcie高速通路给其升级。这样不仅对整个异构服务器升级有了时间成本上的约束,在s0成本下需要整个服务器运行也无形中增加了电费成本和人员管理成本。

技术实现要素:

5.针对在s5状态下,主bmc到从bmc的pcie通路是不通的,只能通过i2c慢速通路升级,而要给gpu模块通过pcie高速通路实现快速升级,只能在整个设备上电后即s0状态下才可以通过pcie高速通路给其升级。这样不仅对整个异构服务器升级有了时间成本上的约束,在s0成本下需要整个服务器运行也无形中增加了电费成本和人员管理成本的问题,本发明提供一种实现双bmc切换升级的系统、方法。

6.本发明的技术方案是:

7.第一方面,本发明技术方案提供一种实现双bmc切换升级的系统,包括主板和io切换板;

8.主板上设有主bmc,io切换板上设有从bmc、通路选择芯片;

9.通路选择芯片连接有网络接口,通路选择芯片分别通过一个phy芯片与主bmc和从bmc连接;

10.从bmc与通路选择芯片连接;用于控制通路选择芯片的通路选择;

11.从bmc用于连接待升级模块。

12.主bmc判断需从bmc进行管理升级时,判断系统当前状态;当系统当前为s5状态时,主bmc通过i2c发送控制指令到从bmc,从bmc接收到控制指令后控制通路选择芯片动作使网络接口与从bmc通信;从bmc对待升级模块进行管理升级;从bmc在升级完成后,控制通路选择芯片动作使网络接口与主bmc通信。通路选择芯片由主bmc通过i2c和heart beat来选择网络控制权归属主bmc还是从bmc,这样当gpu需要在s5状态下进行管理和升级时,可以通过主bmc将网络控制权切换到从bmc,即可完成从bmc的管理升级通路的切换。

13.优选地,主bmc内部和从bmc内部均设有ep控制器和rc控制器;ep控制器连接有ep端口,rc控制器连接有rc端口;

14.主bmc的ep端口连接有vga模块;

15.从bmc的rc端口与待升级模块连接。

16.优选地,系统s0状态时,从bmc进行管理升级的过程如下:

17.通路选择芯片与主bmc连接的phy芯片通信连接,网络接口与主bmc通信连接,主bmc的rc端口和从bmc的ep端口通信;通过从bmc的rc端口给待升级模块进行管理升级;

18.或,主bmc通过i2c发送控制指令到从bmc,从bmc接收到控制指令后,发送切换控制信号到通路选择芯片,通路选择芯片动作使网络接口与从bmc通信连接,通过从bmc的rc端口给待升级模块进行管理升级。

19.优选地,系统s5状态时,从bmc进行管理升级的过程如下:

20.主bmc通过i2c发送控制指令到从bmc,从bmc接收到控制指令后,发送切换控制信号到通路选择芯片,通路选择芯片动作使网络接口与从bmc通信连接,通过从bmc的rc端口给待升级模块进行管理升级。通过主bmc将网络控制权切换到从bmc,即可完成从bmc的管理升级通路的切换,解决了在s5状态下主bmc不能通过pcie通路进行管理升级待升级模块的问题。

21.从bmc内设有寄存器,主bmc通过i2c与从bmc的寄存器通信,主bmc通过i2c发送控制指令到从bmc,将从bmc寄存器的bit0数据位写状态1,同时,发送一个心跳信号给从bmc;从bmc接收到心跳信号后,到对应的寄存器读取对应数据位的状态值;从bmc判断寄存器的bit0数据位的状态值是否为1;若是,返回主bmc一个心跳信号,从bmc根据接收到的指令输出切换控制信号给通路选择芯片,通路选择芯片动作使网络接口与从bmc通信,同时从bmc将对应的寄存器的bit1数据位写状态1,代表切换已执行。

22.从bmc在升级完成后将自己的寄存器的bit0数据位更改回初始状态0,并发送一个心跳信号给主bmc;主bmc接收心跳信号到之后,查看从bmc的寄存器bit0数据位的状态值;若寄存器bit0数据位的状态值为0,则将从bmc的寄存器的bit 1数据位改回0,同时发送一个心跳信号给从bmc,代表控制权已经拿回。

23.主bmc和从bmc出到机框上的网络接口,通过通路选择芯片来切换。当s5状态下需要升级delta-gpu时,切换到从bmc即可。两个bmc之间网络接口的控制权的选择,由主bmc发出i2c指令和heart beat来选择。通路选择芯片的选择信号由从bmc来控制,但是控制信号的命令是由主bmc的i2c传输命令来决定的。heart beat信号每一次操作,必须主bmc和从bmc各发送一次代表操作完成,并确认过状态ok。heart beat信号每一次操作,主bmc和从bmc各发送一次代表操作完成的信号时间间隔不能超过100ms,防止误操作。

24.第二方面,本发明技术方案提供一种实现双bmc切换升级的方法,应用于第一方面所述的实现双bmc切换升级的系统,所述方法包括如下步骤:

25.主bmc判断需从bmc进行管理升级时,判断系统当前状态;

26.当系统当前为s5状态时,主bmc通过i2c发送控制指令到从bmc,从bmc接收到控制指令后控制通路选择芯片动作使网络接口与从bmc通信;

27.从bmc对待升级模块进行管理升级;

28.从bmc在升级完成后,控制通路选择芯片动作使网络接口与主bmc通信。

29.通过主bmc将网络控制权切换到从bmc,即可完成从bmc的管理升级通路的切换,解决了在s5状态下主bmc不能通过pcie通路进行管理升级待升级模块的问题。

30.优选地,主bmc判断需从bmc进行管理升级时,判断系统当前状态的步骤之后还包括:

31.当系统当前为s0状态时,执行步骤:主bmc通过i2c发送控制指令到从bmc,从bmc接收到控制指令后控制通路选择芯片动作使网络接口与从bmc通信;

32.或,直接主bmc的rc端口和从bmc的ep端口通信,通过从bmc的rc端口给待升级模块进行管理升级。

33.优选地,主bmc通过i2c发送控制指令到从bmc,从bmc接收到控制指令后控制通路选择芯片动作使网络接口与从bmc通信的步骤包括:

34.主bmc通过i2c发送控制指令到从bmc,将从bmc寄存器的bit0数据位写状态1,同时,发送一个心跳信号给从bmc;

35.从bmc接收到心跳信号后,到对应的寄存器读取对应数据位的状态值;

36.从bmc根据接收到的指令输出切换控制信号给通路选择芯片,通路选择芯片动作使网络接口与从bmc通信。

37.优选地,从bmc根据接收到的指令输出切换控制信号给通路选择芯片,通路选择芯片动作使网络接口与从bmc通信的步骤之后还包括:

38.从bmc将对应的寄存器的bit1数据位写状态1,代表切换已执行。

39.优选地,从bmc根据接收到的指令输出切换控制信号给通路选择芯片,通路选择芯片动作使网络接口与从bmc通信的步骤包括:

40.从bmc判断寄存器的bit0数据位的状态值是否为1;

41.若是,返回主bmc一个心跳信号,从bmc根据接收到的指令输出切换控制信号给通路选择芯片,通路选择芯片动作使网络接口与从bmc通信;

42.若否,设定时间间隔后,执行步骤:主bmc通过i2c发送控制指令到从bmc,将从bmc寄存器的bit0数据位写状态1,同时,发送一个心跳信号给从bmc。

43.优选地,从bmc在升级完成后,控制通路选择芯片动作使网络接口与主bmc通信的步骤包括:

44.从bmc在升级完成后将自己的寄存器的bit0数据位更改回初始状态0,并发送一个心跳信号给主bmc;

45.主bmc接收心跳信号到之后,查看从bmc的寄存器bit0数据位的状态值;

46.若寄存器bit0数据位的状态值为0,则将从bmc的寄存器的bit 1数据位改回0,同时发送一个心跳信号给从bmc,代表控制权已经拿回。

47.主bmc和从bmc出到机框上的网络接口,通过通路选择芯片来切换。当s5状态下需要升级delta-gpu时,切换到从bmc即可。两个bmc之间网络接口的控制权的选择,由主bmc发出i2c指令和heart beat来选择。通路选择芯片的选择信号由从bmc来控制,但是控制信号的命令是由主bmc的i2c传输命令来决定的。heart beat信号每一次操作,必须主bmc和从bmc各发送一次代表操作完成,并确认过状态ok。heart beat信号每一次操作,主bmc和从bmc各发送一次代表操作完成的信号时间间隔不能超过100ms,防止误操作。

48.从以上技术方案可以看出,本发明具有以下优点:通路选择芯片由主bmc通过i2c和心跳信号来选择网络控制权归属主bmc还是从bmc,这样当待升级模块需要在s5状态下进行管理和升级时,可以通过主bmc将网络控制权切换到从bmc,即可完成从bmc的管理升级通路的切换,解决了在s5状态下主bmc不能通过pcie通路进行管理升级待升级模块的问题。

49.此外,本发明设计原理可靠,结构简单,具有非常广泛的应用前景。

50.由此可见,本发明与现有技术相比,具有突出的实质性特点和显著地进步,其实施的有益效果也是显而易见的。

附图说明

51.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,对于本领域普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

52.图1是本发明一个实施例的实现s5状态下的双bmc切换升级的系统的示意性框图。

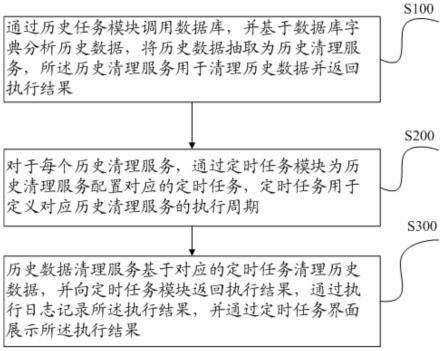

53.图2是本发明一个实施例的方法的示意性流程图。

54.图3是本发明另一个实施例的方法的示意性流程图。

具体实施方式

55.现有的异构服务器的机头是采用intel x86架构,bmc使用的是ast2600,所有的pcie设备要求支持mctp协议,由mb主板上的bmc ast2600的pcie接口rc端口,通过io switch板上的bmc pcie ep端口通路给nvidia delta模块进行管理升级。根据ast2600的手册,因为当使用mctp组件管理协议时,bmc的ep控制器和rc控制器的复位是同一个。所以mb主板的pcie rc通路的复位时间是由ep端口的复位时间来决定的,而从bmc的ep接口通路跟主bmc的pcie rc通路相连,且从bmc也要求支持mctp组件管理协议,这种情况下,从bmc的pcie rc端口的就绪时间也由从bmc的ep端口就绪时间来决定,而主bmc的pcie ep端口即vga的就绪时间是s0状态下才会就绪,即整个异构服务器pcie通道的生效时间通常在s0状态下即整个设备完全上电后才会生效。这种情况下就导致按照现有的拓扑,在s5状态下,mb主板上的bmc到io switch板上的bmc的pcie通路是不通的,只能通过i2c慢速通路升级,而要给nvidia delta next gpu模块通过pcie高速通路实现快速升级,只能在整个设备上电后即s0状态下才可以通过pcie高速通路给其升级。这样不仅对整个异构服务器升级有了时间成本上的约束,在s0成本下需要整个服务器运行也无形中增加了电费成本和人员管理成本。为了使本技术领域的人员更好地理解本发明中的技术方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术

人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本发明保护的范围。

56.如图1所示,本发明实施例提供一种实现双bmc切换升级的系统,包括主板和io切换板;

57.主板上设有主bmc,io切换板上设有从bmc、通路选择芯片;

58.通路选择芯片连接有网络接口,通路选择芯片分别通过一个phy芯片与主bmc和从bmc连接;

59.从bmc与通路选择芯片连接;用于控制通路选择芯片的通路选择;

60.从bmc用于连接待升级模块。

61.主bmc判断需从bmc进行管理升级时,判断系统当前状态;当系统当前为s5状态时,主bmc通过i2c发送控制指令到从bmc,从bmc接收到控制指令后控制通路选择芯片动作使网络接口与从bmc通信;从bmc对待升级模块进行管理升级;从bmc在升级完成后,控制通路选择芯片动作使网络接口与主bmc通信。

62.需要说明的是,主bmc内部和从bmc内部均设有ep控制器和rc控制器;ep控制器连接有ep端口,rc控制器连接有rc端口;

63.主bmc的ep端口连接有vga模块;

64.从bmc的rc端口与待升级模块连接。

65.系统s0状态时,从bmc进行管理升级的过程如下:

66.通路选择芯片与主bmc连接的phy芯片通信连接,网络接口与主bmc通信连接,主bmc的rc端口和从bmc的ep端口通信;通过从bmc的rc端口给待升级模块进行管理升级;

67.或,主bmc通过i2c发送控制指令到从bmc,从bmc接收到控制指令后,发送切换控制信号到通路选择芯片,通路选择芯片动作使网络接口与从bmc通信连接,通过从bmc的rc端口给待升级模块进行管理升级。

68.也就是说,so状态下有升级需求网络接口rj45来自主bmc,当然主bmc也可以发指令更改从bmc寄存器状态值,并发送心跳信号给从bmc通知从bmc去升级也可以,s0状态下如果主bmc的pcie通路出了问题,也可以选择这种方式把网络接口rj45控制权交给从bmc,让其实现快速通路升级。

69.系统s5状态时,从bmc进行管理升级的过程如下:

70.主bmc通过i2c发送控制指令到从bmc,从bmc接收到控制指令后,发送切换控制信号到通路选择芯片,通路选择芯片动作使网络接口与从bmc通信连接,通过从bmc的rc端口给待升级模块进行管理升级。

71.从bmc内设有寄存器,主bmc通过i2c与从bmc的寄存器通信,主bmc通过i2c发送控制指令到从bmc,将从bmc寄存器的bit0数据位写状态1,同时,发送一个心跳信号给从bmc;从bmc接收到心跳信号后,到对应的寄存器读取对应数据位的状态值;从bmc判断寄存器的bit0数据位的状态值是否为1;若是,返回主bmc一个心跳信号,从bmc根据接收到的指令输出切换控制信号给通路选择芯片,通路选择芯片动作使网络接口与从bmc通信,同时从bmc将对应的寄存器的bit1数据位写状态1,代表切换已执行。

72.从bmc在升级完成后将自己的寄存器的bit0数据位更改回初始状态0,并发送一个心跳信号给主bmc;主bmc接收心跳信号到之后,查看从bmc的寄存器bit0数据位的状态值;

若寄存器bit0数据位的状态值为0,则将从bmc的寄存器的bit 1数据位改回0,同时发送一个心跳信号给从bmc,代表控制权已经拿回。

73.下面以待升级模块是nvidia的delta next gpu模块为例进行说明如下:

74.通过通路选择芯片直接切换升级bmc的选择,当需要升级nvidia的delta-gpu模块时,直接将rj45切换到从bmc上的接口,这样pcie升级管理通路不再依赖于主bmc的pcie通路,从bmc的pcie通路的就绪时间仅由io切换板自己的时钟模块来决定。这样我们就可以通过通路选择芯片切换rj45的方式实现在s5状态下,通过pcie通路对delta-gpu模块进行快速管理升级。通路选择芯片的选择信号由主从bmc之间的i2c通路来控制,主bmc在发送控制指令到从bmc,将从bmc的寄存器的bit0数据块的状态写1,同时,发送一个heart beat(心跳)信号给从bmc,从bmc接收到heart beat信号之后,到对应的寄存器读取指令,确认寄存器bit0状态是否为1,若是,则返回主bmc一个heart beat代表寄存器check ok信号,两个heart beat的确认时间不能超过100ms,以防跟下一个状态切换确认有冲突,从bmc根据主bmc的i2c发过来的指令,输出切换控制信号给通路选择芯片,并同时将自身的寄存器的bit1数据位填写状态1,代表切换已执行。网络控制权归属从bmc。从bmc在升级完成后,需将网络控制权交还给主bmc,即需要从bmc将自己的内部寄存器bit0更改回初始状态0,并发送一个heart beat给主bmc,主bmc接收到之后,查看从bmc的寄存器的bit0是否更改回0,如果已更改,则将从bmc的寄存器的bit 1改回0,代表网络控制权已拿回,归属主bmc,同时发送一个heart beat给从bmc代表控制权已经拿回。

75.需要说明的是,主bmc和从bmc出到机框上的网络接口,通过通路选择芯片来切换。当s5状态下需要升级delta-gpu时,切换到从bmc即可。两个bmc之间网络接口的控制权的选择,由主bmc发出i2c指令和heart beat来选择。通路选择芯片的选择信号由从bmc来控制,但是控制信号的命令是由主bmc的i2c传输命令来决定的。heart beat信号每一次操作,必须主bmc和从bmc各发送一次代表操作完成,并确认过状态ok。heart beat信号每一次操作,主bmc和从bmc各发送一次代表操作完成的信号时间间隔不能超过100ms,防止误操作。本发明实施例中的通路选择芯片可以选择两路的mux芯片来完成。

76.mb主板的pcie rc通路的复位时间是由ep端口的复位时间来决定的,而从bmc的ep接口通路跟主bmc的pcie rc通路相连,且从bmc也要求支持mctp组件管理协议,这种情况下,从bmc的pcie rc端口的就绪时间也由从bmc的ep端口就绪时间来决定,而主bmc的pcie ep端口即vga的就绪时间是s0状态下才会就绪,即整个异构服务器pcie通道的生效时间通常在s0状态下即整个设备完全上电后才会生效。这种情况下就导致按照现有的拓扑,在s5状态下,mb主板上的bmc到io switch板上的bmc的pcie通路是不通的,只能通过i2c慢速通路升级,而要给nvidia delta next gpu模块通过pcie高速通路实现快速升级,只能在整个设备上电后即s0状态下才可以通过pcie高速通路给其升级。这样不仅对整个异构服务器升级有了时间成本上的约束,在s0成本下需要整个服务器运行也无形中增加了电费成本和人员管理成本,针对上述问题,如图2所示,本发明实施例提供一种实现双bmc切换升级的方法,应用于实现双bmc切换升级的系统,所述系统包括主板和io切换板;主板上设有主bmc,io切换板上设有从bmc、通路选择芯片;通路选择芯片连接有网络接口,通路选择芯片分别通过一个phy芯片与主bmc和从bmc连接;从bmc与通路选择芯片连接;用于控制通路选择芯片的通路选择;从bmc用于连接待升级模块;所述方法包括如下步骤:

77.步骤1:主bmc判断需从bmc进行管理升级时,判断系统当前状态;

78.步骤2:当系统当前为s5状态时,主bmc通过i2c发送控制指令到从bmc,从bmc接收到控制指令后控制通路选择芯片动作使网络接口与从bmc通信;

79.步骤3:从bmc对待升级模块进行管理升级;

80.步骤4:从bmc在升级完成后,控制通路选择芯片动作使网络接口与主bmc通信。

81.需要说明的是,主bmc判断需从bmc进行管理升级时,当系统当前为s0状态时,执行步骤:主bmc通过i2c发送控制指令到从bmc,从bmc接收到控制指令后控制通路选择芯片动作使网络接口与从bmc通信;

82.或,直接主bmc的rc端口和从bmc的ep端口通信,通过从bmc的rc端口给待升级模块进行管理升级。

83.如图3所示,在有些实施例中,步骤2中,主bmc通过i2c发送控制指令到从bmc,从bmc接收到控制指令后控制通路选择芯片动作使网络接口与从bmc通信的步骤包括:

84.步骤21:主bmc通过i2c发送控制指令到从bmc,将从bmc寄存器的bit0数据位写状态1,同时,发送一个心跳信号给从bmc;

85.步骤22:从bmc接收到心跳信号后,到对应的寄存器读取对应数据位的状态值;

86.步骤23:从bmc根据接收到的指令输出切换控制信号给通路选择芯片,通路选择芯片动作使网络接口与从bmc通信。

87.步骤24:从bmc将对应的寄存器的bit1数据位写状态1,代表切换已执行。

88.在有些实施例中,步骤23中,从bmc根据接收到的指令输出切换控制信号给通路选择芯片,通路选择芯片动作使网络接口与从bmc通信的步骤包括:

89.步骤231:从bmc判断寄存器的bit0数据位的状态值是否为1;

90.若是,执行步骤232;若否,设定时间间隔后,执行步骤21;

91.步骤232:返回主bmc一个心跳信号,从bmc根据接收到的指令输出切换控制信号给通路选择芯片,通路选择芯片动作使网络接口与从bmc通信;本步骤中,从bmc返回主bmc一个心跳信号时,主bmc接收到返回的心跳信号后需要进行时间节点的判断,需要将接收到返回的心跳信号的时间与最近一次主bmc发送心跳信号到从bmc的时间做差,判断时间差值是否在设定阈值范围内,这里一般是100ms,若是,正常进行操作即可,若不是,设定时间间隔后主bmc需要查询从bmc寄存器的状态值,根据从bmc的状态值进行操作。

92.例如,主bmc在发送控制指令到从bmc,将从bmc的寄存器的bit0数据块的状态写1,同时,发送一个heart beat(心跳)信号给从bmc,从bmc接收到heart beat信号之后,到对应的寄存器读取指令,确认寄存器bit0状态是否为1,若是,则返回主bmc一个heart beat代表寄存器check ok信号,主bmc发送给从bmc的heart beat(心跳)信号和从bmc返回给主bmc的heart beat(心跳)信号,这两个heart beat信号的之间的时间间隔不能超过100ms。

93.在有些实施例中,步骤4中,从bmc在升级完成后,控制通路选择芯片动作使网络接口与主bmc通信的步骤包括:

94.步骤41:从bmc在升级完成后将自己的寄存器的bit0数据位更改回初始状态0,并发送一个心跳信号给主bmc;

95.步骤42:主bmc接收心跳信号到之后,查看从bmc的寄存器bit0数据位的状态值;

96.步骤43:若寄存器bit0数据位的状态值为0,则将从bmc的寄存器的bit 1数据位改

回0,同时发送一个心跳信号给从bmc,代表控制权已经拿回。

97.需要说明的是,主bmc和从bmc出到机框上的网络接口,通过通路选择芯片来切换。当s5状态下需要升级delta-gpu时,切换到从bmc即可。两个bmc之间网络接口的控制权的选择,由主bmc发出i2c指令和heart beat来选择。通路选择芯片的选择信号由从bmc来控制,但是控制信号的命令是由主bmc的i2c传输命令来决定的。heart beat信号每一次操作,必须主bmc和从bmc各发送一次代表操作完成,并确认过状态ok。heart beat信号每一次操作,主bmc和从bmc各发送一次代表操作完成的信号时间间隔不能超过100ms,防止误操作。

98.尽管通过参考附图并结合优选实施例的方式对本发明进行了详细描述,但本发明并不限于此。在不脱离本发明的精神和实质的前提下,本领域普通技术人员可以对本发明的实施例进行各种等效的修改或替换,而这些修改或替换都应在本发明的涵盖范围内/任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。