1.本发明涉及电放大器以及包含电放大器和调制器的设备。

背景技术:

2.快速模拟驱动器是高速光收发器中的关键组件;然而,随着数据速率增加超过40gb/s,实现低功率放大器和高带宽驱动电路变得越来越困难。光调制器需要大的驱动电流或大的电压摆幅来实现必要的速度,这又牵扯大的输出缓冲器或大的增益级,两者都导致较高的功耗和减小的带宽,从而进一步加剧了这个问题。

3.可以采用几种均衡技术来扩展光调制器的带宽,诸如前馈均衡(下文称为ffe方法)或连续时间线性均衡(下文称为ctle方法),其中后者耗电较少;然而,负米勒电容(下文称为nmc方法)或电感峰化通常用于抵消大晶体管的寄生电容,如中国专利申请cn104617483以及s.sedighi等人在ieee国际微波研讨会文摘(ieee international microwave symposium digest)(2012)上题为“具有2.5v输出摆幅的低功率20-gbs sige bicmos驱动器(low-power 20-gbs sige bicmos driver with 2.5v output swing)”的论文所示。

4.使用ffe方法和ctle方法的主要缺点是两者都降低了低频增益,因此带宽的提高是以牺牲电光效应为代价的。关于电感峰化,片上电感器可能消耗大量面积,增加芯片成本,并且可能耦合到电路的其他敏感部分;因此,可能需要无电感电路。在这方面,更好的方法是负米勒电容(nmc),其中两个附加的交叉连接电容器用于中和晶体管的寄生基极-集电极电容。由于nmc是基于交叉连接电容器产生的正反馈,因此稳定性始终是个问题。此外,由于米勒效应减小,对于发射极负反馈电阻的较高值,所获得的带宽增强减小。

5.本发明的目的

6.鉴于上述内容,本发明的目的是提供一种改进的电放大器。

7.本发明的另一目的是提供一种包含至少一个电放大器和至少一个调制器的改进设备。

技术实现要素:

8.本发明的示例性实施例涉及一种电放大器,包含:差分前置放大器,其具有第一输出端口和第二输出端口;以及下游放大器级,其具有第一输出单元和第二输出单元;其中,第一输出单元连接到差分前置放大器的第一输出端口,并且第二输出单元连接到差分前置放大器的第二输出端口;并且其中,负阻抗转换器电气地位于所述差分前置放大器和所述下游放大器级中的至少一个中。

9.本发明的上述示例性实施例可以提供大的带宽和减少的稳定性问题。基本思想是使用负电容,该负电容可以不仅中和前置放大器的晶体管的寄生电容,而且中和后续下游放大器级的负载电容。

10.负阻抗转换器优选地被配置成提供负电容。

11.负阻抗转换器可以电气地位于差分前置放大器中,并且将负电容施加到差分前置放大器的第一输出端口和第二输出端口。

12.差分前置放大器优选地包含第一和第二晶体管。

13.第一晶体管的发射极可以提供差分前置放大器的第一输出端口。

14.第二晶体管的发射极可以提供差分前置放大器的第二输出端口。

15.负阻抗转换器优选地将负电容施加到第一和第二晶体管的发射极。

16.第三晶体管的集电极可以连接到第四晶体管的基极。

17.第四晶体管的集电极可以连接到第三晶体管的基极。

18.至少一个电容器优选地连接第三晶体管和第四晶体管的发射极。

19.第三晶体管、第四晶体管和至少一个电容器优选地形成是所述负阻抗转换器的至少一部分或者是所述负阻抗转换器的至少一部分。

20.第一晶体管的发射极优选地连接到第三晶体管的集电极和第四晶体管的基极两者。第二晶体管的发射极优选地连接到第四晶体管的集电极和第三晶体管的基极两者。

21.第一晶体管的基极可以形成差分前置放大器的第一输入端口。

22.第二晶体管的基极可以形成差分前置放大器的第二输入端口。

23.第三晶体管和第四晶体管的发射极优选地通过第一电容器和第二电容器来连接。

24.第一和第二电容器优选地是串联连接的。

25.第一和第二电容器可以是可变的。

26.第一晶体管的发射极可以经由第一电阻连接到第四晶体管的基极。

27.第二晶体管的发射极可以经由第二电阻连接到第三晶体管的基极。

28.可替代地或附加地,负阻抗转换器可以电气地位于下游放大器级中,并可以将负电容施加到下游放大器级。

29.在后者实施例中,下游放大器可以包含第一和第二晶体管。

30.(下游放大器级的)第一和第二晶体管中的至少一个的发射极优选地提供下游放大器的输出端口。

31.负阻抗转换器优选地耦合下游放大器级的第一和第二晶体管的发射极,并将负电容施加到第一和第二晶体管的发射极。

32.(下游放大器级的)第三晶体管的集电极优选地连接到(下游放大器级的)第四晶体管的基极。

33.第四晶体管的集电极优选地连接到第三晶体管的基极。

34.(下游放大器级的)至少一个电容器优选地连接该第三晶体管和第四晶体管的发射极。

35.第三晶体管、第四晶体管和至少一个电容器优选地形成下游放大器级的负阻抗转换器的至少一部分或者是下游放大器级的负阻抗转换器的至少一部分。

36.第一晶体管的发射极优选地连接到第三晶体管的集电极和第四晶体管的基极两者。

37.第二晶体管的发射极优选地连接到第四晶体管的集电极和第三晶体管的基极两者。

38.第一晶体管的发射极优选地经由第一电阻连接到第四晶体管的基极。

39.第二晶体管的发射极优选地经由第二电阻连接到第三晶体管的基极。

40.第三和第四晶体管的基极优选地经由第三电阻来连接。

41.第一晶体管的发射极可以经由第一辅助电容器连接到第四晶体管的基极。第二晶体管的发射极可以经由第二辅助电容器连接到第三晶体管的基极。

42.第三和第四晶体管的基极优选地经由第三电阻和第四电阻来连接。

43.第三电阻和第四电阻优选地是串联连接的。

44.第三电阻与第四电阻之间的中点优选地连接到电压源,所述电压源确定通过第三晶体管和第四晶体管的电流。

45.第三和第四晶体管的发射极优选地经由电阻器而接地。

46.第一晶体管的基极可以形成下游放大器级的第一输入端口。

47.第二晶体管的基极可以形成下游放大器级的第二输入端口。

48.所述负阻抗转换器可以包含第一电容器和第二电容器。第一和第二电容器优选地是串联连接的。第一和第二电容器优选地是可变的。

49.放大器可以包含至少两个差分前置放大器。

50.负阻抗转换器优选地位于所述至少两个差分前置放大器中的两者中。

51.负阻抗转换器优选地被各自配置成提供负电容。

52.负阻抗转换器中的每一个可以将其负电容施加到所分配的差分前置放大器的两个输出端口。

53.在上述所有配置中,放大器可以包含用于以单端配置驱动负载的单个输出端口。

54.可替代地或附加地,放大器可以包含用于差分地驱动负载的两个输出端口。

55.本发明的另一实施例涉及一种设备,其包含具有负阻抗转换器的至少一个电放大器以及由所述至少一个放大器驱动的至少一个调制器。

56.放大器可以以推挽模式驱动调制器。

附图说明

57.为了容易理解获得本发明的上述和其他优点的方式,将通过参考附图中示出的本发明的具体实施例来呈现上面简要描述的本发明的更特定的描述。应理解,这些附图仅描绘了本发明的典型实施例,且因此不应被认为是对其范围的限制,将通过使用附图以附加的特性和细节来描述和解释本发明,其中

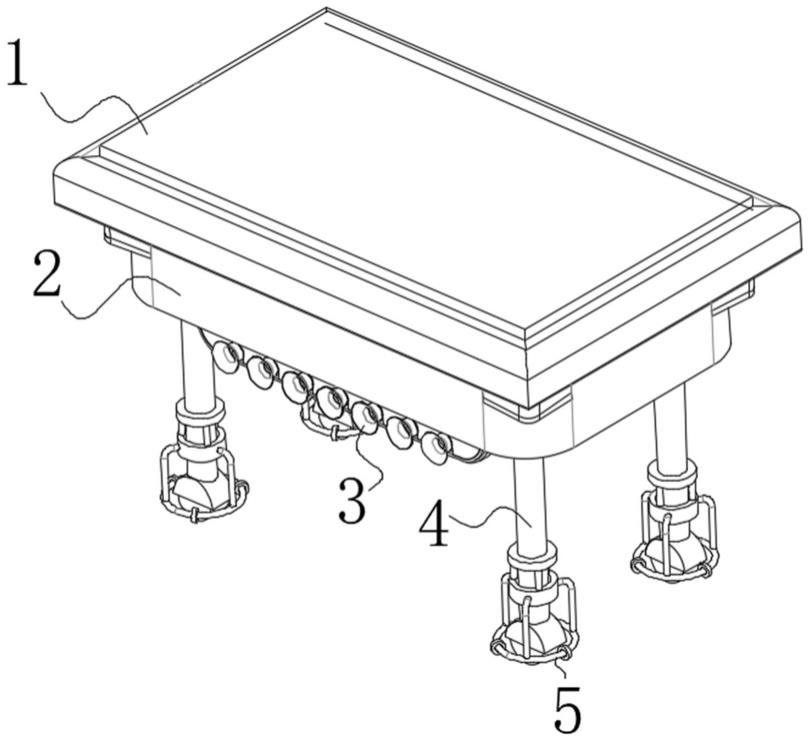

58.图1示出根据本发明的放大器和设备的第一示例性实施例,

59.图2示出了与没有负阻抗转换器nic的可比放大器相比,图1放大器(nic方法)的可实现带宽,

60.图3示出根据本发明的放大器和设备的第二示例性实施例,

61.图4示出第二示例性实施例的等效电路,

62.图5示出根据本发明的放大器和设备的第三示例性实施例,

63.图6示出第三示例性实施例的等效电路,

64.图7示出根据本发明的放大器和设备的第四示例性实施例,

65.图8示出了在具有和没有负阻抗转换器nic的情况下第四实施例在最大带宽上的增益依赖性,

66.图9示出根据本发明的放大器和设备的第五示例性实施例,

67.图10示出根据本发明的放大器和设备的第六示例性实施例,以及

68.图11示出根据本发明的放大器和设备的第七示例性实施例。

具体实施方式

69.通过参考附图,将最好地理解本发明的优选实施例。将容易理解的是,如本文附图中大体描述和说明的,本发明可以在很大范围内变化。因此,如图所示,本发明的示例性实施例的以下更详细描述并不旨在限制所要求保护的本发明的范围,而是仅仅代表本发明的目前优选实施例。

70.图1展示设置有电源电压v

cc

的根据本发明的电放大器10的第一实施例。

71.放大器10包含具有第一输出端口pao1和第二输出端口pao2的差分前置放大器pa。

72.下游放大器级das包含第一输出单元ou1和第二输出单元ou2。第一输出单元ou1连接到差分前置放大器pa的第一输出端口pao1,并且第二输出单元ou2连接到差分前置放大器pa的第二输出端口pao2。

73.负阻抗转换器nic电气地位于差分前置放大器pa中。负阻抗转换器nic提供负电容,并且将负电容施加到差分前置放大器pa的第一输出端口paol和第二输出端口pao2。

74.差分前置放大器pa包含第一晶体管t1和第二晶体管t2。第一晶体管t1的发射极提供差分前置放大器pa的第一输出端口paol。第二晶体管t2的发射极提供差分前置放大器pa的第二输出端口pao2。负阻抗转换器nic将负电容施加到第一晶体管t1和第二晶体管t2的发射极。

75.负阻抗转换器nic由第三晶体管t3、第四晶体管t4和电容器c

nic

形成。

76.第三晶体管t3的集电极连接到第四晶体管t4的基极。第四晶体管t4的集电极连接到第三晶体管t3的基极。第三晶体管t3和第四晶体管t4的发射极通过串联布置的电容器c

nic

来连接。

77.在图1的示例性实施例中,第一晶体管t1的发射极连接到第三晶体管t3的集电极和第四晶体管t4的基极两者。第二晶体管t2的发射极连接到第四晶体管t4的集电极和第三晶体管t3的基极两者。

78.第一晶体管t1的基极形成差分前置放大器pa的第一输入端口pai1。第二晶体管t2的基极形成差分前置放大器pa的第二输入端口pai2。输入端口pai1和pai2被差分地提供输入信号v

in

。

79.在图1的实施例中,输出单元ou1和ou2中的每一个包含晶体管t5/t6、电阻器r

gain

和电流源si。输出单元ou1和ou2通过电容器c

deg

和电阻器r

deg

来耦合。

80.晶体管中的一个(此处是晶体管t6)的发射极提供了负载load连接到的下游放大器das的输出端口。

81.上面参考图1描述的示例性实施例提供了大的带宽,而没有或者只有不明显的稳定性问题。基本思想是使用负阻抗转换器nic的负电容,其不仅中和晶体管t1和t2的寄生电容,而且中和下游放大器级das的整个负载电容。由于电容器c

nic

跨接在交叉耦合的晶体管t3和t4的两个发射极上,所以在第一晶体管t3的集电极上看到的等效阻抗z

nic

是:

[0082][0083]

上面等式中的变量和下面等式中的变量在下面附加的公式符号的单独列表中定义。

[0084]

如果我们用c

load

表示下游放大器级das的等效负载电容,原则上可以通过强加c

nic

=c

load

来中和该电容。

[0085]

图1的负阻抗转换器nic不会导致任何显著的功率损耗。在图1所示的配置中,晶体管t1基极处的最小电压等于基极-发射极电压与电流源si所提供的电流镜的饱和电压之和。因此,有可能在发射极跟随器电流镜上方容纳负阻抗转换器nic,如图1所示,而无需附加的电压余量,即电源和总功耗保持不变。图1放大器的总传递函数为:

[0086][0087]

只要r

e2

≥r

e1

,就能确保稳定性,因为没有一个系数将是负的。假设晶体管t1和t2具有相同的尺寸re=r

e1

=r

e2

,并且考虑到由系数c4确定的极点处于非常高的频率,我们可以将等式(2)近似为:

[0088][0089]

具有负阻抗转换器nic的放大器10的频率响应为:

[0090][0091]

图2展示(基于等式(3)和(4))与没有负阻抗转换器nic但基于nmc方法的可比放大器相比较,图1的放大器10(使用nic方法)的最大可实现带宽。可见,在某一增益下,nic方法优于nmc方法。为了解释这一点,让我们进一步简化前面的等式,忽略增益电阻和基极电感

的影响,并考虑由系数a1确定的零点通常处于非常高的频率:

[0092][0093]

通过等式(5),当m=√2时获得最大带宽:

[0094][0095]

没有负阻抗转换器nic时的频率响应可以近似为:

[0096][0097]

如果我们强加c

nmc

=c

bc

,则所得带宽将是:

[0098][0099]

我们现在可以比较等式(6)和(8)来理解负阻抗转换器nic何时提供更大的带宽:

[0100][0101]

在前一个示例中,c

be

=5.5 c

bc

,因此当a≤17.3db时,负阻抗转换器nic的性能优于nmc方法。由于高速电路中的单级增益从未超过20db,因此我们可以得出结论,nic方法通常比nmc方法更有利。实际上,当还考虑增益节点处的负载电容时,阈值增益将移动到更高的值。

[0102]

图3描绘根据本发明的放大器10的第二示例性实施例。在此实施例中,两个可变电容器c

var

替代了图1中的两个固定电容器cnic。可变电容器c

var

提供可变电感器。图4中展示等效电路。利用nmc方法实现可变电感器是不可行的,实际上阱电容会严重影响输出带宽,而在nic方法中,通过利用电路的差分性质,阱电容被虚拟接地吸收。可变电容器可以用于修改电路的频率行为。实际上,当选择m=√2时,获得巴特沃兹(butterworth)滤波器形状,但是其他形状(即贝塞尔(bessel))或其他频率行为也是可能的。

[0103]

图5描绘根据本发明的放大器10的第三示例性实施例。图5的实施例包含两个附加电阻器rb。第一晶体管t1的发射极经由第一个电阻器rb连接到第四晶体管t4的基极,并且第二晶体管t2的发射极经由第二个电阻器rb连接到第三晶体管t3的基极。

[0104]

为了实现更平坦的增益和更低的峰化,有可能调整kb的值。这可以通过引入与晶体管t3和t4的基极串联的电阻器rb来实现,使得lb′

=τb·

(rb rb),如图6中描绘的等效电路所示。

[0105]

图7描绘根据本发明的放大器10的第四示例性实施例。此处,负阻抗转换器nic电气地位于下游放大器级das中,并将负电容施加到下游放大器级das。

[0106]

下游放大器级das包含第一晶体管t1和第二晶体管t2。第一晶体管t1的基极形成

下游放大器级das的第一输入端口dasi1;并且第二晶体管t2的基极形成下游放大器级das的第二输入端口dasi2。第二晶体管中的一个(此处是晶体管t2)的发射极提供了负载load连接到的下游放大器的输出端口。

[0107]

负阻抗转换器nic耦合下游放大器级das的第一晶体管t1和第二晶体管t2的发射极,并向它们施加负电容。

[0108]

负阻抗转换器nic由第三晶体管t3、第四晶体管t4以及由串联布置的两个电容器c

nic

形成的堆叠电容器形成。第三晶体管t3的集电极连接到第四晶体管t4的基极。第四晶体管t4的集电极连接到第三晶体管t3的基极。两个电容器c

nic

连接第三晶体管t3和第四晶体管t4的发射极。

[0109]

在图7的实施例中,第一晶体管t1的发射极连接到第三晶体管t3的集电极和第四晶体管t4的基极两者。第二晶体管t2的发射极连接到第四晶体管t4的集电极和第三晶体管t3的基极两者。

[0110]

图7的实施例还允许增加作为负载load连接到放大器10的下游调制器的带宽。实际上,nic方法在驱动基于电光效应的重负载光学设备(诸如注频调制器、eam等...)的电路中是有利的,因为它可以提供低阻抗驱动电路和发射极跟随器。如上所述,nic级的引入出现而没有功率损耗。

[0111]

这又意味着降低去加重,随后增强电光效应。实际上,对于没有nic级的图7的电路,我们可以写为:

[0112][0113]

因此,如果我们希望零点补偿负载引入的极点r

deg c

deg

=r

e c

load

,带宽将扩展因子1 g

mrdeg

/2,但增益将降低相同的因子。因此,要么电光效应降低,要么电压摆幅必须增加,因此需要更高的电流或更高的增益电阻,这又会再次降低带宽。对于图7中具有nic级的电路,忽略电感式元件,我们可以将频率响应表示为:

[0114][0115]

由于最大带宽1.85ω0是在m=√2时获得的,因此我们可以将(11)简化为:

[0116][0117]

等式(12)表明,电容式负反馈引入的零点必须补偿1.85倍小的时间常数。这意味着,给定相等的c

deg

,nic方法将需要1.85倍小的负反馈电阻,对应于大5.3db(参见图8)。

[0118]

图8展示在具有和没有负阻抗转换器nic的情况下在最大带宽上的g

out

。

[0119]

图9描绘根据本发明的放大器10的第五示例性实施例。该实施例的负阻抗转换器nic包含两个值为n

·

rd的电阻器和一个值为2

·

rd的第三电阻器。

[0120]

第一晶体管t1的发射极经由电阻器nrd中的一个连接到第四晶体管t4的基极;并

且第二晶体管t2的发射极经由电阻器nrd中的另一个连接到第三晶体管t3的基极。第三晶体管t3和第四晶体管t4的基极经由第三电阻器2rd来连接。

[0121]

在图9的实施例中,有可能使用电阻分压器来减小上述对的集电极-基极之间的电压摆幅,因为输出电压摆幅可能大到足以导致交叉耦合对的饱和。电阻器以dc电平与图7的实施例相同的方式布置,但是在ac操作中,交叉耦合对上的电压降低了一个因子(n 1)。只要晶体管t3和t4的尺寸是晶体管t1和t2的尺寸的(n 1)倍并且如果n

·

rd》》r

e4

,等式(1)至(11)的有效性就成立。必须注意,当c

nic

=c

load

/[√2(n 1)]时,将达到最大带宽。

[0122]

图10描绘根据本发明的放大器10的第六示例性实施例。此处,第一晶体管t1的发射极经由第一辅助电容器cd连接到第四晶体管t4的基极。第二晶体管t2的发射极经由第二辅助电容器cd连接到第三晶体管t3的基极。

[0123]

此外,第三晶体管t3和第四晶体管t4的基极经由两个电阻r

bias

来连接。电阻r

bias

是串联连接的。电阻r

bias

之间的中点连接到确定第三晶体管t3和第四晶体管t4中的电流的电压源。

[0124]

此外,第三晶体管t3和第四晶体管t4的发射极经由电阻器re而非电流源接地。

[0125]

如果在感兴趣的频率范围内,re》》1/(s

·cnic

),比缩放因子将为n=cb/cd。

[0126]

只要晶体管t3和t4的尺寸是晶体管t1和t2的尺寸的(n 1)倍,等式(1)至(11)的有效性就成立。当c

nic

=c

load

/[√2(n 1)]时,将达到最大带宽。

[0127]

图11描绘根据本发明的放大器10的第七示例性实施例。在此实施例中放大器包含两个差分前置放大器pa1和pa2。两个差分前置放大器pa1和pa2被提供有差分输入信号va和vb。

[0128]

负阻抗转换器nic定位于差分前置放大器pa1和pa2中的每一个中。每一负阻抗转换器nic将其负电容施加到所分配的差分前置放大器pa1或pa2的输出端口pao1和pao2。

[0129]

负载load连接在下游放大器级das的输出端口daso1和daso2之间。

[0130]

在图11的实施例中,集成了ffe电路以进一步扩展带宽。实际上,在典型的ffe电路中,两个或更多个差分对连接到同一输出节点。为了提高速度,这里不可能使用nmc方法,因为两个或更多个不同的信号将作用于交叉连接的电容器,因此使用电感峰化或共源共栅级。给定晶体管堆栈,后一种方法需要更大的电源,或者降低电压摆幅。

[0131]

在上面参考图1至11论述的实施例中,假定在输出节点没有附加的寄生元件(诸如焊盘/导线杂散电容和电感),放大器(驱动器)和电光调制器的共同集成将导致最佳的速度提高。

[0132]

在上面参考图1至11讨论的实施例中,所有的电路都可以用各种技术(cmos、bjt等

…

)实现。

[0133]

在上面参考图1至11讨论的实施例中,负载load可以仅连接到一个输出端(单端配置),或者在可能的情况下连接到两个输出端(差分地)(即推挽式调制器)。

[0134]

上面通过示例描述的操作原理可以应用于包括放大器和光调制器(例如,相位调制器、振幅调制器、偏振调制器、注频调制器、耗尽调制器等等

…

)的任何类型的设备。

[0135]

放大器(驱动器)和电光调制器的共同集成通常可以提供最佳的性能,假定没有附加的寄生元件(诸如焊盘/导线杂散电容和电感),否则其会使调制器电极上的rf信号降级并干扰到延迟补偿环路的高速连接上的传播延迟。

[0136]

本文公开的本发明的各种实施例和实施例的方面不仅要按照本说明书中具体描述的顺序和上下文来理解,而且要包括任何顺序及其任何组合。只要上下文需要,所有单数词应被视为包括复数,且反之亦然。只要上下文需要,所有列出的带有词“和”的选项应被视为包括词“或”,且反之亦然,以及它们的任何组合。

[0137]

在附图和说明书中,已经公开了本发明的多个实施例。申请人想要强调的是,每一实施例的每一特征可以与任何其他实施例相结合或添加到任何其他实施例中,以便修改相应的实施例并创建附加的实施例。这些附加的实施例形成了本公开的一部分,且因此,申请人可以在诉讼的后期阶段提交关于这些附加实施例的进一步的专利权利要求。

[0138]

此外,申请人想要强调的是,每一以下从属权利要求的每一特征可以与任何现有的独立权利要求以及任何其他(一个或多个)现有的从属权利要求相结合(不考虑现有的权利要求结构)。

[0139]

因此,申请人可以在诉讼的后期阶段将进一步的专利权利要求指向其他权利要求组合。

[0140]

例如,权利要求25和26的设备可以包含权利要求2至24中的任一项的特征(以任何组合)。

[0141]

此外,权利要求1的放大器可以包含从属权利要求2至24中的任一项、多项或所有项的特征。换句话说,每一从属权利要求可以参考任何其他从属权利要求,而不管当前的权利要求结构和从属权利要求在下面列出的顺序。

[0142]

公式符号列表:

[0143]

τ

b 基极传输时间

[0144]rb 基极电阻

[0145]re 小信号发射极电阻

[0146]gm 晶体管跨导

[0147]cload 下游放大器级的等效负载电容

[0148]cbe 小信号基极-发射极电容

[0149]cbc 小信号基极-集电极电容

[0150]cdeg 差分对发射极负反馈电容

[0151]cgain 增益级集电极寄生电容

[0152]cout 等效输出负载电容

[0153]cnmc 用于米勒效应补偿的交叉耦合基极-集电极电容(负米勒电容)

[0154]cnic 等效负阻抗转换器发射极电容

[0155]rgain 增益级集电极电阻

[0156]rdeg 差分对发射极负反馈电阻

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。