一种移相全桥dc-dc变换器的同步整流控制方法

技术领域

1.本发明涉及电力电子技术领域,尤其涉及一种移相全桥dc-dc变换器的同步整流控制方法。

背景技术:

2.近年来,对于服务器和车载充电器等的电源,要求其能够处理更大功率的需求增加。这类大功率电源中大多采用全桥电路,尤其是相移全桥(phase shift full bridge,以下称“psfb”)电路,传统的应用于相移全桥的同步整流驱动时序采用简单的或逻辑,无法实现全工作范围内的同步整流。移相全桥(psfb)转换器是中高功率dc/dc转换器中的一种有吸引力的拓扑结构,因为它通过实现一次侧开关的零电压开关(zvs)、低rms电流和简单的控制方案实现高效率并且具有固定的开关频率。由于这一优势,它已被广泛应用于各种应用,如服务器电源、电动汽车充电器和大功率led驱动器。因其能够在超级mosfet和igbt等开关元件导通时实现零电压开关工作,可以减少开关损耗,故可以处理更大的功率。由于生产工艺的原因,相移全桥电路中使用的mosfet和igbt等开关元件中会出现寄生二极管,也称体二极管,在移相全桥电路整流工作期间仍然有电流流经开关管的体二极管造成较大的功率损耗。

3.现有的移相全桥dc-dc变换器的同步整流策略一般采用简单的逻辑,虽然能够实现同步整流的功能,但并不能很好的与使用二极管整流时工作方式相契合,在同步开关管关断后,仍然会有电流流经其体二极管产生功率损耗,这就是二极管整流时序带来的功耗问题。

技术实现要素:

4.针对现有技术的不足,本发明公开了一种移相全桥dc-dc变换器的同步整流控制方法,以解决上述背景技术中提出的问题。

5.(一)技术方案

6.为实现以上目的,本发明通过以下技术方案予以实现:本发明针对移相全桥dc-dc变换器现有的同步整流技术不能很好的实现二极管整流时序带来的功耗问题,提出了一种移相全桥dc-dc变换器的同步整流控制方法,在传统的移相全桥dc-dc变换器的同步整流电路二次侧中,采用便于控制的开关管来替代二极管,并利用单片机微控制器控制移相全桥电路的同步整流驱动时序逻辑,使变压器将原边能量传递至副边的过程中,二次侧开关管始终处于低阻抗的导通阶段,实现进一步减小副边开关管损耗的目的。并对移相全桥电路产生占空比损耗的原理进行仿真分析,进一步得出移相全桥电路产生占空比丢失的原因及其持续时间,在仿真中对移相全桥电路产生占空比进行改进,进而确定同步整流时序逻辑,根据得出的同步整流驱动时序,建立移相全桥dc-dc变换器的闭环仿真分析来验证同步整流时序能够很好的近似二极管导通情况,相比于传统或逻辑的驱动时序,能够更有效地减少开关管上的功率损耗。

7.本发明的单片机微控制器控制移相全桥电路包括了变压器t的一次侧全桥电路、变压器t的二次侧的同步整流电路、单片机控制器,一次侧全桥电路由电压源u、第一开关管q1、第二开关管q2、第三开关管q3、第四开关管q4、谐振电感l1组成,二次侧的同步整流电路由第五开关管q5、第六开关管q6、输出滤波电感l2、输出滤波电容c1及负载r组成,第一开关管q1和第三开关管q3串联后与电压源u并联在一起,第二开关管q2与第四开关管q4串联后与电压源u并联在一起,谐振电感l1串联在变压器t的原边与第一开关管q1之间,第五开关管q5、第六开关管q6并联在变压器t的副边,输出滤波电容c1与负载r并联在输出滤波电感l2的一端与变压器t的副边之间,输出滤波电感l2的另一端与第五开关管q5的阴极相连,第一开关管q1、第二开关管q2、第三开关管q3、第四开关管q4、第五开关管q5、第六开关管q6的栅极与单片机控制器的io口连接,由单片机控制器产生的驱动时序控制第一开关管q1、第二开关管q2、第三开关管q3、第四开关管q4、第五开关管q5、第六开关管q6的栅极,,且对负载r上的电压电流进行采样输入单片机控制器中。

8.本发明的采用单片机微控制器控制移相全桥电路的同步整流驱动时序逻辑实施步骤为:

9.s1:建立移相全桥变换器各部分的数学模型

10.建立移相全桥dc-dc变换器结构,通过变换器的设计,使变换器参数的设计能够满足其应用要求;

11.s2:分析变换器的工作模态

12.1.开关模态0,t0时刻:

13.t0之前,第一开关管q1和第四开关管q4导通,电压源u上的一次侧电流i

p

流经第一开关管q1、谐振电感l1、变压器t的原边绕组及第四开关管q4,整流侧电流流经第五开关管q5、输出滤波电感l2、输出滤波电容c1及负载r;

14.2.开关模态1,[t0,t1]:

[0015]

记t0时刻流经变压器t的一次侧电流的电流i1的值为i1,在t0时刻关断第一开关管q1,变压器t的一次侧电流i

p

分别给第一开关管q1、第三开关管q3的并联电容充、放电,第一开关管q1为零电压关断,这段时间里,谐振电感l1与滤波电感l2串联,可以认为变压器t的一次侧电流i

p

近似不变。这样变压器t的一次侧电流i

p

和第一开关管q1、第三开关管q3两端的电压为:

[0016]ip

(t)=i

p

(t0)=i1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(1)

[0017][0018][0019]

在t1时刻,第三开关管q3两端电压下降到零,第三开关管q3的反并联二极管自然导通,开关模态1结束,

[0020]

此开关模态的时间计算为:

[0021]

t

01

=2c

leadvin

/i1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(4)

[0022]

其中v

in

为移相全桥dc-dc变换器的输入电压;

[0023]

3.开关模态2,[t1,t2]:

[0024]

第三开关管q3的反并联二极管导通后,开通第三开关管q3,此时第三开关管q3为零电压开通,用k表示变压器t的变比,这段时间里,变压器t的一次侧电流i

p

等于折算到变压器t一次侧的滤波电感电流i

lf

,即:

[0025]ip

(t)=i

lf

(t)/k

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(5)

[0026]

在t2时刻,变压器t的一次侧电流i

p

下降到i2;

[0027]

4.开关模态3,[t2,t3]:

[0028]

在t2时刻,关断第四开关管q4,变压器t的一次侧电流i

p

分别给第四开关管q4、第二开关管q2的并联电容充、放电,第四开关管q4为零电压关断,此时变压器t的二次侧绕组的电势变为下正上负,这时第六开关管q6导通,由于第五开关管q5、第六开关管q6同时导通,使得变压器二次侧绕组电压为零,即产生占空比损耗,这段时间里,谐振电感l1与第四开关管q4、第二开关管q2的输出电容谐振工作,变压器t的一次侧电流i

p

和第四开关管q4、第二开关管q2两端的电压为:

[0029]ip

(t)=i2cosω1(t-t2)

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(6)

[0030][0031][0032]

其中:在t3时刻,当第四开关管q4两端的电压上升到输入电压v

in

,第二开关管q2的反并联二极管自然导通,开关模态3结束;

[0033]

此开关模态的时间计算为:

[0034][0035]

5.开关模态4,[t3,t4]:

[0036]

在t3时刻,第二开关管q2的反并联二极管自然导通,将第二开关管q2的电压钳位在零位,此时第二开关管q2是零电压开通;

[0037]

在t4时刻,变压器t的一次侧电流i

p

下降到零,第二开关管q2,第三开关管q3的反并联二极管自然关断;

[0038]

6.开关模态5,[t4,t5]:

[0039]

在t4时刻,变压器t的一次侧电流i

p

由正值过零,并且负方向增加,但由于变压器t的一次侧电流i

p

仍不足以提供负载电流,负载电流仍由第五开关管q5、第六开关管q6提供回路,因此原边的绕组电压仍然为零,谐振电感lr两端电压为v

in

,i

p

反向增加,其大小为:

[0040][0041]

在t5时刻,变压器t的原边的电流到达折算到变压器t原边的负载电流-i

lf

(t5)/k,该开关模态结束,此时,第五开关管q5关断,第六开关管q6流过全部负载电流;

[0042]

7.开关模态6,[t5,t6]:

[0043]

t5到t6这段时间里,电源给负载r供电,在t6时刻,第三开关管q3关断,移相全桥dc-dc变换器开始在另一个半周期工作,其工作情况类似于上述的半个周期;

[0044]

s3:求出占空比丢失的时间,并给出其同步整流的时序逻辑

[0045]

基于以上分析,可以得出移相全桥dc-dc变换器的占空比损耗计算公式为:

[0046][0047]

由于t

23

很短,可以忽略,因此占空比丢失的持续时间可以近似为很短,可以忽略,因此占空比丢失的持续时间可以近似为基于移相全桥的一个开关周期工作模态的分析,可以得出其产生占空比丢失的原因及其持续时间,因此得出改进后的移相全桥同步整流时序,进而得出第五开关管q5时序的逻辑推导过程,由其卡诺图可得,其改进后的同步整流时序逻辑为:

[0048][0049]

其中,q1为变压器t一次侧第一开关管q1的驱动时序;q4为一次侧mos管q4的驱动时序;de为所得的占空比损耗延时时序。

[0050]

同理,改进后的第六开关管q5的同步整流时序逻辑为:

[0051][0052]

s4:根据得出的同步整流驱动时序,建立移相全桥dc-dc变换器的闭环仿真模型,通过仿真来验证同步整流时序能够很好的近似二极管导通情况。

[0053]

采用上述发明带来的有益效果:

[0054]

1.本发明在不影响移相全桥dc-dc变换器运行状态和功能的条件下,改善其变压器二次侧的功率损耗。

[0055]

2.本发明给出了一种基于单片机微控制器数字控制的移相全桥电路的同步整流驱动时序逻辑,根据得出的同步整流驱动时序,建立移相全桥dc-dc变换器的闭环仿真模型,通过仿真来验证同步整流时序能够很好的近似二极管导通情况,可以进一步减小大电流场合下同步开关管的功率损耗。

附图说明

[0056]

图1为本发明中基于二极管整流的移相全桥dc-dc变换器电路拓扑图;

[0057]

图2为本发明中基于二极管整流的移相全桥dc-dc变换器一个开关周期内的工作波形;

[0058]

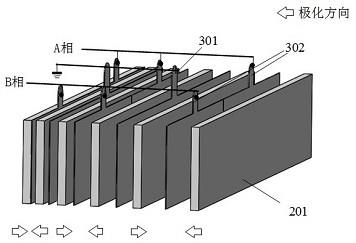

图3为本发明的单片机微控制器控制移相全桥电路的拓扑图;

[0059]

图4为本发明的单片机微控制器控制移相全桥电路的同步整流时序;

[0060]

图5为本发明的第五开关管q5时序的逻辑推导过程图;

[0061]

图6为本发明的移相全桥dc-dc变换器的闭环仿真模型;

[0062]

图7为本发明的单片机微控制器控制移相全桥电路的驱动时序波形与基于二极管整流的移相全桥dc-dc变换器导通情况的对比图。

具体实施方式

[0063]

下面结合附图和具体实施方式对本发明作进一步说明。

[0064]

请参阅图1至图7所示为本发明中的一种移相全桥dc-dc变换器的同步整流控制方法。

[0065]

如图1所示为基于二极管整流的移相全桥dc-dc变换器电路拓扑图,包括了第一变压器t1的一次侧全桥电路,以及第一变压器t1的二次侧的同步整流电路,一次侧全桥电路由第一电压源u1、第七开关管q7、第八开关管q8、第九开关管q9、第十开关管q10、第一谐振电感l2组成,二次侧的同步整流电路由第一整流二极管d1、第二整流二极管d2、第一输出滤波电感l3、输出第一滤波电容c2及第一负载r1组成,第七开关管q7和第九开关管q9串联后与第一电压源u1并联在一起,第八开关管q8和第十开关管q10串联后与第一电压源u1并联在一起,第一谐振电感l3串联在第一变压器t1的原边与第七开关管q7之间,第一整流二极管d1、第二整流二极管d2并联在第一变压器t1的副边,第一输出滤波电容c2与第一负载r1并联在第一输出滤波电感l4的一端与第一变压器t1的副边之间,第一输出滤波电感l4的另一端与第一整流二极管d1的阴极相连。

[0066]

如图2所示为基于二极管整流的移相全桥dc-dc变换器一个开关周期内的工作波形图,可见由于引入了第一谐振电感l3实现了第一变压器t1一次侧开关管的零电压开通,但同时带来了占空比损耗的问题,这就是二极管整流时序带来的功耗问题。

[0067]

如图3所示,本发明的单片机微控制器控制移相全桥电路包括了变压器t的一次侧全桥电路、变压器t的二次侧的同步整流电路、单片机控制器,一次侧全桥电路由电压源u、第一开关管q1、第二开关管q2、第三开关管q3、第四开关管q4、谐振电感l1组成,二次侧的同步整流电路由第五开关管q5、第六开关管q6、输出滤波电感l2、输出滤波电容c1及负载r组成,第一开关管q1和第三开关管q3串联后与电压源u并联在一起,第二开关管q2与第四开关管q4串联后与电压源u并联在一起,谐振电感l1串联在变压器t的原边与第一开关管q1之间,第五开关管q5、第六开关管q6并联在变压器t的副边,输出滤波电容c1与负载r并联在输出滤波电感l2的一端与变压器t的副边之间,输出滤波电感l2的另一端与第五开关管q5的阴极相连,第一开关管q1、第二开关管q2、第三开关管q3、第四开关管q4、第五开关管q5、第六开关管q6的栅极与单片机控制器的io口连接,且对负载r上的电压电流进行采样输入单片机控制器中。

[0068]

本发明的采用单片机微控制器控制移相全桥电路的同步整流驱动时序逻辑实施步骤为:

[0069]

s1:建立移相全桥变换器各部分的数学模型

[0070]

建立移相全桥dc-dc变换器结构,通过变换器的设计,使变换器参数的设计能够满足其应用要求;

[0071]

s2:分析变换器的工作模态

[0072]

1.开关模态0,t0时刻:

[0073]

t0之前,第一开关管q1和第四开关管q4导通,电压源u上的一次侧电流i

p

流经第一开关管q1、谐振电感l1、变压器t的原边绕组及第四开关管q4,整流侧电流流经第五开关管q5、输出滤波电感l2、输出滤波电容c1及负载r;

[0074]

2.开关模态1,[t0,t1]:

[0075]

记t0时刻流经变压器t的一次侧电流的电流i1的值为i1,在t0时刻关断第一开关管q1,变压器t的一次侧电流i

p

分别给第一开关管q1、第三开关管q3的并联电容充、放电,第一开关管q1为零电压关断,这段时间里,谐振电感l1与滤波电感l2串联,可以认为变压器t的一次侧电流i

p

近似不变。这样变压器t的一次侧电流i

p

和第一开关管q1、第三开关管q3两端

的电压为:

[0076]ip

(t)=i

p

(t0)=i1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(1)

[0077][0078][0079]

在t1时刻,第三开关管q3两端电压下降到零,第三开关管q3的反并联二极管自然导通,开关模态1结束,

[0080]

此开关模态的时间计算为:

[0081]

t

01

=2c

leadvin

/i1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(4)

[0082]

其中v

in

为移相全桥dc-dc变换器的输入电压;

[0083]

3.开关模态2,[t1,t2]:

[0084]

第三开关管q3的反并联二极管导通后,开通第三开关管q3,此时第三开关管q3为零电压开通,用k表示变压器t的变比,这段时间里,变压器t的一次侧电流i

p

等于折算到变压器t一次侧的滤波电感电流i

lf

,即:

[0085]ip

(t)=i

lf

(t)/k

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(5)

[0086]

在t2时刻,变压器t的一次侧电流i

p

下降到i2;

[0087]

4.开关模态3,[t2,t3]:

[0088]

在t2时刻,关断第四开关管q4,变压器t的一次侧电流i

p

分别给第四开关管q4、第二开关管q2的并联电容充、放电,第四开关管q4为零电压关断,此时变压器t的二次侧绕组的电势变为下正上负,这时第六开关管q6导通,由于第五开关管q5、第六开关管q6同时导通,使得变压器二次侧绕组电压为零,即产生占空比损耗,这段时间里,谐振电感l1与第四开关管q4、第二开关管q2的输出电容谐振工作,变压器t的一次侧电流i

p

和第四开关管q4、第二开关管q2两端的电压为:

[0089]ip

(t)=i2cosω1(t-t2)

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(6)

[0090][0091][0092]

其中:在t3时刻,当第四开关管q4两端的电压上升到输入电压v

in

,第二开关管q2的反并联二极管自然导通,开关模态3结束;

[0093]

此开关模态的时间计算为:

[0094][0095]

5.开关模态4,[t3,t4]:

[0096]

在t3时刻,第二开关管q2的反并联二极管自然导通,将第二开关管q2的电压钳位在零位,此时第二开关管q2是零电压开通;

[0097]

在t4时刻,变压器t的一次侧电流i

p

下降到零,第二开关管q2,第三开关管q3的反并联二极管自然关断;

[0098]

6.开关模态5,[t4,t5]:

[0099]

在t4时刻,变压器t的一次侧电流i

p

由正值过零,并且负方向增加,但由于变压器t的一次侧电流i

p

仍不足以提供负载电流,负载电流仍由第五开关管q5、第六开关管q6提供回路,因此原边的绕组电压仍然为零,谐振电感lr两端电压为v

in

,i

p

反向增加,其大小为:

[0100][0101]

在t5时刻,变压器t的原边的电流到达折算到变压器t原边的负载电流-i

lf

(t5)/k,该开关模态结束,此时,第五开关管q5关断,第六开关管q6流过全部负载电流;

[0102]

7.开关模态6,[t5,t6]:

[0103]

t5到t6这段时间里,电源给负载r供电,在t6时刻,第三开关管q3关断,移相全桥dc-dc变换器开始在另一个半周期工作,其工作情况类似于上述的半个周期;

[0104]

s3:求出占空比丢失的时间,并给出其同步整流的时序逻辑

[0105]

基于以上分析,可以得出移相全桥dc-dc变换器的占空比损耗计算公式为:

[0106][0107]

由于t

23

很短,可以忽略,因此占空比丢失的持续时间可以近似为很短,可以忽略,因此占空比丢失的持续时间可以近似为基于移相全桥的一个开关周期工作模态的分析,可以得出其产生占空比丢失的原因及其持续时间,因此得出单片机微控制器控制移相全桥电路的同步整流时序,图5给出了第五开关管q5时序的逻辑推导过程,由其卡诺图可得,其改进后的同步整流时序逻辑为:

[0108][0109]

其中,q1为变压器t一次侧第一开关管q1的驱动时序;q4为一次侧mos管q4的驱动时序;de为所得的占空比损耗延时时序。

[0110]

同理,改进后的第六开关管q6的同步整流时序逻辑为:

[0111][0112]

s4:根据得出的同步整流驱动时序,建立移相全桥dc-dc变换器的闭环仿真模型,通过仿真来验证同步整流时序能够很好的近似二极管导通情况。

[0113]

图6根据得出的同步整流驱动时序,建立移相全桥dc-dc变换器的闭环仿真模型,图7为单片机微控制器控制移相全桥电路的驱动时序波形与基于二极管整流的移相全桥dc-dc变换器导通情况的对比图,验证了本发明的单片机微控制器控制移相全桥电路的驱动时序能够很好的近似二极管导通情况,相比于传统或逻辑的驱动时序,能够更有效地减少开关管上的功率损耗。

[0114]

本发明的工作原理与工作过程如下:

[0115]

在传统的移相全桥dc-dc变换器的同步整流电路二次侧中,采用便于控制的开关管来替代二极管,并利用单片机微控制器控制移相全桥电路的同步整流驱动时序逻辑,使变压器将原边能量传递至副边的过程中,二次侧开关管始终处于低阻抗的导通阶段,实现进一步减小副边开关管损耗的目的。并对移相全桥电路产生占空比损耗的原理进行仿真分

析,进一步得出移相全桥电路产生占空比丢失的原因及其持续时间,在仿真中对移相全桥电路产生占空比进行改进,进而确定同步整流时序逻辑,根据得出的同步整流驱动时序,建立移相全桥dc-dc变换器的闭环仿真分析来验证同步整流时序能够很好的近似二极管导通情况,相比于传统或逻辑的驱动时序,能够更有效地减少开关管上的功率损耗。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。