1.本发明涉及半导体发光元件,特别涉及具备具有量子阱构造的活性层的半导体发光元件。

背景技术:

2.以往,激光被用于加工用途,需要高输出且高效率的激光源。作为这样的激光源而使用半导体激光元件等半导体发光元件。在加工用途中,特别是在焊接加工用途中,希望激光源的进一步的高输出化。

3.在专利文献1中记载了用来使半导体发光元件高输出化的技术的一例。在专利文献1中记载了以下技术:在具有量子阱构造的活性层中,使阱层中的重空穴(heavy hole)的第一量子能级与势垒层(barrier layer)的价带顶部的能级之间的能量差δev较小,并且,使阱层中的电子的第一量子能级与势垒层的导带底部的能级之间的能量差δec较大。在专利文献1所记载的半导体发光元件中,通过使能量差δev较小,使空穴容易运动,从而提高空穴与电子的复合的概率,并且,通过使能量差δec较大来抑制电子从阱层的溢出(即,泄漏)。

4.现有技术文献

5.专利文献

6.专利文献1:日本特开平10-256659号公报

技术实现要素:

7.发明要解决的课题

8.但是,在专利文献1所记载的半导体发光元件中,由于能量差δec较大,所以为了将电子向阱层注入而需要的工作电压增大。随之,半导体发光元件的自发热增大,所以热饱和水平下降。

9.本发明用于解决这样的课题,目的在于提供能够在抑制工作电压的同时抑制电子从阱层的溢出的半导体发光元件等。

10.用来解决课题的手段

11.为了解决上述课题,本发明的半导体发光元件的一技术方案具备:基板;n型包层,配置在上述基板的上方;活性层,配置在上述n型包层的上方;以及p型包层,配置在上述活性层的上方;上述活性层具有:阱层;n侧第一势垒层,配置在上述阱层的上述n型包层侧;以及p侧势垒层,配置在上述阱层的上述p型包层侧;上述p侧势垒层包含in;上述n侧第一势垒层的in组份比低于上述p侧势垒层的in组份比;上述n侧第一势垒层的带隙能量比上述p侧势垒层的带隙能量小。

12.这样,使n侧第一势垒层的in组份比小于p侧势垒层的in组份比,并且使n侧第一势垒层的带隙小于p侧势垒层的带隙。由此,能够使p侧势垒层与n侧第一势垒层的导带势能的能量差δec比p侧势垒层与n侧第一势垒层的价带势能的能量差δev大。因而,能够抑制空穴的电传导所需要的电压的增大、即半导体发光元件的工作电压的增大,并且抑制电子从

阱层的溢出。

13.此外,在本发明的半导体发光元件的一技术方案中,可以是,上述n侧第一势垒层的组份由al

ybn1

ga

1-xbn1-ybn1

in

xbn1

as表示;上述p侧势垒层的组份由al

ybp1

ga

1-xbp1-ybp1

in

xbp1

as表示;0≦ybn1≦1、0≦xbn1《1、0《ybp1《1、0《xbp1《1以及xbn1《xbp1的关系成立。

14.通过采用具有这样的组份的n侧第一势垒层及p侧势垒层,能够使n侧第一势垒层的in组份比小于p侧势垒层的in组份比,并且使n侧第一势垒层的带隙比p侧势垒层的带隙小。

15.此外,在本发明的半导体发光元件的一技术方案中,可以是,进而,ybn1《ybp1的关系成立。

16.由此,p侧势垒层与n侧第一势垒层的导带势能的能量差δec增大,所以能够进一步抑制电子从阱层的溢出。

17.此外,在本发明的半导体发光元件的一技术方案中,可以是,进而,0.2≦ybn1≦0.4,ybp1≦xbp1 0.975ybn1 0.069,ybp1≧0.4xbp1 0.975ybn1 0.029,以及xbp1≦0.15的关系成立。

18.这样,通过使n侧第一势垒层的al组份比ybn1为0.2以上0.4以下,能够在抑制向阱层的光约束系数的大幅下降的同时实现波导的低损耗化。

19.此外,关于p侧势垒层的al组份比ybp1,通过上述关系的成立,能够将n侧第一势垒层与p侧势垒层之间的价带势能的能量差δev2抑制为30mev以下,并且将n侧第一势垒层与p侧势垒层之间的导带势能的能量差δec2增大到25mev以上。因而,通过抑制能量差δev2,能够抑制工作电压的增大,通过增大能量差δec2,能够抑制电子的溢出。

20.此外,通过将p侧势垒层的al组份比xbp1设为0.15以下,能够将gaas基板与p侧势垒层的晶格失配抑制为最大1.2%。

21.此外,在本发明的半导体发光元件的一技术方案中,可以是,还具备配置在上述阱层与上述p侧势垒层之间的p侧中间层;上述p侧中间层的组份由al

ykp1

ga

1-ykp1

as表示;ybp1≦xbp1 0.975ykp1 0.069、ybp1≧0.4xbp1 0.975ykp1 0.029以及0.2≦ykp1≦0.4的关系成立。

22.在关于p侧势垒层的al组份比ybp1而上述关系成立的情况下,p侧势垒层与p侧中间层之间的导带势能的能量差δec2为25mev以上,价带势能的能量差δev2为30mev以下。由此,能够抑制妨碍空穴向阱层的注入的情况,所以能够抑制工作电压的增大。此外,能够抑制电子从阱层的溢出。

23.此外,通过将p侧中间层的al组份比设为0.2以上、0.4以下,能够更高精度地控制垂直方向上的光分布,能够在使光约束系数增大的同时实现波导的低损耗化。

24.此外,通过在阱层与p侧势垒层之间配置与gaas基板大致晶格匹配的由algaas层构成的p侧中间层,能够使活性层附近的压缩应变的形成区域分散,所以能够抑制因压缩应变的集中造成的晶体性的下降。

25.进而,由于能够减小阱层与p侧中间层之间的价带势能的能量差δev,所以能够抑制高阶能级的轻空穴的形成。因而,能够抑制偏光比的下降。

26.此外,在本发明的半导体发光元件的一技术方案中,可以是,还具备配置在上述n侧第一势垒层与上述阱层之间的n侧第二势垒层;上述n侧第二势垒层的组份由

al

ybn2

ga

1-xbn2-ybn2

in

xbn2

as表示;ybn2≧xbn2 ybn1、ybn2≦0.4xbn2 0.975ybn1 0.061、xbn2≦0.15以及0.2≦ybn1≦0.35的关系成立。

27.在关于n侧第二势垒层的al组份比ybn2而上述关系成立的情况下,n侧第一势垒层与n侧第二势垒层之间的导带势能的能量差δec2为50mev以下,价带势能的能量差δev2为30mev以上。由此,能够抑制妨碍电子向阱层的注入的情况,所以能够抑制工作电压的增大。此外,能够抑制空穴从阱层的溢出。

28.此外,通过使n侧第一势垒层的al组份比较低而为0.2以上0.35以下,能够提高n侧第一势垒层的折射率,所以容易使垂直方向上的光分布靠近n型半导体层侧。因而,波导的低损耗化变得容易。

29.此外,在本发明的半导体发光元件的一技术方案中,可以是,还具备配置在上述阱层与上述n侧第二势垒层之间的n侧第三势垒层;上述n侧第三势垒层的组份由al

ybn3

ga

1-ybn3

as表示;ybn2≧xbn2 ybn3、ybn2≦0.4xbn2 0.975ybn3 0.061以及0.2≦ybn3≦0.35的关系成立。

30.在关于n侧第二势垒层的al组份比ybn2而上述关系成立的情况下,n侧第二势垒层与n侧第三势垒层之间的导带势能的能量差δec2为50mev以下。此外,通过将n侧第三势垒层的al组份比设为0.35以下,能够减小n侧第三势垒层的带隙能量。因而,能够抑制妨碍电子向阱层的注入的情况,所以能够抑制工作电压的增大。

31.此外,在关于n侧第二势垒层的al组份比ybn2而上述关系成立的情况下,n侧第二势垒层与n侧第三势垒层之间的价带势能的能量差δev2为0mev以上。因而,能够抑制空穴从阱层的溢出。

32.此外,通过使n侧第三势垒层的al组份比较低而为0.2以上0.35以下,能够使n侧第三势垒层的折射率变高,所以容易使垂直方向上的光分布靠近n型半导体层侧。因而,波导的低损耗化变得容易。

33.此外,在本发明的半导体发光元件的一技术方案中,可以是,还具备配置在上述p侧势垒层与上述p型包层之间、折射率比上述p型包层大的p侧导引层。

34.这样,通过在p侧势垒层上具备折射率比p型包层大的p侧导引层,能够高精度地控制垂直方向上的光分布,能够抑制光分布过度向n型半导体层侧偏倚的情况。因而,能够抑制向阱层的垂直方向上的光约束系数的变小以及阱层内的工作载流子密度的增大。即,能够抑制半导体发光元件的温度特性劣化。进而,如果将p侧导引层设为无掺杂,则能够抑制因杂质掺杂带来的自由载流子损耗的增大,所以能够实现波导的低损耗化。结果,能够实现温度特性良好的、斜率效率高的半导体激光元件。

35.此外,在本发明的半导体发光元件的一技术方案中,可以是,上述p侧导引层的组份由al

ygp1

ga

1-ygp1

as表示;ybp1≦xbp1 0.975ygp1 0.069、ybp1≧0.4xbp1 0.975ygp1 0.029以及0.2≦ygp1≦0.4的关系成立。

36.具有这样的组份的p侧导引层与gaas基板大致晶格匹配。由此,能够使具有压缩性的晶格失配的p侧势垒层的膜厚成为临界膜厚以下。因而,能够抑制p侧势垒层的晶体性下降。

37.进而,在阱层是包含al的四元半导体材料膜的情况下,活性层的压缩应变增大。因此,通过将与gaas基板大致晶格匹配的p侧导引层配置在p侧势垒层的上方,能够抑制活性

层附近的压缩应变的积蓄。此外,该情况下,由于重空穴与轻空穴的最低能级间势能增大,所以能够减小轻空穴与电子的复合概率。因而,能够减小由于轻空穴与电子的复合而引起的tm偏光成分,所以偏光比提高。

38.通过上述关系的成立,能够将p侧势垒层与p侧导引层之间的价带势能的能量差δev2抑制为30mev以下,并且将导带势能的能量差δec2增大到25mev以上,所以能够在抑制工作电压的增大的同时抑制电子从阱层的溢出。

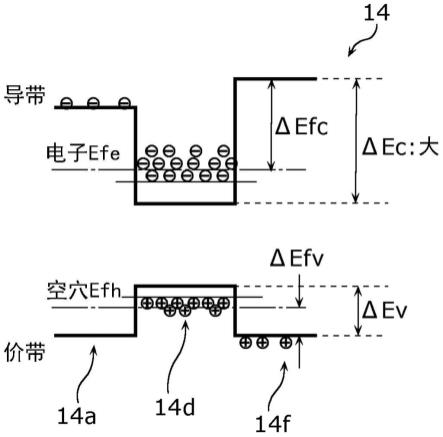

39.此外,通过将p侧导引层的al组份比ygp1设为0.2以上、0.4以下,能够更高精度地控制垂直方向上的光分布,能够在抑制光约束系数的大幅下降的同时实现波导的低损耗化。

40.此外,在本发明的半导体发光元件的一技术方案中,可以是,上述p侧导引层由(al

ygp2

ga

1-ygp2

)

0.5

in

0.5

p表示。

41.由此,在p侧导引层中,空位或zn、mg等杂质容易扩散。因而,通过使空位或杂质在半导体发光元件中扩散,在形成端面窗构造时,能够减少形成所需要的时间。此外,由于能够降低在使杂质扩散时使用的杂质的浓度,所以能够减少由杂质带来的光吸收。因而,能够抑制半导体发光元件的发光效率的下降。

42.此外,在本发明的半导体发光元件的一技术方案中,可以是,上述n型包层的组份由al

yn1

ga

1-yn1

as表示;上述p型包层的组份由al

yp1

ga

1-yp1

as表示;0《yn1《yp1《1的关系成立。

43.这样,由于n型包层的al组份比低于p型包层的al组份比,所以n型包层的折射率比p型包层的折射率大。随之,垂直方向上的光分布向n型包层侧偏倚。如上述那样,由于光从半导体发光元件的波导受到的自由载流子损耗在掺杂浓度比n型半导体层高的p型半导体层中变大,所以通过使垂直方向的光分布靠近n型半导体层,能够实现波导损耗的减少。

44.通过使光分布向n型包层侧偏倚,向作为发光层的阱层的垂直方向上的光约束系数下降,所以如上述那样,电子容易从阱层向p侧势垒层溢出。但是,在本发明的半导体发光元件中,由于p侧势垒层与n侧第一势垒层的导带势能的能量差δec较大,所以能够抑制电子的溢出。因而,能够实现能够在抑制工作电压的增大的同时使温度特性比以往的半导体发光元件提高、并且斜率效率高的低工作电流的半导体发光元件。

45.此外,在本发明的半导体发光元件的一技术方案中,可以是,上述n型包层的组份由(al

yn2

ga

1-yn2

)

0.5

in

0.5

p表示;上述p型包层的组份由(al

yp2

ga

1-yp2

)

0.5

in

0.5

p表示;0《yn2《yp2《1的关系成立。

46.通过具备具有这样的组份的n型包层及p型包层,在n型包层及p型包层中,空位或zn、mg等杂质容易扩散。因而,通过在半导体发光元件中使空位或杂质扩散,在形成端面窗构造时,能够减少形成所需要的时间。此外,由于能够降低在使杂质扩散时使用的杂质的浓度,所以能够减少由杂质带来的光吸收。因而,能够抑制半导体发光元件的发光效率的下降。

47.此外,通过0《yn2《yp2《1的关系的成立,能够使p型包层的折射率比n型包层的折射率降低。因而,能够使激光的强度分布向n型包层侧偏倚。即,能够减少在p型包层中传播的激光,所以能够降低由p型包层的杂质引起的自由载流子损耗。由此,能够实现波导的低损耗化。

48.此外,在本发明的半导体发光元件的一技术方案中,可以是,上述阱层的组份由

al

yw

ga

1-xw-yw

in

xw

as表示;0≦yw《1以及0《xw《1的关系成立。

49.这样,在阱层的组份是al

yw

ga

1-xw-yw

in

xw

as的情况下,通过调整阱层的al组份比、ga组份比及in组份比,能够调整阱层的应变的大小、阱层与各势垒层的导带及价带的能量差。因而,能够进行半导体发光元件的振荡波长的调整以及电子从阱层的溢出的控制。

50.此外,在本发明的半导体发光元件的一技术方案中,可以是,进而,0《yw《1的关系成立。

51.这样,阱层包含al,从而在阱层具有压缩应变的情况下,能够减少在阱层的价带中形成的轻空穴数。这里,轻空穴(lh)与电子复合而生成的光,与重空穴(hh)与电子复合而生成的光相比,tm模式光的比例较大。因而,通过减少在阱层的价带中形成的轻空穴数,能够降低轻空穴与电子的复合概率,所以能够增大来自半导体发光元件的输出光的偏光比(te模式光的强度相对于tm模式光的强度的比)。

52.此外,在本发明的半导体发光元件的一技术方案中,可以是,上述基板是gaas基板。

53.这样,通过使用gaas基板作为基板,从而在作为势垒层及阱层而使用algainas类的四元半导体材料的情况下,能够使阱层产生压缩应变。在阱层具有压缩应变的情况下,通过调整阱层的组份,能够减少在阱层的价带中形成的轻空穴数。因而,能够降低轻空穴与电子的复合概率,所以能够增大来自半导体发光元件的输出光的偏光比。

54.此外,在本发明的半导体发光元件的一技术方案中,可以是,上述n型包层的带隙能量比上述p型包层的带隙能量小。

55.由此,n型包层的折射率比p型包层的折射率高。因此,与基板的主面垂直的方向上的光分布向n型包层侧偏倚。这里,在n型半导体层中,通过将n型杂质的掺杂浓度设为1

×

10

16

cm-3

以上、1

×

10

18

cm-3

以下的范围,能够抑制电阻值。另一方面,在p型半导体层中,如果不将p型杂质的掺杂浓度设为1

×

10

18

cm-3

以上则无法抑制电阻值。因而,光从半导体发光元件的波导受到的自由载流子损耗在掺杂浓度比n型半导体层高的p型半导体层中变大。因此,通过如本发明的半导体发光元件那样使光分布向n型包层侧偏倚,能够降低波导损耗。

56.通过使光分布向n型包层侧偏倚,向作为发光层的阱层的垂直方向(与基板的主面垂直的方向)上的光约束系数下降。因此,在半导体发光元件中激光振荡的情况下,阱层中的工作载流子增大,有效质量比空穴小的电子容易从阱层向p侧势垒层溢出。但是,在本发明的半导体发光元件中,由于p侧势垒层与n侧第一势垒层的导带势能的能量差δec较大,所以能够抑制电子的溢出。因而,能够实现能够在抑制工作电压的增大的同时使温度特性比以往的半导体发光元件提高、并且斜率效率高的低工作电流的半导体发光元件。

57.此外,在本发明的半导体发光元件的一技术方案中,可以是,在上述活性层的光射出端面部,形成有端面窗构造。

58.在alas、gaas及inas中,inas晶格常数最大,带隙能量最小。在如本发明的半导体发光元件那样对阱层及各势垒层采用algainas类的四元半导体材料而得到希望的带隙能量的情况下,与对阱层采用由ingaas构成的半导体材料得到希望的带隙能量的情况相比,由于由algainas构成的阱层的in的含有率提高,所以阱层的压缩应变变大。

59.此外,关于使用氮化物类的半导体材料的情况,在aln、gan及inn中,inn晶格常数最大,并且带隙能量最小。该情况下,对阱层及各势垒层采用包含由algainn构成的四元类

的半导体材料的层而得到希望的带隙能量的情况下,与对阱层采用由ingan或algan构成的半导体材料得到希望的带隙能量的情况相比,由algainn构成的阱层的in的含有率提高,所以阱层的压缩应变变大。

60.根据以上,在对阱层及各势垒层采用algainas、algainn等的构造中,在使空位或杂质扩散到半导体发光元件的光射出端面部的情况下,由于使阱层的应变能量变小,阱层的in原子容易与相对于层叠方向存在于iii族的晶格位置的al原子及ga原子交换。因而,阱层的带隙能量容易变大。

61.结果,光密度较大的光射出端面部的阱层的带隙能量变大,能够形成所谓的窗构造。由此,即使光射出端面部的带隙能量通过发热而变小,也能够维持光射出端面部的阱层的光吸收较小的状态。因而,能够抑制由于光射出端面部吸收光而引起的cod(catastrophic optical damage)的发生。

62.进而,如果通过空位扩散形成窗构造,则与通过杂质部扩散形成窗构造的情况相比,能够抑制因杂质的存在造成的自由载流子损耗的发生,所以能够抑制斜率效率的下降。

63.此外,在本发明的半导体发光元件的一技术方案中,可以是,与在上述活性层中没有形成上述端面窗构造的部分的带隙能量相比,在上述活性层中形成有上述端面窗构造的部分的带隙能量较大。

64.由此,即使光射出端面部的带隙能量通过发热而变小,也能够维持光射出端面部的阱层的光吸收较小的状态。因而,能够抑制由于光射出端面部吸收光而引起的cod的发生。

65.此外,为了解决上述课题,本发明的半导体发光元件的制造方法的一技术方案包括:准备基板的工序;在上述基板的上方形成n型包层的工序;在上述n型包层的上方形成活性层的工序;在上述活性层的上方形成p型包层的工序;以及在上述活性层形成端面窗构造的工序;上述活性层具有:阱层;n侧第一势垒层,配置在上述阱层的上述n型包层侧;以及p侧势垒层,配置在上述阱层的上述p型包层侧;上述p侧势垒层包含in;上述n侧第一势垒层的in组份比低于上述p侧势垒层的in组份比;上述n侧第一势垒层的带隙能量比上述p侧势垒层的带隙能量小;在形成上述端面窗构造的工序中,使空位或杂质在上述活性层中扩散。

66.由此,能够制造n侧第一势垒层的in组份比小于p侧势垒层的in组份比、并且n侧第一势垒层的带隙小于p侧势垒层的带隙的半导体发光元件。根据这样的半导体发光元件,能够使p侧势垒层与n侧第一势垒层的导带势能的能量差δec比p侧势垒层与n侧第一势垒层的价带势能的能量差δev大。因而,能够抑制空穴的电气传导所需要的电压的增大即半导体发光元件的工作电压的增大,并且抑制电子从阱层的溢出。

67.此外,例如,在对阱层及各势垒层采用algainas、algainn等的构造中,在半导体发光元件的光射出端面部使空位或杂质扩散了的情况下,使阱层的应变能量变小,所以阱层的in原子容易与相对于层叠方向存在于iii族的晶格位置的al原子及ga原子交换。因而,阱层的带隙能量容易变大。

68.结果,光密度较大的光射出端面部的阱层的带隙能量变大,能够形成端面窗构造。由此,即使光射出端面部的带隙能量通过发热而变小,也能够维持光射出端面部的阱层的光吸收较小的状态。因而,能够抑制由于光射出端面部吸收光而引起的cod的发生。

69.发明效果

70.根据本发明,能够提供能够在抑制工作电压的同时抑制从阱层的电子的溢出的半导体发光元件等。

附图说明

71.图1是表示实施方式1的半导体发光元件的整体结构的示意性剖视图。

72.图2是表示实施方式1的半导体发光元件具备的活性层的详细结构的示意性剖视图。

73.图3是表示比较例的活性层的能带构造的概要的示意图。

74.图4是表示实施方式1的活性层的能带构造的概要的示意图。

75.图5是表示实施方式1的活性层的n侧第一势垒层与p侧势垒层的导带势能及价带势能各自的能量差的示意图。

76.图6是表示algainas类材料的带隙能量(eg)的in及al组份比依赖性的曲线图。

77.图7是表示algainas类材料的价带势能的in及al组份比依赖性的曲线图。

78.图8是表示algainas类材料的导带势能的in及al组份比依赖性的曲线图。

79.图9是表示algainas类材料与al

0.2

ga

0.8

as之间的导带势能的能量差δec2及价带势能的能量差δev2与algainas类材料的组份的关系的曲线图。

80.图10是表示algainas类材料与al

0.3

ga

0.7

as之间的导带势能的能量差δec2及价带势能的能量差δev2与algainas类材料的组份的关系的曲线图。

81.图11是表示algainas类材料与al

0.4

ga

0.6

as之间的导带势能的能量差δec2及价带势能的能量差δev2与algainas类材料的组份的关系的曲线图。

82.图12是表示比较例1的半导体发光元件的电流-电压特性的模拟结果的曲线图。

83.图13是表示比较例2的半导体发光元件的电流-电压特性的模拟结果的曲线图。

84.图14是表示实施方式1的半导体发光元件的电流-电压特性的模拟结果的曲线图。

85.图15是表示比较例1、比较例2及实施方式1的各半导体发光元件的四元势垒层的al组份比与工作电压的关系的曲线图。

86.图16是表示实施方式1的阱层的al组份比与重空穴能级及轻空穴能级的关系的计算结果的第一曲线图。

87.图17是表示实施方式1的阱层的al组份比与重空穴能级及轻空穴能级的关系的计算结果的第二曲线图。

88.图18是表示实施方式1的阱层的al组份比与重空穴能级及轻空穴能级的关系的计算结果的第三曲线图。

89.图19是表示实施方式1的变形例1的半导体发光元件的能带构造的概要的示意图。

90.图20是表示实施方式1的变形例1的p侧势垒层与p侧导引层之间的导带势能及价带势能各自的能量差δec2及δev2的示意图。

91.图21是表示实施方式1的变形例1的p侧势垒层的al组份比与能量差δec2及δev2的关系的曲线图。

92.图22是表示实施方式1的变形例2的半导体发光元件的能带构造的概要的示意图。

93.图23是表示实施方式1的变形例3的半导体发光元件的能带构造的概要的示意图。

94.图24是表示实施方式1的变形例4的半导体发光元件的能带构造的概要的示意图。

95.图25是表示实施方式1的变形例5的半导体发光元件的能带构造的概要的示意图。

96.图26是表示实施方式1的变形例6的半导体发光元件的能带构造的概要的示意图。

97.图27是表示实施方式1的变形例7的半导体发光元件的光射出端面部的结构的剖视图。

98.图28是表示实施方式2的半导体发光元件的整体结构的示意性剖视图。

99.图29是表示实施方式3的半导体发光元件的整体结构的示意性剖视图。

100.图30是表示实施方式3的半导体发光元件的各部的尺寸的示意性剖视图。

101.图31是表示实施方式3的半导体发光元件的安装状态的示意性剖视图。

102.图32是表示实施方式3的半导体发光元件的与活性层的x轴方向的位置对应的剪切应力σxy的分布的曲线图。

103.图33是表示实施方式4的半导体发光元件的制造方法的工序的流程图。

具体实施方式

104.以下,参照附图对本发明的实施方式进行说明。另外,以下说明的实施方式均表示本发明的一具体例。因而,以下实施方式中表示的数值、形状、材料、构成要素、构成要素的配置位置及连接形态等作为一例而并不意欲限定本发明。

105.此外,各图是示意图,并不一定严格地图示。因而,在各图中比例尺等并不一定一致。另外,在各图中,对于实质上相同的结构赋予相同附图标记,将重复的说明省略或简化。

106.此外,在本说明书中,用语“上方”及“下方”不是指绝对性的空间识别中的上方(铅直上方)及下方(铅直下方),而用作基于层叠结构中的层叠顺序而由相对位置关系规定的用语。此外,用语“上方”及“下方”不仅适用于将两个构成要素相互隔开间隔配置而在两个构成要素之间存在其他构成要素的情况,还适用于两个构成要素以相互相接的状态配置的情况。

107.(实施方式1)

108.对实施方式1的半导体发光元件进行说明。

109.[1-1.整体结构]

[0110]

首先,使用图1及图2对本实施方式的半导体发光元件的整体结构进行说明。图1是表示本实施方式的半导体发光元件1的整体结构的示意性剖视图。图2是表示本实施方式的半导体发光元件1具备的活性层14的详细结构的示意性剖视图。

[0111]

半导体发光元件1是通过被施加电压而发光的元件。在本实施方式中,半导体发光元件1是射出900nm以上980nm以下左右的波长的激光的半导体激光元件。更具体地讲,半导体发光元件1射出915nm左右的波长的激光。图1表示半导体发光元件1的与激光的谐振方向垂直的剖面。半导体发光元件1的谐振器长即激光的谐振方向的端面间的距离没有特别限定,在本实施方式中是2mm以上。此外,半导体发光元件1的谐振器长也可以是4mm以上。这样,通过使谐振器长变长,能够降低半导体发光元件1的热阻,所以能够使散热性提高。因而,能够增大半导体发光元件1热饱和的光输出。如图1所示,半导体发光元件1具备基板10、缓冲层11、n型包层12、活性层14、p型包层17、电流狭窄层19、接触层18、n侧电极31和p侧电极32。

[0112]

基板10是作为半导体发光元件1的基台的板状部件。在本实施方式中,基板10是n

型gaas基板。

[0113]

缓冲层11是用来抑制由基板10与n型包层12的晶格失配引起的应变的层。缓冲层11的结构没有特别限定,在本实施方式中,缓冲层11是膜厚0.5μm的n型gaas层。在缓冲层11中,作为杂质而掺杂有浓度3

×

10

17

cm-3

的si。

[0114]

n型包层12是配置在基板10上方的n型的包层。n型包层12是与活性层14相比折射率低并且带隙能量(bandgap energy)高的层。n型包层12的结构没有特别限定,在本实施方式中,n型包层12是膜厚4μm的n型al

0.305

ga

0.695

as层。在n型包层12中,作为杂质而掺杂有浓度1

×

10

18

cm-3

的si。

[0115]

活性层14配置在n型包层12的上方,是具有量子阱构造的发光层。在本实施方式中,活性层14如图2所示,具有n侧第一势垒层14a、阱层14d和p侧势垒层14f。

[0116]

阱层14d是配置在n侧第一势垒层14a与p侧势垒层14f之间的量子阱层。在本实施方式中,阱层14d是膜厚6nm的al

0.08

ga

0.67

in

0.25

as层。

[0117]

n侧第一势垒层14a是配置在阱层14d的n型包层12侧的势垒层。在本实施方式中,n侧第一势垒层14a是膜厚7nm的al

0.27

ga

0.73

as层。

[0118]

p侧势垒层14f是配置在阱层14d的p型包层17侧的势垒层。在本实施方式中,p侧势垒层14f是膜厚7nm的al

0.45

in

0.10

ga

0.45

as层。p侧势垒层14f的膜厚被设定为,使得在p侧势垒层14f的p型包层17侧的端面中,阱层14d内的电子的波函数衰减到小于最大振幅的1%。由此,能够抑制阱层14d内的电子因隧道效应而穿透p侧势垒层14f、即产生漏电流。此外,p侧势垒层14f具有压缩应变,如果超过临界膜厚则发生晶格缺陷。因此,p侧势垒层14f的膜厚也可以是3nm以上以便能够抑制阱层14d的电子因隧道效应而穿透,并且是临界膜厚以下。这里,如果设p侧势垒层14f相对于基板10的晶格失配的绝对值为q%,则临界膜厚可以设定为20/q。

[0119]

p型包层17是配置在活性层14上方的p型的包层。p型包层17是与活性层14相比折射率低并且带隙能量高的层。p型包层17的结构没有特别限定,在本实施方式中,p型包层17是膜厚0.7μm的p型al

0.7

ga

0.3

as层。在p型包层17中,作为杂质而掺杂有浓度2

×

10

18

cm-3

的c(碳原子)。

[0120]

接触层18是配置在p型包层17上方的层,与p侧电极32相接。接触层18的结构没有特别限定,在本实施方式中,接触层18是膜厚0.4μm的p型gaas层。在接触层18中,作为杂质而掺杂有浓度2

×

10

18

cm-3

的c。

[0121]

电流狭窄层19是配置在p型包层17上方的层,其发挥功能以使得在半导体发光元件1中电流在窄区域中集中地流动,即,将电流约束在一部分区域中。在本实施方式中,电流狭窄层19是配置在p型包层17与接触层18之间的n型的半导体层。电流狭窄层19沿着半导体发光元件1的激光谐振方向具有长尺寸状的开口部19a。在开口部19a中配置接触层18。由此,仅在电流狭窄层19的开口部19a中流过电流。即,电流被约束在开口部19a。随之,在活性层14中的开口部19a下方的区域中流过电流,所以该区域成为发光部。电流狭窄层19的结构没有特别限定,在本实施方式中,电流狭窄层19是膜厚0.25μm的n型gaas层。在电流狭窄层19中,作为杂质而掺杂有浓度2

×

10

18

cm-3

的si。

[0122]

n侧电极31是配置在基板10的下方的主面(即,基板10的主面中的层叠有半导体层的主面的背侧的主面)上的电极。n侧电极31的结构没有特别限定,在本实施方式中,n侧电

极31包括从基板10侧依次层叠的膜厚90nm的auge膜、膜厚20nm的ni膜、膜厚50nm的au膜、膜厚100nm的ti膜、膜厚50nm的pt膜、膜厚50nm的ti膜、膜厚100nm的pt膜以及膜厚500nm的au膜。

[0123]

p侧电极32是配置在接触层18上方的电极。p侧电极32与接触层18欧姆接触。p侧电极32的结构没有特别限定,在本实施方式中,p侧电极32包括从接触层18侧依次层叠的膜厚50nm的ti膜、膜厚150nm的pt膜以及膜厚50nm的au膜。

[0124]

[1-2.作用及效果]

[0125]

接着,对本实施方式的半导体发光元件1的作用及效果进行说明。

[0126]

[1-2-1.活性层的作用及效果]

[0127]

首先,一边与比较例的半导体发光元件的作用进行比较,一边使用图3及图4说明本实施方式的半导体发光元件1的活性层14的作用及效果的概要。图3及图4分别是表示比较例及本实施方式的各活性层的能带构造的概要的示意图。另外,在图3及图4中,还一并表示了p侧势垒层与阱层的导带势能的能量差δec及价带势能的能量差δev、以及电子的费米能级efe及空穴的费米能级efh。此外,在图4中,还表示了电子的费米能级efe与p侧势垒层14f的导带势能的能量差δefc、以及空穴的费米能级efh与p侧势垒层14f的价带势能的能量差δefv。

[0128]

图3所示的比较例的活性层与本实施方式的活性层14同样,具有n侧第一势垒层14a、阱层14d和p侧势垒层。比较例的p侧势垒层的组份与本实施方式的p侧势垒层14f的组份不同。比较例的p侧势垒层是algaas层,不包含in。

[0129]

关于具有这样的p侧势垒层的比较例的活性层,研究为了抑制电子的溢出而增大能量差δec的情况。该情况下,通过使p侧势垒层的al组份比变大,能够增大能量差δec。但是,随之能量差δev也增大。因而,空穴为了越过p侧势垒层而需要的能量也增大,所以半导体发光元件的工作电压增大。

[0130]

另一方面,在图4所示的本实施方式的活性层14中,p侧势垒层14f包含in,n侧第一势垒层14a的in组份比低于p侧势垒层14f的in组份比。此外,n侧第一势垒层14a的带隙能量比p侧势垒层14f的带隙能量小。通过这样的活性层14,如图4所示,能够在抑制能量差δev及δefv的增大的同时增大能量差δec及δefc。因而,能够通过抑制能量差δev及δefv的增大来抑制半导体发光元件1的工作电压的增大,并且能够通过增大能量差δec及δefc来抑制电子的溢出。

[0131]

对于上述的本实施方式的活性层14的特性,使用图5~图8详细地进行说明。图5是表示本实施方式的活性层14的n侧第一势垒层14a和p侧势垒层14f的导带势能及价带势能各自的能量差的示意图。如图5所示,定义n侧第一势垒层14a和p侧势垒层14f的导带势能及价带势能各自的能量差δecb及δevb。图6、图7及图8分别是表示algainas类材料的带隙能量(eg)、价带势能以及导带势能的in及al组份比依赖性的曲线图。在图6、图7及图8中,纵轴分别表示带隙能量、价带势能及导带势能,横轴分别表示in组份比。此外,在图6~图8中,表示了以al组份比为参数且使其从0到1每次0.1地变化的情况的曲线图。

[0132]

如图6所示,in组份比越大则带隙能量越小,al组份比越大则带隙能量越大。例如,ga

0.7

in

0.3

as的带隙能量约1.0ev与al

0.4

in

0.6

as的带隙能量约1.23ev的差(图6所示的δeg)、即能量差δecb与δevb的和为约0.23ev。这样,在algainas类材料中,即使在增大了in组份

比的情况下,也能够通过增大al组份比而使带隙能量变大。

[0133]

如图7及图8所示,in组份比越大,则价带势能越高,导带势能越低。另一方面,al组份比越大,则价带势能越低,导带势能越高。此外,对应于al组份比及in组份比的变化,导带势能的变化量比价带势能的变化量大。例如,ga

0.7

in

0.3

as的价带势能约-5.35ev与al

0.4

in

0.6

as的价带势能约-5.41ev的能量差δecb是约0.16ev,相对于此,能量差δevb是约0.06ev。该情况下,能量差δecb是能量差δevb的2.7倍。这样,在algainas类材料中,通过调整al组份比及in组份比,能够使价带势能比导带势能更大地变化。因而,在n侧第一势垒层14a及p侧势垒层14f中,通过采用algainas类材料且调整各组份,如图4所示,能够在抑制能量差δev及δefv的增大的同时使能量差δec及δefc增大。在本实施方式中,n侧第一势垒层14a的in组份比低于p侧势垒层14f的in组份比,并且,n侧第一势垒层14a的带隙能量比p侧势垒层14f的带隙能量小。由此,能够在抑制能量差δev及δefv的增大的同时将能量差δec及δefc增大。因而,能够在抑制空穴的电传导所需要的电压的增大即半导体发光元件的工作电压的增大的同时,抑制电子从阱层的溢出。

[0134]

此外,如果设n侧第一势垒层14a的al组份比及in组份比分别为ybn1及xbn1,则n侧第一势垒层14a的组份由al

ybn1

ga

1-xbn1-ybn1

in

xbn1

as表示。如果设p侧势垒层14f的al组份比及in组份比分别为ybp1及xbp1,则p侧势垒层14f的组份由al

ybp1

ga

1-xbp1-ybp1

in

xbp1

as表示。在本实施方式中,关于这些组份比,0≦ybn1≦1,0≦xbn1《1,0《ybp1《1,0《xbp1《1以及xbn1《xbp1的关系成立。通过采用具有这样的组份的n侧第一势垒层14a及p侧势垒层14f,能够使n侧第一势垒层14a的in组份比小于p侧势垒层14f的in组份比,并且使n侧第一势垒层14a的带隙小于p侧势垒层14f的带隙。

[0135]

此外,在本实施方式中,关于al组份比,ybn1《ybp1的关系成立。由此,p侧势垒层14f与n侧第一势垒层14a的导带势能的能量差δec增大,所以能够进一步抑制电子从阱层14d的溢出。

[0136]

此外,在本实施方式中,如果设阱层14d的al组份比及in组份比分别为xw及yw,则阱层14d的组份由al

yw

ga

1-xw-yw

in

xw

as表示,0≦yw《1及0《xw《1的关系成立。这样,在阱层14d的组份是al

yw

ga

1-xw-yw

in

xw

as的情况下,通过调整阱层14d的al组份比、ga组份比及in组份比,能够调整阱层14d的应变的大小、以及阱层14d与各势垒层之间的导带及价带的势能差。因而,能够调整半导体发光元件1的振荡波长并且控制电子从阱层14d的溢出。

[0137]

接着,对于本实施方式的n侧第一势垒层14a及p侧势垒层14f的al组份比及in组份比的关系,使用图9~图11更详细地进行说明。图9、图10及图11分别是表示algainas类材料与al

0.2

ga

0.8

as、al

0.3

ga

0.7

as及al

0.4

ga

0.6

as之间的导带势能的能量差δec2及价带势能的能量差δev2与algainas类材料的组份的关系的曲线图。图9~图11的横轴及纵轴分别表示algainas类材料的in组份比x及al组份比y。在图9~图11中,分别用虚线及实线来表示能量差δec2及能量差δev2为规定值的in组份比x与al组份比y的关系。例如,在图9中,分别用虚线来表示能量差δec2为-50mev、-20mev、0mev、25mev、50mev、75mev、100mev、150mev及200mev的in组份比x与al组份比y的关系。此外,在图9中,分别用实线表示能量差δev2为-40mev、-20mev、0mev、30mev、40mev、60mev、80mev及100mev的in组份比x与al组份比y的关系。

[0138]

例如,为了抑制电子从阱层14d的溢出,为了使由al

0.2

ga

0.8

as构成的n侧第一势垒

层14a与由alyga

1-x-y

in

x

as构成的p侧势垒层14f的导带势能的能量差为25mev以上,采用与图9所示的δec2为25mev的直线y=0.4x 0.225上及其上方的区域中的点对应的in组份比x及al组份比y即可。即,关于in组份比x及al组份比y,y≧0.4x 0.225的关系成立即可。

[0139]

此外,为了抑制半导体发光元件1的工作电压的增大,为了使由al

0.2

ga

0.8

as构成的n侧第一势垒层14a与由alyga

1-x-y

in

x

as构成的p侧势垒层14f的价带势能的能量差为30mev以下,采用与图9所示的δev2为30mev的直线y=x 0.265上及其下方的区域中的点对应的in组份比x及al组份比y即可。即,关于in组份比x及al组份比y,y≦x 0.265的关系成立即可。

[0140]

为了进一步抑制半导体发光元件1的工作电压的增大,为了使由al

0.2

ga

0.8

as构成的n侧第一势垒层14a和由alyga

1-x-y

in

x

as构成的p侧势垒层14f的价带势能的能量差为0mev以下,如图9所示,关于in组份比x及al组份比y,y≦x 0.2的关系成立即可。此外,为了进一步抑制电子从阱层14d的溢出,为了使由al

0.2

ga

0.8

as构成的n侧第一势垒层14a与由alyga

1-x-y

in

x

as构成的p侧势垒层14f的导带势能的能量差为50mev以上,如图9所示,关于in组份比x及al组份比y,y≧0.4x 0.255的关系成立即可。

[0141]

因而,在采用由al

0.2

ga

0.8

as构成的n侧第一势垒层14a的情况下,为了在抑制半导体发光元件1的工作电压的增大(δev2≦30mev)的同时抑制电子从阱层14d的溢出(δec2≧25mev),关于由alyga

1-x-y

in

x

as构成的p侧势垒层14f的in组份比x及al组份比y,y≧0.4x 0.225及y≦x 0.265的关系成立即可。该关系成立的in组份比x及al组份比y的组合与图9所示的被施以阴影的区域的点对应。此外,为了进一步抑制半导体发光元件1的工作电压的增大(δev2≦0mev),进一步使y≦x 0.2的关系成立即可。该关系成立的in组份比x及al组份比y的组合,与图9所示的被施以阴影的区域中的被更密地以圆点施以阴影的区域的点对应。此外,为了进一步抑制电子从阱层14d的溢出(δec2≧50mev),进一步使y≧0.4x 0.255的关系成立即可。

[0142]

在采用由al

0.3

ga

0.7

as构成的n侧第一势垒层14a的情况下,也与采用由al

0.2

ga

0.8

as构成的n侧第一势垒层14a的情况同样,能够根据图10所示的曲线图决定p侧势垒层14f的组份。即,为了在抑制半导体发光元件1的工作电压的增大(δev2≦30mev)的同时抑制电子从阱层14d的溢出(δec2≧25mev),如图10所示,关于由alyga

1-x-y

in

x

as构成的p侧势垒层14f的in组份比x及al组份比y,y≧0.4x 0.32及y≦x 0.36的关系成立即可。该关系成立的in组份比x及al组份比y的组合与图10所示的被施以阴影的区域的点对应。此外,为了进一步抑制半导体发光元件1的工作电压的增大(δev2≦0mev),y≦x 0.3的关系成立即可。该关系成立的in组份比x及al组份比y的组合与图10所示的被施以阴影的区域中的被更密地以圆点施以阴影的区域的点对应。此外,为了进一步抑制电子从阱层14d的溢出(δec2≧50mev),进一步使y≧0.4x 0.355的关系成立即可。

[0143]

在采用由al

0.4

ga

0.6

as构成的n侧第一势垒层14a的情况下,也与采用由al

0.2

ga

0.8

as构成的n侧第一势垒层14a的情况同样,能够根据图11所示的曲线图决定p侧势垒层14f的组份。即,为了在抑制半导体发光元件1的工作电压的增大(δev2≦30mev)的同时抑制电子从阱层14d的溢出(δec2≧25mev),如图11所示,关于由alyga

1-x-y

in

x

as构成的p侧势垒层14f的in组份比x及al组份比y,y≧0.4x 0.42及y≦x 0.46的关系成立即可。该关系成立的in组份比x及al组份比y的组合与图11所示的被施以阴影的区域的点对应。此外,为了进一步抑

efficiency)高的低工作电流的半导体发光元件。

[0160]

此外,如果设n型包层12的al组份比为yn1,则n型包层12的组份由al

yn1

ga

1-yn1

as表示,如果设p型包层17的al组份比为yp1,则p型包层17的组份由al

yp1

ga

1-yp1

as表示,0《yn1《yp1《1的关系成立。

[0161]

这样,由于n型包层12的al组份比yn1比p型包层17的al组份比yp1小,所以n型包层12的折射率比p型包层17的折射率大。随之,垂直方向上的光分布向n型包层12侧偏倚。如上述那样,光从半导体发光元件1的波导受到的自由载流子损耗在掺杂浓度比n型半导体层高的p型半导体层中变大,因此通过使垂直方向的光分布靠近n型半导体层,能够实现波导损耗的减小。

[0162]

由于光分布向n型包层12侧偏倚,向作为发光层的阱层14d的垂直方向上的光约束系数下降,所以如上述那样,电子容易从阱层14d向p侧势垒层14f溢出。但是,在本实施方式的半导体发光元件1中,由于p侧势垒层14f与n侧第一势垒层14a的导带势能的能量差δec较大,所以能够抑制电子的溢出。因而,能够实现能够在抑制工作电压的增大的同时比以往的半导体发光元件提高温度特性、并且斜率效率高的低工作电流的半导体发光元件1。

[0163]

[1-2-3.电流-电压特性]

[0164]

接着,关于本实施方式的半导体发光元件1的电流-电压特性,一边与比较例比较一边使用图12~图15进行说明。图12、图13及图14分别是表示比较例1、比较例2及本实施方式的各半导体发光元件的电流-电压特性的模拟结果的曲线图。在图12~图14的各曲线图中,横轴及纵轴分别表示向半导体发光元件施加的电压及电流。图15是表示比较例1、比较例2及本实施方式的各半导体发光元件的四元势垒层的al组份比与工作电压的关系的曲线图。图15的曲线图的横轴表示四元势垒层的al组份比,纵轴表示工作电压。另外,图15所示的工作电压表示工作电流(即,施加于半导体发光元件的电流)为8a的情况下的工作电压。

[0165]

比较例1的半导体发光元件在n侧第一势垒层及p侧势垒层是由相同的四元势垒层即algainas类材料形成的势垒层这一点上与本实施方式的半导体发光元件1不同。作为四元势垒层的组份,采用了al

0.4

ga

0.5

in

0.1

as、al

0.45

ga

0.45

in

0.1

as、al

0.5

ga

0.4

in

0.1

as及al

0.55

ga

0.35

in

0.1

as。此外,在图12中,还一并表示了采用组份为al

0.3

ga

0.7

as的三元势垒层的情况下的模拟结果。此外,阱层的组份是al

0.04

ga

0.77

in

0.19

as。

[0166]

比较例2的半导体发光元件在仅n侧第一势垒层是与比较例1同样的四元势垒层、p侧势垒层是三元势垒层这一点上与本实施方式的半导体发光元件1不同。p侧势垒层的组份是al

0.3

ga

0.7

as。此外,在图13中,还一并表示了作为n侧第一势垒层而采用组份为al

0.3

ga

0.7

as的三元势垒层的情况下的模拟结果。此外,阱层的组份与比较例1同样是al

0.04

ga

0.77

in

0.19

as。

[0167]

在本实施方式的半导体发光元件1中,仅p侧势垒层14f是与比较例1同样的四元势垒层,n侧第一势垒层14a是组份为al

0.3

ga

0.7

as的三元势垒层。此外,在图14中,还一并表示了作为p侧势垒层14f而采用组份为al

0.3

ga

0.7

as的三元势垒层的情况下的模拟结果。此外,阱层14d的组份与比较例1及比较例2同样是al

0.04

ga

0.77

in

0.19

as。

[0168]

如图12~图15所示,在本实施方式的半导体发光元件1中,与比较例1及比较例2的半导体发光元件相比能够降低工作电压。特别是,四元势垒层中的al组份比越大,工作电压的降低效果越显著。在本实施方式的半导体发光元件1中,由于即使p侧势垒层14f的al组份

比变动也能够抑制工作电压的增大,所以能够扩大p侧势垒层14f的组份控制的自由度。由此,能够改善半导体发光元件1的制造中的成品率。

[0169]

此外,在本实施方式的半导体发光元件1中,由于仅将p侧势垒层14f设为四元势垒层,所以与将n侧第一势垒层14a及p侧势垒层14f双方设为四元势垒层的情况相比,能够抑制由各势垒层的组份偏差引起的工作电压的增大。

[0170]

[1-2-4.偏光比增大效果]

[0171]

接着,对本实施方式的偏光比(te模式光的强度相对于tm模式光的强度的比)增大效果进行说明。

[0172]

在半导体发光元件中,在轻空穴与电子复合时,通过发生tm模式光而偏光比减小。此外,在以往的半导体发光元件的高输出工作时,由于活性层温度及工作载流子密度上升,所以轻空穴数增大,tm模式光成分增大,所以偏光比下降。

[0173]

此外,如果半导体发光元件的谐振器长变长,则与安装半导体发光元件的子装配体(submount)等的接触面积变大。因此,由半导体发光元件的翘曲、安装用的焊料的凹凸等引起的应变对于活性层的影响变大。随之,活性层的能带构造变化,轻空穴数可能增大。

[0174]

因此,在本实施方式中,通过增大阱层14d的压缩应变,将轻空穴的最低能级与重空穴的最低能级的能量差增大。由此,减少存在于轻空穴的空穴数,减小轻空穴与电子的复合概率。以下,关于本实施方式的阱层14d的重空穴能级及轻空穴能级与阱层14d的组份的关系,使用图16~图18进行说明。

[0175]

图16~图18是表示本实施方式的阱层14d的al组份比与重空穴(hh)能级及轻空穴(lh)能级的关系的计算结果的曲线图。另外,在各图的曲线图的下方,添加了表示在计算中使用的al组份比及in组份比的组合与对应于各组合的晶格失配的表。在图16~图18中分别表示采用不同的n侧第一势垒层14a及p侧势垒层14f的情况下的关系。在图16中,表示了作为n侧第一势垒层14a及p侧势垒层14f而分别采用al

0.24

ga

0.76

as及al

0.35

ga

0.55

in

0.1

as的情况下的关系。在图17中,表示了作为n侧第一势垒层14a及p侧势垒层14f而分别采用al

0.27

ga

0.73

as及al

0.37

ga

0.53

in

0.1

as的情况下的关系。在图18中,表示了作为n侧第一势垒层14a及p侧势垒层14f而分别采用al

0.3

ga

0.7

as及al

0.4

ga

0.5

in

0.1

as的情况下的关系。此外,作为阱层14d,采用algainas类的四元半导体材料膜。

[0176]

在本实施方式中,由于半导体发光元件1的基板10是gaas基板,所以在作为各势垒层及阱层14d而采用algainas类的四元半导体材料的情况下,能够使阱层14d产生压缩应变。在阱层14d具有压缩应变的情况下,通过调整阱层14d的组份,能够减少在阱层14d的价带中形成的轻空穴数。因而,能够减小轻空穴与电子的复合概率,所以能够增大来自半导体发光元件的输出光的偏光比。

[0177]

如图16~图18的各表所示,通过增大阱层14d的al组份比,能够提高阱层14d的晶格失配、即增大阱层14d的压缩应变。由此,如图16~图18的各曲线图所示,能够增大重空穴的最低能级(hh1)与轻空穴的最低能级(lh1)的能量差。例如,如果将阱层14d的组份如上述那样表示为al

yw

ga

1-xw-yw

in

xw

as,则可以成立0《yw《1及0《xw《1的关系。这样,由于阱层14d包含al,在阱层14d具有压缩应变的情况下,能够减少在阱层的价带中形成的轻空穴数。因而,通过减少形成在阱层的价带中的轻空穴数,能够减小轻空穴与电子的复合概率,所以能够增大来自半导体发光元件的输出光的偏光比(te模式光的强度相对于tm模式光的强度的比)。

[0178]

在图16~图18所示的例子中,也可以将阱层14d的al组份比设定为不显现轻空穴的最低能级(lh1)以外的高阶的轻空穴能级(图17及图18所示的lh2等)那样的al组份比。例如,在图16所示的例子中,al组份比是0以上即可,在图17所示的例子中,al组份比是0.005左右以上即可,在图18所示的例子中,al组份比是0.03左右以上即可。如图16~图18所示,关于轻空穴将不形成最低能级(lh1)以外的高阶的轻空穴能级的al组份比的区域作为组份比设定区域。

[0179]

通过如以上这样决定阱层14d的组份,能够增大半导体发光元件1的偏光比。

[0180]

[1-3.变形例1]

[0181]

接着,对本实施方式的变形例1的半导体发光元件使用图19~图21进行说明。图19是表示本变形例的半导体发光元件1a的能带构造的概要的示意图。图20是表示本变形例的p侧势垒层14f与p侧导引层(guide layer)14g之间的导带势能及价带势能各自的能量差δec2及δev2的示意图。图21是表示本变形例的p侧势垒层14f的al组份比与能量差δec2及δev2的关系的曲线图。

[0182]

如图19所示,本变形例的半导体发光元件1a还具备配置在p侧势垒层14f与p型包层17之间、折射率比p型包层17大的p侧导引层14g。在本变形例中,p侧导引层14g是膜厚30nm的al

0.27

ga

0.73

as膜。半导体发光元件1a具备这样的p侧导引层14g,从而能够高精度地控制垂直方向上的光分布,能够抑制光分布过度向n型半导体层侧(即n型包层12侧)偏倚的情况。因而,能够抑制向阱层14d的垂直方向上的光约束系数的变小以及阱层14d内的工作载流子密度的增大。即,能够抑制半导体发光元件1a的温度特性劣化。进而,如果将p侧导引层14g设为不掺杂,则能够抑制因杂质掺加造成的自由载流子损耗的增大,所以能够实现波导的低损耗化。结果,能够实现温度特性优良的斜率效率高的半导体激光元件。

[0183]

此外,如图20所示,如果将p侧势垒层14f与p侧导引层14g之间的导带势能及价带势能各自的能量差表示为δec2及δev2,则p侧势垒层14f的al组份比与能量差δec2及δev2的关系成为图21所示的曲线图那样。这里,p侧导引层14g的组份是al

0.3

ga

0.7

as,p侧势垒层14f的in组份比以0.1固定。

[0184]

为了在使p侧导引层14g的折射率充分大的同时抑制从阱层14d向p侧导引层14g泄漏的电子的产生,导带势能的能量差δec2也可以是40mev以上。该情况下,如图21所示,p侧势垒层14f的al组份比是0.38左右以上即可。此外,为了通过抑制空穴向阱层14d的供给所需要的能量来抑制半导体发光元件1a的工作电压的上升,能量差δev2也可以是30mev以下。该情况下,如图21所示,p侧势垒层14f的al组份比是0.48左右以下即可。

[0185]

此外,与p侧势垒层14f的al组份比及in组份比的关系同样,还能够使用图9~图11决定p侧导引层14g的al组份比与p侧势垒层14f的al组份比及in组份比的关系。如果设p侧导引层14g的al组份比为ygp1,则p侧导引层14g的组份由al

ygp1

ga

1-ygp1

as表示,如果将p侧势垒层14f的al组份比及in组份比分别设为ybp1及xbp1,则

[0186]

ybp1≦xbp1 0.975ygp1 0.069,

[0187]

ybp1≧0.4xbp1 0.975ygp1 0.029,以及

[0188]

0.2≦ygp1≦0.4的关系可以成立。

[0189]

具有这样的组份的p侧导引层14g与由gaas基板构成的基板10大致晶格匹配。由此,能够使具有压缩性的晶格失配的p侧势垒层14f的膜厚成为临界膜厚以下。因而,能够抑

制p侧势垒层14f的晶体性降低。

[0190]

进而,在阱层14d是包含al的四元半导体材料膜的情况下,活性层14的压缩应变增大。因此,通过将与gaas基板大致晶格匹配的p侧导引层14g配置到p侧势垒层14f的上方,能够抑制活性层14附近的压缩应变的积蓄。此外,该情况下,重空穴与轻空穴的最低能级间势能增大,所以能够减小轻空穴与电子的复合概率。因而,能够减少由轻空穴与电子的复合引起的tm偏光成分,所以偏光比提高。

[0191]

此外,通过上述关系的成立,能够将p侧势垒层14f与p侧导引层14g之间的价带势能的能量差δev2抑制为30mev以下,并且将导带势能的能量差δec2增大到25mev以上,所以能够在抑制工作电压的增大的同时抑制电子从阱层的溢出。

[0192]

此外,通过将p侧导引层14g的al组份比ygp1设为0.2以上0.4以下,能够更高精度地控制垂直方向上的光分布,能够在抑制光约束系数的大幅下降的同时实现波导的低损耗化。

[0193]

[1-4.变形例2]

[0194]

接着,使用图22对本实施方式的变形例2的半导体发光元件进行说明。图22是表示本变形例的半导体发光元件1b的能带构造的概要的示意图。

[0195]

如图22所示,本变形例的半导体发光元件1b除了变形例1的半导体发光元件1a的构成要素以外还具备p侧中间层14e。p侧中间层14e是配置在阱层14d与p侧势垒层14f之间的半导体层。在本变形例中,p侧中间层14e是膜厚3nm的al

0.27

ga

0.73

as膜。p侧中间层14e是较薄的层,薄到供给到阱层14d中的电子向p侧势垒层14f侧渗出的程度。

[0196]

如果设p侧中间层14e的al组份比为ykp1,则p侧中间层14e的组份由al

ykp1

ga

1-ykp1

as表示,如果将p侧势垒层14f的al组份比及in组份比分别设为ybp1及xbp1,则

[0197]

ybp1≦xbp1 0.975ykp1 0.069,

[0198]

ybp1≧0.4xbp1 0.975ykp1 0.029,以及

[0199]

0.2≦ykp1≦0.4的关系可以成立。

[0200]

当参照图9~图11,则在关于p侧势垒层14f的al组份比ybp1而上述关系成立的情况下,p侧势垒层14f与p侧中间层14e之间的导带势能的能量差δec2为25mev以上,价带势能的能量差δev2为30mev以下。由此,能够抑制妨碍空穴向阱层14d注入的情况,所以能够抑制工作电压的增大。此外,能够抑制电子从阱层14d的溢出。

[0201]

此外,通过将p侧中间层14e的al组份比设为0.2以上0.4以下,能够更高精度地控制垂直方向上的光分布,能够在使光约束系数增大的同时实现波导的低损耗化。

[0202]

此外,通过在阱层14d与p侧势垒层14f之间配置与gaas基板大致晶格匹配的由algaas层构成的p侧中间层14e,能够使活性层14附近的压缩应变的形成区域分散,所以能够抑制因压缩应变的集中带来的晶体性的下降。

[0203]

进而,由于能够降低阱层14d与p侧中间层14e之间的价带势能的能量差,所以能够抑制高阶能级的轻空穴的形成。因而,能够抑制偏光比的下降。

[0204]

[1-5.变形例3]

[0205]

接着,使用图23对本实施方式的变形例3的半导体发光元件进行说明。图23是表示本变形例的半导体发光元件1c的能带构造的概要的示意图。

[0206]

如图23所示,本变形例的半导体发光元件1c除了变形例1的半导体发光元件1a的

构成要素以外还具备n侧第二势垒层14b。n侧第二势垒层14b是配置在n侧第一势垒层14a与阱层14d之间的半导体层。在本变形例中,n侧第二势垒层14b是膜厚7nm的al

0.31

ga

0.66

in

0.03

as膜。

[0207]

如果将n侧第二势垒层14b的al组份比及in组份比分别设为ybn2及xbn2,则n侧第二势垒层14b的组份由al

ybn2

ga

1-xbn2-ybn2

in

xbn2

as表示,

[0208]

ybn2≧xbn2 ybn1,

[0209]

ybn2≦0.4xbn2 0.975ybn1 0.061,

[0210]

xbn2≦0.15,以及

[0211]

0.2≦ybn1≦0.35的关系可以成立。

[0212]

在关于n侧第二势垒层14b的al组份比ybn2而上述关系成立的情况下,n侧第一势垒层14a与n侧第二势垒层14b之间的导带势能的能量差δec2为50mev以下,价带势能的能量差δev2为30mev以上。由此,能够抑制妨碍电子向阱层14d注入的情况,所以能够抑制工作电压的增大。此外,能够抑制空穴从阱层14d的溢出。

[0213]

此外,通过将n侧第一势垒层14a的al组份比设定得较低且为0.2以上0.35以下,能够提高n侧第一势垒层14a的折射率,所以容易使垂直方向上的光分布靠近n型半导体层侧。因而,波导的低损耗化变得容易。

[0214]

[1-6.变形例4]

[0215]

接着,使用图24对本实施方式的变形例4的半导体发光元件进行说明。图24是表示本变形例的半导体发光元件1d的能带构造的概要的示意图。

[0216]

如图24所示,本变形例的半导体发光元件1d除了变形例3的半导体发光元件1c的构成要素以外,还具备p侧中间层14e和n侧第三势垒层14c。n侧第三势垒层14c是配置在阱层14d与n侧第二势垒层14b之间的半导体层。在本变形例中,n侧第三势垒层14c是膜厚3nm的al

0.27

ga

0.73

as膜。n侧第三势垒层14c是较薄的层,薄到供给到阱层14d中的电子向n侧第二势垒层14b侧渗出的程度。

[0217]

如果设n侧第三势垒层14c的al组份比为ybn3,则n侧第三势垒层14c的组份由al

ybn3

ga

1-ybn3

as表示。这里,可以是,如果将n侧第二势垒层14b的al组份比及in组份比分别设为ybn2及xbn2,则

[0218]

ybn2≧xbn2 ybn3,

[0219]

ybn2≦0.4xbn2 0.975ybn3 0.061,以及

[0220]

0.2≦ybn3≦0.35的关系成立。

[0221]

在关于n侧第二势垒层14b的al组份比ybn2而上述关系成立的情况下,n侧第二势垒层14b与n侧第三势垒层14c之间的导带势能的能量差δec2为50mev以下。此外,通过使n侧第三势垒层14c的al组份比为0.35以下,能够降低n侧第三势垒层14c的带隙能量。因而,能够抑制妨碍电子向阱层14d注入的情况,所以能够抑制工作电压的增大。

[0222]

此外,在关于n侧第二势垒层14b的al组份比ybn2而上述关系成立的情况下,n侧第二势垒层14b与n侧第三势垒层14c之间的价带势能的能量差δev2为0mev以上。因而,能够抑制空穴从阱层14d的溢出。

[0223]

此外,通过将n侧第三势垒层14c的al组份比设定得较低且为0.2以上0.35以下,能够提高n侧第三势垒层14c的折射率,所以容易使垂直方向上的光分布靠近n型半导体层侧。

因而,波导的低损耗化变得容易。

[0224]

[1-7.变形例5]

[0225]

接着,使用图25对本实施方式的变形例5的半导体发光元件进行说明。图25是表示本变形例的半导体发光元件1e的能带构造的概要的示意图。

[0226]

如图25所示,本变形例的半导体发光元件1e具有多重量子阱构造。半导体发光元件1e的活性层具有n侧第一势垒层14a、第一中间势垒层14h、p侧势垒层14f和两层的阱层14d。

[0227]

第一中间势垒层14h是配置在n侧第一势垒层14a与p侧势垒层14f之间的势垒层。在本变形例中,第一中间势垒层14h是膜厚5nm的al

0.3

ga

0.7

as膜。

[0228]

两层的阱层14d中的一个是配置在n侧第一势垒层14a与第一中间势垒层14h之间的第一阱层的一例。两层的阱层14d中的另一个是配置在第一中间势垒层14h与p侧势垒层14f之间的第二阱层的一例。在本变形例中,两个阱层14d分别是膜厚6nm的al

0.08

ga

0.67

in

0.25

as膜。

[0229]

在本变形例那样的具有多重量子阱构造的半导体发光元件1e中,也能够在抑制工作电压的增大的同时在p侧势垒层14f中抑制电子的溢出。

[0230]

另外,在本变形例的半导体发光元件1e中具备两层的阱层14d,但阱层14d的层数并不限定于两层。阱层14d的层数也可以是三以上。在半导体发光元件1e具备n层(n是2以上的整数)的阱层14d的情况下,半导体发光元件1e具备第一中间势垒层到第(n-1)中间势垒层的(n-1)层的中间势垒层。这里,如果将第k中间势垒层(k=1、2、3、

…

、n-1)的al组份比及in组份比分别设为ybk及xbk(k=1、2、3、

…

、n-1),则第k中间势垒层的组份表示为al

ybk

ga

1-xbk-ybk

in

xbk

as。这里,

[0231]

ybn1≦ybk≦ybp1,以及

[0232]

xbn1≦xbk≦xbp1的关系成立,并且,第k中间势垒层的带隙能量是n侧第一势垒层14a的带隙能量以上且p侧势垒层14f的带隙能量以下。

[0233]

由此,能得到与本实施方式的半导体发光元件1同样的效果。此外,通过采用多重量子阱构造,能够减小各阱层的激光振荡状态下的工作载流子密度,所以能够进一步抑制电子的溢出。因而,半导体发光元件1e的温度特性进一步提高。

[0234]

[1-8.变形例6]

[0235]

接着,使用图26对本实施方式的变形例6的半导体发光元件进行说明。图26是表示本变形例的半导体发光元件1f的能带构造的概要的示意图。

[0236]

如图26所示,本变形例的半导体发光元件1f具有多重量子阱构造。半导体发光元件1f的活性层具有n侧第一势垒层14a、第一中间势垒层14ha、p侧势垒层14f和两层的阱层14d。

[0237]

本变形例的第一中间势垒层14ha与变形例5的第一中间势垒层14h同样,是配置在n侧第一势垒层14a与p侧势垒层14f之间的势垒层。在本变形例中,第一中间势垒层14ha具有第一中间n侧势垒层14i和第一中间p侧势垒层14j。

[0238]

第一中间n侧势垒层14i是第一中间势垒层14ha中的配置在n侧第一势垒层14a侧的层。在本变形例中,第一中间n侧势垒层14i是膜厚3nm的al

0.3

ga

0.7

as膜。

[0239]

第一中间p侧势垒层14j是第一中间势垒层14ha中的配置在p侧势垒层14f侧的层。

在本变形例中,第一中间p侧势垒层14j是膜厚3nm的al

0.45

ga

0.45

in

0.1

as膜。

[0240]

两层的阱层14d中的一个是配置在n侧第一势垒层14a与第一中间势垒层14ha之间的第一阱层的一例。两层的阱层14d中的另一个是配置在第一中间势垒层14ha与p侧势垒层14f之间的第二阱层的一例。在本变形例中,两个阱层14d分别是膜厚6nm的al

0.08

ga

0.67

in

0.25

as膜。

[0241]

在本变形例那样的具有多重量子阱构造的半导体发光元件1f中,也能够在抑制工作电压的增大的同时在p侧势垒层14f中抑制电子的溢出。

[0242]

另外,在本变形例的半导体发光元件1f中具备两层的阱层14d,但阱层14d的层数并不限定于两层。阱层14d的层数也可以是三以上。在半导体发光元件1f具备n层(n是2以上的整数)的阱层14d的情况下,半导体发光元件1f具备从第一中间势垒层到第(n-1)中间势垒层的(n-1)层的中间势垒层。此外,第k中间势垒层(k=1、2、3、

…

、n-1)具有第k中间n侧势垒层和第k中间p侧势垒层。如果将第k中间势垒层(k=1、2、3、

…

、n-1)具有的第k中间n侧势垒层的al组份比及in组份比分别设为ybck及xbck(k=1、2、3、

…

、n-1),将第k中间p侧势垒层的al组份比及in组份比分别设为ybk及xbk(k=1、2、3、

…

、n-1),则第k中间n侧势垒层及第k中间p侧势垒层的组份分别表示为al

ybck

ga

1-xbck-ybck

in

xbck

as及al

ybk

ga

1-xbk-ybk

in

xbk

as。这里,

[0243]

ybn1≦ybk≦ybp1,

[0244]

xbn1≦xbk≦xbp1,以及

[0245]

ybn1≦ybck≦ybp1的关系成立,并且,第k中间n侧势垒层的带隙能量是第k中间p侧势垒层的带隙能量以下,第k中间p侧势垒层的带隙能量是p侧势垒层14f的带隙能量以下。

[0246]

由此,能得到与变形例5的半导体发光元件1e同样的效果。

[0247]

此外,也可以是,

[0248]

ybp1≦xbp1 0.975ybck 0.069

[0249]

ybp1≧0.4xbp1 0.975ybck 0.029

[0250]

0.2≦ybck≦0.4的关系成立。

[0251]

由此,能够通过第k中间势垒层来抑制第k中间n侧势垒层与第k中间p侧势垒层之间的价带势能差的增大,并且能够使得第k中间p侧势垒层与第k中间n侧势垒层相比导带势能变大。因而,能够不损害相邻的两个阱层14d间的空穴的电传导性地抑制电子从各阱层14d的溢出。

[0252]

因此,如果ybn1、xbn1、ybp1、xbp1、ybk及ybck是上述范围内,则能得到与变形例5的半导体发光元件1e同样的效果,并且,通过采用本变形例的多重量子阱构造,不仅能够降低阱层14d的激光振荡状态下的工作载流子密度,还能够实现电子的溢出的抑制以及温度特性的提高。

[0253]

[1-9.变形例7]

[0254]

接着,使用图27对本实施方式的变形例7的半导体发光元件进行说明。图27是表示本变形例的半导体发光元件1g的光射出端面部40的结构的剖视图。在图27中,表示了本变形例的半导体发光元件1g的与激光的谐振方向平行并且与基板10的主面垂直的剖面的一部分。

[0255]

本变形例的半导体发光元件1g,在光射出端面部40中具有所谓的端面窗构造(window mirror structure)这一点上与实施方式1的半导体发光元件1不同,在其他方面是一致的。另外,在图27中省略了n侧电极31及p侧电极32。另外,光射出端面部40是包括半导体发光元件1g的光射出端面1f的区域。另外,不仅是在光射出端面部40,半导体发光元件1g可以在后侧端面部(即,包括光射出端面1f的相反侧的端面的区域)也具有端面窗构造。后侧端面部占据的区域没有特别限定,例如至少包括从后侧端面的谐振方向上的长度为谐振器长的1%的区域。

[0256]

具体而言,本变形例的半导体发光元件1g的活性层14的光射出端面部40中扩散有空位或杂质。以下,对本变形例的端面窗构造详细地进行说明。

[0257]

在alas、gaas及inas中,inas晶格常数最大,带隙能量最小。在如本变形例的半导体发光元件1g那样对阱层14d及各势垒层使用algainas类的四元半导体材料而得到希望的带隙能量的情况下,与对阱层使用由ingaas构成的半导体材料得到希望的带隙能量的情况相比,由algainas构成的阱层的in的含有率提高,所以阱层的压缩应变变大。

[0258]

根据以上,在对阱层14d及各势垒层使用algainas类的四元半导体材料的构造中,在将空位或杂质扩散到半导体发光元件的光射出端面部40的情况下,由于使阱层14d的应变能量变小,所以阱层14d的in原子容易与相对于层叠方向存在于iii族的晶格位置的al原子及ga原子交换。因而,阱层14d的带隙能量容易变大。

[0259]

结果,光密度大的光射出端面部40处的阱层的带隙能量变大,能够形成所谓的窗构造。即,与在活性层14中没有形成端面窗构造的部分的带隙能量相比,在活性层14中形成有端面窗构造的部分的带隙能量变大。由此,即使光射出端面部40的带隙能量由于发热而变小,也能够维持光射出端面部40的阱层14d的光吸收较小的状态。因而,能够抑制由于光射出端面部40吸收光而引起的cod的发生。

[0260]

如果设窗构造的向谐振方向的长度为lw,则lw较长时谐振器端面与不是窗构造的区域(增益区域)的间隔变长。增益区域是在活性层14中产生发光的区域。通过向增益区域的电流注入,在活性层14中发生发光复合和非发光复合。

[0261]

活性层14的温度不仅通过半导体发光元件1g中包含的串联电阻成分的焦耳发热而上升,还通过伴随着非发光复合的发热而上升。谐振器端面由于在制造谐振器时通过解理而形成,所以容易产生晶体缺陷能级。当半导体发光元件1g时,谐振器端面的带隙能量进一步变小,所以谐振器端面处的晶体缺陷能级下的光吸收变得更大,容易发生cod。

[0262]

若使lw较长,则增益区域与谐振器端面的距离较远,增益区域的发热对谐振器端面带来的影响变小,对于抑制cod的发生是有利的。但是,如果lw过长,则由于增益区域长度变短,所以向增益区域的电流集中变大。随之,电子从活性层14的溢出增大,所以温度特性下降。

[0263]

相对于此,在如上述那样对阱层14d及各势垒层采用algainas类的四元半导体材料的情况下,阱层14d的in原子容易与相对于层叠方向存在于iii族的晶格位置的al原子及ga原子交换,有阱层14d的带隙能量容易变大的效果。在窗构造区域的活性层14的带隙能量变大的情况下,窗构造区域中的激光的光吸收变小,窗构造区域中的发热也变小。因此,在本实施方式的半导体发光元件1g中,即使使lw较短,增益区域的发热的影响对谐振器端面带来的影响也变小,与以往的对阱层14d采用ingaas、对各势垒层采用algaas的构造相比,

能够缩短lw。具体而言,以往lw需要30μm以上,但如果对阱层14d及各势垒层采用algainas类的四元半导体材料,则lw为15μm以上就能够抑制cod发生。

[0264]

进而,如果通过空位扩散而形成窗构造,则与通过杂质部扩散形成窗构造的情况相比,能够抑制因杂质的存在带来的自由载流子损耗的发生,所以能够抑制斜率效率的下降。

[0265]

(实施方式2)

[0266]

对实施方式2的半导体发光元件进行说明。本实施方式的半导体发光元件在活性层14与n型包层之间还具备n侧导引层等方面与实施方式1的半导体发光元件1不同。以下,对于本实施方式的半导体发光元件,以与实施方式1的半导体发光元件1的不同点为中心,利用图28进行说明。

[0267]

图28是表示本实施方式的半导体发光元件101的整体结构的示意性剖视图。如图28所示,本实施方式的半导体发光元件101除了实施方式1的半导体发光元件1的各构成要素以外,还具备n侧导引层13、第一应变控制层15和第二应变控制层16。

[0268]

n侧导引层13是配置在n型包层12与活性层14之间的n型半导体层。n侧导引层13的折射率比n型包层12大。由此,与实施方式1的半导体发光元件1相比,能够将垂直方向上的光分布配置得更靠近活性层14。因而,能够抑制向活性层14的光约束系数的下降。在本实施方式中,通过使n侧导引层13的al组份比低于n型包层12的al组份比,从而增大了n侧导引层13的折射率。此外,n侧导引层13包含n型的杂质,n侧导引层13的n型包层12侧的区域的杂质浓度比活性层14侧的区域的杂质浓度低。由此,能够抑制对n侧导引层13的电传导性的损害,并且降低由n侧导引层13中的杂质引起的波导损耗。具体而言,n侧导引层13是膜厚1μm的al

0.27

ga

0.73

as层。此外,n侧导引层13的膜厚之中,在活性层14侧的膜厚0.25μm的部分,掺杂有浓度5

×

10

17

cm-3

的si,在n型包层12侧的膜厚0.75μm的部分,掺杂有浓度5

×

10

16

cm-3

的si。n侧导引层13的杂质浓度没有特别限定,为了降低n侧导引层13的波导损耗,可以将n侧导引层13中的n型包层12侧的部分的杂质浓度例如设为1

×

10

17

cm-3

以下。此外,也可以使n侧导引层13中的活性层14侧的部分的杂质浓度例如比1

×

10

17

cm-3

高,以免损害n侧导引层13的电传导性。

[0269]

第一应变控制层15配置在活性层14与p型包层17之间,是包含al的半导体层。在本实施方式中,第一应变控制层15是膜厚0.05μm的al

0.70

ga

0.30

as层。

[0270]

第二应变控制层16配置在第一应变控制层15与p型包层17之间,是与第一应变控制层15相比al组份比低且杨氏模量小的半导体层。在本实施方式中,第二应变控制层16是膜厚0.16μm的al

0.30

ga

0.70

as层。

[0271]

第一应变控制层15及第二应变控制层16的杂质浓度例如是2

×

10

17

cm-3

以上、6

×

10

17

cm-3

以下。在本实施方式中,在第一应变控制层15及第二应变控制层16中掺杂有浓度3

×

10

17

cm-3

的c。

[0272]

第一应变控制层15及第二应变控制层16是用来抑制在将半导体发光元件101进行结朝下(junction down)安装的情况下(即,将p侧电极32与安装面连接的情况下)安装应变对活性层14带来的影响的层。在本实施方式的半导体发光元件101中,在结朝下安装的情况下,安装应变所引起的应力的大部分被杨氏模量小的第二应变控制层16吸收。因此,能够抑制安装应变所引起的应力作用于在比第二应变控制层16距安装面远的位置配置的活性层

14。因此,能够使活性层14中的应变稳定为在晶体生长中决定的应变的大小。随之,安装半导体发光元件101后的带构造的控制性提高,所以能够进行稳定的高温高输出动作。因而,根据本实施方式,能够稳定地实现温度特性良好、斜率效率高、适合于高温高输出动作的半导体激光元件。

[0273]

(实施方式3)

[0274]

对实施方式3的半导体发光元件进行说明。本实施方式的半导体发光元件,与实施方式2的半导体发光元件101的不同点在于,在p型半导体层具有隆起部。以下,对于本实施方式的半导体发光元件,以与实施方式2的半导体发光元件101的不同点为中心,利用图29进行说明。

[0275]

图29是表示本实施方式的半导体发光元件201的整体结构的示意性剖视图。如图29所示,本实施方式的半导体发光元件101具备基板10、缓冲层11、n型包层12、n侧导引层13、活性层14、第一应变控制层15、第二应变控制层16、p型包层17、接触层218、电流阻挡层20、n侧电极31和p侧电极32。

[0276]

本实施方式的接触层218具有与实施方式2的接触层18同样的组份,但在具有隆起部218r这一点上与实施方式2的接触层18不同。在接触层218的上表面(即,p侧电极32侧的面),形成有在激光的谐振方向上延伸的两条槽218t,在两条槽218t之间形成隆起部218r。在本实施方式中,电流集中地被约束在隆起部218r,沿着隆起部218r形成波导。

[0277]

电流阻挡层20是用来使电流集中于隆起部218r的绝缘层。电流阻挡层20配置在接触层218上的隆起部218r以外的区域。在本实施方式中,电流阻挡层20配置在接触层218上的隆起部218r的上表面以外的区域。换言之,在电流阻挡层20中,在隆起部218r上形成有沿着激光的谐振方向延伸的狭缝。电流阻挡层20是绝缘膜即可,没有特别限定,在本实施方式中是膜厚0.02μm的sio2膜。

[0278]

接着,使用图30~图32对本实施方式的半导体发光元件201的作用及效果进行说明。图30是表示本实施方式的半导体发光元件201的各部的尺寸的示意性剖视图。图31是表示本实施方式的半导体发光元件201的安装状态的示意性剖视图。图32是表示本实施方式的半导体发光元件201的活性层14的x轴方向的位置所对应的剪切应力σxy的分布的曲线图。

[0279]

如图30所示,设半导体发光元件201的各层的层叠方向(即,与基板10的主面垂直的方向)为y轴方向。此外,设与激光的谐振方向及y轴方向垂直的方向为x轴方向。此外,如图30所示,设两个槽218t各自的x轴方向的宽度为d1,设隆起部218r的x轴方向的宽度为wr。此外,设半导体发光元件201的x轴方向的宽度为wc。

[0280]

说明将这样的半导体发光元件201如图31所示那样结朝下安装于子装配体202的情况下作用于半导体发光元件201的应力。

[0281]

子装配体202例如是由cu形成的板状的部件。

[0282]

这里,半导体发光元件201的热膨胀系数是与gaas的热膨胀系数(5.35

×

10-6

k-1

)相同的程度,小于子装配体202的热膨胀系数(5.35

×

10-6

k-1

)。在将半导体发光元件201结朝下安装于这样的子装配体202的情况下,半导体发光元件201和子装配体202的热膨胀系数之差所对应的剪切应力作用于半导体发光元件201的活性层14。该情况下,半导体发光元件201从子装配体202受到在x轴方向上被压缩的朝向的应力。具体而言,如图31所示,在半

导体发光元件201的x轴方向的右侧及左侧的端部,分别作用有顺时针朝向的剪切应力σ1r及逆时针朝向的剪切应力σ1l。此外,在隆起部218r的右侧及左侧的端部,分别作用有逆时针朝向的剪切应力σ2r及顺时针朝向的剪切应力σ2l。这样,对半导体发光元件201作用有相对于隆起部218r的x轴方向的中心对称的剪切应力。

[0283]

这里,使用图31及图32对作用于半导体发光元件201的剪切应力进行说明。在图32中,表示了半导体发光元件201的x轴方向的宽度wc为500μm、隆起部218r的x轴方向的宽度wr是200μm的情况下的剪切应力在x轴方向上的分布。另外,在图32中,表示了槽218t的宽度d1为20μm、40μm及80μm的情况下的计算结果。此外,在图32中还一并表示了没有槽218t的情况下的剪切应力的计算结果。

[0284]

如图31所示,例如,在隆起部218r的x轴方向的右侧的端部,由槽218t引起的剪切应力σ2r和由半导体发光元件201的x轴方向的右侧的端部引起的剪切应力σ1r相互为相反朝向,因此剪切应力变弱(参照图32的位置x为100μm的点)。在隆起部218r的x轴方向的左侧的端部,也与右侧的端部同样,剪切应力变弱(参照图32的位置x为-100μm的点)。

[0285]

在半导体发光元件201中,如在图30中粗虚线箭头所示那样,电流从隆起部218r一边在x轴方向上扩散一边到达活性层14。因此,半导体发光元件201中的激光由于在活性层14中一直分布到与槽218t的x轴方向的位置对应的区域,所以受到槽218t的剪切应力的影响。另外,图30所示的虚线椭圆表示激光的分布区域的外缘。此外,活性层14中的剪切应力的分布如果相对于隆起部218r的x轴方向的中央不是完全反对称,则在通过剪切应力而在半导体发光元件201中产生了双折射率性的情况下,由于光分布与剪切应力的相关积分不再是0,所以偏光面倾斜。另外,这里剪切应力与光分布的相关积分由以下的式子表示。

[0286]

[数式1]

[0287]

∫∫σ

xy

|φ|2dxdy|φ|2:光分布

[0288]

在本实施方式中,通过形成槽218t,能够减小隆起部218r的x轴方向端部的剪切应力,所以能够抑制由剪切应力引起的对于光分布的影响。因而,根据本实施方式的半导体发光元件201,在半导体发光元件201中发生了相对于x轴方向的中央非对称的应变的情况下偏光面倾斜从而偏光比下降的情况能够被抑制。例如,通过使槽218t的x轴方向上的宽度d1为10μm以上,能够使隆起部218r的x轴方向端部附近的剪切应力减弱。另一方面,如果使槽218t的宽度d1过宽,则由于在结朝下安装时载荷集中于隆起部218r,所以槽218t的宽度d1可以设为40μm以下。

[0289]

此外,关于槽218t的深度,如果使槽218t的阶差部(即,槽218t的底面与侧面相连的部分)过于接近于活性层14,则在其凹凸的影响下在活性层14中产生的剪切应力增大,偏光比下降。因此,槽218t的深度可以是0.3μm以下。在本实施方式中,槽218t仅形成在接触层218中,其深度是0.2μm。

[0290]

(实施方式4)

[0291]

对实施方式4的半导体发光元件及其制造方法进行说明。本实施方式的半导体发光元件主要在用于p侧导引层、n型包层及p型包层的材料上与实施方式1的变形例3的半导体发光元件1c不同。以下,对于本实施方式的半导体发光元件,以与实施方式1的变形例3的半导体发光元件1c的不同点为中心进行说明。

[0292]

[4-1.整体结构]

[0293]

首先,对本实施方式的半导体发光元件的整体结构进行说明。本实施方式的半导体发光元件与实施方式1的变形例3的半导体发光元件1c同样,具备基板、n型包层、活性层、p型包层、电流狭窄层、接触层、n侧电极和p侧电极。本实施方式的半导体发光元件还具备配置在n型包层与活性层之间的n侧导引层。

[0294]

本实施方式的半导体发光元件主要在用于各层的材料上与半导体发光元件1c不同。以下,对于本实施方式的半导体发光元件具备的各层中的、采用与半导体发光元件1c具备的各层不同的材料的层以及n侧导引层进行说明。

[0295]

n型包层的组份如果设al的组份比为yn2则由(al

yn2

ga

1-yn2

)

0.5

in

0.5

p表示。另外,(al

yn2

ga

1-yn2

)

0.5

in

0.5

p这一记载中的in的组份比(以及(al

yn2

ga

1-yn2

)的组份比)是指将小数点第2位四舍五入而成为0.5的范围的组份比。关于由小数表示的其他组份比也同样,并不限定于仅一个值,是指将比所记载的小数低位的值四舍五入而成为该小数的范围的组份比。通过将n型包层的组份设为(al

yn2

ga

1-yn2

)

0.5

in

0.5

p,在n型包层中空位或zn、mg等杂质容易扩散。因而,当通过使空位或杂质扩散而在半导体发光元件中形成端面窗构造时,能够减少形成所需要的时间。此外,能够减少在使杂质扩散时使用的杂质的浓度,所以能够减少由杂质带来的光吸收。因而,能够抑制半导体发光元件的发光效率的下降。

[0296]

此外,在为了使形成在由n型gaas构成的基板上的n型包层的应变成为

±

0.2%以下而al的组份比为0以上0.6以下的情况下,in的组份比可以是0.45以上0.513以下。在本实施方式中,n型包层是膜厚3.5μm的n型(al

0.14

ga

0.86

)

0.5

in

0.5

p层。n型包层包括掺杂有相互不同的浓度的杂质的多个部分。n型包层从距基板较近的端面起依次包括掺杂有浓度1

×

10

18

cm-3

的si的厚度2.5μm的部分、掺杂有浓度5

×

10

17

cm-3

的si的厚度0.5μm的部分、以及掺杂有浓度2

×

10

17

cm-3

的si的厚度0.5μm的部分。

[0297]

n侧导引层配置在n型包层与活性层之间。在本实施方式中,n侧导引层是膜厚0.5μm的n型(al

0.04

ga

0.96

)

0.5

in

0.5

p层。在n侧导引层中掺杂有浓度1

×

10

17

cm-3

的si。

[0298]

活性层具有n侧第一势垒层、n侧第二势垒层、阱层、p侧势垒层和p侧导引层。在本实施方式中,n侧第一势垒层是膜厚14nm的无掺杂al

0.5

ga

0.5

as层。n侧第二势垒层是膜厚3.5nm的无掺杂al

0.55

ga

0.45

as层。阱层是膜厚6nm的无掺杂in

0.08

ga

0.92

as层。p侧势垒层是膜厚3.5nm的无掺杂al

0.59

ga

0.16

in

0.25

as层。

[0299]

p侧导引层的组份如果设al的组份比为ygp2则由(al

ygp2

ga

1-gp2

)

0.5

in

0.5

p表示。通过将p侧导引层的组份设为(al

ygp2

ga

1-gp2

)

0.5

in

0.5

p,在p侧导引层中空位或zn、mg等杂质容易扩散。因而,起到与上述的n型包层同样的效果。在本实施方式中,是膜厚220nm的p型(al

0.04

ga

0.96

)

0.5

in

0.5

p层。在p侧导引层中掺杂有浓度1

×

10

17

cm-3

的c。

[0300]

p型包层的组份如果设al的组份比为yp2则由(al

yp2

ga

1-yp2

)

0.5

in

0.5

p表示。通过将p型包层的组份设为(al

yp2

ga

1-yp2

)

0.5

in

0.5

p,在p型包层中空位或zn、mg等杂质容易扩散。因而,起到与上述的n型包层同样的效果。在本实施方式中,p型包层是厚度0.8μm的p型(al

0.6

ga

0.4

)

0.5

in

0.5

p层。在p型包层中掺杂有浓度2

×

10

18

cm-3

的c。

[0301]

进而,在本实施方式中,关于n型包层的al的组份比yn2及p型包层的al的组份比yp2,0《yn2《yp2《1的关系成立。由此,能够使p型包层的折射率相比n型包层的折射率减小。因而,能够使激光的强度分布向n型包层侧偏倚。即,能够减少在p型包层中传播的激光,所以能够减小由p型包层的杂质引起的自由载流子损耗。由此,能够实现波导的低损耗化。

[0302]

[4-2.制造方法]

[0303]

接着,使用图33对本实施方式的半导体发光元件的制造方法进行说明。图33是表示本实施方式的半导体发光元件的制造方法的工序的流程图。

[0304]

如图33所示,首先,准备基板(s10)。在本实施方式中,准备n型gaas基板。

[0305]

接着,在基板的上方形成n型包层(s20)。在本实施方式中,在基板的上表面,作为n型包层而形成n型(al

yn2

ga

1-yn2

)

0.5

in

0.5

p层。

[0306]

接着,在n型包层的上方形成n侧导引层(s30)。在本实施方式中,在n型包层的上表面,作为n侧导引层而形成n型(al

0.04

ga

0.96

)

0.5

in

0.5

p层。

[0307]

接着,在n侧导引层的上方形成活性层(s40)。在本实施方式中,作为活性层,在n侧导引层的上表面,依次形成n侧第一势垒层、n侧第二势垒层、阱层、p侧势垒层和p侧导引层。具体而言,作为n侧第一势垒层而形成无掺杂al

0.5

ga

0.5

as层,作为n侧第二势垒层而形成无掺杂al

0.55

ga

0.45

as层,作为阱层而形成无掺杂in

0.08

ga

0.92

as层,作为p侧势垒层而形成无掺杂al

0.59

ga

0.16

in

0.25

as层,作为p侧导引层而形成p型(al

ygp2

ga

1-gp2

)

0.5

in

0.5

p层。

[0308]

接着,在活性层的上方形成p型包层(s50)。在本实施方式中,在活性层的上表面,作为p型包层而形成p型(al

yp2

ga

1-yp2

)

0.5

in

0.5

p层。

[0309]

接着,在p型包层的上方形成电流狭窄层(s60)。在本实施方式中,在p型包层的上表面,作为电流狭窄层而形成n型gaas层,通过光刻法及蚀刻等,沿着激光谐振方向形成长尺寸状的开口部。

[0310]

接着,在电流狭窄层的上方形成接触层(s70)。在本实施方式中,在电流狭窄层的上表面及开口部,作为接触层而形成p型gaas层。

[0311]

上述各半导体层例如通过有机金属气相沉积法(mocvd)等形成。

[0312]

接着,在活性层形成端面窗构造(s80)。具体而言,从接触层的上表面使空位或杂质向活性层的光射出端面部扩散。通过这样使空位或杂质扩散,能够使活性层的光射出端面部的量子阱构造无序化。随之,能够使活性层的带隙能量增大。即,能够形成窗构造。在本实施方式中,作为n型包层而形成了n型(al

yn2

ga

1-yn2

)

0.5

in

0.5

p层,作为p侧导引层而形成了p型(al

ygp2

ga

1-gp2

)

0.5

in

0.5

p层,作为p型包层而形成了p型(al

yp2

ga

1-yp2

)

0.5

in

0.5

p层,所以空位或杂质容易扩散。因而,能够减少在端面窗构造的形成中需要的时间。此外,由于能够降低在使杂质扩散时使用的杂质的浓度,所以能够减少由杂质带来的光吸收。因而,能够抑制半导体发光元件的发光效率的下降。另外,不仅在光射出端面部,端面窗构造还可以形成在半导体发光元件的形成谐振器的两方的端面部。

[0313]

接着,形成电极(s90)。具体而言,在接触层的上表面形成p侧电极,在基板的下方的主面形成n侧电极。在本实施方式中,作为p侧电极,从接触层侧依次形成ti膜、pt膜及au膜,作为n侧电极,从基板10侧依次形成auge膜、ni膜、au膜、ti膜、pt膜、ti膜、pt膜及au膜。

[0314]

如以上这样,能够制造本实施方式的半导体发光元件。

[0315]

(变形例等)

[0316]

以上,对于本发明的半导体发光元件及其制造方法基于各实施方式进行了说明,但本发明并不限定于上述各实施方式。

[0317]

例如,在上述各实施方式中,表示了半导体发光元件是半导体激光元件的例子,但半导体发光元件并不限定于半导体激光元件。例如,半导体发光元件也可以是超辐射发光

二极管(super luminescent diode)。

[0318]

此外,在上述各实施方式中,在半导体发光元件中使用algainas类材料,但也可以使用其他半导体材料。例如,也可以使用氮化物类的半导体材料。具体而言,也可以使用algainn类材料。以下,对algainas类材料及algainn类材料的导带势能及价带势能进行说明。

[0319]

对导带势能及价带势能带来影响的物性是电子亲和力、带隙能量及晶格应变。晶格应变由半导体层的晶格常数和层叠该半导体层的基板的晶格常数决定。在algainas类材料及algainn类材料中,在作为它们的构成要素的二元化合物(alas、gaas及inas、以及aln、gan及inn)中,电子亲和力、带隙能量、晶格常数的大小关系是以下这样的。关于电子亲和力,以inas、gaas、alas的顺序变小,以inn、gan、aln的顺序变小。带隙能量以alas、gaas、inas的顺序变小,以aln、gan、inn的顺序变小。关于algainas类材料的构成要素的晶格常数,inas比gaas及alas大,gaas及alas是相同程度。此外,关于algainn类材料的构成要素的晶格常数,inn比gan及aln大,gan及aln是相同程度。

[0320]

根据上述的关系性可知,即使四元半导体材料的v族原子不同,上述物性的大小关系也类似。

[0321]

在作为algainas类材料的构成要素的alas、gaas及inas中,inas晶格常数最大且带隙能量最小。在对于阱层及势垒层采用包含algainas类的四元半导体材料的层而得到希望的带隙能量的情况下,与对于阱层采用由ingaas构成的层而得到希望的带隙的情况相比,由algainas构成的阱层的in的含有率提高,所以阱层的压缩应变变大。

[0322]

在algainn类材料中,在aln、gan、inn中,inn晶格常数最大且带隙能量最小。在对于阱层及势垒层采用包含algainn类的四元半导体材料的层得到希望的带隙能量的情况下,与对于阱层采用ingan或对于势垒层采用由algan构成的层而得到希望的带隙的情况相比,由algainn构成的阱层的in的含有率提高,所以阱层的压缩应变变大。

[0323]

此外,关于电子亲和力,越多地包含in则越大、越多地包含al则越小这样的关系性对于algainas类材料及algainn类材料双方都符合。

[0324]

因此,如果对势垒层采用algainas类材料,增大in组份比并增大带隙能量,则导带势能的变化(δebc)比价带势能的变化(δebv)大,这在algainn类材料中也同样。因而,作为形成上述各实施方式的半导体发光元件的材料,也可以使用algainn类的四元半导体材料。例如,实施方式1的变形例1的半导体发光元件1a也可以具备由gan基板构成的基板、膜厚1.5μm的由al

0.25

ga

0.75

n(si浓度:1

×

10

18

cm-3

)构成的n型包层、膜厚30nm的由al

0.2

ga

0.8

n构成的n侧第一势垒层、膜厚2.8nm的由al

0.01

ga

0.98

in

0.01

n构成的阱层、膜厚7nm的由al

0.40

ga

0.515

in

0.085

n构成的p侧势垒层、膜厚30nm的由al

0.2

ga

0.8

n构成的p侧导引层以及膜厚0.6μm的由al

0.3

ga

0.7

n(mg浓度:1

×

10

19

cm-3

)构成的p型包层。由此,能得到振荡波长是360nm波段的紫外线激光,能够实现能够在抑制工作电压的同时抑制电子从阱层的溢出的氮化物类的半导体发光元件。

[0325]

此外,如果在p侧中间层14e、p侧势垒层14f及p侧导引层14g的至少一层中掺杂p型的杂质,则该层的导带势能变高。因此,能够提高抑制高温高输出动作时的电子的溢出的效果。进而,该情况下,由于掺杂了p型的杂质的层的电阻变小,所以能够减少半导体发光元件中包含的串联电阻成分。随之,还能够抑制工作中的焦耳热的产生,所以能够进一步提高半

导体发光元件的高温工作时的热饱和的光输出。作为p型的杂质,可以使用不易从进行了掺杂的位置发生扩散的c(碳原子)或mg。

[0326]

这里,作为掺杂的浓度,在包含algaas的algainas类材料的情况下,为了提高电传导性和导带势能,可以是1

×

10

17

cm-3

以上,也可以是2

×

10

17

cm-3

以上。此外,如果过度提高向阱层14d的附近的p侧中间层14e、p侧势垒层14f及p侧导引层14g的杂质的掺杂浓度,则自由载流子损耗变高,导致半导体发光元件的发光效率的下降,所以向这些各层的掺杂的浓度可以是1

×

10

18

cm-3

以下,也可以是6

×

10

17

cm-3

以下。

[0327]

此外,在包含algan的algainn类材料的情况下,在掺杂剂中使用mg的情况下,为了提高电传导性和导带势能,掺杂的浓度可以是1

×

10

18

cm-3

以上,也可以是2

×

10

18

cm-3

以上。此外,如果过度提高向阱层14d的附近的p侧中间层14e、p侧势垒层14f及p侧导引层14g的杂质的掺杂浓度,则自由载流子损耗变高,导致半导体发光元件的发光效率的下降,所以向这些各层的掺杂的浓度可以是1

×

10

19

cm-3

以下,也可以是6

×

10

18

cm-3

以下。

[0328]

此外,在向p侧中间层14e、p侧势垒层14f及p侧导引层14g的至少一层进行掺杂的情况下,p型的杂质掺杂浓度也可以使距阱层14d较近侧的浓度相对较低。这样,距作为发光层的阱层14d最近的杂质掺杂区域的杂质浓度下降,所以能够减小自由载流子损耗。因而,能够减小在波导中传播的激光的波导损耗。

[0329]

此外,对于上述各实施方式施以本领域技术人员想到的各种变形而得到的形态、或在不脱离本发明的主旨的范围内将上述各实施方式的构成要素及功能任意地组合而实现的形态也包含在本发明中。

[0330]

例如,实施方式1的各变形例既可以相互组合,也可以也与其他实施方式组合。例如,也可以将实施方式1的变形例7的端面窗构造对实施方式1的其他变形例及其他实施方式加以应用。另外,关于使用氮化物类的半导体材料的情况,在aln、gan、inn中,inn晶格常数最大并且带隙能量最小。该情况下,在对阱层及各势垒层采用包含由algainn构成的四元类半导体材料的层而得到希望的带隙能量的情况下,与对阱层采用ingan或algan得到希望的带隙能量的情况相比,由algainn构成的阱层的in的含有率提高,所以阱层的压缩应变变大。因而,与上述的对阱层及各势垒层采用包含algainas类材料的层的情况同样,能够容易地形成窗构造。

[0331]

此外,实施方式4的半导体发光元件的制造方法对于其他实施方式及变形例的半导体发光元件的制造也能够应用。例如,在实施方式1及其各变形例的半导体发光元件的制造中,能够应用将实施方式4的半导体发光元件的制造方法的n侧导引层形成工序省略、将各半导体层的结构变更了的制造方法。此外,在实施方式2的半导体发光元件101的制造中,能够应用对实施方式4的半导体发光元件的制造方法追加第一应变控制层15及第二应变控制层16的形成工序、将各半导体层的结构变更了的制造方法。此外,在实施方式3的半导体发光元件201的制造中,能够应用在实施方式4的半导体发光元件的制造方法的p型包层形成工序中将电流狭窄层形成工序省略、追加对p型包层及接触层形成隆起部的工序以及形成电流阻挡层20的工序、将各半导体层的结构变更了的制造方法。

[0332]

产业上的可利用性

[0333]

本发明的半导体发光元件例如能够作为高输出且高效率的光源而用作激光加工用的光源。

[0334]

附图标记说明

[0335]

1、1a、1b、1c、1d、1e、1f、1g、101、201 半导体发光元件

[0336]

10 基板

[0337]

11 缓冲层

[0338]

12 n型包层

[0339]

13 n侧导引层

[0340]

14 活性层

[0341]

14a n侧第一势垒层

[0342]

14b n侧第二势垒层

[0343]

14c n侧第三势垒层

[0344]

14d 阱层

[0345]

14e p侧中间层

[0346]

14f p侧势垒层

[0347]

14g p侧导引层

[0348]

14h、14ha 第一中间势垒层

[0349]

14i 第一中间n侧势垒层

[0350]

14j 第一中间p侧势垒层

[0351]

15 第一应变控制层

[0352]

16 第二应变控制层

[0353]

17 p型包层

[0354]

18、218 接触层

[0355]

19 电流狭窄层

[0356]

19a 开口部

[0357]

20 电流阻挡层

[0358]

31 n侧电极

[0359]

32 p侧电极

[0360]

40 光射出端面部

[0361]

202 子装配体

[0362]

218r 隆起部

[0363]

218t 槽

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。