1.本公开的各方面一般地涉及振荡器,并且更具体地,涉及被配置为生成正交时钟信号的振荡器。

背景技术:

2.很多无线和有线通信系统采用正交振幅调制(qam)收发器来发射和接收数据。很多qam收发器包括正交时钟信号生成器,以提供用于对发射数据进行调制或编码以及对接收数据进行解调或解码的同相(i)和正交(q)时钟信号。i和q时钟信号之间的相位失配可能会在发射的信号和接收的信号中引入i/q失配减损,这继而可能导致信号劣化和数据错误。因为i/q相位失配可能与时钟频率相关,所以,例如,诸如在基于几吉比特的串行/解串(serdes)的通信中,随着时钟频率增大,使i/q相位失配最小化变得越来越重要。

技术实现要素:

3.提供本发明内容是为了以简化形式介绍下文将在具体实施方式中进一步描述的一些概念。本发明内容不旨在标识所要求保护的主题的关键特征或必要特征,也不旨在限制所要求保护的主题的范围。此外,本公开的系统、方法和装置均具有若干创新方面,没有任何单个方面独自负责本文所公开的期望属性。

4.本公开中描述的主题的一个创新方面可以用于在正交时钟生成器中减小同相(i)和正交(q)时钟信号之间的相位失配。在一些实施方式中,一种正交时钟生成器可以包括第一注入锁定振荡器、第二注入锁定振荡器、第一选择电路、第二选择电路和相位内插器。第一注入锁定振荡器可以被配置为至少部分地基于第一参考时钟信号生成多个第一时钟信号。第一选择电路可以耦合到第一注入锁定振荡器,并且可以被配置为选择第一时钟信号之一作为发射正交时钟信号。相位内插器可以耦合到第一注入锁定振荡器,并且被配置为基于多个第一时钟信号生成第二参考时钟信号。第二注入锁定振荡器可以被配置为至少部分地基于第二参考时钟信号生成多个第二时钟信号。第二选择电路耦合到第二注入锁定振荡器,并且被配置为选择第二时钟信号之一作为接收正交时钟信号。

5.本公开中描述的主题的另一个创新方面可以在可编程逻辑装置中实施。在一些实施方式中,该可编程逻辑装置可以包括发射数据处理块、接收数据处理块和正交时钟生成器。发射数据处理块可以被配置为使用发射正交信号发射数据,并且接收数据处理块可以被配置为使用接收正交信号接收数据。正交时钟生成器可以耦合到发射数据处理块和接收数据处理块,并且可以包括第一注入锁定振荡器、第一选择电路、相位内插器、第二注入锁定振荡器和第二选择电路。第一注入锁定振荡器可以被配置为至少部分地基于第一参考时钟信号生成多个第一时钟信号。第一选择电路可以被配置为选择第一时钟信号之一作为发射正交时钟信号。相位内插器可以耦合到第一注入锁定振荡器,并且被配置为基于第一时钟信号中的所选择的一对生成第二参考时钟信号。第二注入锁定振荡器可以被配置为至少部分地基于第二参考时钟信号生成多个第二时钟信号。第二选择电路可以被配置为选择第

二时钟信号之一作为接收正交时钟信号。

6.本公开中描述的主题的另一个创新方面可以被实施为一种用于操作正交时钟生成器的方法。在一些实施方式中,该方法可以包括:至少部分地基于第一参考时钟信号生成多个第一时钟信号;选择多个第一时钟信号之一作为发射正交时钟信号;至少部分地基于多个第一时钟信号生成第二参考时钟信号;至少部分地基于第二参考时钟信号生成多个第二时钟信号;以及选择多个第二时钟信号之一作为接收正交时钟信号。

7.下文提供了本公开中描述的主题的各方面的其他非限制性示例。

8.示例1:一种正交时钟生成器,包括:第一注入锁定振荡器,所述第一注入锁定振荡器被配置为至少部分地基于第一参考时钟信号生成多个第一时钟信号;第一选择电路,所述第一选择电路耦合到第一注入锁定振荡器,并且被配置为选择第一时钟信号之一作为发射正交时钟信号;相位内插器,所述相位内插器耦合到第一注入锁定振荡器,并且被配置为基于第一时钟信号中的所选择的一对生成第二参考时钟信号;第二注入锁定振荡器,所述第二注入锁定振荡器被配置为至少部分地基于第二参考时钟信号生成多个第二时钟信号;以及第二选择电路,所述第二选择电路耦合到第二注入锁定振荡器,并且被配置为选择第二时钟信号之一作为接收正交时钟信号。

9.示例2:根据示例1所述的正交时钟生成器,其中所述发射正交时钟信号包括第一同相(i)分量和第一正交(q)分量,并且所述接收正交时钟信号包括第二i分量和第二q分量。

10.示例3:根据示例1所述的正交时钟生成器,其中所述发射正交时钟信号被提供到关联可编程装置的发射数据处理块,所述接收正交时钟信号被提供到关联可编程装置的接收数据处理块。

11.示例4:根据示例3所述的正交时钟生成器,其中所述相位内插器被配置为至少部分地基于由接收数据处理块提供的输入信号生成第二参考时钟信号。

12.示例5:根据示例1所述的正交时钟生成器,其中多个第一时钟信号中的每个在相位上彼此偏移四十五度,并且多个第二时钟信号中的每个在相位上彼此偏移四十五度。

13.示例6:根据示例1所述的正交时钟生成器,其中第一注入锁定振荡器、相位内插器和第二注入锁定振荡器至少部分地由参考电压控制。

14.示例7:根据示例6所述的正交时钟生成器,还包括:正交锁定环(qll),所述正交锁定环被配置为至少部分地基于多个第二时钟信号生成控制信号;以及电压调节器,所述电压调节器被配置为至少部分地基于控制信号生成参考电压。

15.示例8:根据示例7所述的正交时钟生成器,还包括:粗略频率跟踪电路,所述粗略频率跟踪电路被配置为至少部分地基于检测到启动条件而选择性地禁用控制信号。

16.示例9:根据示例8所述的正交时钟生成器,其中所述电压调节器被配置为在检测到的启动条件期间建立正交锁定之前,控制第一注入锁定振荡器和第二注入锁定振荡器的振荡频率。

17.示例10:根据示例1所述的正交时钟生成器,其中:第一注入锁定振荡器至少部分地由第一参考电压控制;并且相位内插器和第二注入锁定振荡器至少部分地由第二参考电压控制。

18.示例11:根据示例10所述的正交时钟生成器,还包括:第一正交锁定环(qll),所述

第一qll被配置为至少部分地基于多个第一时钟信号生成第一控制信号;第一电压调节器,所述第一电压调节器被配置为至少部分地基于第一控制信号生成第一参考电压;第二qll,所述第二qll被配置为至少部分地基于多个第二时钟信号生成第二控制信号;以及第二电压调节器,所述第二电压调节器被配置为至少部分地基于第二控制信号生成第二参考电压。

19.示例12:根据示例11所述的正交时钟生成器,还包括粗略频率跟踪电路,所述粗略频率跟踪电路被配置为至少部分地基于检测到启动条件而选择性地禁用第一和第二控制信号。

20.示例13:一种可编程逻辑装置,包括:发射数据处理块,所述发射数据处理块被配置为使用发射正交时钟信号发射数据;接收数据处理块,所述接收数据处理块被配置为使用接收正交时钟信号接收数据;以及正交时钟生成器,所述正交时钟生成器耦合到发射数据处理块和接收数据处理块,包括:第一注入锁定振荡器,所述第一注入锁定振荡器被配置为至少部分地基于第一参考时钟信号生成多个第一时钟信号;第一选择电路,所述第一选择电路被配置为选择第一时钟信号之一作为发射正交时钟信号;相位内插器,所述相位内插器耦合到第一注入锁定振荡器,并且被配置为基于第一时钟信号中的所选择的一对生成第二参考时钟信号;第二注入锁定振荡器,所述第二注入锁定振荡器被配置为至少部分地基于第二参考时钟信号生成多个第二时钟信号;以及第二选择电路,所述第二选择电路被配置为选择第二时钟信号之一作为接收正交时钟信号。

21.示例14:根据示例13所述的可编程逻辑装置,其中第一注入锁定振荡器、相位内插器和第二注入锁定振荡器至少部分地由参考电压控制。

22.示例15:根据示例14所述的可编程逻辑装置,还包括:正交锁定环(qll),所述正交锁定环被配置为至少部分地基于多个第二时钟信号生成控制信号;以及电压调节器,所述电压调节器被配置为至少部分地基于控制信号生成参考电压。

23.示例16:根据示例15所述的可编程逻辑装置,还包括粗略频率跟踪电路,所述粗略频率跟踪电路被配置为至少部分地基于检测到启动条件而选择性地禁用控制信号。

24.示例17:一种用于操作正交时钟生成器的方法,包括:至少部分地基于第一参考时钟信号生成多个第一时钟信号;选择多个第一时钟信号之一作为发射正交时钟信号;至少部分地基于多个第一时钟信号生成第二参考时钟信号;至少部分地基于第二参考时钟信号生成多个第二时钟信号;以及选择多个第二时钟信号之一作为接收正交时钟信号。

25.示例18:根据示例17所述的方法,其中第二参考时钟信号是通过在一对第一时钟信号之间进行内插生成的。

26.示例19:根据示例17所述的方法,其中第二参考时钟信号是至少部分地基于来自接收数据处理块的输入信号生成的。

27.示例20:根据示例17所述的方法,其中多个第一时钟信号中的每个从多个第二时钟信号中的对应一个偏移四十五度。

附图说明

28.本文描述的示例性实施方式是以举例的方式例示的,并且不旨在受到附图中的图的限制。在整个附图和说明书中,类似的数字指代类似的元件。需注意,以下附图的相对尺

寸可能未按比例绘制。

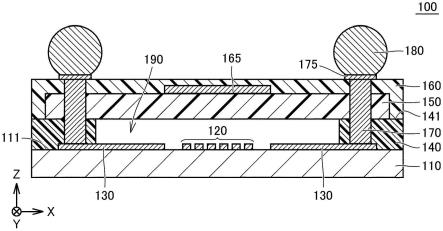

29.图1示出了可以在其内实施本公开的各方面的示例性可编程装置的框图。

30.图2示出了根据一些实施方式的收发器的简化框图。

31.图3示出了根据一些实施方式的示例性正交时钟生成器的框图。

32.图4a示出了根据一些实施方式的另一个示例性正交时钟生成器的框图。

33.图4b示出了根据其他实施方式的另一个示例性正交时钟生成器的框图。

34.图5a示出了根据一些实施方式的再一个示例性正交时钟生成器的框图。

35.图5b示出了根据其他实施方式的再一个示例性正交时钟生成器的框图。

36.图6示出了根据一些实施方式的例示性流程图,其绘示了用于操作正交时钟生成器的示例性操作。

具体实施方式

37.本公开的各方面可以用于减小或最小化可能劣化有线和无线通信的信号完整性的i/q失配和其他相位误差。在一些实施方式中,公开了一种正交时钟生成器,其利用两个注入锁定振荡器和单个相位内插器来生成同相(i)和正交(q)时钟信号的第一集合以及i和q时钟信号的第二集合。i和q时钟信号的第一和第二集合可以相对于彼此相移,并且可以用于发射和接收数据。通过使用单个相位内插器而不是多个相位内插器,本公开的各方面可以相对于常规正交时钟生成器减小相位失配。

38.在以下描述中,阐述了很多具体细节,例如,具体部件、电路和工艺的示例,以提供对本公开的透彻理解。本文所使用的术语“耦合”表示直接耦合到或通过一个或多个居间部件或电路耦合。而且,在以下描述中,为了解释的目的,阐述了具体术语和/或细节,以便提供对示例性实施方式的透彻理解。然而,本领域技术人员要明了的是,可能不需要采用这些具体细节来实践示例性实施方式。在其他实例中,公知的电路和装置以框图形式示出,以避免使本公开难以理解。通过本文描述的各种总线提供的任何信号都可以与其他信号进行时间复用,并且通过一个或多个公共总线被提供。另外,电路元件或软件块之间的互连可以被示为总线或单个信号线(single signal line)。总线中的每个可以替代地是单个信号线,并且单个信号线中的每个可以替代地是总线,单个线或总线可以代表用于部件之间通信的大量物理或逻辑机构的任何一种或多种。示例性实施方式不应被理解为限于本文描述的具体示例,而是在其范围内包括所附权利要求定义的所有实施方式。

39.图1示出了可以在其内实施本公开各方面的示例性可编程装置100的框图。在一些实施方式中,装置100可以形成于单个管芯上。在其他实施方式中,装置100可以跨多个管芯分布。另外地,或者替代地,装置100可以被实施为包括若干能够彼此交互的子系统的片上系统(soc)。于是,图1中所示的可编程装置100是可以在其内实施本公开的各方面的可编程装置的例示性示例;具有另外的或更少的处于相似或不同布置方式的块或模块的其他实施方式是可能的。

40.装置100可以包括若干子系统,例如可编程逻辑(pl)110、片上网络(noc)互连系统120、专用电路130、ccix和pcie模块(cpm)140、连接构造(connectivity fabric)145、收发器150、输入/输出(i/o)块160和存储器控制器170。在一个或多个实施方式中,装置100可以包括图1中未示出的其他子系统或部件。此外,尽管为了简单未示出,但装置100可以耦合到

若干外围部件(例如,一个或多个高性能存储器装置195)和/或其他装置或芯片(例如,另一个可编程装置)。

41.pl 110包括可以被编程以执行若干不同用户定义的功能或操作的电路。在一些实施方式中,pl 110可以包括可编程电路块或片(tile)的阵列,可编程电路块或片均包括可编程互连电路和可编程逻辑电路。可编程电路块可以包括(但不限于)可配置逻辑块(clb)、随机存取存储器块(bram)、数字信号处理块(dsp)、时钟管理器、延迟锁定环(dll)和/或能够被编程或配置为实施用户指定的电路设计的其他逻辑或电路。另外地,或者替代地,pl 110可以包括若干输入/输出块(iob)。在一个或多个实施方式中,pl 110可以被实施为能够跨可编程构造分布的可编程构造子区域(fabric sub-region,fsr)的阵列。在一些方面中,fsr可以被实施为可编程构造内的可重复片。

42.可编程互连电路可以包括由可编程互连点(pip)互连的长度各异的多个互连线。互连线可以被配置为在特定可编程片内的部件之间、在不同可编程片内的部件之间、以及在可编程片和其他子系统或装置的部件之间提供连接。可以通过向配置寄存器中加载配置数据来对可编程互连电路和可编程电路块进行编程或配置,该配置数据定义可编程元件如何被配置和操作以实施对应的用户指定的电路设计。在一些方面中,若干可编程电路块中的每个内的可编程互连电路可以形成为装置100提供块级和/或装置级信号路由资源可编程互连构造的部分。

43.每个clb可以包括查找表(lut)、触发器、组合逻辑和/或可编程互连电路,它们可以由配置数据统一编程以对宽度各异的输入信号执行各种逻辑功能(例如,加法和减法)。lut可以是任何适当大小,并且可以包括任何适当数量的输入和输出。在一些方面中,每个clb可以包括32个lut和64个触发器。clb中的每个还可以包括能够用于实施更宽的逻辑功能的乘法器和算术执行逻辑。在一些实施方式中,pl 110的资源可以被实施为在可编程装置100中布置成列的可重复片,并且可以被分成若干固定高度和宽度的区域。对于图1的示例而言,pl 110被绘示为占据装置100的不同区域。在其他实施方式中,pl 110可以被实施为可编程构造的统一区域。

44.可以被制造为装置100的一部分的noc互连系统120提供可以选择性地使装置100的各种资源、子系统、电路和其他部件互连的高速、高带宽的可编程信号路由网络。如图1所示,在一些实施方式中,noc互连系统120可以跨装置100的可编程构造在水平和垂直方向上(例如,朝向边缘)延伸。另外地,或者替代地,noc互连系统120可以跨可编程构造在一个或多个对角线方向上延伸。此外,尽管在图1的示例中示为具有单个柱状(columnar)部分,但在其他实施方式中,noc互连系统120可以包括跨可编程构造的高度垂直延伸的多个柱状部分。因此,示例性noc互连系统120的特定布局、形状、大小、取向和其他物理特性仅仅用于例示本文所公开的各种实施方式。

45.在一些实施方式中,noc互连系统120可以采用数据包协议(data packet protocol)和存储器映射地址以将信息作为打包的数据在装置100的各种资源、子系统、电路和其他部件之间进行路由。数据包可以包括可以由noc互连系统120使用以将数据包路由到其指示的目的地的源地址、目的地地址和协议信息。在一个或多个实施方式中,数据包可以包括服务质量(qos)信息,qos信息允许例如基于分配的优先级、流量类型和/或流信息对数据包通过noc互连系统120的传输进行优先化。在这样的实施方式中,noc互连系统120可

以包括优先逻辑,该优先逻辑能够确定所接收数据包的流量类别的优先级等级,并且在对数据包排队进行传输时使用所确定的优先级等级或流量类型。

46.尽管为了简单起见未示出,noc互连系统120也可以包括调度器和仲裁逻辑。调度器可以用于使用noc互连系统120的一个或多个物理和/或虚拟信道,将数据包的传输从源地址调度到目的地地址。仲裁逻辑可以用于仲裁对noc互连系统120的访问,例如,以使冲突和其他争用相关的延迟最小化。对于使用堆叠硅互连(ssi)技术制造装置100的实施方式,noc互连系统120的柱状部分可以在相邻的超级逻辑区域(slr)之间提供信号连接,例如,以允许在主slr和从slr之间路由配置数据。

47.在一些实施方式中,noc互连系统120可以包括在noc互连系统120和装置100的各种资源、子系统、电路和其他部件之间提供选择性连接的多个节点、端口或其他接口(为了简单起见未示出)。例如,noc互连系统120可以允许装置100的多个子系统共享对片上存储器(ocm)资源、处理资源和/或i/o资源的访问。通过选择性地使装置100中可能需要和使用大量数据的各种资源、子系统、电路和其他部件互连,noc互连系统120可以减轻本地互连资源上的信号路由负担,由此提高装置性能并允许比其他可编程装置更大的配置灵活性。而且,通过提供比装置级和块级可编程互连具有更高数据传输速率和更低误差率的高性能信号路由网络,noc互连系统120可以(与其他可编程装置相比)提高装置100的处理能力和数据吞吐量。

48.专用电路130可以包括任何适当的硬连线电路,该硬连线电路包括(但不限于)处理器、串行收发器、数字信号处理器(dsp)、模数转换器(adc)、数模转换器(dac)、装置管理资源、装置监测资源、装置测试管理资源等。在一些实施方式中,专用电路130可以包括处理系统(ps)和平台管理控制器(pmc)。在一些实施方式中,ps可以包括若干处理器核心、高速缓存存储器、和可配置为直接耦合到装置100的i/o引脚的单向和/或双向接口。在一些方面中,每个处理器核心可以包括能够用于顺序数据处理的中央处理单元(cpu)或标量处理器。pmc可以用于基于从外部存储器提供的配置数据(例如,配置比特流)启动和配置装置100。pmc还可以用于配置pl 110并控制装置100的各种加密、认证、系统监测和调试能力。

49.ccix和pcie模块(cpm)140可以包括在装置100和若干外部部件(例如,外部装置或芯片)之间提供连接的若干接口。在一些实施方式中,cpm 140可以包括若干外围互连快速(pcie)接口和用于加速器的缓存一致性互连(ccix)接口,该pcie和ccix接口经由收发器150提供到其他装置或芯片的连接。在一些方面中,pcie和ccix接口可以被实施为收发器150的部分。

50.可编程互连构造(为了简单起见未示出)可以提供块级和/或装置级信号路由资源,该块级和/或装置级信号路由资源能够基于加载到对应的配置寄存器中的配置数据选择性地使可编程构造的附近区域中的电路和子系统互连。在一些实施方式中,可编程互连构造可以包括多个构造子区域(fsr),fsr可以被实施为可重复片并且跨装置100分布。在一些方面中,fsr可以包括与pl 110的各种可编程逻辑电路(例如,clb、dsp和bram)相关联的可编程互连元件的部分。

51.收发器150可以提供与连接到装置100的一个或多个其他装置或芯片(为简单起见未示出)的信号连接。收发器150可以包括若干不同的数据串行器和解串行器(serdes),例如,吉比特串行收发器。如图1中所示,在一些实施方式中,收发器150可以被实施为沿装置

100的右侧和左侧的各个位置定位的若干可重复片。在其他实施方式中,收发器150可以被定位于装置100的其他适当位置中。

52.i/o块160耦合到装置的i/o引脚(为简单起见未示出)并且可以为装置100提供i/o能力。例如,i/o块160可以从一个或多个其他装置接收数据,并且可以向装置100中的若干目的地驱动所接收的数据。i/o块160也可以从装置100中的若干源接收数据,并且可以经由装置的i/o引脚向一个或多个其他装置驱动所接收的数据。在一些实施方式中,i/o块160可以被实施为可重复片。装置100可以包括任何适当数量的i/o块160,并且因此图1中所示的示例性实施方式仅仅是例示性的。

53.i/o块160可以包括任何数量的适当i/o电路或装置。在一些实施方式中,i/o块160可以包括极高性能i/o(xpio)电路、高密度i/o(hdio)电路和复用i/o(mio)电路。xpio电路可以进行优化以用于高性能通信,例如提供到存储器控制器170的高速度、低延迟接口。hdio电路可以提供支持更低速度和更高电压i/o能力(与xpio电路相比)的成本有效的方案。mio电路可以提供能够由各种子系统访问的通用i/o资源,例如,各种子系统例如是pl 110、专用电路130和cpm 140。

54.在一些实施方式中,i/o块160的第一行可以被实施为沿装置100的底部边缘定位的可重复片,并且i/o块160的第二行可以被实施为沿装置100的顶部边缘定位的可重复片。在一些方面中,实施i/o块160的可重复片可以彼此不同。例如,一些i/o块160可以实施xpio电路,其他i/o块160可以实施hdio电路,其他i/o块160可以实施mio电路。

55.存储器控制器170可以用于控制对装置100内和/或外部提供的各种存储器资源的访问。存储器控制器170可以包括双倍数据速率v4(ddr4)存储器控制器、双倍数据速率v5(ddr5)存储器控制器、高带宽存储器(hbm)控制器和/或其他适当的存储器控制器。在一个或多个实施方式中,存储器控制器170中的一些或全部可以包括调度器,该调度器具有可以改善存储器访问效率的事务重新排序能力。

56.在一些实施方式中,存储器控制器170的第一行可以被实施为沿装置100的底边缘定位的可重复片,并且存储器控制器170的第二行可以被实施为沿装置100的顶边缘定位的可重复片。在一些方面中,实施存储器控制器170的可重复片可以彼此不同。例如,第一数量的存储器控制器170可以实施ddr4存储器控制器,第二数量的存储器控制器170可以实施lpddr4存储器控制器,并且第三数量的存储器控制器170可以实施hbm控制器。例如,如图1的示例中所示,实施i/o块160和存储器控制器170的可重复片可以彼此交替地定位或分布。装置100可以包括任何数量的i/o块160和存储器控制器170,并且因此图1中绘示的i/o块160和存储器控制器170的数量和位置仅仅是例示性的。

57.尽管为了简单起见在图1中未示出,但装置100可以包括在pl110内提供的在i/o块160和可编程互连之间提供连接的边界逻辑接口(bli)。在一些方面中,bli可以允许大而复杂的外部装置(例如,hbm)表现出是装置100的可编程构造中的小得多的块(例如,clb)。在一些实施方式中,bli可以布置于被定位在可编程构造的顶部和底部边界或边缘的行中。通过这种方式,bli可以用于在柱状逻辑结构(例如,clb列或dsp列)和i/o资源行(例如,i/o块160)之间路由信号。

58.图2示出了根据一些实施方式的收发器200的简化框图。收发器200可以是图1的收发器150中的一个或多个的一个示例,收发器200被示出为包括耦合于输入端子(in)和输出

端子(out)之间的发射(tx)前端210、发射数据处理块220、正交时钟生成器230、接收(rx)数据处理块240和接收前端250。在一些实施方式中,收发器200可以是吉比特serdes收发器。在其他实施方式中,收发器200可以是另一种适当类型或配置方式。

59.正交时钟生成器230耦合到tx数据处理块220和rx数据处理块240,包括输入端子以接收参考时钟信号clk

ref

。对于图2的示例而言,参考时钟信号clk

ref

是由参考时钟生成器201生成的,参考时钟生成器201可以是包括(但不限于)基于晶体的振荡器、锁相环等的任何可行的参考时钟源。在其他实施方式中,参考时钟信号clk

ref

可以由另一适当的电路或振荡器生成。

60.正交时钟生成器230可以基于clk

ref

生成第一正交时钟信号231和第二正交时钟信号232。在一些实施方式中,第一正交时钟信号231可以用于发射数据,并且第二正交时钟信号232可以用于接收数据。尽管为了简单起见在图2中未示出,但第一正交时钟信号231可以包括同相(i)分量和正交(q)分量,并且第二正交时钟信号232可以包括i分量和q分量。在一些实施方式中,第一正交时钟信号231的i和q分量(也可以称为i和q时钟信号)可以被实施为微分信号,并且第二正交时钟信号232的i和q分量(也可以称为i和q时钟信号)可以被实施为微分信号。

61.在一个或多个实施方式中,第一正交时钟信号231可以在频率上与第二正交时钟信号232相关,但可以在相位上相对于第二正交时钟信号232偏移。例如,第一和第二正交时钟信号231-232可以具有相同的频率,并且在相位上彼此偏移45度。作为另一个示例,第一和第二正交时钟信号231-232可以具有相同的频率,并且在相位上彼此偏移90度(或45度的某个其他适当整数倍)。

62.发射数据处理块220耦合于正交时钟生成器230和发射前端210之间,可以接收由正交时钟生成器230生成的第一正交时钟信号231。发射数据处理块220也可以接收要由收发器200发射的输出数据221。输出数据221可以由图1的可编程装置100的pl 110、专用电路130或任何其他可行的电路、部件或子系统提供。发射数据处理块220可以使用第一正交时钟信号231来对数据处理221进行编码和/或调制以用于发射。在一些实施方式中,发射数据处理块220可以基于第一正交时钟信号231对输出数据221进行串行化。

63.发射前端210可以处理发射数据处理块220提供的已编码和/或已调制的输出数据,并且可以将已处理的输出数据作为发射数据211提供给有线或无线通信介质。发射前端210可以包括任何数量的适于准备已处理的输出数据以作为发射数据211来发射的电路或者部件。例如,在一些方面中,发射前端210可以包括放大器、混频器、滤波器和被配置为提高信号完整性同时使噪声、失真和定时误差最小化的其他部件。

64.接收前端250可以从一个或多个其他装置或电路,经由无线介质或有线连接、经由输入端子in接收rx数据251。在一些实施方式中,接收前端250可以包括放大器、混频器、滤波器和适于最大化数据接收速率同时使数据损失、噪声和失真最小化的任何其他电路或部件。接收前端250可以向接收数据处理块240提供rx数据251。

65.接收数据处理块240也耦合到正交时钟生成器230,接收数据处理块240可以使用第二正交时钟信号232来对rx数据251进行解码和/或解调,以生成输入数据241。输入数据241可以被提供(或路由)到图1的可编程装置100的pl 110、专用电路130或任何其他可行的电路、部件或子系统。在一些实施方式中,接收数据处理块240可以基于第二正交时钟信号

232对rx数据251进行解串行化。

66.图3示出了根据一些实施方式的示例性正交时钟生成器300的框图。正交时钟生成器300可以包括注入锁定振荡器(ilo)310、第一相位内插器321、第二相位内插器322、正交锁定环(qll)340和电压调节器350。在一些方面中,正交时钟生成器300可以是图2的正交时钟生成器230的一个示例。

67.ilo 310包括耦合到参考时钟生成器201的第一输入端、耦合到电压调节器350的第二输入端、以及耦合到第一和第二相位内插器321-322的输出端,ilo 310可以是能够生成与参考时钟信号clk

ref

具有相同频率但在相位上彼此偏移的多个时钟信号的任何适当的ilo。在一些实施方式中,ilo 310可以被配置为微分振荡器,并且参考时钟生成器201可以提供clk

ref

作为微分时钟信号。

68.ilo 310可以生成数量为m、频率锁定到clk

ref

的时钟信号clk

ilo

,其中m是大于1的整数。也可以称为时钟相位的时钟信号clk

ilo

可以在相位上彼此间距相等或偏移,例如,使得时钟信号clk

ilo

中的每个具有是参考相位偏移的整数倍的唯一相位。例如,在图3的实施方式中,ilo 310生成m=八个在相位上彼此偏移四十五度的时钟信号clk

ilo

,其中第一时钟信号clk_0没有相位偏移,第二时钟信号clk_45相对于clk_0具有45度的相位偏移,第三时钟信号clk_90相对于clk_0具有90度的相位偏移,第四时钟信号clk_135相对于clk_0具有135度的相位偏移,第五时钟信号clk_180相对于clk_0具有180度的相位偏移,第六时钟信号clk_225相对于clk_0具有225度的相位偏移,第七时钟信号clk_270相对于clk_0具有270度的相位偏移,并且第八时钟信号clk_315相对于clk_0具有315度的相位偏移。

69.第一相位内插器321和第二相位内插器322可以使用互补金属氧化物硅(cmos)技术、电流模式逻辑(cml)或任何其他可行技术来实施。第一相位内插器321可以使用由ilo 310提供的m个时钟信号clk

ilo

的第一集合来生成一个或多个同相(i)输出时钟信号,并且第二相位内插器322可以使用由ilo 310提供的m个时钟信号clk

ilo

的第二集合来生成一个或多个正交(q)输出时钟信号。在图3的示例中,第一相位内插器321可以生成被表示为i和信号的微分同相(i)输出时钟信号,其中是i的逻辑补码。类似地,第二相位内插器322可以生成被表示为q和信号的微分正交(q)输出时钟信号,其中是q的逻辑补码。在其他情况下,第一和第二相位内插器321-322可以分别生成单端i和q时钟信号。

70.在一些实施方式中,第一相位内插器321可以在时钟信号clk

ilo

的第一集合(或第二集合)的相邻的时钟信号对之间进行内插,以生成同相输出时钟信号,例如,使得i和信号可以具有任何期望相位。类似地,第二相位内插器322可以在时钟信号clk

ilo

的第二集合(或第一集合)的相邻的时钟信号对之间进行内插,以生成正交输出时钟信号,例如,使得q和信号可以具有任何期望相位。

71.qll 340包括耦合到ilo 310的一个或多个输出端的若干输入端,并且包括耦合到电压调节器350的控制端子的输出端。在一些实施方式中,qll 340可以接收m个时钟信号clk

ilo

(例如,时钟信号clk_0、clk_45、clk_90、clk_135、clk_180、clk_225、clk_270和clk_315),并且可以被配置为基于m个时钟信号clk

ilo

之间的一个或多个关系生成控制信号(ctrl)。ctrl信号被提供到电压调节器350的控制输入端,电压调节器继而可以至少部分地基于ctrl信号生成参考电压v

ref

。

72.电压调节器350可以向ilo 310、第一相位内插器321和第二相位内插器322的控制端子提供参考电压v

ref

。参考电压v

ref

可以用于控制、调节或修改ilo 310、第一相位内插器321和第二相位内插器322的一个或多个操作特性。

73.在一些实施方式中,qll 340也可以接收由图2的接收数据处理块240提供的一个或多个信号(为简单起见未示出)。这些一个或多个信号可以实现或指示传入的rx数据的各种特性,并且qll 340可以被配置为至少部分地基于这些一个或多个信号生成控制信号ctrl。例如,在一些方面中,这些一个或多个信号可以以这样的方式调节参考电压v

ref

,该方式使第一相位内插器321维持同相输出时钟信号和rx数据之间的特定关系,和/或使第二相位内插器322维持正交输出时钟信号和rx数据之间的特定关系。

74.第一和第二相位内插器321-322内的电路元件(例如,混频器和滤波器)之间的失配可能导致同相输出时钟信号和正交时钟信号之间的定时失配。根据本公开的其他方面,通过使用单个相位内插器(而不是图3的两个相位内插器321-322),可以避免i和q输出时钟信号之间的定时失配。

75.图4a示出了根据一些实施方式的另一个示例性正交时钟生成器400的框图。正交时钟生成器400可以是图2的正交时钟生成器230的示例,正交时钟生成器400被示出为包括第一ilo 411、第二ilo412、相位内插器420、若干缓存431、433和435、若干选择电路432和434、正交锁定环(qll)440、电压调节器450、粗略频率跟踪电路460和开关465。

76.第一ilo 411包括耦合以接收第一参考电压v

ref1

的第一输入端、耦合到电压调节器450的第二输入端、以及耦合到第一缓存431的输出端,第一ilo 411可以是能够生成与参考时钟信号clk

ref

具有相同频率但在相位上彼此偏移的多个时钟信号的任何适当的ilo。第一参考时钟信号clk

ref

可以由参考时钟生成器201(图4中为了简单起见未示出)生成,或者替代地由另一个适当的时钟发生电路生成。在一些实施方式中,第一ilo 411可以被配置为微分振荡器,并且参考时钟生成器201可以提供clk

ref1

作为微分时钟信号。

77.第一ilo 411可以生成数量为p、频率锁定到clk

ref1

的第一时钟信号clk

ilo1

,其中p是大于1的整数。也可以称为时钟相位的第一时钟信号clk

ilo1

可以在相位上彼此间距相等或偏移,例如,使得第一时钟信号clk

ilo1

中的每个具有是参考相位偏移的整数倍的唯一相位。例如,在一些实施方式中,第一ilo 411可以生成p=8个在相位上彼此偏移四十五度的第一时钟信号clk

ilo1

,其中第一时钟信号clk_0没有相位偏移,第二时钟信号clk_45相对于clk_0具有45度的相位偏移,第三时钟信号clk_90相对于clk_0具有90度的相位偏移,第四时钟信号clk_135相对于clk_0具有135度的相位偏移,第五时钟信号clk_180相对于clk_0具有180度的相位偏移,第六时钟信号clk_225相对于clk_0具有225度的相位偏移,第七时钟信号clk_270相对于clk_0具有270度的相位偏移,并且第八时钟信号clk_315相对于clk_0具有315度的相位偏移。

78.在一些实施方式中,由第一ilo 411生成的第一时钟信号clk

ilo1

可以由缓存431缓存,以生成缓存的第一时钟信号clk

ilo1’,其可以被提供给相位内插器420和第一选择电路432。在其他实施方式中,可以省略任选缓存431(由虚线示出),并且可以将第一时钟信号clk

ilo1

提供给相位内插器420和第一选择电路432。在一些实施方式中,任选缓存435(由虚线示出)可以缓存所缓存的第一时钟信号clk

ilo1’用于相位内插器420。在其他实施方式中,可以省略任选缓存435。

79.相位内插器420可以使用由第一ilo 411提供的第一时钟信号clk

ilo1

来生成第二参考时钟信号clk

ref2

。在图4的示例中,相位内插器420可以生成第二参考时钟信号clk

ref2

作为微分信号。在一些实施方式中,相位内插器420可以在多个第一时钟信号clk

ilo1

中的相邻的时钟信号对之间进行内插,以生成第二参考时钟信号clk

ref2

。通过这种方式,相位内插器420可以生成与第一时钟信号clk

ilo1

具有任意相位关系的第二参考时钟信号clk

ref2

。另外地,或者替代地,相位内插器420可以从相关联的接收电路(例如,时钟数据恢复电路和/或接收数据处理块)接收信号422,并且可以使用信号422来控制或调节内插。

80.相位内插器420可以使用互补金属氧化物硅(cmos)技术、电流模式逻辑(cml)或任何其他可行的技术来实施。在一些实施方式中,相位内插器420可以是图3的第一相位内插器321或第二相位内插器322的示例。因此,尽管为简单起见未示出,但数量为p的第一时钟信号clk

ilo1

中的每个可以被提供给相位内插器420的对应的输入端,并且相位内插器420可以基于数量为p的第一时钟信号clk

ilo1

之间的关系来生成第二参考时钟信号clk

ref2

。

81.第一选择电路432可以被配置为选择第一时钟信号clk

ilo1

中的两个(或一对)作为i/q输出时钟信号416进行提供。在一些实施方式中,第一选择电路432可以选择任何适当的第一时钟信号clk

ilo1

的对作为i/q tx输出时钟信号416进行提供。诸如图2的发射数据处理块220的发射电路可以使用i/q输出时钟信号416来对数据进行编码或调制以用于发射。

82.第二ilo 412包括耦合到相位内插器420的第一输入端、从电压调节器450接收v

ref

的第二输入端、以及耦合到任选缓存433(如虚线所示)的输出端,第二ilo 412可以是能够生成与第二参考时钟信号clk

ref2

具有相同频率但在相位上彼此偏移的多个时钟信号的任何适当的ilo。第二ilo 412可以生成数量为p、频率锁定到clk

ref2

的第二时钟信号clk

ilo2

,其中p是大于1的整数。也可以称为时钟相位的第二时钟信号clk

ilo2

可以在相位上彼此间距相等或偏移,例如,使得第二时钟信号clk

ilo2

中的每个具有是参考相位偏移的整数倍的唯一相位。

83.在一些实施方式中,第二时钟信号clk

ilo2

也可以在相位上彼此间距相等或偏移,例如,使得第二时钟信号clk

ilo2

中的每个具有是参考相位偏移的整数倍的唯一相位。例如,在一些实施方式中,第二ilo 412可以生成p=8个在相位上彼此偏移四十五度的第二时钟信号clk

ilo2

,其中第一时钟信号clk_0没有相位偏移,第二时钟信号clk_45相对于clk_0具有45度的相位偏移,第三时钟信号clk_90相对于clk_0具有90度的相位偏移,第四时钟信号clk_135相对于clk_0具有135度的相位偏移,第五时钟信号clk_180相对于clk_0具有180度的相位偏移,第六时钟信号clk_225相对于clk_0具有225度的相位偏移,第七时钟信号clk_270相对于clk_0具有270度的相位偏移,并且第八时钟信号clk_315相对于clk_0具有315度的相位偏移。在一些方面中,第二时钟信号clk

ilo2

可以被提供给任选缓存433,以生成多个缓存的第二时钟信号clk

ilo2’。

84.第二选择电路434可以被配置为选择第二时钟信号clk

ilo2

中的两个(或一对)作为i/q rx输出时钟信号436进行提供。在一些实施方式中,第二选择电路434可以选择任何适当的第二时钟信号clk

ilo2

的对作为i/q rx输出时钟信号436进行提供。诸如图2的接收数据处理块240的接收电路可以使用i/q rx输出时钟信号436来对由收发器400接收的数据进行解码或解调。

85.qll 440包括(经由任选缓存433)耦合到第二ilo 412的一个或多个输出端的若干

输入端,并且包括耦合到电压调节器450的控制端子的输出端。在一些实施方式中,qll 440可以接收数量为p的第二时钟信号clk

ilo2

(例如,时钟信号clk_0、clk_45、clk_90、clk_135、clk_180、clk_225、clk_270和clk_315),并且可以被配置为基于第二时钟信号clk

ilo2

之间的一个或多个关系生成控制信号(ctrl)。ctrl信号被提供到电压调节器450的控制输入端,电压调节器继而可以至少部分地基于ctrl信号生成参考电压v

ref

。

86.电压调节器450可以向第一ilo 411、第二ilo 412、相位内插器420和任选缓存431和433的控制端子提供参考电压v

ref

。参考电压v

ref

可以用于控制、调节或修改第一ilo 411、第二ilo 412和相位内插器420(以及任选缓存431和433)的一个或多个操作特性。在一些实施方式中,qll 440可以基于第二时钟信号clk

ilo2

的相对相位控制或调节控制信号(ctrl)的值。电压调节器450可以至少部分地基于控制信号(ctrl)调节v

ref

的值,由此允许qll 440基本控制第一ilo 411、第二ilo 412和相位内插器420的各种操作。在一些实施方式中,电压调节器450还可以控制任选缓存431和433的操作。

87.粗略频率跟踪电路460可以包括有限状态机(fsm)461和数模转换器(dac)462,粗略频率跟踪电路460可以用于控制至少第一ilo 411和第二ilo 412的初始启动操作。在一些实施方式中,粗略频率跟踪电路460可以响应于检测到启动条件而生成控制电压v

ctrl

,并且使用控制电压v

ctrl

临时禁用由qll 440在启动操作期间生成的ctrl信号。更具体而言,在检测到启动条件时,fsm 461可以使选择信号生效,该选择信号使开关465闭合(例如,处于导电状态),并且fsm 461可以输出数字电压或代码,该数字电压或代码使得dac462将v

ctrl

驱动到经由开关465禁用ctrl信号的电平,例如,使得电压调节器450能够在启动条件期间建立正交锁定之前,控制至少第一ilo 411和第二ilo 512的振荡频率。在其他时间,fsm 461可以使sel信号失效,以使开关465关断(例如,以将开关465维持在非导电状态)。

88.在一些实施方式中,i/q失配可能存在于i/q tx时钟信号416之间和/或可能存在于i/q rx时钟信号436之间。i/q tx时钟信号416之间的失配和i/q rx时钟信号436之间的失配可能是由于qll 440监测第二时钟信号clk

ilo2

而未监测第一时钟信号clk

ilo1

导致的。

89.图4b示出了根据其他实施方式的另一个示例性正交时钟生成器401的框图。正交时钟生成器401在很多方面类似于图4a的正交时钟生成器400,不同之处在于qll 440接收缓存的第一时钟信号clk

ilo1’作为输入信号,而不是例如接收缓存的第二时钟信号clk

ilo2’作为输入信号。

90.图5a示出了根据一些实施方式的再一个示例性正交时钟生成器500的框图。正交时钟生成器500可以包括第一ilo 511、第二ilo512、相位内插器520、第一任选缓存531、第一选择电路532、第二任选缓存533、第二选择电路534、第一qll 541、第二qll 542、第一电压调节器551、第二电压调节器552、粗略频率跟踪电路560、第一开关561和第二开关562。如下文更详细地描述的,正交时钟生成器500可以使用第一qll 541来控制由发射数据处理块使用的i/q tx时钟信号516,并且可以使用第二qll 542来控制由接收数据处理块使用的i/q rx信号536。

91.第一ilo 511包括耦合以接收第一参考时钟信号clk

ref1

的第一输入端、耦合以接收由第一电压调节器551生成的第一参考电压v

ref1

的第二输入端、以及耦合到第一缓存531的输出端,第一ilo 511可以是能够生成与第一参考时钟信号clk

ref1

具有相同频率但在相位上彼此偏移的多个时钟信号的任何适当的ilo。第一参考时钟信号clk

ref1

可以由参考时

钟生成器201(图5中为了简单起见未示出)生成,或者替代地由另一个适当的时钟发生电路生成。在一些实施方式中,第一ilo 511可以被配置为微分振荡器,并且参考时钟生成器201可以提供clk

ref1

作为微分时钟信号。

92.第一ilo 511可以生成数量为n、频率锁定到clk

ref1

的第一时钟信号clk

ilo1

,其中n是大于1的整数。也可以称为时钟相位的第一时钟信号clk

ilo1

可以在相位上彼此间距相等或偏移,例如,使得第一时钟信号clk

ilo1

中的每个具有是参考相位偏移的整数倍的唯一相位。例如,在一些实施方式中,第一ilo 511可以生成n=8个在相位上彼此偏移四十五度的第一时钟信号clk

ilo1

,其中第一时钟信号clk_0没有相位偏移,第二时钟信号clk_45相对于clk_0具有45度的相位偏移,第三时钟信号clk_90相对于clk_0具有90度的相位偏移,第四时钟信号clk_135相对于clk_0具有135度的相位偏移,第五时钟信号clk_180相对于clk_0具有180度的相位偏移,第六时钟信号clk_225相对于clk_0具有225度的相位偏移,第七时钟信号clk_270相对于clk_0具有270度的相位偏移,并且第八时钟信号clk_315相对于clk_0具有315度的相位偏移。

93.在一些实施方式中,由第一ilo 511生成的第一时钟信号clk

ilo1

可以由缓存531缓存,以生成缓存的第一时钟信号clk

ilo1’,其可以被提供给相位内插器520、第一选择电路532和第一qll 541。在其他实施方式中,可以省略任选缓存531(由虚线示出),并且可以将第一时钟信号clk

ilo1

提供给相位内插器520、第一选择电路532和第一qll 541。在一些实施方式中,任选缓存535(由虚线示出)可以缓存所缓存的第一时钟信号clk

ilo1’用于相位内插器520。在其他实施方式中,可以省略任选缓存535。

94.第一qll 541包括(经由任选缓存531)耦合到第一ilo 511的一个或多个输出端的若干输入端,并且包括耦合到第一电压调节器551的控制端子的输出端。在一些实施方式中,第一qll 541可以接收数量为n的第一时钟信号clk

ilo1

(例如,时钟信号clk_0、clk_45、clk_90、clk_135、clk_180、clk_225、clk_270和clk_315),并且可以被配置为基于第一时钟信号clk

ilo1

之间的一个或多个关系生成第一控制信号(ctrl1)。ctrl1信号被提供到第一电压调节器551的控制输入端,第一电压调节器继而可以至少部分地基于ctrl1信号生成v

ref1

。

95.第一电压调节器551可以向第一ilo 511和任选缓存531的控制端子提供v

ref1

,例如,以控制、调节或修改第一ilo 511和任选缓存531的一个或多个操作特性。在一些实施方式中,第一qll 541可以基于第一时钟信号clk

ilo1

的相对相位控制或调节ctrl1的值。第一电压调节器551可以至少部分地基于ctrl1信号调节v

ref1

的值,由此允许第一qll 541控制第一ilo 511的各种操作。

96.相位内插器520可以使用由第一ilo 511提供的第一时钟信号clk

ilo1

来生成第二参考时钟信号clk

ref2

。在图5的示例中,相位内插器520可以生成第二参考时钟信号clk

ref2

作为微分信号。在一些实施方式中,相位内插器520可以在多个第一时钟信号clk

ilo1

中的相邻的时钟信号对之间进行内插,以生成第二参考时钟信号clk

ref2

。通过这种方式,相位内插器520可以生成与第一时钟信号clk

ilo1

具有任意相位关系的第二参考时钟信号clk

ref2

。另外地,或者替代地,相位内插器520可以从相关联的接收电路(例如,时钟数据恢复电路和/或接收数据处理块)接收信号522,并且可以使用信号522来控制或调节内插。

97.相位内插器520可以使用互补金属氧化物硅(cmos)技术、电流模式逻辑(cml)或任

何其他可行的技术来实施。在一些实施方式中,相位内插器520可以是图3的第一相位内插器321或第二相位内插器322的示例。于是,尽管为简单起见未示出,但数量为n的第一时钟信号clk

ilo1

中的每个可以被提供给相位内插器520的对应的输入端,并且相位内插器520可以基于数量为n的第一时钟信号clk

ilo1

之间的关系来生成第二参考时钟信号clk

ref2

。

98.第一选择电路532可以被配置为选择第一时钟信号clk

ilo1

中的两个(或一对)作为i/q tx输出时钟信号516进行提供。在一些实施方式中,第一选择电路532可以选择任何适当的第一时钟信号clk

ilo1

的对作为i/q tx输出时钟信号516进行提供。诸如图2的发射数据处理块220的发射电路可以使用i/q tx输出时钟信号516来对数据进行编码或调制以用于发射。

99.第二ilo 512包括用于从相位内插器520接收第二参考时钟信号clk

ref2

的第一输入端、用于接收由第二电压调节器552生成的第二参考电压v

ref2

的第二输入端、以及耦合到任选缓存533(如虚线所示)的输出端,第二ilo 512可以是能够生成与第二参考时钟信号clk

ref2

具有相同频率但在相位上彼此偏移的多个时钟信号的任何适当的ilo。

100.在一些实施方式中,第二时钟信号clk

ilo2

也可以在相位上彼此间距相等或偏移,例如,使得第二时钟信号clk

ilo2

中的每个具有是参考相位偏移的整数倍的唯一相位。例如,在一些实施方式中,第二ilo 512可以生成n=8个在相位上彼此偏移四十五度的第二时钟信号clk

ilo2

,其中第一时钟信号clk_0没有相位偏移,第二时钟信号clk_45相对于clk_0具有45度的相位偏移,第三时钟信号clk_90相对于clk_0具有90度的相位偏移,第四时钟信号clk_135相对于clk_0具有135度的相位偏移,第五时钟信号clk_180相对于clk_0具有180度的相位偏移,第六时钟信号clk_225相对于clk_0具有225度的相位偏移,第七时钟信号clk_270相对于clk_0具有270度的相位偏移,并且第八时钟信号clk_315相对于clk_0具有315度的相位偏移。在一些方面中,第二时钟信号clk

ilo2

可以被提供给任选缓存533,以生成多个缓存的第二时钟信号clk

ilo2’。

101.第二选择电路534可以被配置为选择第二时钟信号clk

ilo2

中的两个(或一对)作为i/q rx输出时钟信号536进行提供。在一些实施方式中,第二选择电路534可以选择任何适当的第二时钟信号clk

ilo2

的对作为i/q rx输出时钟信号536进行提供。诸如图2的接收数据处理块240的接收电路可以使用i/q rx输出时钟信号536来对由收发器500接收的数据进行解码或解调。

102.第二qll 542包括(经由任选缓存533)耦合到第二ilo 512的一个或多个输出端的若干输入端,并且包括耦合到第二电压调节器552的控制端子的输出端。在一些实施方式中,第二qll 452可以接收数量为n的第二时钟信号clk

ilo2

(例如,时钟信号clk_0、clk_45、clk_90、clk_135、clk_180、clk_225、clk_270和clk_315),并且可以被配置为基于第二时钟信号clk

ilo2

之间的一个或多个关系生成第二控制信号(ctrl2)。ctrl2信号被提供到第二电压调节器552的控制输入端,第二电压调节器继而可以至少部分地基于ctrl2信号生成和/或调节v

ref2

的值。

103.第二电压调节器552可以向相位内插器520、第二ilo 512和任选缓存533的控制端子提供v

ref2

,例如,以控制、调节或修改相位内插器520和第二ilo 512的一个或多个操作特性。在一些实施方式中,第二qll 542可以基于第二时钟信号clk

ilo2

的相对相位控制或调节ctrl2信号的值。第二电压调节器552可以至少部分地基于ctrl2信号调节v

ref2

的值,由此允

许第二qll 542控制相位内插器520和第二ilo 512的各种操作。

104.粗略频率跟踪电路560可以是图4的粗略频率跟踪电路460的一种实施方式,粗略频率跟踪电路560可以用于控制至少第一ilo 511和第二ilo 512的初始启动操作。在一些实施方式中,粗略频率跟踪电路560可以响应于检测到启动条件而生成控制电压v

ctrl

并使选择(sel)信号生效,并且使用控制电压v

ctrl

和sel信号经由第一开关561临时禁用ctrl1信号和/或经由第二开关562临时禁用ctrl2信号。更具体而言,在检测到启动条件时,粗略频率跟踪电路560可以使sel信号生效以闭合或导通开关561-562,并且可以将v

ctrl

驱动到经由开关561禁用ctrl1信号和/或经由开关562禁用ctrl1信号的电平。通过这种方式,粗略频率跟踪电路560可以允许第一电压调节器551控制第一ilo 511的振荡频率,并且可以允许第二电压调节器552在启动条件期间建立正交锁定之前控制第二ilo 512的振荡频率。

105.图5b示出了根据其他实施方式的再一个示例性正交时钟生成器501的框图。正交时钟生成器501在很多方面类似于图5a的正交时钟生成器500,不同之处在于相位内插器520可以由第一参考电压v

ref1

来控制,而不是例如由第二参考电压v

ref2

来控制。

106.图6示出了根据一些实施方式的例示性流程图,其绘示了用于操作正交时钟生成器的示例性操作600。操作600可以用于操作任何适当的正交时钟生成器,例如包括图4a的正交时钟生成器400、图4b的正交时钟生成器401、图5a的正交时钟生成器500和图5b的正交时钟生成器501。因此,尽管下文相对于图4a的正交时钟生成器400、图4b的正交时钟生成器401、图5a的正交时钟生成器500和图5b的正交时钟生成器501进行了描述,但示例性操作600可以与其他适当的正交时钟生成器一起使用。

107.操作600可以开始于至少部分地基于第一参考时钟信号生成多个第一时钟信号(602)。也参考图4a和图4b,第一ilo 411可以基于第一参考时钟信号clk

ref1

生成多个第一时钟信号clk

ilo1

。在一些实施方式中,第一时钟信号clk

ilo1

可以包括可以被选择以用作i和q tx时钟信号的整数个时钟信号。

108.操作600可以继续进行,选择多个第一时钟信号之一作为发射正交时钟信号(604)。也参考图4a和图4b,选择电路432可以选择第一时钟信号clk

ilo1

中的任何适当一个作为i/q tx输出时钟信号416进行提供。诸如图2的发射数据处理块220的发射电路可以使用i/q tx输出时钟信号416来对数据进行编码或调制以用于发射。

109.操作600可以继续进行,至少部分地基于多个第一时钟信号生成第二参考时钟信号(606)。也参考图4a和图4b,相位内插器420可以使用由第一ilo 411提供的第一时钟信号clk

ilo1

来生成第二参考时钟信号clk

ref2

。在一些实施方式中,相位内插器420可以在多个第一时钟信号clk

ilo1

中的相邻时钟信号对之间进行内插,以生成第二参考时钟信号clk

ref2

。例如,因此第二参考时钟信号clk

ref2

可以具有相对于第一时钟信号clk

ilo1

的任意相位。

110.操作600可以继续进行,至少部分地基于第二参考时钟信号生成多个第二时钟信号(608)。也参考图4a和图4b,第二ilo 412可以基于第二参考时钟信号clk

ref2

生成多个第二时钟信号clk

ilo2

。在一些实施方式中,第二时钟信号clk

ilo2

可以包括可以被选择以用作i和q rx时钟信号的整数个时钟信号。

111.操作600可以继续进行,选择多个第二时钟信号之一作为接收正交时钟信号(610)。也参考图4a和图4b,第二选择电路434可以选择第二时钟信号clk

ilo2

中的任何适当一对作为i/q rx输出时钟信号436进行提供。诸如图2的接收数据处理块240的接收电路可

以使用i/q rx输出时钟信号436来对数据进行编码或调制以用于发射。

112.本领域的技术人员将认识到,可以使用各种不同技术中的任一种来表示信息和信号。例如,在整个以上描述中提到的数据、指令、命令、信息、信号、比特、符号和芯片可以由电压、电流、电磁波、磁场或粒子、光场或粒子或其任意组合来表示。

113.此外,本领域的技术人员将进一步认识到,结合本文公开的各方面描述的各种例示性逻辑框、模块、电路和算法步骤可以被实施为电子硬件、计算机软件或两者的组合。为了清楚地例示硬件和软件的这种可互换性,上文按照其功能一般性地描述了各种例示性部件、块、模块、电路和步骤。这样的功能性是被实施为硬件还是软件是取决于具体应用以及对整个系统施加的设计约束。技术人员可以针对特定应用通过不同方式实施所描述的功能性,但这样的实施方式决策不应被解释为导致脱离本公开的范围。

114.结合本文公开的各方面描述的方法、序列或算法可以直接实现于硬件中、处理器执行的软件模块中或两者的组合中。软件模块可以驻留在ram锁存器、闪存锁存器、rom锁存器、eprom锁存器、eeprom锁存器、寄存器、硬盘、可移动磁盘、cd-rom或本领域已知的任何其他形式的储存介质中。示例性储存介质被耦合到处理器,使得处理器能够从储存介质读取信息并向储存介质写入信息。替代地,储存介质可以与处理器是一体的。

115.在以上说明书中,已经参考其具体示例性实施方式描述了示例性实施方式。然而,显然可以对本公开的示例性实施例做出各种修改和变化,而不脱离所附权利要求中阐述的本公开的更宽的范围。相应地,应当从例示的意义上而非从限定的意义上来考虑说明书和附图。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。