技术特征:

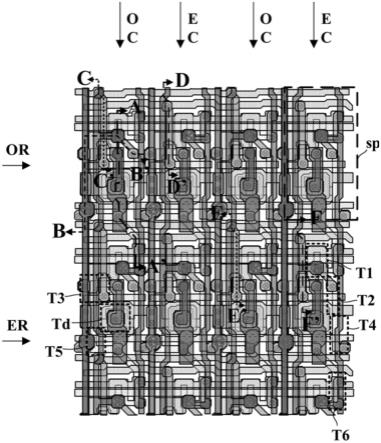

1.一种阵列基板,其包括以包括m行和n列的阵列布置的多个子像素;其中,所述阵列基板包括:多个第一栅线;多个第二栅线;多个第三栅线;多个第四栅线;多个第一数据线;多个第二数据线;多个第三数据线;以及多个第四数据线;其中所述多个第一栅线中的相应第一栅线被配置为向在第(2n-1)列中且在第(2m-1)行中的子像素提供栅极驱动信号,其中,1≤n≤n/2,1≤m≤m/2;所述多个第二栅线中的相应第二栅线被配置为向在第(2n-1)列中且在第(2m)行中的子像素提供栅极驱动信号;所述多个第三栅线中的相应第三栅线被配置为向在第(2n)列中且在第(2m)行中的子像素提供栅极驱动信号;所述多个第四栅线中的相应第四栅线被配置为向在第(2n)列中且在第(2m-1)行中的子像素提供栅极驱动信号;所述多个第一数据线中的相应第一数据线被配置为向在第(2n-1)列中且在第(2m-1)行中的子像素提供数据电压信号;所述多个第二数据线中的相应第二数据线被配置为向在第(2n-1)列中且在第(2m)行中的子像素提供数据电压信号;所述多个第三数据线中的相应第三数据线被配置为向在第(2n)列中且在第(2m)行中的子像素提供数据电压信号;以及所述多个第四数据线中的相应第四数据线被配置为向在第(2n)列中且在第(2m-1)行中的子像素提供数据电压信号;其中所述多个子像素包括:在第(2n-1)列中且在第(2m-1)行中的相应第一子像素;在第(2n-1)列中且在第(2m)行中的相应第二子像素;在第(2n)列中且在第(2m)行中的相应第三子像素;以及在第(2n)列中且在第(2m-1)行中的相应第四子像素。2.根据权利要求1所述的阵列基板,其中,所述第二相应栅线和所述第三相应栅线位于所述相应第一子像素和所述相应第二子像素之间,并且位于所述相应第三子像素和所述相应第四子像素之间;所述第一相应栅线和所述第四相应栅线通过所述相应第一子像素并且通过所述相应第四子像素而与所述第二相应栅线和所述第三相应栅线间隔开;所述相应第二数据线和所述相应第三数据线在所述相应第一子像素和所述相应第四子像素之间,并且在所述相应第二子像素和所述相应第三子像素之间;所述相应第一数据线通过所述相应第一子像素并且通过所述相应第二子像素而与所

述相应第二数据线和所述相应第三数据线间隔开;以及所述相应第四数据线通过所述相应第三子像素并且通过所述相应第四子像素而与所述相应第二数据线和所述相应第三数据线间隔开。3.根据权利要求1或2所述的阵列基板,还包括:在所述相应第一子像素中并且电连接到所述相应第一栅线的相应第一子像素栅线;在所述相应第二子像素中并且电连接到所述相应第二栅线的相应第二子像素栅线;在所述相应第三子像素中并且电连接到所述相应第三栅线的相应第三子像素栅线;以及在所述相应第四子像素中并且电连接到所述相应第四栅线的相应第四子像素栅线。4.根据权利要求3所述的阵列基板,还包括第一栅极绝缘层和第二栅极绝缘层;其中,所述相应第一子像素栅线、所述相应第二子像素栅线、所述相应第三子像素栅线和所述相应第四子像素栅线位于所述第一栅极绝缘层和所述第二栅极绝缘层之间;以及所述相应第一栅线、所述相应第二栅线、所述相应第三栅线和所述相应第四栅线位于所述第二栅极绝缘层的远离所述相应第一子像素栅线、所述相应第二子像素栅线、所述相应第三子像素栅线和所述相应第四子像素栅线的一侧。5.根据权利要求4所述的阵列基板,其中,所述阵列基板的多个像素驱动电路中的各个像素驱动电路包括存储电容器;所述存储电容器包括:第一电容器电极,其与所述相应第一子像素栅线、所述相应第二子像素栅线、所述相应第三子像素栅线和所述相应第四子像素栅线位于同一层中;以及第二电容器电极,其与所述相应第一栅线、所述相应第二栅线、所述相应第三栅线和所述相应第四栅线位于同一层中。6.根据权利要求3至5中任一项所述的阵列基板,还包括:相应第一栅线连接线,其延伸到所述相应第一子像素中,并且电连接所述相应第一栅线和所述相应第一子像素栅线;相应第二栅线连接线,其延伸到所述相应第二子像素中,并且电连接所述相应第二栅线和所述相应第二子像素栅线;相应第三栅线连接线,其延伸到所述相应第三子像素中,并且电连接所述相应第三栅线和所述相应第三子像素栅线;以及相应第四栅线连接线,其延伸到所述相应第四子像素中,并且电连接所述相应第四栅线和所述相应第四子像素栅线。7.根据权利要求6所述的阵列基板,还包括第一栅极绝缘层、第二栅极绝缘层和层间电介质层;其中,所述相应第一子像素栅线、所述相应第二子像素栅线、所述相应第三子像素栅线和所述相应第四子像素栅线位于所述第一栅极绝缘层和所述第二栅极绝缘层之间;所述相应第一栅线、所述相应第二栅线、所述相应第三栅线和所述相应第四栅线位于所述第二栅极绝缘层的远离所述相应第一子像素栅线、所述相应第二子像素栅线、所述相应第三子像素栅线和所述相应第四子像素栅线的一侧;以及所述相应第一栅线连接线、所述相应第二栅线连接线、所述相应第三栅线连接线和所

述相应第四栅线连接线位于所述层间电介质层的远离所述相应第一栅线、所述相应第二栅线、所述相应第三栅线和所述相应第四栅线的一侧。8.根据权利要求5所述的阵列基板,其中,所述多个子像素中的相应一个还包括第一连接线,所述第一连接线通过所述第二电容器电极中的孔电连接至所述第一电容器电极,并且电连接至包括多个像素驱动电路中的相应像素驱动电路的一部分的半导体材料层。9.根据权利要求8所述的阵列基板,其中,所述阵列基板的多个像素驱动电路中的相应像素驱动电路包括存储电容器,所述存储电容器包括第一电容器电极和第二电容器电极;除了其中不包括所述第二电容器电极的一部分的孔区域外,所述第二电容器电极在基底基板上的正投影完全覆盖所述第一电容器电极在所述基底基板上的正投影并留有余量;所述阵列基板还包括第一栅极绝缘层、第二栅极绝缘层和层间电介质层;所述第一电容器电极位于所述第一栅极绝缘层和所述第二栅极绝缘层之间;所述第二电容器电极位于所述第二栅极绝缘层和所述层间电介质层之间;以及所述第一连接线位于所述层间电介质层的远离所述第二电容器电极的一侧;其中,所述阵列基板还包括:第一通孔,其位于所述孔区域中并延伸穿过所述层间电介质层和所述第二栅极绝缘层;以及第二通孔,其延伸穿过所述层间电介质层、所述第二栅极绝缘层和所述第一栅极绝缘层;其中,所述第一连接线通过所述第一通孔连接到所述第一电容器电极;以及所述第一连接线通过所述第二通孔连接到半导体材料层。10.根据权利要求9所述的阵列基板,其中,多个像素驱动电路中的相应像素驱动电路包括:驱动晶体管;第一晶体管;第二晶体管;第三晶体管;第四晶体管;第五晶体管;以及第六晶体管;其中所述第三晶体管的源极、所述第三晶体管的有源层、所述第三晶体管的漏极、所述第一晶体管的源极、所述第一晶体管的有源层、所述第一晶体管的漏极是所述多个子像素中的相应一个中的整体结构的部分;以及所述第一连接线通过所述第二通孔连接到所述第三晶体管的源极和所述第一晶体管的漏极。11.根据权利要求8至10中任一项所述的阵列基板,其中,所述多个子像素中的相应一个还包括在所述第一连接线上的第一平坦化层,以及位于所述第一平坦化层的远离所述第一连接线的一侧的第一防干扰块;所述第一防干扰块在基底基板上的正投影与所述第一连接线在所述基底基板上的正投影至少部分重叠;以及

所述第一防干扰块电连接到所述多个子像素中的相应一个中的相应发光元件的阳极,并且电连接到所述半导体材料层。12.根据权利要求11所述的阵列基板,其中,多个像素驱动电路中的相应像素驱动电路包括:驱动晶体管;第一晶体管;第二晶体管;第三晶体管;第四晶体管;第五晶体管;以及第六晶体管;其中,所述第三晶体管的源极通过第一连接线电连接到所述第二电容器电极,并且电连接到所述第一晶体管的漏极;以及所述第一防干扰块在所述基底基板上的正投影与所述第三晶体管的源极在所述基底基板上的正投影至少部分重叠。13.根据权利要求11或12所述的阵列基板,其中,所述多个子像素中的相应一个还包括电连接所述第一防干扰块和所述半导体材料层的第二连接线;所述第一连接线和所述第二连接线在同一层中;所述第一防干扰块通过延伸穿过所述第一平坦化层的第三通孔电连接到所述第二连接线;所述阵列基板还包括第一栅极绝缘层、第二栅极绝缘层和层间电介质层;以及所述第二连接线通过延伸穿过所述层间电介质层、所述第二栅极绝缘层和所述第一栅极绝缘层的第四通孔电连接到所述半导体材料层。14.根据权利要求13所述的阵列基板,其中,多个像素驱动电路中的相应像素驱动电路包括:驱动晶体管;第一晶体管;第二晶体管;第三晶体管;第四晶体管;第五晶体管;以及第六晶体管;其中所述第五晶体管的源极、所述第五晶体管的有源层、所述第五晶体管的漏极、所述第六晶体管的源极、所述第六晶体管的有源层、所述第六晶体管的漏极是所述多个子像素中的相应一个中的整体结构的部分;以及所述第二连接线通过所述第四通孔电连接到所述第五晶体管的漏极和所述第六晶体管的漏极。15.根据权利要求8至14中任一项所述的阵列基板,其中,所述多个子像素中的相应一个还包括将重置信号线电连接到所述半导体材料层的第三连接线。

16.根据权利要求15所述的阵列基板,还包括:在所述半导体材料层上的第一栅极绝缘层;在所述第一栅极绝缘层上的第二栅极绝缘层;以及层间电介质层,其位于所述第二栅极绝缘层的远离所述第一栅极绝缘层的一侧;其中,所述第三连接线位于所述层间电介质层的远离所述第二栅极绝缘层的一侧;所述第三连接线通过延伸穿过所述层间电介质层、所述第二栅极绝缘层和所述第一栅极绝缘层的第五通孔电连接到所述半导体材料层。17.根据权利要求16所述的阵列基板,其中,多个像素驱动电路中的相应像素驱动电路包括:驱动晶体管;第一晶体管;第二晶体管;第三晶体管;第四晶体管;第五晶体管;以及第六晶体管;其中,所述第三连接线电连接到所述第六晶体管的源极;所述第六晶体管的栅极连接到重置控制信号线;以及所述第六晶体管的漏极连接到所述多个子像素中的相应一个中的相应发光元件的阳极。18.根据权利要求1至17中任一项所述的阵列基板,还包括被配置为向所述多个子像素提供电源电压信号的多个第一电压供应线和多个第二电压供应线;其中,所述多个第一电压供应线与所述多个第一数据线、所述多个第二数据线、所述多个第三数据线和所述多个第四数据线在同一层中;所述多个第一电压供应线和多个第二电压供应线基本上彼此平行;以及所述多个第一电压供应线中的相应一个在基底基板上的正投影与所述多个第二电压供应线中的相应一个在所述基底基板上的正投影至少部分地重叠;其中,所述阵列基板还包括在所述基底基板上的在所述多个第一电压供应线中的相应一个与所述多个第二电压供应线中的相应一个之间的第一平坦化层;以及所述多个第一电压供应线中的相应一个通过延伸穿过所述第一平坦化层的通孔连接到所述多个第二电压供应线中的相应一个。19.根据权利要求1至18中任一项所述的阵列基板,所述多个子像素中的相应一个还包括被配置为被提供有电源电压信号的第二防干扰块;所述阵列基板的多个像素驱动电路中的各个像素驱动电路包括:存储电容器,其包括第一电容器电极和第二电容器电极;所述第二防干扰块与所述第二电容器电极在同一层中;以及所述第二防干扰块在基底基板上的正投影与半导体材料层在所述基底基板上的正投影至少部分地重叠,所述半导体材料层包括多个像素驱动电路中的相应像素驱动电路的一部分。

20.根据权利要求19所述的阵列基板,其中,多个像素驱动电路中的相应像素驱动电路包括:驱动晶体管;第一晶体管;第二晶体管;第三晶体管;第四晶体管;第五晶体管;以及第六晶体管;其中,所述第三晶体管的源极通过第一连接线电连接到所述第二电容器电极,并且电连接到所述第一晶体管的漏极;以及所述第二防干扰块在所述基底基板上的正投影与所述第三晶体管的源极在所述基底基板上的正投影至少部分重叠。21.根据权利要求19或20所述的阵列基板,还包括:多个第一电压供应线和多个第二电压供应线,其被配置为向所述多个子像素提供所述电源电压信号;层间电介质层,其在所述多个第二电压供应线与所述第二防干扰块之间,以及在所述多个第二电压供应线与所述第二电容器电极之间;以及第一平坦化层,其在所述多个第二电压供应线和所述多个第一电压供应线之间;其中,所述多个第二电压供应线中的相应一个通过延伸穿过所述层间电介质层的第六通孔电连接至所述第二防干扰块。22.根据权利要求21所述的阵列基板,其中,所述多个第二电压供应线中的相应一个通过延伸穿过所述层间电介质层的第七通孔电连接到所述第二电容器电极。23.根据权利要求1至22中任一项所述的阵列基板,还包括:相应第一数据线延伸突出部,其从所述相应第一数据线突出到所述相应第一子像素中,并电连接所述相应第一数据线和所述相应第一子像素中的第一像素驱动电路;相应第二数据线延伸突出部,其从所述相应第二数据线突出到所述相应第二子像素中,并电连接所述相应第二数据线和所述相应第二子像素中的第二像素驱动电路;相应第三数据线延伸突出部,其从所述相应第三数据线突出到所述相应第三子像素中,并电连接所述相应第三数据线和所述相应第三子像素中的第三像素驱动电路;以及相应第四数据线延伸突出部,其从所述相应第四数据线突出到所述相应第四子像素中,并电连接所述相应第四数据线和所述相应第四子像素中的第四像素驱动电路。24.根据权利要求23所述的阵列基板,其中,所述相应第一数据线延伸突出部、所述相应第二数据线延伸突出部、所述相应第三数据线延伸突出部和所述相应第四数据线延伸突出部与所述多个数据线在同一层中;所述阵列基板还包括:在所述相应第一子像素中的相应第一中继电极;在所述相应第二子像素中的相应第二中继电极;在所述相应第三子像素中的相应第三中继电极;

在所述相应第四子像素中的相应第四中继电极;以及第一平坦化层,其在所述多个数据线与所述相应第一中继电极、所述相应第二中继电极、所述相应第三中继电极和所述相应第四中继电极之间;其中,所述相应第一中继电极、所述相应第二中继电极、所述相应第三中继电极和所述相应第四中继电极分别通过分别延伸穿过所述第一平坦化层的通孔连接到所述相应第一数据线延伸突出部、所述相应第二数据线延伸突出部、所述相应第三数据线延伸突出部和所述相应第四数据线延伸突出部;所述相应第一中继电极将所述相应第一数据线延伸突出部电连接到包括所述第一像素驱动电路的一部分的半导体材料层;所述相应第二中继电极将所述相应第二数据线延伸突出部电连接到所述半导体材料层;所述相应第三中继电极将所述相应第三数据线延伸突出部电连接到所述半导体材料层;所述相应第四中继电极将所述相应第四数据线延伸突出部电连接到所述半导体材料层。25.根据权利要求24所述的阵列基板,其中,多个像素驱动电路中的相应像素驱动电路包括:驱动晶体管;第一晶体管;第二晶体管;第三晶体管;第四晶体管;第五晶体管;以及第六晶体管;其中,所述阵列基板还包括在所述半导体材料层与所述相应第一中继电极、所述相应第二中继电极、所述相应第三中继电极、所述相应第四中继电极之间的层间电介质层、第二栅极绝缘层和第一栅极绝缘层;其中,所述相应第一中继电极、所述相应第二中继电极、所述相应第三中继电极和所述相应第四中继电极分别通过分别延伸穿过所述层间电介质层、所述第二栅极绝缘层和所述第一栅极绝缘层的通孔分别连接到分别在所述第一像素驱动电路、所述第二像素驱动电路、所述第三像素驱动电路和所述第四像素驱动电路中的第二晶体管的源极。26.根据权利要求24或25所述的阵列基板,还包括被配置为向所述多个子像素提供电源电压信号的多个第一电压供应线和多个第二电压供应线;其中所述第一平坦化层在所述多个第二电压供应线和所述多个第一电压供应线之间;所述多个第一电压供应线与所述多个数据线在同一层中;以及所述多个第二电压供应线与所述相应第一中继电极、所述相应第二中继电极、所述相应第三中继电极和所述相应第四中继电极在同一层中。27.根据权利要求1至26中任一项所述的阵列基板,还包括与所述多个栅线位于同一层中的多个重置信号线;

其中,所述相应第二栅线和所述相应第三栅线在所述多个重置信号线中的相应一个与所述相应第一子像素或所述相应第四子像素之间。28.一种显示设备,包括根据权利要求1至27中任一项所述的阵列基板以及连接至所述阵列基板的集成电路。

技术总结

提供一种阵列基板。该阵列基板包括以包括M行和N列的阵列布置的多个子像素。该阵列基板包括:在第(2n-1)列中且在第(2m-1)行中的相应第一子像素;在第(2n-1)列中且在第(2m)行中的相应第二子像素;在第(2n)列中且在第(2m)行中的相应第三子像素;以及在第(2n)列中且在第(2m-1)行中的相应第四子像素。1)行中的相应第四子像素。1)行中的相应第四子像素。

技术研发人员:李梅 董甜 王丽

受保护的技术使用者:京东方科技集团股份有限公司

技术研发日:2020.10.22

技术公布日:2022/7/9

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。