1.各种实施例总体上涉及电子电路,并且具体地涉及接收器中的时钟数据恢复(cdr)电路。

背景技术:

2.时钟数据恢复(cdr)电路是用于高速串行通信的接收器系统中的重要模块。cdr电路可以为数据恢复生成正确的采样时钟相位。高速串行通信链路的质量可能对采样对接相位(sampling dock phase)很敏感,尤其是在存在抖动和噪声的情况下。

3.在具有确定用于对输入数据进行采样的时钟相位的相位内插器的接收器中,cdr电路可用于识别当前使用的对接相位是否是捕获输入数据的最佳对接相位。cdr电路可以为相位内插器提供动态相位调整。cdr电路可以运行以将对接相位位置移向数据眼的中心。当前对接相位离数据眼的中心越远,cdr电路锁定到正确的对接相位所需的时间就越长。较长的锁定时间可能会导致数据丢失。

4.一种现有的cdr电路是边缘采样cdr电路。边缘采样cdr电路可以对模拟输入波形进行过采样,以生成正确的数据采样对接并恢复传输的数据。边缘采样cdr电路可以假定要在零交叉点(zero-crossing point)之间的中心附近采样的数据。所产生的过采样系统可能比以符号率(也称为波特率)运行的系统消耗更多的时钟功率。此外,随着信道损耗分布的变化,要采样的模拟波形可能不一定是对称的。因此,将数据采样对接保持在零交叉点之间的中心可能不是最佳的。

技术实现要素:

5.装置和相关方法涉及采用具有最小均方误差波特率时钟的连续时间线性均衡(ctle)电路和数据恢复电路,以能够锁定到眼图的中心或接近中心。在说明性示例中,电路可以包括被配置为接收数据和误差样本的符号间干扰(isi)检测器、耦接到isi检测器的输出的求和电路、被配置为接收求和电路的输出并产生平均输出的移动平均滤波器电路、被配置为响应平均输出和预定阈值产生投票的投票器、以及被配置为响应所产生的投票产生代码信号的累加器和代码发生器。通过引入移动平均滤波器和投票器,可以获得更快的锁定到眼图中心或接近中心的方法。

6.各种实施例可以实现一个或多个优点。例如,在一些实施例中,ctle适配可以将前标和后标符号间干扰(isi)控制到相对较小的量,而不是完全将前标和后标isi归零。在一些实施例中,不是通过一次考虑一位数据样本来执行适配,而是可以计算128位数据样本的平均值。因此,可以更快地执行cdr适配。并且该适配可能伴随着少量的前标和/或后标isi。因此,具有mmse波特率cdr的ctle可以轻松快速地锁定到眼图的中心或中心附近。ctle的适配可能执行得更快。在一些实施例中,通过使锁定点位于眼图的中心或中心附近,可以获得基本相等的余量,并且可以为接收器提供足够的余量来正确地采样位。在一些实施例中,投

票器可以接收可编程阈值(例如,用户定义的值),可以获得不同的均衡性能。一些实施例可以使接收器能够承受少量的符号间干扰(isi),然而,可以很好地控制这些少量的isi。在一些实施例中,ctle适配的使用可以省略有限脉冲响应(fir)的使用,因此,如果允许少量isi,则可以减少串行器/解串器(serdes)系统的功耗。

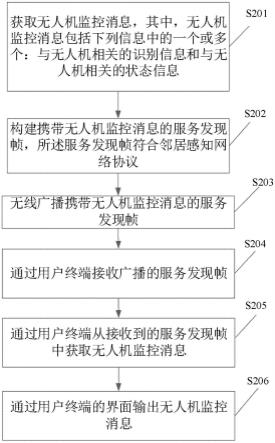

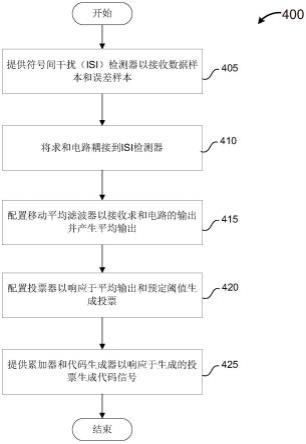

7.在一个示例中,电路包括:(a)符号间干扰(isi)检测器,其被配置为接收数据样本和误差样本;(b)求和电路,其被配置为接收isi检测器的输出并生成适配信息信号;(c)移动平均滤波器,其被配置为从求和电路接收适配信息信号并产生平均输出;(d)投票器,其被配置为响应于平均输出和预定阈值产生投票;以及(e)累加器和代码生成器,其被配置为响应于生成的投票生成代码信号。符号间干扰(isi)检测器被配置为接收数据样本和错误样本。

8.在一些实施例中,isi检测器可以被配置为根据第一后标的真值表运行。在一些实施例中,isi检测器可以被配置为根据第一前标的真值表运行。在一些实施例中,isi检测器可以被配置为根据第一前标的真值表运行。在一些实施例中,投票器可以包括比较器,当平均输出等于预定阈值时,比较器被配置为产生零。在一些实施例中,当平均输出大于预定阈值时,比较器可以被配置为在每个适配周期生成-1、0或 1ctle适配投票。在一些实施例中,累加器和代码生成器可以包括寄存器。在一些实施例中,预定阈值的范围可以从3到4。在一些实施例中,数据样本的位宽可以是128位。在一些实施例中,可以从通过使用数据限幅器以一波特率发送的信号中导出数据样本。在一些实施例中,可以从通过使用误差限幅器以一波特率的发送的信号中导出误差样本。

9.在另一个示例中,一种方法包括(a)提供符号间干扰(isi)检测器以接收数据样本和误差样本,(b)配置求和电路以接收isi检测器的输出并生成适配信息信号,(c)配置移动平均滤波器以从求和电路接收适配信息信号并生成平均输出,(d)配置投票器以响应平均输出和预定阈值产生投票,以及(e)提供累加器和代码生成器以响应生成的投票生成代码信号。

10.在一些实施例中,isi检测器可以被配置为根据第一后标的真值表运行。在一些实施例中,isi检测器可以被配置为根据第一前标的真值表运行。在一些实施例中,投票器可以包括比较器,比较器被配置为比较平均输出和预定阈值,并且当平均输出等于预定阈值时,比较器可以被配置为产生零。在一些实施例中,当平均输出大于预定阈值时,比较器可以被配置为在每个适配时钟周期产生-1、0或 1ctle适配投票。在一些实施例中,累加器和代码生成器可以包括寄存器。在一些实施例中,预定阈值的范围可以从3到4。在一些实施例中,数据样本的位宽可以是128位。在一些实施例中,数据样本可以从通过使用数据限幅器以一波特率发送的信号中导出。在一些实施例中,误差样本可以从通过使用误差限幅器以一波特率的发送的信号中导出。

11.各种实施例的细节在以下附图和描述中阐述。从描述和附图以及从权利要求中,其他特征和优点将是显而易见的。

附图说明

12.图1描绘了可以在其上实现所公开的电路和过程的示例性可编程集成电路(ic)。

13.图2a描绘了示例性通信系统。

14.图2b描绘了示例性接收器的框图。

15.图3描绘了在接收器中实现的示例性适配电路的框图。

16.图4描绘了实现图3中的适配电路的示例性方法的流程图。

17.图5a描绘了仿真眼图。

18.图5b描绘了在适配电路中使用的移动平均滤波器的输出的仿真结果。

19.图5c描绘了接收器中ctle的稳定行为的波形。

20.图6描绘了用于片上系统(soc)类型的集成电路(ic)的示例性架构。

21.各图中相同的参考符号表示相同的元件。

具体实施方式

22.装置和相关方法涉及采用具有最小均方误差(mmse)波特率时钟和数据恢复(cdr)电路的连续时间线性均衡(ctle)电路,以便能够锁定到眼图的中心或接近中心。在说明性示例中,电路可以包括被配置为接收数据和误差样本的符号间干扰(isi)检测器、耦接到isi检测器的输出的求和电路、被配置为接收求和电路的输出并产生平均输出的移动平均滤波器,投票器被配置为响应平均输出和预定阈值产生投票,以及累加器和代码发生器,累加器和代码发生器被配置为响应所产生的投票产生代码信号。通过引入移动平均滤波器和投票器,可以获得更快的锁定到眼图中心或接近中心的方法。

23.为了帮助理解,本文档组织如下。首先,参考图1简要介绍适合进行数据通信的示例性平台(例如,fpga)。第二,参考图2a-4,讨论转向说明适配电路的示意图和实现适配电路的方法的示例性实施例。然后,参考图5a-5c,讨论了适配电路的性能的示例性仿真结果。最后,参考图6,简要介绍了适用于执行数据通信和信号转换的另一示例性平台(例如,片上系统(soc))。

24.图1描绘了可以在其上实现所公开的电路和过程的示例性可编程集成电路(ic)。可编程ic 100包括fpga逻辑。可编程ic 100可以用各种可编程资源实现并且可以被称为片上系统(soc)。fpga逻辑的各种示例可以包括阵列中的几种不同类型的可编程逻辑块。

25.例如,图1描绘了包括大量不同可编程块(tile)的可编程ic 100,包括多千兆位收发器(mgt)101、可配置逻辑块(clb)102、随机存取存储器块(bram)103、输入/输出块(iob)104、配置和时钟逻辑(config/clocks)105、数字信号处理块(dsp)106、专用输入/输出块(i/o)107(例如,时钟端口)、和其他可编程逻辑108(例如,数字时钟管理器、模数转换器、系统监控逻辑)。可编程ic 100包括专用处理器块(proc)110。可编程ic 100可以包括内部和外部重配置端口(未示出)。

26.在各种示例中,可以使用mgt 101来实现串行器/解串器。mgt 101可以包括各种数据串行器和解串器。数据串行器可以包括各种多路复用器实现方案。数据解串器可以包括各种解复用器实现方案。

27.在fpga逻辑的一些示例中,每个可编程块包括可编程互连元件(int)111,其具有去到和来自每个相邻块中的对应互连元件的标准化互连124。因此,可编程互连元件一起实现了所示fpga逻辑的可编程互连结构。可编程互连元件int 111包括去到和来自同一块内的可编程逻辑元件的元件间连接120,如图1中包括的示例所示。可编程互连元件int111包括去到和来自同一块内的可编程互连元件int 111的int内部连接122,如图1中包括的示例

所示。

28.例如,clb 102可包括可被编程以实现用户逻辑的可配置逻辑元件(cle)112,以及单个可编程互连元件int 111。bram 103可包括bram逻辑元件(brl)113和一个或更多可编程互连元件。在一些示例中,包括在块中的互连元件的数量可以取决于块的高度。在图示的实现方案中,bram块具有与五个clb相同的高度,但也可以使用其他数目(例如,四个)。dsp块106可以包括dsp逻辑元件(dspl)114和一个或多个可编程互连元件。iob 104可以包括例如输入/输出逻辑元件(iol)115的两个实例和可编程互连元件int 111的一个实例。例如连接到i/o逻辑元件115的实际i/o接合焊盘可以使用层叠在各种图示逻辑块之上的金属制造,并且可以不限于输入/输出逻辑元件115的区域。

29.在图示的实现方案中,靠近裸片中心的柱状区域(如图1中的阴影所示)用于配置、时钟和其他控制逻辑。从列延伸的水平区域109将时钟和配置信号分布在可编程ic 100的宽度上。注意,对“柱状”和“水平”区域的引用是相对于以纵向方向观看绘图的。

30.一些利用图1所示架构的可编程ic可包括额外的逻辑块,这些逻辑块破坏了构成可编程ic大部分的常规柱状结构。额外的逻辑块可以是可编程块和/或专用逻辑。例如,图1中所示的处理器块proc 110跨越几列clb 102和bram 103。

31.图1描绘了示例性可编程ic架构。列中逻辑块的数量、列的相对宽度、列的数量和顺序、列中包含的逻辑块的类型、逻辑块的相对大小以及互连/逻辑实现是纯粹作为例子提供。例如,在实际的可编程ic中,可以在clb 102出现的任何地方包括多于一个相邻列的clb 102,以促进用户逻辑的有效实现。

32.高速数字(hsd)集成电路(ic)可用于串行器/解串器(serdes)系统。在这样的系统中,发送器电路和接收器电路之间可能存在有损信道,并且在高数据速率下,接收到的数据流可能会严重失真,并且需要在使用前重建(均衡)。

33.图2a描绘了示例性通信系统。在这个描绘的示例中,串行通信系统200包括通过传输介质206耦接到接收器204的发送器202。发送器202可以是串行器-解串器(serdes)208的一部分。接收器204也可以是serdes 210的一部分。传输介质206可以包括印刷电路板(pcb)迹线、通孔、电缆、连接器、去耦电容器等。在一些实施例中,serdes 208可以被设置在集成电路(ic)212中,并且serdes 210可以被设置在ic 214中。

34.发送器202使用数字基带调制技术将串行数据驱动到传输介质206上。通常,串行数据被划分为符号(symbol)。发送器202将每个符号转换成映射到该符号的模拟电压。发送器202将从每个符号产生的模拟电压耦接到传输介质206。在一些实施例中,发送器202可以使用二进制不归零(nrz)调制方案。在二进制nrz中,符号可以是一位的串行数据,并且可以使用两个模拟电压来表示每一位。在一些示例中,发送器202可以使用多级数字基带调制技术,例如脉冲幅度调制(pam),其中符号包括多位的串行数据并且可以使用多于两个的模拟电压来表示每个位。

35.接收器204可以包括时钟和数据恢复(cdr)电路216。接收器204从传输介质206接收模拟信号。传输介质206可能降低传输的模拟信号的信号质量。信道插入损耗是模拟信号的信号功率随频率而变的衰减。当信号通过传输介质时,模拟信号的高频分量可能比低频分量衰减得更多。一般来说,信道插入损耗会随着频率的增加而增加。模拟信号中的信号脉冲能量可以在传输介质206上传播期间从一个符号周期扩散到另一个符号周期。由此导致

的失真被称为符号间干扰(isi)。

36.cdr电路216运行以从模拟信号中恢复数据和时钟。接收器204将恢复的数据提供给serdes 210中的物理编码子层(pcs)电路218用于解码和进一步处理。如图2a所示,发送器202可以使用发送器参考时钟220,并且接收器204可以使用接收器参考时钟222。在一些实施例中,发送器参考时钟220和接收器参考时钟222之间可能存在差异,它可以被称为发送器参考时钟和接收器参考时钟222之间的频率偏移。当发送器参考时钟220和接收器参考时钟222使用独立的时钟源时(例如,频率名义上相同但不是完全相同的时钟源),可能存在频率参考偏移。在一些实施例中,频率偏移可以是固定的(例如,等于常数)。在一些实施例中,频率偏移可以不是固定的,例如,可以是时间的周期性函数。

37.图2b描绘了示例性接收器的框图。接收器204包括连续时间线性均衡器(ctle)224。ctle 224被耦接以从传输介质206接收模拟信号。ctle 224可以作为高通滤波器或带通滤波器运行来补偿传输介质206的低通特性。ctle 224的频率响应的峰值可以由适配电路242调整。

38.ctle 224输出第一均衡模拟信号226。判决电路(例如,判决反馈均衡器(dfe))230耦接到ctle 224的输出并接收第一均衡模拟信号226。判决电路230可以是可运行的,以均衡第一均衡模拟信号226来补偿后标(post-cursor)isi。在这个描绘的示例中,判决电路230还包括限幅器(slicer)228。限幅器228对第一均衡模拟信号226进行采样以生成每个符号k的数据样本dk和误差样本ek。每个限幅器228可以使用采样时钟以一波特率(符号率)对其模拟输入信号进行采样,以生成数据和误差样本。数据样本dk可以包括符号的估计值,误差样本ek可以包括符号的估计判决误差。每个数据样本dk和每个误差样本ek可以包括一个或多个位,这取决于所采用的调制方案的类型(例如,二进制nrz的一位样本和pam的多位样本)。

39.在一些实施例中,接收器204还可以包括解串器(未示出)以对数据样本dk和误差样本ek进行分组以生成要由cdr电路216处理的解串信号。时钟管理器232可以被配置为从例如由相位内插器(pi)238输出的采样时钟237b生成采样时钟信号233(例如,限幅器228使用的数据采样时钟和/或误差采样时钟)。pi 238的另一个输入耦接到锁相环(pll)236的输出。在另一个示例中,时钟管理器232的功能可以结合到pi 238中。时钟管理器232还可以降低由pi 238提供的采样时钟237b的频率。

40.cdr电路216耦接到限幅器228的输出以接收数据样本dk和误差样本ek。在这个描绘的示例中,cdr电路216响应于接收到的数据样本dk和误差样本ek生成pi码信号239。pi 238从pll 236接收参考时钟信号237a。pi 238可以基于由cdr电路216输出的pi码信号239来移动参考时钟信号237a的相位。pi 238可以输出移相的参考时钟信号,例如,作为由限幅器228使用的采样时钟信号237b。在一些实施例中,cdr电路216可以包括相位检测器,该相位检测器被配置为接收数据样本dk和误差样本ek以生成pi码信号239。在一些实施例中,限幅器228可以包括单独的数据限幅器和误差限幅器。在一些实施例中,限幅器228可以包括例如四个误差限幅器。

41.数据样本dk和误差样本ek也被适配电路242接收。在一些实施例中,适配电路242可以通过使用已知算法基于数据样本dk和误差样本ek生成用于ctle 224的控制信号244和用于适配判决电路230的适配控制代码245。

42.在这个描绘的示例中,适配电路242包括符号间干扰(isi)检测器240。被耦接以接收数据样本dk和误差样本ek的isi检测器240确定是否调整数据采样时钟信号233的相位,以及数据采样时钟信号233的相位应该调整到哪个方向。适配电路242还生成适配控制代码245以适配判决电路230。在一些实施例中,cdr电路216可以根据最小均方误差(mmse)算法运行。在一些实施例中,cdr电路216可以根据mueller-muller算法运行。适配电路242的示例性框图将参考图3进行详细描述。

43.在一些实施例中,接收器204还可以包括自动增益控制(agc)电路。ctle 224的输出可以耦接到agc电路的输入。agc电路可用于控制高通滤波器的增益。agc电路的增益也可以由适配电路242控制。在一些实施例中,agc电路可以在ctle电路224之前。在其他示例中,接收器204可以包括其他类型的具有或不具有放大功能的连续时间滤波器。在一些实施例中,可以使用不同的算法来使得ctle电路224只看第一后标。

44.图3描绘了在接收器中实现的示例性适配电路的框图。在这个描绘的示例中,适配电路242包括isi检测器240。数据和误差样本可以是128位。isi检测器240接收128位数据样本dk(例如,d(128))和128位误差样本ek(例如,e(128)),并产生相位检测结果信号,该相位检测结果信号提供净相位检测结果。在这个描绘的示例中,响应于接收到的数据样本dk和误差样本ek,isi检测结果信号可以是h-1

递增信号241a以增加采样时钟信号233的相位或者可以是h-1

递减信号241b以减少采样时钟信号233的相位。isi检测器240可以根据图3所示的真值表308运行。真值表308可以基于第一后标(postcursor)h或第一前标(precursor)h-1

。在这个描绘的示例中,当前数据样本d_curr、下一个数据样本d_next1和当前误差样本e_curr被考虑以确定是增加(例如,h-1

_inc)还是减少(例如,h-1

_dec)采样时钟信号233的相位。

45.适配电路242包括加法电路310。加法电路310例如从isi检测器240接收h-1

增量信号241a和h-1

减量信号241b,并生成到移动平均滤波器320的h-1

适配信息信号315。在这个描绘的示例中,由于数据样本dk和误差样本ek可以是128位,移动平均滤波器320可以一次接收128位的h-1

适配信息,然后生成h-1

适配信息信号315的平均信号325。可以使用不同的数学算法来配置移动平均滤波器320以获得平均信号325。在一些实施例中,移动平均滤波器320可以是加权移动平均滤波器。在一些实施例中,移动平均滤波器320可以是累积移动平均滤波器。在一些实施例中,移动平均滤波器320可以是指数移动平均滤波器。其他加权系统也可用于配置移动平均滤波器320以获得平均信号325。

46.平均信号325由投票器330接收。投票器330还被配置为接收预定值335并且响应于接收到的平均信号325和预定值335生成投票信号340。在这个描绘的示例中,预定值335可以是指示可接受的移动平均步长的可编程阈值。通过引入可编程阈值(例如,用户定义的值),可以获得不同的均衡性能/结果。在一些实施例中,投票器可以包括一个或多个比较器,比较器被配置为指示平均信号325和预定值335之间的关系。在一些实施例中,可编程阈值的范围可以从1到10,例如,从3到4。此外,预定值的窗口边界可参考不同的设计需求(例如判决电路230中的误差限幅器和数据限幅器的有效数量和/或总线宽度)进行缩放。

47.当平均信号325大于预定值(例如,3)335时,投票器330可以在每个适配时钟周期产生-1、0或 1ctle适配投票。如果平均信号325小于预定值335,则投票器330可以产生数字0。如果平均信号325等于预定值335,投票器330可以产生数字-1。累加器和代码生成器345

被配置为累加被包括在投票器330的输出中的投票信号340,并输出适配控制代码信号245(例如,32位信号)以控制dfe适配。在一些实施例中,累加器和代码生成器345可以包括一个或多个寄存器。通过引入移动平均滤波器320和投票器330,ctle适配可以将前标isi和后标isi控制到相对较小的量,而不是将前标isi和后标isi完全归零。并且该适配可能伴随着少量的前标和/或后标isi。因此,具有mmse波特率cdr 216的ctle 224可能能够轻松快速地锁定到眼图的中心或中心附近。此外,该适配可以更快地解决。

48.图4描绘了实现图3中的适配电路的示例性方法的流程图。对于实施参考图3描述的适配电路242的方法400进行了讨论。方法400包括:在405,提供符号间干扰(isi)检测器(例如,isi检测器240)以便从判决电路(例如,判决电路230,其包括限幅器228)接收数据样本和误差样本。方法400还包括,在410,将求和电路(例如,求和电路310)耦接到isi检测器240的输出。

49.方法400还包括,在415,配置移动平均滤波器(例如,移动平均滤波器320)以接收求和电路310的输出并产生平均输出(例如,平均信号325)。方法400还包括,在420,配置投票器(例如,投票器330)以响应于平均输出325和预定阈值335生成投票(例如,投票信号340)。方法400还包括,在425,提供累加器和代码生成器(例如,累加器和代码生成器345)以响应于生成的投票340生成代码信号。通过引入移动平均滤波器320和投票器330,ctle适配可以控制前标和后标isi为相对较小的量,而不是将前标和后标isi完全归零。并且适配可能伴随着少量的前标和/或后标isi。因此,具有mmse波特率cdr216的ctle 224可以能够轻松快速地锁定到眼图的中心或中心附近。

50.图5a描绘了仿真的眼图。参考图3描述的适配电路242已在系统模型中实现并进行了仿真。标有锁定点的以眼图表示的结果在图5a上示出。如图5a所示,眼图锁定(例如,通过mmse波特率cdr)被居中。通过将锁定点设置在眼图的中心或中心附近,可以获得基本相等的余量,并且可以为接收器204提供足够的余量来正确采样位。

51.图5b描绘了在适配电路中使用的移动平均滤波器的输出的仿真结果。在该图中,示出了在适配电路242中使用的移动平均滤波器320的输出的仿真结果。移动平均滤波器320的输出(例如,平均信号325)已由ctle 224调整到3~4的窗口范围内。例如,平均信号325可以是可以由用户决定的h-1

投票滤波器或h1投票滤波器。仿真并显示了基于第一后标h1生成的平均信号和基于第一前标h-1

生成的平均信号。接收器可能能够承受少量的符号间干扰(isi)。

52.图5c描绘了接收器中ctle的稳定行为(settling behavior)的波形。对接收器204中ctle 224的稳定行为进行了仿真。如图5c所示,ctle控制码被稳定为控制范围0~31内某个值。通过引入移动平均滤波器和投票器,可以获得更快的锁定到眼图中心或接近中心的方法。

53.在这个描绘的示例中,适配电路242与接收器204和ctle 224被布置在相同的ic上。在另一个实施例中,适配电路242可以在不同的ic(例如,另一个fpga)中实现以控制均衡。

54.在一些实施例中,适配电路242可以被实现为硬块固定电路(hard block fixed circuitry)。例如,专用集成电路(asic)可以提供具有定制硬件电路的用于生成适配代码信号的适配电路。

55.在一些实施例中,适配电路242的一些或全部功能可以在处理器中实现,该处理器被配置为执行存储在数据存储器中的一组指令以控制均衡。例如,投票器330的功能可以在处理器中实现。在一些实施例中,处理器可以布置在相同的集成电路上,该集成电路可以是具有接收器204的fpga。例如,适配电路242和数据存储器可以在片上系统(soc)的可编程逻辑块中实现,或在soc的使用固定电路的硬块中实现,并且接收器204可以在另一个硬块中通过使用例如soc的固定电路来实现。

56.图6描绘了用于集成电路(ic)的片上系统(soc)类型的示例性架构。soc 600是可编程ic和集成可编程设备平台的示例。在图6的例子中,所示的soc 600的各种不同的子系统或区域可以在单个集成封装内提供的单个裸片上实现。在其他示例中,不同子系统可以在作为单个集成封装提供的多个互连裸片上实现。

57.在示例中,soc 600包括具有不同功能的电路的多个区域。在该示例中,soc 600可选地包括数据处理引擎(dpe)阵列602。soc 600包括可编程逻辑(pl)区域604(以下称为pl区域或pl)、处理系统(ps)606、片上网络(noc)608、和一个或多个硬连线电路块610。dpe阵列602被实现为多个互连的、硬连线的和可编程的处理器,这些处理器具有到soc 600的其他区域的接口。

58.pl 604是可以被编程以执行特定功能的电路。作为示例,pl 604可以实现为现场可编程门阵列类型的电路。pl 604可以包括可编程电路块阵列。pl 604内的可编程电路块的示例包括但不限于可配置逻辑块(clb)、专用随机存取存储器块(bram和/或ultraram或uram)、数字信号处理块(dsp)、时钟管理器、和/或延迟锁定循环(dll)。

59.pl 604中的每个可编程电路块通常包括可编程互连电路和可编程逻辑电路。可编程互连电路通常包括由可编程互连点(pip)互连的大量不同长度的互连线。通常,互连线被配置(例如,基于每条线)以提供基于每位的连接性(例如,其中每条线传送单个信息位)。可编程逻辑电路通过使用可包括例如查找表、寄存器、算术逻辑等的可编程元件来实现用户设计的逻辑。可编程互连和可编程逻辑电路可以通过将配置数据加载到定义可编程元件如何配置和操作的内部配置存储器单元中来编程。

60.ps 606被实现为作为soc 600的一部分制造的硬连线电路。ps 606可以被实现为,或包括,各种不同处理器类型中的任一种,每个处理器类型都能够执行程序代码。例如,ps606可以被实现为单独的处理器,例如,被实现为能够执行程序代码的单核。在另一示例中,ps 606可以被实现为多核处理器。在又一示例中,ps 606可以包括一个或多个核心、模块、协处理器、接口和/或其他资源。ps 606可以使用多种不同类型的架构中的任何一种来实现。可用于实现ps 606的示例架构可包括但不限于arm处理器架构、x86处理器架构、gpu架构、移动处理器架构、dsp架构、或能够执行计算机可读指令或程序代码的任何其它适当的架构。

61.noc 608包括互连网络,用于在soc 600中的端点电路之间共享数据。端点电路可以设置在dpe阵列602、pl区域604、ps 606和/或硬连线电路块610中。noc 608可以包括具有专用开关的高速数据路径。在一个示例中,noc 608包括水平路径、垂直路径、或水平和垂直路径。图6所示的区域的排列和数量仅仅是一个例子。noc 608是soc 600内可用于连接选定组件和/或子系统的通用基础设施的示例。

62.noc 608提供到pl 604、ps 606和选定的硬连线电路块610的连接性。noc 608是可

编程的。在与其他可编程电路一起使用的可编程noc的情况下,在创建用于在soc 600内实现的用户电路设计之前,要通过noc 608路由的网络是未知的。noc 608可以通过将配置数据加载到内部配置寄存器来进行编程,该内部配置寄存器限定了noc 608中的元件(例如交换器和接口)如何配置和操作以在交换器之间以及在noc接口之间传递数据。

63.noc 608被制造为soc 600的一部分,虽然不可物理修改,但可以被编程以建立用户电路设计的不同主电路和不同从电路之间的连接。例如,noc 608可以包括多个可编程交换器,它们能够建立连接用户指定的主电路和从电路的分组交换网络。在这方面,noc 608能够适配不同的电路设计,其中每个不同的电路设计具有在可以由noc 608耦接的、在soc 600的不同位置实现的主电路和从电路的不同组合。noc 608可以被编程在用户电路设计的主电路和从电路之间路由数据,例如应用数据和/或配置数据。例如,noc 608可以被编程以将pl 604内实现的不同用户指定电路与ps 606和/或dpe阵列602、与不同的硬连线电路块、和/或与soc 600外部的不同电路和/或系统进行耦接。

64.硬连线电路块610可以包括输入/输出(i/o)块和/或收发器,用于向soc 600、存储器控制器等外部的电路和/或系统发送和接收信号。不同i/o块的示例可以包括单端和伪差分i/o以及高速差分时钟收发器。此外,硬连线电路块610可被实施以执行特定功能。硬连线电路块610的示例包括但不限于密码引擎、数模转换器、模数转换器等。soc 600内的硬连线电路块610在本文中可以不时地被称为专用块。

65.在图6的例子中,pl 604显示在两个单独的区域中。在另一个示例中,pl 604可以实现为可编程电路的统一区域。在又一个示例中,pl 604可以实现为可编程电路的多于两个不同的区域。pl 604的特定组织并非旨在作为限制。在这方面,soc 600包括一个或多个pl区604、ps 606和noc 608。dpe阵列602可以任选地被包括在内。

66.在其他示例实现方案中,soc 600可以包括位于ic的不同区域中的两个或更多个dpe阵列602。在其他示例中,soc 600可以被实现为多裸片ic。在这种情况下,每个子系统都可以在不同的裸片上实现。不同的裸片可以通过使用多种可用的多裸片ic技术中的任何一种(例如将裸片并排堆叠在中介层上,使用其中ic被实现为多芯片模块(mcm)的堆叠裸片架构等)进行通信链接。在多裸片ic示例中,应当理解,每个裸片可以包括单个子系统、两个或更多个子系统、一个子系统和另一个部分子系统,或者它们的任何组合。

67.可编程集成电路(ic)是指一种包含可编程逻辑的器件。可编程器件或ic的一个示例是现场可编程门阵列(fpga)。fpga的特点是包含可编程电路块。可编程电路块的示例包括但不限于输入/输出块(iob)、可配置逻辑块(clb)、专用随机存取存储器块(bram)、数字信号处理块(dsp)、处理器、时钟管理器、和延迟锁定循环(dll)。现代可编程ic已经发展到包括与一个或多个其他子系统相结合的可编程逻辑。例如,一些可编程ic已演变成片上系统或“soc”,其中包括可编程逻辑和硬连线处理器。其他种类的可编程ic包括附加的和/或不同的子系统。

68.尽管已经参照附图描述了各种实施例,但其他实施例也是可能的。例如,在一些实施例中,可以使用其他前标和/或后标来代替第一前标和第一后标来生成用于移动平均滤波器的输入。例如,移动平均滤波器和投票器可以扩展到使用mmse算法进行适配的任何其他领域。

69.可以使用包括各种电子硬件在内的电路来实现各种示例。作为示例而非限制,硬

件可以包括晶体管、电阻器、电容器、开关、集成电路和/或其他器件。在各种示例中,电路可以包括模拟和/或数字逻辑、分立元件、迹线和/或制造在包括各种集成电路(例如,fpga、asic)的硅衬底上的存储器电路。在一些实施例中,电路可以涉及由处理器执行的预编程指令和/或软件的执行。例如,各种系统可能涉及硬件和软件。

70.实施例的一些方面可以实现为计算机系统。例如,各种实施例可以包括数字和/或模拟电路、计算机硬件、固件、软件或它们的组合。装置元件可以在有形地体现在信息载体(例如,在机器可读存储设备)中的计算机程序产品中实现,用于由固定硬件处理器执行;并且方法可由可编程处理器执行指令程序以通过对输入数据进行操作并产生输出来执行各种实施例的功能。一些实施例可以有利地在一个或多个计算机程序中实现,该程序可在包括至少一个处理器、至少一个输入、和/或至少一个输出的可编程系统上执行,该处理器被耦接以从数据存储器接收数据和指令并将数据和指令传输到数据存储器。数据存储器可以包括例如存储器空间中的一个或多个寄存器或存储器位置。计算机程序是一组指令,可以直接或间接地在计算机中用于执行某种活动或产生某种结果。计算机程序可以以任何形式的编程语言编写,包括编译或解释语言,并且可以以任何形式部署,包括作为独立程序或作为模块、组件、子程序或其他适合使用的单元在计算环境中。

71.在各种实施例中,计算机系统可以包括非暂态存储器。存储器可以连接到一个或多个处理器,该处理器可以被配置用于存储数据和计算机可读指令,包括处理器可执行程序指令。一个或多个处理器可以访问数据和计算机可读指令。处理器可执行程序指令在由一个或多个处理器执行时可以使一个或多个处理器执行各种操作。

72.在各种实施例中,计算机系统可以包括物联网(iot)设备。物联网设备可能包括嵌入电子设备、软件、传感器、执行器和使这些对象能够收集和交换数据的网络连接性。通过将数据通过接口发送到另一个设备,物联网设备可以与有线或无线设备一起使用。物联网设备可能会收集有用的数据,然后在其他设备之间自主传输数据。

73.已经描述了许多实施方式。然而,应当理解,可以进行各种修改。例如,如果公开的技术的步骤以不同的顺序执行,或者如果公开的系统的组件以不同的方式组合,或者如果这些组件补充有其他组件,都可以获得有利的结果。因此,其他实施方式都是在所附权利要求的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。