一种si cmos逻辑器件与gan电力电子器件单片异质集成电路及其制备方法

技术领域

1.本发明属于半导体器件技术领域,具体涉及一种si cmos逻辑器件与gan电力电子器件单片异质集成电路及其制备方法。

背景技术:

2.随着摩尔定律的不断延续,硅基器件的制造成本和技术难度不断提高。并且受制于硅材料本身的物理特性(如较小的禁带宽度、较低的电子迁移率等),使得si基器件无法满足高压、高功率密度的应用需求,例如电源适配器、电动汽车充电。而氮化镓(gan)具有电子迁移率高、禁带宽度大、导通损耗小等优点,十分适用于高压、高功率、高频领域。

3.由于p型gan材料不易激活,以及宽禁带材料固有空穴迁移率低,阻碍了gan cmos技术的发展。基于此,传统的解决方法是将si cmos逻辑器件与化合物半导体通过多芯片模块组装等方式进行集成,这种方法面临互连距离长和由于引线键合引入的寄生电感而导致损耗高的问题,大大限制了器件的性能发挥,同时增加了电路制造的成本和复杂性。

技术实现要素:

4.为了解决现有技术中存在的上述问题,本发明提供了一种si cmos逻辑器件与gan电力电子器件单片异质集成电路及其制备方法。本发明要解决的技术问题通过以下技术方案实现:

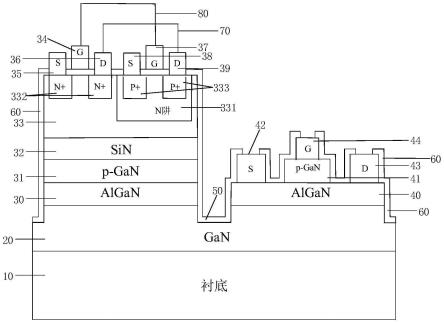

5.本发明实施例的第一方面提供一种si cmos逻辑器件与gan电力电子器件单片异质集成电路,包括:衬底、位于所述衬底上的gan缓冲层、位于所述gan缓冲层上的第一algan势垒层和第二algan势垒层;

6.所述第一algan势垒层和所述第二algan势垒层之间具有隔离槽,所述隔离槽延伸至所述gan缓冲层内;

7.所述第一algan势垒层上设有第一p-gan层,所述第一p-gan层上设有sin隔离层;所述sin隔离层上设有p-si层;所述p-si层中设有n阱掺杂区和nmos源漏区;所述n阱掺杂区内设有pmos源漏区;所述p-si层上覆盖有栅介质层;

8.所述栅介质层上设有第一栅电极;所述第一栅电极的两侧分别设有第一源电极和第一漏电极;所述第一源电极和所述第一漏电极穿过所述栅介质层延伸至所述p-si层上且位于所述nmos源漏区上;

9.所述栅介质层上设有第二栅电极;所述第二栅电极的两侧分别设有第二源电极和第二漏电极;所述第二源电极和所述第二漏电极穿过所述栅介质层延伸至所述p-si层上且位于所述pmos源漏区上;

10.所述第二algan势垒层上设有第二p-gan层、第三源电极和第三漏电极;

11.所述第三源电极和所述第三漏电极分别位于所述第二p-gan层的两侧;

12.所述第二p-gan层上设有第三栅电极;

13.所述隔离槽上覆盖有所述栅介质层,所述第二algan势垒层、所述第二p-gan层、所述第三源电极、所述第三漏电极和所述第三栅电极上覆盖有所述栅介质层,且所述第三源电极、所述第三漏电极和所述第三栅电极上的栅介质层均开设有通孔;

14.所述第一漏电极与所述第二漏电极通过第一金属互联条电气连接;

15.所述第一栅电极与所述第二栅电极通过第二金属互联条电气连接;

16.所述gan缓冲层的外侧边上具有台阶结构,gan缓冲层的一侧的台阶结构的竖向侧壁由gan缓冲层延伸至p-si层,另一侧的台阶结构的竖向侧壁由gan缓冲层延伸至第二algan势垒层。

17.在本发明的一个实施例中,所述p-si层印制到所述sin隔离层上,si cmos逻辑器件与gan电力电子器件单片异质集成。

18.在本发明的一个实施例中,所述栅介质层的材料为al2o3;

19.所述第一栅电极和所述第二栅电极的材料为多晶硅;

20.所述第一源电极和所述第一漏电极分别与所述nmos源漏区形成欧姆接触,且材料均为铝;

21.所述第二源电极和所述第二漏电极分别与所述pmos源漏区形成欧姆接触,且材料均为铝。

22.在本发明的一个实施例中,所述第三源电极和所述第三漏电极的材料均包括自下而上层叠的钛、铝、镍和金,且与所述第二algan势垒层形成欧姆接触;

23.所述第三栅电极的材料包括自下而上层叠的镍和金,且与所述第二p-gan层形成欧姆接触。

24.在本发明的一个实施例中,所述衬底的材料为蓝宝石或硅,厚度为400-500μm;

25.所述gan缓冲层的厚度为1-5μm;

26.所述第一algan势垒层和所述第二algan势垒层的厚度均为15-30nm;

27.所述第一p-gan层和所述第二p-gan层的厚度均为70-120nm;

28.所述sin隔离层的厚度为150-200nm;

29.所述第一金属互联条和所述第二金属互联条的厚度均为200-300nm。

30.在本发明的一个实施例中,所述p-si层的厚度为100-300nm;

31.所述第一栅电极和所述第二栅电极的厚度均为100-200nm;

32.所述第一源电极、所述第一漏电极、所述第二源电极和所述第二漏电极的厚度均为30-100nm;所述栅介质层的厚度为10-30nm。

33.在本发明的一个实施例中,所述第三源电极和所述第三漏电极的厚度均为260nm;所述第三栅电极的厚度为120-250nm。

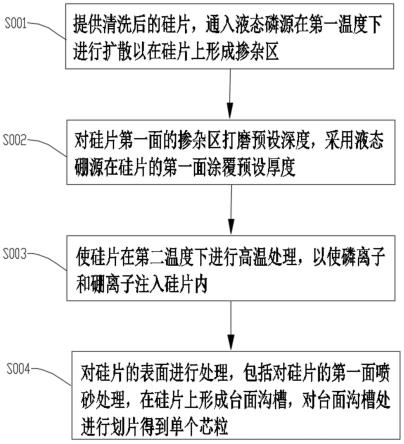

34.本发明实施例的第二方面提供一种si cmos逻辑器件与gan电力电子器件单片异质集成电路制备方法,包括:

35.步骤一、制备sin/p-gan/algan/gan/衬底基片;

36.步骤二、对soi晶片制备得到待转移p-si薄膜产品;

37.步骤三、采用转移印刷技术,将所述待转移p-si薄膜产品的p-si薄膜转印在所述sin/p-gan/algan/gan/衬底基片上以形成si有源层,且所述si有源层位于所述sin/p-gan/algan/gan/衬底基片的一侧;

38.步骤四、在所述si有源层的一侧刻蚀深至gan缓冲层的隔离槽,在所述隔离槽的两侧分别形成p-si/sin/p-gan/algan/gan孤岛和sin/p-gan/algan/gan孤岛;

39.所述p-si/sin/p-gan/algan/gan孤岛的algan势垒层和p-gan层分别为第一algan势垒层和第一p-gan层;

40.所述sin/p-gan/algan/gan孤岛的algan势垒层为第二algan势垒层;

41.步骤五、在步骤四制备得到的产品的边缘进行台面刻蚀,形成延伸至gan缓冲层的台阶结构;

42.步骤六、采用离子注入工艺,在所述p-si/sin/p-gan/algan/gan孤岛的所述p-si层中注入磷离子,形成所述n阱掺杂区;

43.步骤七、采用离子注入工艺,在所述p-si/sin/p-gan/algan/gan孤岛的所述p-si层中所述n阱掺杂区之外的区域注入磷离子,并在氮气氛围下退火,以激活杂质,形成重掺杂的nmos源漏区;

44.步骤八、采用离子注入工艺,在所述p-si/sin/p-gan/algan/gan孤岛的所述n阱掺杂区注入硼离子,并在的氮气氛围下退火,以激活杂质,形成重掺杂的pmos源漏区;

45.步骤九、将所述sin/p-gan/algan/gan孤岛上的sin层完全刻蚀,得到p-gan/algan/gan孤岛;

46.步骤十、刻蚀掉所述p-gan/algan/gan孤岛上栅极区以外的p-gan层,得到第二p-gan层;

47.步骤十一、在所述p-gan/algan/gan孤岛的源极区和漏极区上依次淀积钛金属、铝金属、镍金属和金金属,分别形成第三源电极和第三漏电极,并在氮气氛围下退火,使得第三源电极和第三漏电极均与所述第二algan势垒层形成欧姆接触;

48.步骤十二、在所述p-gan/algan/gan孤岛的栅极区上依次淀积镍金属和金金属,形成第三栅电极;

49.步骤十三、在氮气氛围下,在步骤十制备的产品的表面上淀积三氧化二铝,形成栅介质层;然后在所述p-si/sin/p-gan/algan/gan孤岛的栅介质层上的两个栅极区分别淀积多晶硅,形成第一栅电极和第二栅电极;

50.步骤十四、将所述p-si/sin/p-gan/algan/gan孤岛的所述nmos源漏区和所述pmos源漏区对应位置上栅介质层刻蚀掉,并分别淀积铝金属,形成第一源电极、第一漏电极、第二源电极和第二漏电极,并在氮气氛围下退火,使得第一源电极和第一漏电极均与对应的所述nmos源漏区形成欧姆接触,第二源电极和第二漏电极均与对应的所述pmos源漏区形成欧姆接触;

51.步骤十五、分别刻蚀掉覆盖所述第三栅电极、所述第三源电极和所述第三漏电极上的部分栅介质层形成通孔,以使所述第三栅电极、所述第三源电极和所述第三漏电极部分裸露;

52.步骤十六、在栅介质层上淀积第一金属互联条,以使所述第一漏电极和所述第二漏电极之间形成金属互连;在栅介质层上淀积第二金属互联条,以使所述第一栅电极和所述第二栅电极之间形成金属互连,得到本发明实施例的第一方面所述的单片异质集成电路。

53.本发明的有益效果:

54.本发明不仅兼顾了si cmos高集成度、强大的逻辑功能和gan电力电子器件优异的高频高效率等性能,而且通过在si cmos逻辑电路放置高性能gan电力电子器件实现电路性能优化,使用标准半导体晶圆互连工艺互连器件和子电路,有效降低寄生电感和功率损耗,提高系统的工作频率和效率。提高了集成化程度减小了电路体积的同时降低制备工艺难度,降低了制造成本。

55.以下将结合附图及实施例对本发明做进一步详细说明。

附图说明

56.图1是本发明一种si cmos逻辑器件与gan电力电子器件单片异质集成电路的截面结构示意图;

57.图2a-图2u是本发明一种si cmos逻辑器件与gan电力电子器件单片异质集成电路的制备方法流程示意图。

58.附图标记说明:

59.10-衬底;20-gan缓冲层;30-第一algan势垒层;31-第一p-gan层;32-sin隔离层;33-p-si层;331-n阱掺杂区;332-nmos源漏区;333-pmos源漏区;34-第一栅电极;35-第一源电极;36-第一漏电极;37-第二栅电极;38-第二源电极;39-第二漏电极;40-第二algan势垒层;41-第二p-gan层;42-第三源电极;43-第三漏电极;44-第三栅电极;50-隔离槽;60-栅介质层;70-第一金属互联条;80-第二金属互联条。

具体实施方式

60.下面结合具体实施例对本发明做进一步详细的描述,但本发明的实施方式不限于此。

61.实施例一

62.请参见图1,本发明实施例的第一方面提供一种si cmos逻辑器件与gan电力电子器件单片异质集成电路,包括:衬底10、位于衬底10上的gan缓冲层20、位于gan缓冲层20上的第一algan势垒层30和第二algan势垒层40。

63.第一algan势垒层30和第二algan势垒层40之间具有隔离槽50,隔离槽50延伸至gan缓冲层20内。

64.第一algan势垒层30上设有第一p-gan层31,第一p-gan层31上设有sin隔离层32。sin隔离层32上设有p-si层33。p-si层33中设有n阱掺杂区331和nmos源漏区332,p-si层33中的n阱掺杂区331之外进行磷离子注入形成nmos源漏区332。n阱掺杂区331内设有pmos源漏区333,具体地,n阱掺杂区331进行硼离子注入形成pmos源漏区333。p-si层33上覆盖有栅介质层60。

65.栅介质层60上设有第一栅电极34。第一栅电极34的两侧分别设有第一源电极35和第一漏电极36。第一源电极35和第一漏电极36穿过栅介质层60延伸至p-si层33上且位于nmos源漏区332上。具体地,nmos源漏区332上设有第一源电极35和第一漏电极36,第一源电极35和第一漏电极36之间的栅介质层60上设有第一栅电极34。

66.栅介质层60上设有第二栅电极37。第二栅电极37的两侧分别设有第二源电极38和第二漏电极39。第二源电极38和第二漏电极39穿过栅介质层60延伸至p-si层33上且位于

pmos源漏区333上。具体地,pmos源漏区333上设有第二源电极38和第二漏电极39,第二源电极38和第二漏电极39之间的栅介质层60上设有第二栅电极37。以上位于第一algan势垒层30这一侧的结构形成形成硅的n阱cmos器件。

67.第二algan势垒层40上设有第二p-gan层41、第三源电极42和第三漏电极43。第三源电极42和第三漏电极43分别位于第二p-gan层41的两侧。

68.第二p-gan层41上设有第三栅电极44。隔离槽50上覆盖有栅介质层60,第二algan势垒层40、第二p-gan层41、第三源电极42、第三漏电极43和第三栅电极44上覆盖有栅介质层60,且第三源电极42、第三漏电极43和第三栅电极44上的栅介质层60均开设有通孔。以上位于第二algan势垒层40层这一侧的结构形成形成形成gan电力电子器件。

69.第一漏电极36与第二漏电极39通过第一金属互联条70电气连接。第一栅电极34与第二栅电极37通过第二金属互联条80电气连接。gan缓冲层20的外侧边上具有台阶结构,gan缓冲层20的一侧的台阶结构(硅的n阱cmos器件这一侧的台阶结构)的竖向侧壁由gan缓冲层20延伸至p-si层33,gan缓冲层20的另一侧的台阶结构(gan电力电子器件这一侧的台阶结构)的竖向侧壁由gan缓冲层20延伸至第二algan势垒层40。

70.本实施例中,不仅兼顾了si cmos高集成度、强大的逻辑功能和gan电力电子器件优异的高频高效率等性能,而且通过在si cmos逻辑电路放置高性能gan电力电子器件实现电路性能优化,使用标准半导体晶圆互连工艺互连器件和子电路,而且避免键合引线和电路引入的寄生电感,有效降低功率损耗,提高系统的工作频率和效率。提高了集成化程度减小了电路体积的同时降低制备工艺难度,降低了制造成本。

71.其中,图1中第一金属互联条70和第二金属互联条80在图中仅示意连接关系,具体位置关系不限于图1中的示例,可以根据实际需要设置即可。

72.进一步地,p-si层33印制到sin隔离层32上,si cmos逻辑器件与gan电力电子器件单片异质集成。

73.进一步地,栅介质层60的材料为al2o3。第一栅电极34和第二栅电极37的材料为多晶硅。第一源电极35和第一漏电极36分别与nmos源漏区332形成欧姆接触,且材料均为铝。第二源电极38和第二漏电极39分别与pmos源漏区333形成欧姆接触,且材料均为铝。

74.第一栅电极34和第二栅电极37的厚度均为100-200nm;第一源电极35、第一漏电极36、第二源电极38和第二漏电极39的厚度均为30-100nm;p-si层33的厚度为100-300nm;栅介质层60的厚度为10-30nm。

75.进一步地,第三源电极42和第三漏电极43的材料均包括自下而上层叠的钛、铝、镍和金,且第三源电极42和第三漏电极43均与第二algan势垒层40形成欧姆接触。第三栅电极44的材料包括自下而上层叠的镍和金,且第三栅电极44与第二p-gan层41形成欧姆接触。第三源电极42和第三漏电极43的厚度均为260nm。第三栅电极44的厚度为120-250nm。

76.进一步地,衬底10的材料为蓝宝石或硅,厚度为400-500μm;

77.gan缓冲层20的厚度为1-5μm;

78.第一algan势垒层30和第二algan势垒层40的厚度均为15-30nm;

79.第一p-gan层31和第二p-gan层41的厚度均为70-120nm;

80.sin隔离层32的厚度为150-200nm;

81.第一金属互联条70和第二金属互联条80的厚度均为200-300nm。

82.实施例二

83.本发明实施例的第二方面提供一种si cmos逻辑器件与gan电力电子器件单片异质集成电路制备方法,包括:

84.步骤一、制备sin/p-gan/algan/gan/衬底基片。

85.具体地,采用金属有机物化学气相淀积和原子层沉积工艺,在衬底10上外延gan缓冲层20;在gan缓冲层20上外延algan势垒层;在algan势垒层外延p-gan层,在p-gan层上外延sin层,得到sin/p-gan/algan/gan/衬底基片。

86.其中,衬底10的材料为蓝宝石或硅,厚度为400-500μm;gan缓冲层20的厚度为1-5μm;algan势垒层的厚度均为15-30nm;p-gan层的厚度均为70-120nm;sin层的厚度为150-200nm。

87.步骤二、对soi晶片制备得到待转移p-si薄膜产品。具体制备过程如下:

88.2.1、采用光刻与反应离子刻蚀工艺,在soi晶片上形成p-si薄膜孤岛。

89.2.2、采用湿法刻蚀工艺,将步骤2.1得到的产品放入49%hf溶液中,刻蚀掉未被p-si薄膜孤岛覆盖的埋氧化层。

90.2.3采用光刻工艺,在p-si薄膜边缘制作锚点,以防止后续完全刻蚀埋氧化层后p-si薄膜的位移和脱落。

91.2.4、采用湿法刻蚀工艺,将2.3得到的产品放入49%hf溶液中,完全刻蚀埋氧化层,使p-si薄膜掉落在soi晶片的基底上,得到待转移p-si薄膜产品。

92.步骤三、采用转移印刷技术,将待转移p-si薄膜产品的p-si薄膜转印在sin/p-gan/algan/gan/衬底基片上以形成si有源层,且si有源层位于sin/p-gan/algan/gan/衬底基片的一侧。

93.转印过程具体为:

94.3.1、将sin/p-gan/algan/gan/衬底基片,依次置于丙酮、无水乙醇和去离子水中超声清洗,再用氮气枪吹干。

95.3.2、将固态聚二甲基硅氧烷pdms与刻蚀掉埋氧化层的soi晶片贴合,再将两者以10cm/s的速度分离,以使p-si薄膜粘附在聚二甲基硅氧烷pdms上。

96.3.3、将粘有p-si薄膜的固态聚二甲基硅氧烷pdms与sin/p-gan/algan/gan/衬底基片贴合,再将两者以1mm/s的速度分离,以使硅薄膜粘附在sin/p-gan/algan/gan/衬底基片上,完成p-si薄膜的转印,在sin/p-gan/algan/gan/衬底基片上形成p-si层33。其中,p-si层33的厚度为100-300nm。

97.步骤四、采用光刻和感应耦合等离子刻蚀工艺,在si有源层的一侧刻蚀深至gan缓冲层20的隔离槽50,在隔离槽50的两侧分别形成p-si/sin/p-gan/algan/gan孤岛和sin/p-gan/algan/gan孤岛。隔离槽50深度为400-600nm。

98.p-si/sin/p-gan/algan/gan孤岛的algan势垒层和p-gan层分别为第一algan势垒层30和第一p-gan层31;sin/p-gan/algan/gan孤岛的algan势垒层为第二algan势垒层40。第一algan势垒层30和第二algan势垒层40的厚度均为15-30nm;第一p-gan层31和第二p-gan层41的厚度均为70-120nm。

99.p-si/sin/p-gan/algan/gan孤岛上的sin层也即是sin隔离层32。

100.步骤五、采用光刻和感应耦合等离子刻蚀工艺,在步骤四制备得到的产品的边缘

进行台面刻蚀,形成延伸至gan缓冲层20的台阶结构。多个器件在同时使用时,台阶结构可以形成器件之间的隔离,其中一个器件损坏不会影响其他器件的正常工作。台面刻蚀深度700-900nm。

101.步骤六、采用离子注入工艺,在p-si/sin/p-gan/algan/gan孤岛的p-si层33中注入剂量为5~9

×

10

13

cm-2

,能量为20kev的磷离子,形成形成硅pmos的n阱掺杂区331。

102.步骤七、采用离子注入工艺,在p-si/sin/p-gan/algan/gan孤岛的p-si层33中n阱掺杂区331之外的区域注入剂量为5

×

10

15

cm-2

,能量为20kev的磷离子,并在850℃的氮气氛围下退火10min,以激活杂质,形成硅nmos重掺杂的nmos源漏区332。

103.步骤八、采用离子注入工艺,在p-si/sin/p-gan/algan/gan孤岛的n阱掺杂区331注入剂量为5

×

10

15

cm-2

,能量为20kev的硼离子,并在850℃的氮气氛围下退火10min,以激活杂质,形成重掺杂的pmos源漏区333。

104.步骤九、采用光刻与反应离子刻蚀工艺,将sin/p-gan/algan/gan孤岛上的sin层完全刻蚀,得到p-gan/algan/gan孤岛。

105.步骤十、采用光刻与反应离子刻蚀工艺,刻蚀掉p-gan/algan/gan孤岛上栅极区以外的p-gan层,得到第二p-gan层41。

106.步骤十一、采用电子束蒸发工艺,在p-gan/algan/gan孤岛的源极区和漏极区上依次淀积20nm厚的钛金属、140nm厚的铝金属、55nm厚的镍金属和45nm厚的金金属,分别形成第三源电极42和第三漏电极43,并在850℃的氮气氛围下退火30s,使得第三源电极42和第三漏电极43均与第二algan势垒层40形成欧姆接触。

107.步骤十二、采用电子束蒸发工艺,在p-gan/algan/gan孤岛的栅极区上依次淀积20-50nm厚的镍金属和100-200nm厚的金金属,形成gan电力电子器件的第三栅电极44。

108.步骤十三、采用原子层淀积工艺,在300℃温度条件与氮气氛围下,在步骤十制备的产品的表面上淀积三氧化二铝,形成硅nmos、硅pmos的栅介质层60;然后再采用低压化学气相淀积工艺在p-si/sin/p-gan/algan/gan孤岛的栅介质层60上的两个栅极区分别淀积100-200nm厚的多晶硅,形成硅nmos的第一栅电极34和硅pmos的第二栅电极37。

109.步骤十四、将p-si/sin/p-gan/algan/gan孤岛的nmos源漏区332和pmos源漏区333对应位置上栅介质层60刻蚀掉,并分别淀积30-100nm厚的铝金属,形成硅nmos的第一源电极35和第一漏电极36,硅pmos的第二源电极38和第二漏电极39,并在温度为400℃的氮气氛围下退火20min,使得第一源电极35和第一漏电极36均与对应的nmos源漏区332形成欧姆接触,第二源电极38和第二漏电极39均与对应的pmos源漏区333形成欧姆接触。

110.步骤十五、采用湿法刻蚀工艺,使用浓度为5%的hf溶液分别刻蚀掉覆盖gan电力电子器件的第三栅电极44、第三源电极42和第三漏电极43上的部分栅介质层60形成通孔,以使第三栅电极44、第三源电极42和第三漏电极43部分裸露。

111.步骤十六、采用电子束蒸发工艺,在栅介质层60上淀积第一金属互联条70,以使第一漏电极36和第二漏电极39之间形成金属互连。在栅介质层60上淀积第二金属互联条80,以使第一栅电极34和第二栅电极37之间形成金属互连,得到实施例一中的si cmos逻辑器件与gan电力电子器件单片异质集成电路。第一金属互联条70和第二金属互联条80的厚度均为200-300nm,材料均为金属铝。

112.实施例三

113.本发明实施例提供一种si cmos逻辑器件与gan电力电子器件单片异质集成电路制备方法,在蓝宝石衬底10上制备p-si薄膜厚度为200nm的si-gan单片异质集成反相器,包括以下步骤:

114.步骤301、制备sin/p-gan/algan/gan/衬底基片。

115.具体地,采用金属有机物化学气相淀积和原子层沉积工艺,在衬底10上外延gan缓冲层20;在gan缓冲层20上外延algan势垒层;在algan势垒层外延p-gan层,在p-gan层上外延sin层,得到sin/p-gan/algan/gan/衬底基片,如图2f。其中,衬底10的材料为蓝宝石。

116.步骤302、在soi晶片上形成p-si薄膜孤岛隔离。

117.选取p-si薄膜厚度为200nm、埋氧化层厚度为200nm的soi晶片,如图2a;

118.采用光刻工艺与反应离子刻蚀工艺,在soi晶片的上部刻出p-si薄膜孤岛,如图2b。

119.步骤303、部分刻蚀暴露的埋氧化层。

120.采用湿法刻蚀工艺,将将刻蚀出出p-si薄膜孤岛的soi晶片放入49%hf溶液中浸泡15min,刻蚀掉未被p-si薄膜孤岛覆盖的埋氧化层,如图2c。

121.步骤304、制作光刻胶锚点。

122.采用光刻工艺,在soi晶片上的p-si薄膜边缘制作锚点,以防止后续完全刻蚀埋氧化层后p-si薄膜的位移和脱落,如图2d。

123.步骤305、完全刻蚀整个埋氧化层,以释放p-si薄膜。

124.采用湿法刻蚀工艺,将将制有锚点的soi晶片放入49%hf溶液中浸泡2h,完全刻蚀埋氧化层,使p-si薄膜掉落在soi晶片的基底上,得到待转移p-si薄膜产品,如图2e。

125.步骤306、将得到的p-si薄膜转印到步骤301的sin/p-gan/algan/gan/衬底基片上,如图2g。

126.采用转移印刷技术,将soi晶片上的200nm的p-si薄膜转印sin/p-gan/algan/gan/衬底基片上形成p-si层33,且p-si层33位于sin/p-gan/algan/gan/衬底基片的一侧。sin层厚度为200nm、p-gan层厚度为100nm、algan势垒层厚度为20nm、gan缓冲层20厚度为4μm、蓝宝石衬底10厚度为500μm。

127.转印过程具体为:

128.步骤3061、将sin/p-gan/algan/gan/衬底基片,依次置于丙酮、无水乙醇和去离子水中超声清洗10min,再用氮气枪吹干。

129.步骤3062、将固态聚二甲基硅氧烷pdms与刻蚀掉埋氧化层的soi晶片先进行贴合,再将两者以10cm/s的速度分离,由于聚二甲基硅氧烷pdms是弹粘性物体,表面粘附力与分离速率成正比,因此可快速分离使得pdms具有较大的粘附力,以使p-si薄膜粘附在聚二甲基硅氧烷pdms上。

130.步骤3063、将粘有p-si薄膜的固态聚二甲基硅氧烷pdms与sin/p-gan/algan/gan/衬底基片贴合,再将两者以1mm/s的速度分离,以使硅薄膜粘附在sin/p-gan/algan/gan/衬底基片上,完成p-si薄膜的转印,在sin/p-gan/algan/gan/衬底基片上形成p-si层33。由于分离速度慢,聚二甲基硅氧烷pdms体现出对p-si薄膜的粘附力要比p-si薄膜和sin/p-gan/algan/gan/衬底基片的粘附力小,因此p-si薄膜可被sin/p-gan/algan/gan/衬底基片获取,由此完成p-si薄膜的转印。

131.步骤307、制作硅的n阱cmos器件和gan电力电子器件的孤岛隔离。

132.采用光刻与反应离子刻蚀工艺,在p-si层33的一侧刻蚀深至gan缓冲层20的隔离槽50,在隔离槽50的两侧分别形成p-si/sin/p-gan/algan/gan孤岛和sin/p-gan/algan/gan孤岛,如图2h。

133.p-si/sin/p-gan/algan/gan孤岛的algan势垒层和p-gan层分别为第一algan势垒层30和第一p-gan层31。

134.sin/p-gan/algan/gan孤岛的algan势垒层为第二algan势垒层40。因此,第一algan势垒层30和第二algan势垒层40的厚度均为20nm。第一p-gan层31的厚度为100nm。p-si/sin/p-gan/algan/gan孤岛上的sin层也即是sin隔离层32。

135.步骤308、制作硅的n阱cmos器件和gan电力电子器件的台面隔离。采用光刻和感应耦合等离子刻蚀工艺,在步骤307制备得到的产品的边缘进行台面刻蚀,形成延伸至gan缓冲层20的台阶结构,如图2i。多个器件在同时使用时,台阶结构可以形成器件之间的隔离,其中一个器件损坏不会影响其他器件的正常工作。

136.步骤309、制作硅pmos的n阱掺杂。

137.采用离子注入工艺,在p-si/sin/p-gan/algan/gan孤岛的p-si层33中注入剂量为5~9

×

10

13

cm-2

,能量为20kev的磷离子,形成形成硅pmos的n阱掺杂区331,如图2j。

138.步骤310、制作硅nmos重掺杂的源漏区。

139.采用离子注入工艺,在p-si/sin/p-gan/algan/gan孤岛的p-si层33中n阱掺杂区331之外的区域注入剂量为5

×

10

15

cm-2

,能量为20kev的磷离子,并在850℃的氮气氛围下退火10min,以激活杂质,形成硅nmos重掺杂的nmos源漏区332,如图2k。

140.步骤311、制作硅pmos重掺杂的源漏区。

141.采用离子注入工艺,在p-si/sin/p-gan/algan/gan孤岛的n阱掺杂区331注入剂量为5

×

10

15

cm-2

,能量为20kev的硼离子,并在850℃的氮气氛围下退火10min,以激活杂质,形成重掺杂的pmos源漏区333,如图2l。

142.步骤312、采用光刻与反应离子刻蚀工艺,将sin/p-gan/algan/gan孤岛上的sin层完全刻蚀,得到p-gan/algan/gan孤岛,如图2m。

143.步骤313、采用光刻与反应离子刻蚀工艺,刻蚀掉p-gan/algan/gan孤岛上栅极区以外的p-gan层,得到第二p-gan层41,如图2n。

144.步骤314、制作gan电力电子器件的源、漏电极。

145.采用电子束蒸发工艺,在p-gan/algan/gan孤岛的源极区和漏极区上依次淀积20nm厚的钛金属、140nm厚的铝金属、55nm厚的镍金属和45nm厚的金金属,分别形成第三源电极42和第三漏电极43,并在850℃的氮气氛围下退火30s,使得第三源电极42和第三漏电极43均与第二algan势垒层40形成欧姆接触,如图2o。

146.步骤315、制作gan电力电子器件的栅电极。

147.采用电子束蒸发工艺,在p-gan/algan/gan孤岛的栅极区上依次淀积20nm厚的镍金属和200nm厚的金金属,形成gan电力电子器件的第三栅电极44,如图2p。

148.步骤316、制作硅nmos、pmos的栅电极。

149.采用原子层淀积工艺,在300℃温度条件与氮气氛围下,在步骤315制备的产品的表面上淀积三氧化二铝,形成硅nmos、硅pmos的栅介质层60,如图2q。

150.然后再采用低压化学气相淀积工艺在p-si/sin/p-gan/algan/gan孤岛的栅介质层60上的两个栅极区分别淀积200nm厚的多晶硅,形成硅nmos的第一栅电极34和硅pmos的第二栅电极37,如图2r。

151.步骤317、制作硅nmos、pmos的源、漏电极。

152.将p-si/sin/p-gan/algan/gan孤岛的nmos源漏区332和pmos源漏区333对应位置上栅介质层60刻蚀掉,并分别淀积100nm厚的铝金属,形成硅nmos的第一源电极35和第一漏电极36,硅pmos的第二源电极38和第二漏电极39,并在温度为400℃的氮气氛围下退火20min,使得第一源电极35和第一漏电极36均与对应的nmos源漏区332形成欧姆接触,第二源电极38和第二漏电极39均与对应的pmos源漏区333形成欧姆接触,如图2s。

153.步骤318、电极开孔。

154.采用湿法刻蚀工艺,使用浓度为5%的hf溶液分别刻蚀掉覆盖gan电力电子器件的第三栅电极44、第三源电极42和第三漏电极43上的部分栅介质层60,形成通孔,以使第三栅电极44、第三源电极42和第三漏电极43部分裸露,如图2t。

155.步骤319、制备金属互联条。

156.采用电子束蒸发工艺,在栅介质层60上淀积第一金属互联条70,以使第一漏电极36和第二漏电极39之间形成金属互连。在栅介质层60上淀积第二金属互联条80,以使第一栅电极34和第二栅电极37之间形成金属互连,得到实施例一中的si cmos逻辑器件与gan电力电子器件单片异质集成电路,如图2u。第一金属互联条70和第二金属互联条80的厚度均为300nm,材料均为金属铝。

157.实施例四

158.本发明实施例提供一种si cmos逻辑器件与gan电力电子器件单片异质集成电路制备方法,在硅衬底10上制备p-si薄膜厚度为100nm的单片异质集成si cmos逻辑器件与gan电力电子器件,包括以下步骤:

159.步骤401、制备sin/p-gan/algan/gan/衬底基片。

160.具体地,采用金属有机物化学气相淀积和原子层沉积工艺,在衬底10上外延gan缓冲层20;在gan缓冲层20上外延algan势垒层;在algan势垒层外延p-gan层,在p-gan层上外延sin层,得到sin/p-gan/algan/gan/衬底基片。其中,衬底10的材料为硅。

161.步骤402、在soi晶片上形成p-si薄膜孤岛隔离。

162.选取p-si薄膜厚度为100nm、埋氧化层厚度为200nm的soi晶片,如图;

163.采用光刻工艺与反应离子刻蚀工艺,在soi晶片的上部刻出p-si薄膜孤岛。

164.步骤403、部分刻蚀暴露的埋氧化层。

165.本步骤与实施例三中的步骤303相同。

166.步骤404、制作光刻胶锚点。

167.本步骤与实施例三中的步骤304相同。

168.步骤405、完全刻蚀整个埋氧化层,以释放p-si薄膜。

169.本步骤与实施例三中的步骤305相同。

170.步骤406、将得到的p-si薄膜转印到步骤401的sin/p-gan/algan/gan/衬底基片上。

171.采用转移印刷技术,将soi晶片上的100nm的p-si薄膜转印sin/p-gan/algan/gan/

衬底基片上形成p-si层33,且p-si层33位于sin/p-gan/algan/gan/衬底基片的一侧。sin层厚度为150nm、p-gan层厚度为80nm、algan势垒层厚度为30nm、gan缓冲层20厚度为5μm、硅衬底10厚度为400μm。

172.转印过程具体为:

173.步骤4061、将sin/p-gan/algan/gan/衬底基片,依次置于丙酮、无水乙醇和去离子水中超声清洗10min,再用氮气枪吹干。

174.步骤4062、将固态聚二甲基硅氧烷pdms与刻蚀掉埋氧化层的soi晶片先进行贴合,再将两者以10cm/s的速度分离,由于聚二甲基硅氧烷pdms是弹粘性物体,表面粘附力与分离速率成正比,因此可快速分离使得pdms具有较大的粘附力,以使p-si薄膜粘附在聚二甲基硅氧烷pdms上。

175.步骤4063、将粘有p-si薄膜的固态聚二甲基硅氧烷pdms与sin/p-gan/algan/gan/衬底基片贴合,再将两者以1mm/s的速度分离,以使硅薄膜粘附在sin/p-gan/algan/gan/衬底基片上,完成p-si薄膜的转印,在sin/p-gan/algan/gan/衬底基片上形成p-si层3333。由于分离速度慢,聚二甲基硅氧烷pdms体现出对p-si薄膜的粘附力要比p-si薄膜和sin/p-gan/algan/gan/衬底基片的粘附力小,因此p-si薄膜可被sin/p-gan/algan/gan/衬底基片获取,由此完成p-si薄膜的转印。

176.步骤407、制作硅的n阱cmos器件和gan电力电子器件的孤岛隔离。

177.采用光刻与反应离子刻蚀工艺,在p-si层33的一侧刻蚀深至gan缓冲层20的隔离槽50,在隔离槽50的两侧分别形成p-si/sin/p-gan/algan/gan孤岛和sin/p-gan/algan/gan孤岛。

178.p-si/sin/p-gan/algan/gan孤岛的algan势垒层和p-gan层分别为第一algan势垒层30和第一p-gan层31。

179.sin/p-gan/algan/gan孤岛的algan势垒层为第二algan势垒层40。因此,第一algan势垒层30和第二algan势垒层40的厚度均为30nm。第一p-gan层31的厚度为80nm。p-si/sin/p-gan/algan/gan孤岛上的sin层也即是sin隔离层32。

180.步骤408、制作硅的n阱cmos器件和gan电力电子器件的台面隔离。本步骤与实施例三中的步骤308相同。

181.步骤409、制作硅pmos的n阱掺杂。

182.本步骤与实施例三中的步骤309相同。

183.步骤410、制作硅nmos重掺杂的源漏区。

184.本步骤与实施例三中的步骤310相同。

185.步骤411、制作硅pmos重掺杂的源漏区。

186.本步骤与实施例三中的步骤311相同。

187.步骤412、本步骤与实施例三中的步骤312相同。

188.步骤413、本步骤与实施例三中的步骤313相同。

189.步骤414、制作gan电力电子器件的源、漏电极。

190.本步骤与实施例三中的步骤314相同。

191.步骤415、制作gan电力电子器件的栅电极。

192.采用电子束蒸发工艺,在p-gan/algan/gan孤岛的栅极区上依次淀积30nm厚的镍

金属和150nm厚的金金属,形成gan电力电子器件的第三栅电极44。

193.步骤416、制作硅nmos、pmos的栅电极。

194.采用原子层淀积工艺,在300℃温度条件与氮气氛围下,在步骤415制备的产品的表面上淀积三氧化二铝,形成硅nmos、硅pmos的栅介质层60。

195.然后再采用低压化学气相淀积工艺在p-si/sin/p-gan/algan/gan孤岛的栅介质层60上的两个栅极区分别淀积100nm厚的多晶硅,形成硅nmos的第一栅电极34和硅pmos的第二栅电极37。

196.步骤417、制作硅nmos、pmos的源、漏电极。

197.将p-si/sin/p-gan/algan/gan孤岛的nmos源漏区332和pmos源漏区333对应位置上栅介质层60刻蚀掉,并分别淀积60nm厚的铝金属,形成硅nmos的第一源电极35和第一漏电极36,硅pmos的第二源电极38和第二漏电极39,并在温度为400℃的氮气氛围下退火20min,使得第一源电极35和第一漏电极36均与对应的nmos源漏区332形成欧姆接触,第二源电极38和第二漏电极39均与对应的pmos源漏区333形成欧姆接触。

198.步骤418、电极开孔。

199.本步骤与实施例三中的步骤318相同。。

200.步骤419、制备金属互联条。

201.采用电子束蒸发工艺,在栅介质层60上淀积第一金属互联条70,以使第一漏电极36和第二漏电极39之间形成金属互连。在栅介质层60上淀积第二金属互联条80,以使第一栅电极34和第二栅电极37之间形成金属互连,得到实施例一中的si cmos逻辑器件与gan电力电子器件单片异质集成电路。第一金属互联条70和第二金属互联条80的厚度均为250nm,材料均为金属铝。

202.在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

203.在本发明中,除非另有明确的规定和限定,第一特征在第二特征之“上”或之“下”可以包括第一和第二特征直接接触,也可以包括第一和第二特征不是直接接触而是通过它们之间的另外的特征接触。而且,第一特征在第二特征“之上”、“上方”和“上面”包括第一特征在第二特征正上方和斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”包括第一特征在第二特征正下方和斜下方,或仅仅表示第一特征水平高度小于第二特征。

204.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。此外,本领域的技术人员可以将本说明书中描述的不同实施例或示例进行接合和组合。

205.以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定

本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。