1.本案所描述的技术大致涉及电源管理方法与电路,特别是一种提供静电放电防护的方法、静电放电电路及静电放电单元。

背景技术:

2.静电放电是带电物体之间的突发电流,上述带电物体可能由接触、短路、介电崩溃以及其他的事件所致。若控制不当,静电放电可能会损坏静电放电流动所通过的物体(例如,集成电路)及/或中断电性通讯信号。静电放电事件可能由静电、静电感应或其他内部电路系统的故障所引起。

技术实现要素:

3.本案的一实施例是关于一种提供静电放电防护的方法,包含自输入/输出引脚接收输入电流;当于输入/输出引脚的电压达到阈值电压并将电压箝制于保持电压时,响应于静电放电事件;在静电放电事件期间,静电放电防护于拉至正电压模式或拉至负电压模式下操作。拉至负电压模式通过一系列的多个二极管通过自输入/输出至负电压的静电放电路径,将电压箝制于阈值电压。拉至正电压模式通过一系列的多个二极管通过自输入/输出至正电压的静电放电路径,将电压箝制于第二阈值电压。

4.本案的另一实施例是关于一种静电放电电路。静电放电电路包含第一二极管、第二二极管、第三二极管以及第四二极管。第一二极管与第二二极管自输入/输出引脚至第三二极管的输入与第四二极管的输入以串联配置。第三二极管自第二二极管的输出连接至正电压线路。第四二极管自第二二极管的输出连接至负电压线路。

5.本案的又一实施例是关于一种静电放电单元。静电放电单元包括第一输入二极管、第二上拉二极管及第三下拉二极管。第二上拉二极管连接至第一输入二极管的输出以及正电压供电线路。第三下拉二极管连接至第一输入二极管的输出以及负电压接地线路。

附图说明

6.以下详细描述结合附图阅读时,可以最好地理解本案一实施例的各方面。注意,根据行业中的标准实践,各种特征并未按比例绘制。事实上,为了讨论的清楚起见,各种特征的尺寸可以任意扩大或缩小。

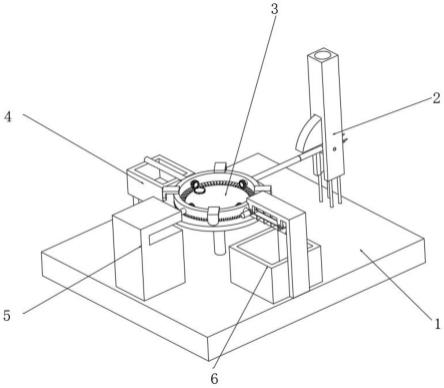

7.图1是描绘一实施例中用以接收输入/输出及电力供应连接件的电力电路的方块图;

8.图2是根据一实施例所描绘的静电放电装置的方块图,上述静电放电装置包括内部电路系统、输入/输出连接件以及正电压/负电压连接件;

9.图3是一实施例中用于故障安全静电放电防护装置的示例电力管理电路的示意图;

10.图4a描绘一实施例中用于故障安全静电放电防护装置的示例电力管理电路的电

路逻辑图;

11.图4b描绘一实施例中于图3示出的电力管理电路的示例操作的电力示意图;

12.图5描绘一实施例中用于故障安全静电放电防护装置的另一实例电力管理电路;

13.图6描绘一实施例中用于图5的电力管理电路的总线图;

14.图7a至图7b描绘一实施例中故障安全静电放电防护装置的电路逻辑图及横截面布局图;

15.图8a至图8b描绘一实施例中图7a至图7b的电力管理电路的静电放电路径图;

16.图9a至图9b是用于图7a至图7b的电力管理电路的额外实例布局分布;

17.图10是一实施例中用于静电放电电路的故障安全操作的示例方法的流程图。

18.【符号说明】

19.100:电力电路

20.101:静电放电装置

21.103:正电压线路

22.105:负电压线路

23.107:输入/输出引脚,输入/输出垫

24.200:静电放电故障安全输入/输出电路

25.207:输入/输出引脚

26.208:输入/输出引脚

27.209:内部电路系统

28.300:静电放电防护电路,电力管理电路

29.301:第一上拉二极管

30.303:第二输入二极管

31.305:第三上拉二极管

32.307:第三下拉二极管

33.309:下拉二极管

34.311:pd模式

35.313:ps模式

36.400:电力管理电路

37.401:输入/输出电压

38.403:输入/输出电流

39.411:保持电压

40.413:第一阈值电压

41.415:第二阈值电压

42.417:崩溃电压

43.419:电流阈值

44.421:操作设计窗口

45.423:静电放电设计窗口

46.425:内部电路系统损坏

47.500:电力管理电路

48.501,503:上拉二极管

49.505:分离的单元

50.507,509:下拉二极管

51.511,513:输入/输出引脚

52.600:电力管理电路

53.601,602,603:输入/输出单元

54.605:故障安全静电放电防护单元

55.611~613:功能电路,功能电路系统

56.621~623:上拉二极管

57.631~633:下拉二极管

58.641,642:二极管总线

59.700:故障安全静电放电防护单元

60.701,702,705:n 节点

61.703,704:p 节点

62.710,711:n型井

63.715:缓冲器

64.720:r型井

65.730:深层n型井

66.750:掺杂布局

67.810:负电压线路

68.820:正电压线路

69.900:布局分布

70.910:第一二极管布局

71.911:p 氧化物扩散层

72.912:缓冲层

73.913:n 氧化物扩散及n型井层

74.915:通孔

75.916:连接板

76.920:第二二极管布局

77.921:p 氧化物扩散层

78.922:缓冲层

79.923:n 氧化物扩散及n型井层

80.926:连接板

81.930:第三共享二极管布局

82.931:p 氧化物扩散及r型井层

83.932:缓冲层

84.933:氧化物扩散、n型井及深n型井层

85.934:缓冲层

86.935:n 氧化物扩散层

87.1000:方法

88.1010,1020,1030,1040:步骤

89.vdd:正电压线路

90.vss:负电压线路

91.d3u:第三上拉二极管

92.d3d:第三下拉二极管

93.i/o,i/o-1,i/o-2:输入/输出

94.pdd,pdd-1,pdd-2:下拉二极管

95.d1:上拉二极管

96.d2:输入二极管

具体实施方式

97.以下内容提供了用于实现提供的标的的不同特征的许多不同的实施例或实例。以下描述元件及配置的特定实例用以简化本案。当然,该些仅为示例,并不旨在进行限制。此外,本案的一实施例可以在各个实例中重复元件符号及/或字母。此重复是出于简单及清楚的目的,其本身并不指定所讨论的各种实施例或组态之间的关系。

98.静电放电可能损坏静电放电流动所通过的电路系统及/或中断电性通讯信号。静电放电事件可能由静电、静电感应或其他内部电路系统故障所引起。本文提供用于防护内部电路系统不受与内部电路系统输入相关联的静电放电事件影响的系统及方法。防护内部电路系统不受静电放电事件影响的一技术系将与电路系统结合的装置连接至下拉电压,并将电源重定向至电源轨。这些用于重定向电源以防止静电放电事件造成意外损害的元件称为静电放电装置。

99.图1是描绘在一实施例中用以接收电路系统输入/输出(i/o)连接件(例如,输入/输出引脚107)的电力电路100的示意图。示例静电放电装置101包括多个输入引脚以及连接至供电线路的连接件,上述多个输入引脚用以接收通过内部电路系统引脚107的电流。经连接的供电线路包括正电压线路(vdd)103及接地或负电压线路(vss)105。静电放电装置101在内部电路系统的正常操作期间关闭。当电压超过阈值电压时,静电放电装置101操作使得电流自内部电路系统或输入/输出引脚107通过静电放电装置101流动至电源线路vdd 103或vss 105。静电放电装置101通过降低输入/输出引脚107处的电压来防护内部电路系统,使得内部电路系统不损坏。

100.图2是根据一实施例所描绘的静电放电故障安全输入/输出电路200的方块图,具有内部电路系统及电源线路的静电放电故障安全输入/输出电路200包括一或多个输入/输出连接件。示例静电放电故障安全输入/输出电路200包括连接至静电放电装置101的内部电路系统209、正电压线路103以及接地或负电压线路105。内部电路系统209配有引脚以接收输入/输出信号。静电放电装置101用以通过电源线路103、105箝制内部电路系统209的电压。静电放电装置101也连接至一或多个输入/输出引脚207和208。静电放电装置101用以使电源行经静电放电路径,上述静电放电路径自内部电路系统209通过静电放电装置101至正电压线路103或负电压线路105。在正常操作期间,静电放电装置被配置为关闭。当自内部电路系统209的输入或输入/输出引脚207和208所量测的电压超过设计的电压阈值时,静电放

电装置101开启,并且随着电流自输入/输出引脚207、208通过静电放电装置101流动至负电压线路105,箝制电压于保持电压。这种通过拉引电流通过静电放电装置101至负电压线路105的电压箝制形式称为拉引至负电压线路105模式(ps模式)。当自内部电路系统的输入所量测的电压超过更大的阈值时,静电放电装置操作于拉引至正电压模式(pd模式)下,并且电流自输入/输出通过静电放电装置流动至正电压线路103。通常而言,在pd模式期间,随着电源的消散,电流流动至正电压线路103及负电压线路105两者。

101.静电放电装置101在电路系统的操作电压与对内部元件具有破坏性的电压之间具有设计窗口(design windows)。静电放电装置可作为较低电压静电放电事件的第一崩溃防护操作,上述静电放电装置用以将电流自输入/输出导引至负电压线路105(或ps模式)。静电放电装置可作为在较高电压静电放电事件发生时的最糟情况操作,上述静电放电装置用以将电流自输入/输出导引至正电压线路103(或pd模式)。示例静电放电装置可包括骤回装置或三-二极管堆叠。

102.举例而言,骤回装置可用作静电放电装置101及/或静电放电电流路径中的元件。骤回装置是电压箝制装置,上述电压箝制装置具有高电阻或开启点,其中的电阻高达崩溃电压,上述电阻在高于上述开启点时急剧下降。装置于开启点导电以降低特定点的电压至保持电压,并允许电流流过晶体管至电源轨。通常而言,骤回装置设计成在电压损坏内部元件之前开启及消散电源,然而当电压在正常操作电压范围内时,骤回装置仍保持高电阻状态。骤回装置通常自输入/输出引脚207、208串联连接至负电压线路105,同时电源箝位器自负电压线路105串联连接至正电压线路103。骤回装置需要一个延伸漏极区,上述延伸漏极区会比所预期的面积更大。此外,上述装置具有与上述漏极区相关联的寄生电阻。骤回装置通过寄生路径来开启,上述寄生路径在复杂的设计中可能难以设计。

103.三-二极管堆叠是用作静电放电装置的设计,其中静电放电装置连接于输入/输出引脚207、208与负电压线路105之间。三-二极管堆叠是以串联配置的三个二极管。当全部三个二极管的电压差超过输入/输出引脚207、208与负电压线路105之间的电压差时,上述操作使得电流流动通过二极管。由于二极管的内电阻,三-二极管堆叠通常具有高操作电阻。为了降低操作电阻,二极管堆叠需要很大的面积。此外,在三-二极管堆叠中,负电压线路105与输入/输出引脚207、208之间通常需要上拉二极管。

104.静电放电故障安全装置101设计成防止电路系统元件因与静电放电事件相关联的过大电源而损坏。当上述装置输入处的电压在与输入/输出引脚207、208或内部电路系统209相关联的操作边界内时,上述装置的设计使得装置不会干扰内部电路系统209的操作。故障安全输入/输出装置101操作以防护内部电路系统209免受静电放电突波的影响,其中静电放电突波与输入/输出连接件(例如,输入/输出引脚207、208)相关联。举例而言,由于外部的故障,在输入时会发生电压突波,其中若电源未消散或重定向,则外部的故障可损坏内部电路系统209。当跨越二极管的电源消散时,温度升高,这会导致热考验。此外,静电放电装置在设计窗口内操作以在崩溃电压之前保持电压,但在可操作的设计内时,静电放电装置不会箝制电压。以这种方式,减少静电放电装置上的电压压降允许更大的设计窗口或更高的设计电压以及更高的电流限制,其中电流限制与输入/输出及内部电路系统连接件相关联。此外,静电放电装置需要在其相关的元件(诸如集成电路)上的布局面积,这会有相关的成本。通常而言,在静电放电设计期间难以控制面积及电压压降。

105.故障安全输入/输出pd模式的电压压降可成功减少,因为故障安全输入/输出pd模式可通过上拉二极管直接开启,而非下拉二极管以及电源箝位器二极管。这方法允许通过直接连接至正电压线路103来扩展设计窗口,而不存在与电源箝位器相关联的电阻损耗。此外,上拉二极管与下拉二极管可置放于分离的单元上,其中分离的单元为多个输入/输出连接件重定向电源。这类单一静电放电装置上的共享静电放电防护降低布局面积要求。此外,此实施例中的布局允许下拉二极管及上拉二极管两者被配置于共享的深n型井之上,从而进一步减少布局面积。

106.图3是根据一实施例的故障安全输入/输出静电放电电路的示例静电放电防护电路300的示意图。静电放电防护电路300是静电放电电路200(如图2中所示)的示范实施例。上述示例静电放电防护电路300包括输入/输出连接件(例如输入/输出引脚107)、电源线路vdd 103和vss105、内部电路系统209、下拉二极管(pull-down diode,pdd)309、第一上拉二极管(d1)301、第二输入二极管(d2)303、第三上拉二极管(d3u)305以及第三下拉二极管(d3d)307。在此实施例中,静电放电装置101所指为第一上拉二极管301、第二输入二极管303、第三上拉二极管305以及第三下拉二极管307。上述静电放电装置101操作以通过输入/输出引脚107防护内部电路系统209免受静电放电的影响,或者上述静电放电装置101操作以通过输入/输出引脚107防护其他电路系统。内部电路系统109连接至外部输入/输出引脚107、下拉二极管309以及静电放电装置101的第一上拉二极管301。

107.连接的下拉二极管309使得电流自负供应电压或接地(例如,负电压线路105)通过下拉二极管309流动至内部电路系统209。下拉二极管309经配置使得阴极侧连接于输入/输出引脚107与内部电路系统209之间,而阳极侧连接至负供应电压线路(例如,负电压线路105)。举例而言,上述下拉二极管309可以是齐纳二极管,诸如暂态电压抑制(transient-voltage-suppression,tsv)二极管。上述二极管下拉二极管309操作以防止异常电压静电放电通过输入/输出进入内部电路系统。在静电放电事件期间,下拉二极管309能够与输入电源反向操作,否则输入电源会流入内部电路系统209。

108.此实施例包括ps模式路径,上述ps模式路径包括流出的电流,其中电流自内部电路系统或输入/输出引脚107流出通过第一上拉二极管301、接着通过第二输入二极管303、通过第三下拉二极管307至负电压线路105。在一般操作期间,内部电路系统与输入/输出引脚上的电压小于vss处的电压加上三-二极管301、303以及307(d1、d2以及d3d)处的电压压降,因此ps模式路径没有电流流动,亦称为关闭状态。当输入/输出引脚107或内部电路系统209连接处的电压超过vss的电压加上第一上拉二极管301、第二输入二极管303以及第三下拉二极管307的电压差(此即习知的阈值电压)时,为了用于ps模式路径,静电放电事件的电流重定向。ps模式静电放电路径通常在ps模式静电放电事件期间启动,以将输入/输出引脚107上或内部电路系统209连接件上所量测的电压降低至保持电压。通过第一上拉二极管301、第二输入二极管303以及第三下拉二极管307的经设计的电子特性以及负电压线路105的电压,检测阈值电压的值与保持电压的值,其中负电压线路105作为接地线路通常为零。部分电动的特性是为二极管上的电压压降、二极管正向偏压时的正向电压以及二极管的操作电阻而设计。

109.此实施例进一步包括pd模式路径,上述pd模式路径包括流出的电流,其中电流自内部电路系统109或输入/输出引脚107流出通过第一上拉二极管301、接着通过第二输入二

极管303、通过第三上拉二极管305至正电压线路103。在一般操作期间,内部电路系统及输入/输出引脚上的电压低于vdd处电压,因此pd模式路径没有电流流动,亦称为关闭状态。当输入/输出引脚或内部电路系统连接处的电压超过vdd的电压加上第一上拉二极管301、第二输入二极管303以及第三上拉二极管305的电压差(即习知的阈值电压)时,为了用于pd模式路径,静电放电事件的电流经重定向。由于vdd电压高于vss电压,故pd模式静电放电事件的电压阈值高于ps模式静电放电事件的电压阈值。此外,通常在pd模式静电放电事件期间,电源不但于二极管上消散,并流动至vdd,还通过第三下拉二极管307流动至vss。pd模式静电放电路径在pd模式静电放电事件期间开启,以将输入/输出引脚107上或内部电路系统209连接处上所量测的电压降低至保持电压。通过第一上拉二极管301、第二输入二极管303以及第三上拉二极管305的经设计的电子特性与正电压线路vdd 103的电压,检测阈值电压的值与保持电压的值。

110.内部电路系统209具有通过输入/输出引脚107连接到至少一输入/输出的连接处。通常而言,内部电路系统连接至多个输入(例如,输入/输出引脚207、208,即io-1、io-2),上述多个输入可发送信号至内部电路系统。此外,内部电路系统连接至可通过静电放电装置101连接的输出。在一示例中,输入/输出引脚107上的静电放电事件电压可能超过一电压阈值,上述电压阈值设定为防护内部电路系统元件,若超过电压或电流的最大值,上述内部电路系统元件可能损坏。在静电放电事件期间,电压经由静电放电装置通过串联的二极管重定向,上述二极管消散电源并且将电源导引至电源线路(正电压线路103、负电压线路105)。静电放电装置101经连接,使得用于开启静电放电装置的量测电压于内部电路系统209或输入/输出引脚107上被量测。

111.在实施例中,三-二极管堆叠的设计经配置,使得电源在流动至电源线路之前通过串联的二极管消散。一旦电压达到电压线路的阈值电压加上二极管上的电压压降,二极管堆叠的配置会箝制上述电压。开启二极管堆叠并非通过寄生电阻路径,因此更易于在复杂的设计中实施。二极管可根据电压降设计来调试,以获得特定的保持电压,其中在内部电路系统正常操作期间上述保持电压并不开启,但在静电放电事件期间,上述保持电压开启作为故障安全以重定向电源,否则电源将超过内部电路系统的元件规范。二极管堆叠具有大的操作电阻或开启电阻,并因此通常具有大的布局面积要求。因此,允许共享二极管的上述配置有利于减少布局面积限制,同时允许电压压降的控制。

112.图4a是根据一实施例的图4a故障安全输入/输出静电放电电路的示例电力管理电路400的示意图,并随附图4b,图4b是示出一实施例中图4a的电源管理电路的示例操作的电源图。参照图4a,下拉二极管309经连接使得电流于正向操作期间自负供应电压或接地(例如,负电压线路105),通过下拉二极管309流动至内部电路系统209。在操作期间下拉二极管309通常关闭,因为负电压线路105的电压低于上述二极管阴极侧的输入/输出引脚107与内部电路系统209连接件的电压。举例而言,下拉二极管309可以是齐纳二极管,诸如暂态电压抑制(tsv)二极管。上述二极管操作以防止异常电压静电放电通过输入/输出进入内部电路系统。此外,输入/输出引脚107上的负电压读数允许电流以正向偏压方式流动通过下拉二极管309,并防止意外电压(例如,静电放电事件)损坏内部电路。在静电放电事件期间,下拉二极管309反向操作以消散输入电源并将电源传输至接地(即负电压线路105),否则上述电源流入内部电路系统209。

113.参照图4b,根据一实施例,阈值电压导致电路上的电压箝制于ps模式电压413及pd模式电压415。所量测输入/输出连接处电压401(即输入/输出电压)表示为图上的x轴,而静电放电装置上电流403(即输入/输出电流)表示为y轴。反向电压通过与输入/输出相关联的下拉二极管309保持于保持电压411(vr)。正向电压具有与静电放电装置101的pd模式311及ps模式313操作相关联的两个保持电压。一旦上述电压达到第一阈值电压413(ps模式)则电压保持,造成在电源图中的垂直斜率。这表示当静电放电装置在ps模式下操作时,重定向至负电压线路105且在二极管上消散的电流。此外,上述电路具有第二阈值电压415(即pd模式),其中于第二阈值电压415下电压箝制于较高的电压阈值。这表示紧急第二电源模式,上述模式将电流导引至正电压线路103且在二极管上消散电源。在pd模式期间,电流亦可通过下拉二极管流动至负电压线路105。

114.静电放电装置101中存在电流阈值419(it),于电流阈值419下静电放电装置101无法进一步箝制电压,并且输入/输出处的电压超过崩溃电压417(vbd)的设计可能导致内部电路系统损坏425。此即是静电放电装置101的故障点。电路的一般操作电压涉及两个电源轨103、105(vdd与vss)之间的输入/输出电压。在此实施例中,负电压线路105为接地,因此操作发生于零伏特的负电压线路105与作为正电压轨的正电压线路103之间。在电路系统的一般操作期间,当装置处于关闭状态时,静电放电装置电流为零。静电放电装置101的可操作静电放电设计窗口423为介于用以开启静电放电装置101的阈值电压与装置的崩溃电压417(vbd)之间的电压。第一保持电压即是ps模式电压413,第一保持电压可计算为三-二极管第一上拉二极管301、第二输入二极管303以及第三下拉二极管307的电压压降加上通常为零的负电压线路105的电压。第二保持电压即是pd模式电压415,第二保持电压可计算为二极管第一上拉二极管301、第二输入二极管303以及第三上拉二极管305的电压降加上正电压线路103的电压。因此在一些实施例中,第一保持电压413和第二保持电压415之间的电压差与正电压线路103和负电压线路105之间的电压差大致相同。

115.图5是用于具有多个输入/输出连接件的静电放电输入/输出故障安全的另一示例电力管理电路500。电路布局包括连接至正电压轨vdd 103与至负电压轨vss 105的多个连接件、连接至第一输入/输出511(i/o-1)、第二输入/输出513(i/o-2)以及一系列的二极管的连接件。在此实施例中,第二输入二极管303(d2)、第三上拉二极管305(d3u)以及第三下拉二极管307(d3d)被配置于分离的单元505(例如,静电放电故障安全单元)上。静电放电装置101包括输入二极管303、第三上拉二极管305以及第三上拉二极管307。静电放电装置101可以是多个分离的单元或单个静电放电故障安全单元。静电放电装置101用以自第一输入/输出511、第二输入/输出513、负电压线路105以及正电压线路103获取输入。静电放电装置101配有连接至第二输入二极管303的阳极侧的第一输入/输出511与第二输入/输出513。第二输入二极管303的阴极侧连接至第三上拉二极管305的阳极侧与第三下拉二极管307的阳极侧。第三下拉二极管307配置为其阳极连接至输入二极管303的阴极侧,而第三下拉二极管307的阴极侧则连接至通常接地的负电压线路105(vss)。

116.每个输入/输出具有输入/输出自身的下拉二极管507和509(pdd-1和pdd-2),下拉二极管的阳极侧连接至负电压线路105,而下拉二极管的阴极侧连接至个别输入/输出引脚511、513(i/o-1和i/o-2)。上述下拉二极管507、509(pdd-1、pdd-2)操作以箝制各个输入/输出,使得电流可反向流动通过下拉二极管。举例而言,上述下拉二极管507、509(pdd-1和

pdd-2)可以是齐纳二极管,诸如暂态电压抑制(tsv)二极管。上述二极管操作以防止静电放电事件产生的异常电源通过输入/输出进入内部电路系统。在静电放电事件期间,下拉二极管507、509(pdd-1和pdd-2)可作为反向偏压来操作以重定向电源,否则上述电源将流入内部电路系统209。

117.每个输入/输出具有自己的上拉二极管d1(501、503),上述上拉二极管501、503的阳极侧连接至个别输入/输出引脚511、513(i/o-1、i/o-2),且上拉二极管501和503的阴极侧连接至输入二极管303的阳极侧。这些二极管操作以沿ps模式静电放电路径或pd模式静电放电路径形成三-二极管串。

118.第二输入二极管、第三上拉二极管以及第三下拉二极管可以上述方式配置于分离的单元505上。上述分离的单元505可通过自与任何连接的输入/输出(举例而言,i/o-1或i/o-2,即511、513)相关联的静电放电事件开启,防护多个输入/输出单元。此外,此实施例通过在不同的输入/输出与内部电路系统连接件之间共享二极管,保留布局面积。如在其他实施例中进一步描述的,分离的单元上的上拉二极管及下拉二极管可在共享的深n型井之上共享布局的配置。因此,上述配置保留布局面积,并允许更大的静电放电设计窗口423,以实现更强健的静电放电防护。

119.图6是根据一实施例的故障安全输入/输出电力管理电路600的总线示意图。除图6中所示故障安全输入/输出电力管理电路600的示例描绘为总线布局且包括额外输入/输出连接件以外,图6中所示的示例与图5中的示例电源管理电路相同。故障安全输入/输出电力管理电路600的示例布局包括三个输入/输出单元601、602、603及故障安全静电放电防护单元605。上述多个单元可以任何次序的单元被配置,或者以垂直的单元被配置。为了清楚及简单起见,本实施例将单元平行布置,以举例说明与共享故障安全静电放电防护单元相关的多个输入/输出结构。在其他实施例中,配置单元用于提高效率或满足元件规范。示例总线布局进一步包括电源轨vdd 103、电源轨vss 105、第一二极管总线641以及第二二极管总线642。

120.在此示例实施例布局中,各个输入/输出单元601、602以及603包括个别功能电路611、612以及613。举例而言,这些电路可以是图2中由静电放电装置101防护的内部电路系统209。第一输入/输出单元601包括下拉二极管631、上拉二极管621(d1)以及功能电路系统611。第一输入/输出单元601在静电放电路径中连接至故障安全静电放电防护单元605,其中静电放电路径包括上拉二极管621、第一二极管总线641以及静电放电防护单元605。再次参考图5,举例而言,静电放电防护单元605可经配置使得第一二极管总线641连接至输入二极管d2,接着连接至第三上拉二极管d3u及第三下拉二极管d3d。第一输入/输出单元601亦包括通过下拉二极管631连接至负电压线路105的连接件,并且第一输入/输出单元601包括连接至vdd的连接件以为功能电路611供电。通过上拉二极管621、501(d1)的第一输入/输出单元601的连接件可以是第一输入/输出引脚511(i/o-1),其中用于输入/输出防护的第一输入/输出引脚511电压由静电放电装置101所量测。

121.第二输入/输出单元602包括下拉二极管632、上拉二极管622(d1)以及功能电路系统612。第二输入/输出单元602在静电放电路径中连接至故障安全静电放电防护单元605,其中静电放电路径包括上拉二极管622、第二二极管总线642以及静电放电防护单元605。类似于第一输入/输出单元601,第二输入/输出单元602可包括连接至第二输入/输出引脚513

的连接件,其中用于输入/输出防护的二输入/输出引脚513电压由静电放电装置所量测。

122.第三输入/输出单元603包括下拉二极管633、上拉二极管632(d1)、及功能电路系统613。第三输入/输出单元603可类似于第一输入/输出单元601及第二输入/输出单元602来配置,第三输入/输出单元603配置为具有连接至负电压线路105、正电压线路103的连接件以及第一二极管总线641或第二二极管总线642。故障安全静电放电路径经配置使得第一二极管总线641或第二二极管总线643连接至上拉二极管632,并进入故障安全静电放电防护单元605。

123.图7a至图7b描绘一实施例中用于故障安全静电放电防护装置的另一示例故障安全静电放电防护单元700。图7a中所示的示例故障安全静电放电防护单元700与图5中的示例分离的单元505相同。在此实施例中,分离的单元505是单一个静电放电防护单元,如同图6中所示的静电放电防护单元605。除图7b中所示的示例中静电放电防护单元605显示为剖面掺杂布局750以外,图7b中所示的示例与图6中所示的静电放电防护单元605相同。示例剖面掺杂布局750与图7a中逻辑布局的故障安全静电放电防护单元700一致。故障安全静电放电装置布局包括深n型井730(deep n-well,dnw)、两个n型井710和711、r型井720、两个n 节点701和702、两个p 节点703和704以及连接至正电压线路701和702、输入二极管703和704以及负电压线路705的连接件。

124.在正向偏压操作期间,在二极管中的电流自阳极流动至阴极。因此,在p 节点703、704与n 节点701、702、705之间形成p-n接合区,使得在布局中形成多个二极管。自连接于输入二极管的p 节点703、704通过r型井720至连接于负电压线路的n 节点705形成第三下拉二极管d3d。自p 节点703、704通过r型井720及各自的n型井710、711至连接于正电压线路的n 节点701、702形成第三上拉二极管d3u。两个n型井710、711以及r型井720形成于深n型井730的顶部上。缓冲器715存在于节点701、702、703、704、705中的每一者之间,上述节点通常为绝缘氧化物,以迫使大部分电流流动通过n型井710、711及r型井720。由于寄生电容极小,这使得设计具有准确且可预期的二极管特性。

125.图8a至图8b是根据一实施例的图7a至图7b的电源管理电路的另一示例的布局配置示意图。图8a至图8b显示故障安全静电放电防护单元的共享二极管的操作。在图8a中,电流于p 节点703、704自d2节点流动通过r型井720并且进入于负电压线路810的n 节点705。此配置形成第三下拉二极管307(d3d),上述第三下拉二极管作为ps模式路径的部分。在图8b中,电流于p 节点703、704自d2节点流动通过r型井720及n型井710、711,进入于正电压线路820的n 节点701、702。此配置形成第三上拉二极管305(d3u),上述第三上拉二极管作为pd模式的部分。

126.在正向偏压操作期间,二极管中的电流自阳极流动至阴极。二极管包括p型及n型元件,使得形成p-n接合区,从而使装置操作如同自阳极至阴极的电阻非常低但自阴极至阳极的电阻非常高。因此,在图8a中,电流于ps模式路径中通过输入二极管303(d2)流入于p 节点703、704的分离的单元布局750,再通过r型井进入连接至负电压线路810的n 节点705,这形成第三下拉二极管307(d3d)。在图8b中,示例布局于pd模式下操作,使得电流沿着pd模式路径820流动。在pd模式期间,电流流动通过pd模式路径,通过输入二极管303(d2)进入p 节点703、704,再通过r型井720,通过n型井710、711进入连接至正电压线路820的n 节点701、702,这形成第三上拉二极管305(d3u)。

127.图9a至图9b是根据一实施例的图7a至图7b的电源管理电路的额外示例布局分布示意图。图9a是故障安全静电放电防护单元中二极管掺杂布局的俯视图。图9b是故障安全静电放电防护单元中二极管掺杂布局的示例剖面图。

128.示例布局分布900包括第一二极管布局910(d1)、第二二极管布局920(d2)以及具有共享二极管的第三布局930(d3u d3d)。第一二极管布局910包括连接至输入/输出垫107、p 氧化物扩散层911、缓冲层912以及n 氧化物扩散与n型井层913的连接件。第一二极管布局910通过与p 氧化物扩散层911接触的通孔915连接至输入/输出垫107。第一二极管布局910通过导电通孔915连接至第二二极管布局920,其中导电通孔915连接n 氧化物与n型井层913至第二二极管布局920的p 氧化物扩散层。

129.第二二极管布局920包括连接至第一二极管布局910、p 氧化物扩散层921、缓冲层922以及n 氧化物扩散与n型井层923的连接件。第二二极管布局920通过接触p 氧化物扩散层911的通孔915连接第一二极管布局910。第二二极管布局920通过导电通孔915连接至第三共享二极管布局930,其中导电通孔915连接n 氧化物与n型井层923至第三共享二极管布局930的p 氧化物扩散及r型井层931。第一二极管布局910与第二二极管布局920之间的连接板916可形成为二极管总线,举例而言,如图6中所示的第一二极管总线641或第二二极管总线642。

130.第三共享二极管布局930包括连接至第二二极管布局920、p 氧化物扩散及r型井层931、两个缓冲层932和934、氧化物扩散、n型井及深层n型井层933以及n 氧化物扩散层935。第三共享二极管布局930通过通孔915连接至第二二极管布局920(d2),上述通孔接触p 氧化物扩散及r型井层931。第三共享二极管布局930通过导电通孔915连接至电源轨vdd 103,上述通孔915接触n 氧化物扩散n型井及深层n型井层933。第三共享二极管布局930通过导电通孔915连接至vss电源轨105,上述导电通孔915接触n 氧化物扩散层935。第二二极管布局920与第三共享二极管布局930之间的连接板926可形成为二极管总线,举例而言,如图6中所示的第一二极管总线641或第二二极管总线642。在其他实施例中,连接板926形成为与第二二极管布局920及第三共享二极管布局930相同的单元的一部分,使得没有二极管总线连接两个二极管布局。

131.图10是描绘根据一实施例的用于在静电放电事件期间用于防护电路系统的方法1000的流程图,上述静电放电事件包括多个防护晶片的电力电路系统。为了便于理解,提供图10的步骤并参照先前所描述的结构,但可理解的是,可使用各种结构执行上述步骤。举例而言,方法1000可由图3、图4a、图5以及图6中的示例电力管理电路300、400、500、600中的一者执行。举例而言,在步骤1010中,可自输入/输出引脚107、511、513接收输入电流。在步骤1020中,当在输入/输出引脚处达到电压阈值时,上述电压箝制于第一保持电压。当输入引脚上的电流推进输入电压至阈值电压时,静电放电事件的响应重定向电流。在步骤1030中,在静电放电事件期间,因着电流通过串联的二极管自输入/输出通过静电放电路径下拉至负电压线路,由pd路径箝制电压。在步骤1040中,若电流进一步推进电压至第二阈值电压,则电流可通过串联的二极管自输入/输出行进通过静电放电路径至正电压线路。上述第二路径进一步箝制电压于崩溃电压之前的阈值电压,并且上述第二路径作为故障安全来操作,以减少在静电放电事件期间电压超过崩溃电压的可能性。

132.本技术案主张2021年3月12日提交的标题为“具有二极管的故障安全静电放电防

护”的美国临时申请案第63/160,049号的权益,其全文以引用的方式并入本文中。

133.本案的一实施例是提供一种安全静电放电防护的方法。包含自输入/输出引脚接收输入电流;当于输入/输出引脚的电压达到阈值电压时响应于静电放电事件,并将电压箝制于保持电压;在静电放电事件期间,静电放电防护于拉至正电压模式或拉至负电压模式下操作。拉至负电压模式通过一系列的多个二极管通过自输入/输出至负电压的静电放电路径,箝制电压于阈值电压。拉至正电压模式通过上述多个二极管通过自输入/输出至正电压的静电放电路径,箝制电压于第二阈值电压。在一实例中,电力电路包括输入/输出引脚、内部电路系统、以及用于降低内部电路系统上电力的二极管。静电放电防护电路系统用以减少电压压降,以获得更大的设计窗口。电静电放电防护电路系统通过各个静电放电路径利用三-二极管串来降低电压压降,这无需电力箝位或骤回装置上方的电压压降。在这个配置中,第一二极管及第二二极管串联连接至第三上拉二极管及第三下拉二极管。第三上拉二极管自第二二极管的输出与正电压电源轨连接。第三下拉二极管自第二二极管的输出与负电压电源轨连接。因为上拉二极管及下拉二极管可共享深n型井,所以这个实施例可占用更少的设计布局面积。此外,可通过将第二二极管、第三上拉二极管及第三下拉二极管配置于与输入/输出或功能电路系统的分离的单元上来减小设计布局面积。这个静电放电的分离单元可连接具有防护电路系统及输入/输出的多个单元,每个输入/输出单元连接至静电放电单元用于静电放电防护。以这种方式,借着由共享静电放电防护单元防护多个单元来减少设计面积。

134.在一些实施例中,静电放电路径包括两个共享二极管、第三上拉二极管以及第三下拉二极管。第三上拉二极管在用于拉至正电压模式的静电放电路径中。第三下拉二极管在用于拉至负电压模式的静电放电路径中。

135.在一些实施例中,自多个输入/输出单元接收输入电流。

136.在一些实施例中,共享二极管、上拉二极管以及下拉二极管配置于与输入/输出分离的单元上。

137.在一些实施例中,用于各个输入/输出引脚的静电放电路径包含在输入/输出单元中用于静电放电路径的上拉二极管、在静电放电单元中作为输入二极管的共享二极管的一者以及静电放电单元中第三上拉二极管或静电放电单元中第三下拉二极管。

138.在一些实施例中,在下拉的静电放电路径中负电压与正电压之间无需额外静电放电电源箝制电路,用于拉至正电压模式的静电放电路径直接通过多个二极管连接多个输入/输出引脚至正电压。

139.本案的另一实施例是提供一种静电放电电路。静电放电电路包含第一二极管、第二二极管、第三二极管以及第四二极管。第一二极管与第二二极管自输入/输出引脚至第三二极管的输入与第四二极管的输入以串联配置。第三二极管自第二二极管的输出连接至正电压线路。第四二极管自第二二极管的输出连接至负电压线路。静电放电电路可通过输入/输出至vdd或输入/输出至vss模式作为故障安全操作。通过直接连接至vdd线及vss线来防护内部或功能电路系统的方法允许开启静电放电防护,而无需基于二极管上方的电压降。这不需要使用电力箝位,上述电力箝位通常会降低静电放电防护的电压降。这进一步允许更大的设计窗口。此外,这个方法不需要骤回装置,因此可基于二极管电压降规格来调谐,而不依赖于寄生电阻路径来开启。自输入/输出至vdd的静电放电路径称为pd模式路径,且

作为最重要的电力消散模式或最后的故障安全操作,以防止电路系统损坏。自输入/输出至vss的静电放电路径称为ps模式路径,且作为较低电力消散模式操作,用于较不严重的静电放电事件。电力通过二极管及电源轨(vdd、vss)消散。这个实施例中实践的方法可通过三-二极管堆叠组态来完成,其中堆叠的第三二极管为用于pd模式路径的上拉二极管或用于ps模式路径的下拉二极管。此外,静电放电故障安全模式可针对多个输入/输出连接来实践。此外,静电放电故障安全方法可在分离的静电放电单元上实践,以保留布局面积。

140.在一些实施例中,第二二极管、第三二极管以及第四二极管配置于与输入/输出电路系统分离的单元上。

141.在一些实施例中,第二二极管、第三二极管以及第四二极管连接至多个输入/输出单元。

142.在一些实施例中,输入/输出电路系统进一步包含下拉二极管,上述下拉二极管的阳极端连接至负电压线路,并且下拉二极管的阴极端连接于输入/输出单元与内部电路系统之间。

143.在一些实施例中,第三二极管与第四二极管分层以共享深n型井。

144.在一些实施例中,第二二极管、第三二极管以及第四二极管连接至多个输入/输出单元。

145.在一些实施例中,输入/输出电路系统进一步包含下拉二极管,上述下拉二极管的阳极端连接至负电压线路,并且下拉二极管的阴极端连接至输入/输出单元与内部电路系统之间。

146.本案的又一实施例是提供一种静电放电单元。静电放电单元包括第一输入二极管、第二上拉二极管、及第三下拉二极管。第二上拉二极管连接至第一输入二极管的输出以及正电压供电线路。第三下拉二极管连接至第一输入二极管的输出以及负电压接地线路。输入/输出连接与防护电路相关联,而输入/输出引脚电压影响静电放电单元是否操作或处于关闭状态。一旦输入/输出引脚上达到阈值电压,电流流动穿过第三下拉二极管及/或第二上拉二极管至分离的电源轨。静电放电单元可配置于共享的深层n型井上方,以减小设计面积布局。三-二极管堆叠可通过一额外上拉二极管串联连接配置,其阳极侧连接至输入/输出,而阴极侧连接至输入二极管的阳极侧输入。这个电路系统组态允许自多个输入/输出单元(各个单元具有上拉二极管及下拉二极管)输入连接至静电放电单元。

147.在一些实施例中,第二下拉二极管与第三上拉二极管被配置为在共享的深n型井之上的布局分布。

148.在一些实施例中,静电放电单元进一步包含自输入/输出引脚至第一输入二极管串联的额外上拉二极管。

149.在一些实施例中,静电放电单元位于与输入/输出单元分离的单元上,上述输入/输出单元通过输入/输出引脚连接至静电放电单元。输入/输出单元包含串联至输入/输出引脚的输入/输出上拉二极管、功能电路系统以及下拉二极管。功能电路系统经连接以由静电放电单元防护。下拉二极管连接于功能电路系统与负电压接地线路之间。

150.在一些实施例中,静电放电单元通过多个输入/输出引脚防护多个功能电路,以及每个输入/输出引脚与输入/输出上拉二极管以串联连接。

151.在一些实施例中,静电放电单元进一步包含用于每个输入/输出引脚的下拉二极

管,上述下拉二极管的阳极端连接至负电压接地线路,并且其阴极端连接于输入/输出单元与功能电路系统之间。

152.在一些实施例中,共享的深n型井及/或r型井经调变,使得上拉二极管上的电压压降不同于下拉二极管上的电压压降。

153.前述内容概述若干实施例的特征,使得熟悉此项技术者可更佳地理解本案的态样。熟悉此项技术者应了解,其可易于使用本案作为用于设计或修改用于实施本文中引入的实施例的相同目的及/或达成相同优势的其他制程及结构的基础。熟悉此项技术者亦应认识到,此类等效构造并不偏离本案的精神及范畴,且此类等效构造可在本文中进行各种改变、取代、及替代而不偏离本案的精神及范畴。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。