1.本发明涉及一种减少串扰的像素阵列基板和一种用于制造像素阵列基板的方法。

背景技术:

2.诸如独立数码相机、移动设备、汽车部件和医疗设备的商业产品中的相机模块包括图像传感器。图像传感器包括形成像素阵列的多个像素,常常还包括形成微透镜阵列的多个微透镜以及形成位于像素阵列和微透镜阵列之间的滤色器阵列的多个滤色器中的至少一个。滤色器阵列的每个滤色器与像素阵列的相应像素对准。类似地,微透镜阵列的每个微透镜与像素阵列的相应像素对准。由图像传感器产生的图像常常包括由电源或光源产生的伪影。光学串扰是一种这样的伪影并且是指在传播通过与像素阵列的第二像素对准的微透镜和/或滤色器之后由像素阵列的第一像素检测到的光。当入射光相对于像素阵列的表面法线以足够高的入射角传播通过微透镜时,会出现一个光学串扰源。

技术实现要素:

3.本文公开的实施例通过防止上面提到的串扰源来减少光学串扰。

4.本发明提供了一种减少串扰的像素阵列基板和一种用于制造像素阵列基板的方法。

5.在第一方面,一种像素阵列基板包括半导体基板、缓冲层和金属环。半导体基板包括第一光电二极管区域。半导体基板的后表面在与第一光电二极管区域上方的后表面的第一后表面区域平行的横截面平面中形成包围第一光电二极管区域的沟槽。缓冲层位于后表面上并且具有(i)位于第一光电二极管区域上方的薄缓冲层区域和(ii)在平行于该横截面平面的平面中在沟槽上方形成环的厚缓冲层区域。金属环位于缓冲层上并覆盖厚缓冲层区域。

6.在一些实施例中,所述金属环包括:在所述厚缓冲层区域上的中间区段;被所述中间区段包围并粘合到所述中间区段的内侧壁和所述厚缓冲层区域的内侧壁两者的内区段;以及粘合到所述中间区段的外侧壁和所述厚缓冲层区域的外侧壁两者的外区段。

7.在一些实施例中,所述内区段和所述外区段中的每一个的厚度在二十纳米和四十纳米之间。

8.在一些实施例中,所述像素阵列基板还包括在所述中间区段的顶表面上的介电环形层。

9.在一些实施例中,所述内区段包括粘合到所述介电环形层的内表面的内顶部区域;以及所述外区段包括粘合到所述介电环形层的外表面的外顶部区域。

10.在一些实施例中,所述像素阵列基板还包括位于所述薄缓冲层区、所述金属环的内侧壁、所述金属环的顶表面和所述介电环形层的顶表面上的衰减层。

11.在一些实施例中,所述厚缓冲层区域的厚度在0.10微米和0.16微米之间。

12.在一些实施例中,所述厚缓冲层区域的宽度在0.10微米和0.25微米之间。

13.在一些实施例中,所述薄缓冲层区域的厚度在二十纳米和四十纳米之间。

14.在一些实施例中,所述像素阵列基板还包括在所述金属环与所述厚缓冲层区域之间的粘合层。

15.在一些实施例中,所述像素阵列基板还包括在所述薄缓冲层区域和所述金属环的内侧壁上的衰减层。

16.在一些实施例中,所述衰减层由钛和氮化钛中的一种形成。

17.在一些实施例中,所述金属环由钨形成。

18.在一些实施例中,所述金属环具有在0.1和0.3微米之间的厚度。

19.在一些实施例中,所述像素阵列基板还包括在所述薄缓冲层区域上并且具有超过所述金属环的厚度的厚度的滤色器。

20.在一些实施例中,所述半导体基板还包括形成二乘二阵列的四个第二光电二极管区域;以及在所述横截面平面中,所述第一光电二极管区域位于由所述四个第二光电二极管区域的相应中心定义的四边形区域内。

21.在一些实施例中,所述半导体基板还包括与所述第一光电二极管区域的第一侧侧边相邻的第二光电二极管区域、与所述第一光电二极管区域的第二侧侧边相邻的第三光电二极管区域,以及与所述第一光电二极管区域角部相邻并与所述第二光电二极管区域和第三光电二极管区域中的每一个侧边相邻的第四光电二极管区域。

22.在第二方面,一种用于制造像素阵列基板的方法包括(i)在设置在半导体基板上的缓冲层上形成金属环;(ii)减小缓冲层的不位于金属环下方的缓冲层区域的厚度,以产生减薄的缓冲层;以及(iii)在减薄的缓冲层和金属环上沉积共形金属层。

23.在一些实施例中,所述方法还包括:移除位于所述金属环的顶表面上方的所述共形金属层的至少一部分;以及移除位于所述半导体基板的光电二极管区域上方的所述共形金属层的部分。

24.在一些实施例中,所述方法还包括在(i)位于所述半导体基板的光电二极管区域上方的所述减薄的缓冲层的部分和(ii)所述金属环的内侧壁上沉积衰减层。

附图说明

25.图1描绘了对场景进行成像的相机。

26.图2是像素阵列基板的横截面示意图,该像素阵列基板是图1的相机的像素阵列基板的实施例。

27.图3是第二像素阵列基板的横截面示意图,第二像素阵列基板是图1的相机的像素阵列基板的实施例。

28.图4是像素阵列基板的横截面示意图,该像素阵列基板是图3的像素阵列基板的实施例。

29.图5是金属环的横截面示意图,该金属环是图3的像素阵列基板的金属环的示例。

30.图6是像素阵列基板的横截面示意图,该像素阵列基板是图3的像素阵列基板的实施例。

31.图7

–

10是在实施例中在制造像素阵列基板的过程中形成的中间基板的相应横截面示意图。

32.图11是图示在实施例中用于制造图3的像素阵列基板的方法的流程图。

33.图12是像素阵列基板的横截面示意图,该像素阵列基板是图3的像素阵列基板的实施例。

34.图13是像素阵列基板的横截面示意图,该像素阵列基板是图3的像素阵列基板的实施例。

具体实施方式

35.在整个说明书中对“一个示例”或“一个实施例”的引用是指结合该示例描述的特定特征、结构或特点包括在本发明的至少一个示例中。因此,在整个说明书中各处出现的短语“在一个示例中”或“在一个实施例中”不一定都是指同一个示例。此外,在一个或多个示例中,可以以任何合适的方式组合特定的特征、结构或特点。

36.为了便于描述,在本文中可以使用空间相对术语,诸如“在...下方”、“在...之下”、“下”、“在...下面”、“在...上方”、“上”等,以描述一个元件或特征与另一个(多个)元件或特征的关系,如图所示。将理解的是,除了附图中描绘的朝向之外,空间相对术语还意图涵盖设备在使用或操作中的不同朝向。例如,如果附图中的设备被翻转,那么被描述为在其他元件或特征“之下”或“下方”或“下面”的元件将被定向为在其他元件或特征“上方”。因此,术语“在...之下”和“在...下面”可以涵盖上方和下方两个朝向。可以以其他方式将设备定向(旋转九十度或以其他朝向),并相应地解释本文中使用的空间相对描述语。此外,还将理解的是,当一层被称为在两个层“之间”时,它可以是两个层之间的唯一层,或者也可以存在一个或多个中间层。

37.术语半导体基板可以是指使用诸如硅、硅锗、锗、砷化镓及其组合之类的半导体形成的基板。术语半导体基板也可以指由一种或多种半导体形成的基板,该基板经历了在基板中形成区域和/或结的先前工艺步骤。半导体基板还可以包括各种特征,诸如掺杂和未掺杂的半导体、硅的外延层以及在基板上形成的其他半导体结构。

38.在整个说明书中,使用了几个技术术语。这些术语应具有其所属领域中的普通含义,除非在本文专门定义或者它们的使用上下文明确地暗示为其他。应当注意的是,在本文档中,元素名称和符号可以互换使用(例如,si与硅);但是,两者具有完全相同的含义。

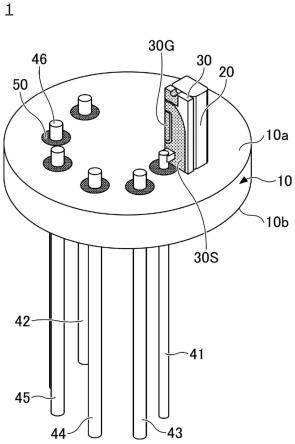

39.图1描绘了对场景进行成像的相机190。相机190包括图像传感器192,图像传感器192包括像素阵列基板100。像素阵列基板100的构成元素可以包括硅和锗中的至少一种。像素阵列基板100包括像素阵列112a。图像传感器192可以是芯片级封装或板上芯片封装的一部分。

40.图2是像素阵列基板200的横截面示意图,像素阵列基板200是像素阵列基板100的示例。图2中所示的横截面平行于由正交轴a1和a3形成的平面,下文中称为x-z平面,其中正交轴a1和a3各自与轴a2正交。在本文中,x-y平面由正交轴a1和a2形成,并且平行于x-y平面的平面被称为横向平面。除非另有说明,否则本文的物体高度是指物体沿着轴a3的范围。在本文中,对轴x、y或z的引用分别指轴a1、a2和a3。而且,在本文中,水平平面平行于x-y平面,宽度是指物体沿着y轴的范围,而竖直方向是沿着z轴。

41.像素阵列基板200包括半导体基板210、钝化层230、缓冲层250、金属环270和滤色器阵列280。金属环270和滤色器阵列280在缓冲层250上。像素阵列基板200还包括微透镜阵

列290,微透镜阵列290包括多个微透镜292和293。每个微透镜292与相应的光电二极管区域212对准以将光引导到其上。每个微透镜293与相应的光电二极管区域213对准以将光引导到其上。

42.半导体基板210包括一个或多个光电二极管区域212。半导体基板210的后表面220在平行于光电二极管区域212上方的后表面220的后表面区域228的横截面平面中形成包围每个光电二极管区域212的沟槽221。沟槽221将小光电二极管区域212与相邻的大光电二极管区域213隔离。后表面区域228可以平行于x-y平面。缓冲层250在后表面220上并且具有均匀的厚度252。

43.半导体基板210的构成元素可以包括硅和锗中的至少一种。半导体基板210包括与后表面220相对的前表面211。后表面220包括内侧壁表面区域222、外侧壁表面区域226和底表面区域224,内侧壁表面区域222、外侧壁表面区域226和底表面区域224形成沟槽221。

44.半导体基板210在前表面211和后表面区域228之间具有厚度216。沟槽221在水平方向和竖直方向上分别具有宽度223和深度225。宽度223可以在0.10微米和0.25微米之间。深度225相对于后表面区域228,并且可以在0.5微米和2.0微米之间。在实施例中,厚度216以介于0.5微米和2.0微米之间超过深度225以确保足够的电隔离。

45.在实施例中,钝化层230覆盖后表面区域228并且位于金属环270和半导体基板210之间。在实施例中,钝化层230邻接后表面220。在实施例中,附加材料层位于钝化层230和后表面220之间。附加层可以比钝化层230薄,并且可以由氧化物形成。在实施例中,钝化层230共形地覆盖每个沟槽221的表面区域222、224和226。钝化层230可以由高κ材料形成,高κ材料例如为介电常数κ大于或等于氮化硅的介电常数(κ≥7)的材料。钝化层230可以具有固定的负电荷,从而在其与半导体基板210的表面界面处产生空穴累积层。氧化铝(al2o3)和氧化铪(hfo2)是这种高κ材料的示例。

46.在实施例中,每个沟槽221填充有沟槽填充材料241。沟槽221、其中的钝化层230的部分和沟槽填充材料241形成深沟槽隔离(dti)结构240。沟槽填充材料241可以是氧化物、金属或它们的组合。

47.在实施例中,半导体基板210包括光电二极管区域212的二维阵列,其中二维阵列的行和列的相应方向定义轴a2和a1的相应方向。相邻的光电二极管区域212在x和y方向中的每个方向上隔开像素间距214。在实施例中,每个光电二极管区域212是在半导体基板210中形成的像素阵列的相应像素的一部分。

48.在实施例中,半导体基板210还包括光电二极管区域213的二维阵列。相邻的光电二极管区域213隔开像素间距214。每个光电二极管区域213位于相应的一对相邻光电二极管区域212之间。光电二极管区域213是与包括光电二极管区域212的二维光电二极管阵列的像素阵列交织的像素阵列的一部分。

49.滤色器阵列280包括多个滤色器282和283,用于对透射通过与其对准的微透镜292或293的光进行光谱过滤。每个滤色器282与相应的光电二极管区域212对准。每个滤色器283与相应的光电二极管区域213对准。在本文中,当滤色器或微透镜的一部分位于光电二极管区域的中心正上方时,滤色器或微透镜与光电二极管区域对准。

50.光电二极管区域212和213具有相应的宽度217和218。在实施例中,宽度218超过宽度217。在实施例中,宽度217在0.7微米和1.0微米之间。在实施例中,宽度218和像素间距

214中的至少一个在0.7微米和3.0微米之间。

51.缓冲层250具有厚度252并且可以由氧化物材料形成。在实施例中,缓冲层250经由化学机械抛光(cmp)减薄至厚度252。cmp在钝化层230、其下方的高κ层和顶表面228上引起机械应力。随着cmp使缓冲层250减薄,引起的机械应力的量值增加,这会导致暗电流和由相机190捕获的图像中的白色像素图像伪影。在实施例中,厚度252超过0.1微米以提供足够的厚度用于应力消除并防止此类伪影。

52.要求厚度252超过0.1微米的成本增加了从大光电二极管区域213到相邻小光电二极管区域212的增加的光学串扰的脆弱性。例如,图2图示了被微透镜293折射的光线202,使得它以入射角203入射在缓冲层上。如果被正确检测,那么光线202将到达微透镜293下方的光电二极管区域213。但是,在被微透镜293折射之后,光线202传播通过滤色器280(1)并在其位置212l处到达光电二极管区域212,这导致光学串扰。

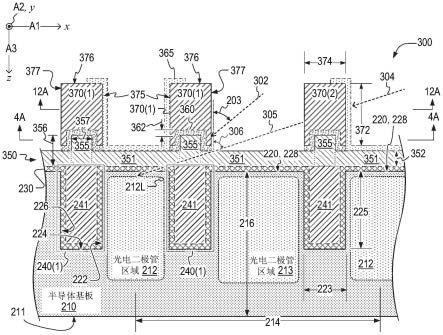

53.图3是降低串扰的像素阵列基板300的横截面示意图,它在下文称为像素阵列基板300。像素阵列基板300弥补了由光线202等造成的光学串扰。像素阵列基板300是像素阵列基板100的示例。

54.像素阵列基板300包括半导体基板210、缓冲层350和金属环370。在水平平面中,金属环370具有孔,其形状可以是多边形(诸如正方形、矩形或六边形)或圆形。

55.在实施例中,以下各项中的至少一个:(a)缓冲层350由氧化物材料形成和(b)金属环370由诸如钨或铝之类的金属形成。在实施例中,像素阵列基板300包括在厚缓冲层区域355和金属环370之间的粘合层360。粘合层360可以由氮化钛形成。粘合层360具有厚度362,其可以在竖直方向和/或水平方向上。在实施例中,厚度362在二十纳米和四十纳米之间。

56.在实施例中,粘合层360由钛和氮化钛中的至少一种形成。粘合层360可以包括钛层和氮化钛层,使得它既用作粘合剂又用作金属阻挡层。例如,钛层将金属环370粘合到厚缓冲层区域355。氮化钛层用作防止金属离子从金属环370扩散到半导体基板210中的扩散阻挡层。

57.缓冲层350在后表面220上并且具有(i)位于光电二极管区域212和213上方的薄缓冲层区域351和(ii)在相邻的薄缓冲层区域351之间并在沟槽240上方的厚缓冲层区域355。厚缓冲层区域355在平行于横截面平面4a的平面中在沟槽221上方形成环。金属环370在缓冲层350上并且覆盖厚缓冲层区域355。图3表示金属环370(1)和相邻的金属环370(2)的一部分。金属环370(1)下方的dti结构240被表示为dti结构240(1)。

58.薄缓冲层区域351具有厚度352,厚度352小于图2的像素阵列基板200的缓冲层250的厚度252。厚度352足够薄以防止光线在金属环370(1)和dti结构240(1)之间传播。在实施例中,厚度352在二十纳米和四十纳米之间。

59.例如,图3图示了以入射角203入射在缓冲层350上的光线302,该入射角203是与光线202相同的入射角。在实施例中,光线302在被对准在大光电二极管区域213上方的微透镜(未示出)折射之后以入射角203传播。光线202导致图2的像素阵列基板200中的光学串扰。光线302具有像光线202一样与光电二极管区域212的位置212l相交的轨迹。然而,由于薄缓冲层区域351的厚度352足够小,例如小于缓冲层250的厚度252,因此金属环370(1)阻挡光线302,并因此防止光线302到达小光电二极管区域212的位置212l并造成光学串扰。在第二示例中,图3图示了光线304和305。光线305在金属环370(1)和dti结构240(1)之间传播,使

得它到达光电二极管区域212。没有金属环370(2),光线305是光线304的延续。但是,对于穿过这样的路径的光线305,厚度352要求其传播角306必须大到使金属环370(2)在光电二极管区域212和光线304之间,使得光线304在它可以传播(如光线305)到光电二极管区域212之前被阻挡。

60.厚缓冲层区域355具有厚度356和宽度357。在实施例中,厚度356在0.10微米和0.16微米之间。下限用于防止导致图像伪影的上面提到的表面应力。上限用于维持足够宽的角响应,例如作为包括光电二极管区域212的像素的主光线角度的函数。在实施例中,宽度357在0.10微米和0.20微米之间。宽度357的上限对于允许将缓冲层350蚀刻至光电二极管区域212上方的厚度352是重要的。

61.金属环370具有高度372和宽度374。在实施例中,高度372在0.1微米和0.3微米之间,这平衡了包括光电二极管区域212的像素的串扰减少和角响应之间的折衷。在实施例中,宽度374在0.16微米和0.26微米之间。宽度374的上限对于允许将缓冲层350蚀刻至光电二极管区域212、213上方的金属环之间的厚度352是重要的。

62.金属环370具有内侧壁375、顶表面376和外侧壁377。在实施例中,像素阵列基板300还包括在(i)光电二极管区域212上方的薄缓冲层区域351的部分和(ii)内侧壁375上的衰减层365,用于衰减朝着光电二极管区域212传播的入射光。衰减层365还可以覆盖顶表面376的至少一部分,并且可以由钛、氮化钛及其组合中的一种形成。在实施例中,衰减层365的厚度在二十纳米和五十纳米之间。在实施例中,衰减层365与表面375、376和光电二极管区域212上方的薄缓冲层区域351的顶表面中的至少一个共形。在实施例中,衰减层365降低光电二极管区域212的光敏度,从而降低光电二极管区域212的量子效率。

63.图4是像素阵列基板400的横截面示意图,像素阵列基板400是像素阵列基板300的示例。图4的横截面在图3中所示的横截面平面4a中。图4表示横截面平面3a,其是图3的横截面平面的示例。像素阵列基板400包括多个光电二极管区域412和多个光电二极管区域413,它们是光电二极管区域212和多个光电二极管区域213的相应示例。虽然横截面平面4a不与光电二极管区域412和413相交,但是图4图示了光电二极管区域412和413以示出它们相对于金属环370和厚缓冲层区域355的位置。由于像素阵列基板400是像素阵列基板300的示例,因此像素阵列基板400可以包括衰减层365,图4中未示出。

64.在实施例中,每个光电二极管区域412位于由形成光电二极管区域413的二乘二阵列的相应光电二极管区域413定义的四边形区域内。在实施例中,四边形区域的形状是正方形、矩形和平行四边形中的一种。例如,光电二极管区域412(1)位于由光电二极管区域413(1

–

4)的相应中心定义的矩形区域419(1)内,并且光电二极管区域412(2)位于由光电二极管区域413(3

–

6)的相应中心定义的矩形区域419(2)内。在实施例中,光电二极管区域412(1)、412(2)位于矩形区域419(1)和419(2)的相应中心处。

65.在实施例中,在前表面211上相邻光电二极管区域212之间的区域或相邻光电二极管区域213之间的区域中定义设备晶体管区域(为简单起见未示出)。设备晶体管区域包括在前表面211上形成的像素晶体管(例如,源极跟随器、复位晶体管、行选择),从而控制包含光电二极管区域212或213的相应像素的操作。

66.在实施例中,每个光电二极管区域412是在半导体基板210中形成的像素阵列416a的相应像素的一部分,并且每个光电二极管区域413是在半导体基板210中形成的像素阵列

417a的相应像素的一部分。像素阵列基板400是像素阵列基板100的示例,使得在实施例中,像素阵列112a包括像素阵列416a和像素阵列417a两者。半导体基板210是半导体基板210的示例。

67.图5是缓冲层350上的金属环570的横截面示意图。金属环570是金属环370的示例并且包括中间区段576、内区段574和外区段578。中间区段576具有内侧壁575、顶表面571和外侧壁577。中间区段576在厚缓冲层区域355上并且包围内区段574。内区段574粘合到内侧壁575和厚缓冲层区域355的内侧壁554两者。外区段578粘合到外侧壁577和厚缓冲层区域355的外侧壁556两者。内区段574和外区段578具有厚度573。在实施例中,厚度573在二十纳米和四十纳米之间。

68.在实施例中,金属环570还包括粘合层560,其是粘合层360的示例。粘合层560(i)将中间区段576粘接到厚缓冲层区域355、(ii)将内区段574粘接到内侧壁575和内侧壁554两者,并且将外区段578粘接到外侧壁577和外侧壁556两者中的至少一个。

69.在实施例中,金属环570还包括在顶表面571上的介电环形层564。环形层564具有内表面563和外表面566。内表面563可以被粘接到其上的内区段574的一部分覆盖。外表面566可以被粘接到其上的外区段578的一部分覆盖。

70.缓冲层350和金属环570是像素阵列基板300的实施例的部分。这个实施例还可以包括衰减层565,衰减层565覆盖光电二极管区域212上方的缓冲层350的薄缓冲层区域351。在实施例中,衰减层565还覆盖内区段574、以及粘合层560和环形层564的部分。衰减层565是图3的衰减层365的示例。

71.图6是像素阵列基板600的横截面示意图,其是像素阵列基板300,在缓冲层350上添加了滤色器阵列680。滤色器阵列680与滤色器阵列280相似,并且包括分别类似于滤色器282和283的滤色器682和683。每个滤色器682与相应的光电二极管区域212对准。每个滤色器683与相应的光电二极管区域213对准。

72.金属环370的顶表面376位于相对于薄缓冲层区域351的顶表面652的高度672处。滤色器阵列680具有顶表面689,顶表面689位于相对于顶表面652的高度686处。高度686的最优范围是通过平衡在过滤不期望的波长与衰减入射在光电二极管区域212和213上的照明的期望波长之间的折衷来确定的。高度686以距离687超过高度672,在实施例中,该距离687在五纳米和四十纳米之间。每个金属环370嵌入在滤色器阵列680中。

73.在实施例中,像素阵列基板600还包括微透镜阵列290,微透镜阵列290包括多个微透镜292和293。每个微透镜292与相应的光电二极管区域212对准,用于将其上的入射光引导到光电二极管区域212。每个微透镜293与相应的光电二极管区域213对准,用于将其上的入射光引导到光电二极管区域213。

74.图7

–

10是在制造像素阵列基板300的过程中形成的中间基板的相应横截面示意图。图7是中间基板700的横截面示意图,中间基板700包括其上设置有钝化层230、缓冲层750、粘合层760、金属层770、硬掩模层780和光致抗蚀剂层790的半导体基板210。半导体基板210的每个沟槽221填充有沟槽填充材料241。在实施例中,缓冲层750的厚度在0.10微米和0.16微米之间。

75.图8是中间基板800的横截面示意图,该中间基板800是在例如经由干法蚀刻移除光电二极管区域212和213上方的层770、780和790的区段之后的中间基板700。中间基板800

包括粘合层860、金属环870、掩模层880和光致抗蚀剂层890,它们分别是在层移除工艺(诸如蚀刻)之后粘合层760、金属层770、掩模层780和光致抗蚀剂层790的剩余区段。

76.图9是中间基板900的横截面示意图。中间基板900是在例如经由蚀刻移除光电二极管区域212和213上方的层750的区段以减薄光电二极管区域212和213上方的层750的区段以产生缓冲层950之后的中间基板800。缓冲层950是图3的缓冲层350的示例,并且具有缓冲层350的厚度352和356。中间基板800还包括粘合层860、金属环870、环形掩模层880和光致抗蚀剂层890。

77.图10是中间基板1000的横截面示意图,该中间基板1000是在移除光致抗蚀剂层890并随后在其上沉积粘合层1060和金属层1070之后的中间基板900。金属层1070具有宽度1073,在实施例中,该宽度在图5的金属环570的内区段574和外区段578的厚度573的相同范围内。

78.掩模层880在平面889中具有顶表面888。图10表示粘合层1060和平面889之间的金属层1070的内区段1074和外区段1078,以及粘合层1060上的金属层1070的水平区段1071。图10还表示金属层1070的帽区段1079和粘合层1060的帽区段1069,它们中的每一个都在平面889上方。

79.移除水平区段1071、在环870上方的帽区段1079的区域和在平面889上方的粘合层1060的部分产生图5的金属环570。金属环870与中间区段576对应;环形掩模层880与介电环形层564对应。金属层1070的内区段1074和外区段1078分别与内区段574和外区段578对应。

80.图11是图示用于制造像素阵列基板的方法1100的流程图。方法1100包括步骤1110、1120和1130。在实施例中,方法1100还包括步骤1140、1150和1160中的至少一个。

81.步骤1110包括在设置在半导体基板上的缓冲层上形成金属环。在步骤1110的示例中,图8的中间基板800的金属环870例如经由光刻工艺从图7的中间基板700形成。

82.在实施例中,步骤1110包括步骤1112、1114和1116中的至少一个。步骤1112包括在缓冲层上沉积金属层。在步骤1112的示例中,金属层770沉积在缓冲层750上或粘合层760上,图7。步骤1114包括在金属层上沉积介电层。在步骤1114的示例中,硬掩模层780和光致抗蚀剂层790中的至少一个沉积在金属层770上。步骤1116包括移除在半导体基板中形成的第一光电二极管区域上方的介电层和金属层的区段以产生金属环。在步骤1116的示例中,移除光电二极管区域212上方的层760、770、780和790的区段以产生金属环870。在实施例中,步骤1116还包括移除与在半导体基板中形成的第一光电二极管区域相邻的第二光电二极管区域上方的介电层和金属层的区段以产生金属环。在步骤1116的另一个示例中,光电二极管区域213上方的层760、770、780和790的区段也被移除以产生与光电二极管区域213对准的金属环。

83.步骤1120包括减小缓冲层的不位于金属环下方的缓冲层区域的厚度以产生位于第一光电二极管上方的减薄的缓冲层。在步骤1120的示例中,缓冲层750的不位于金属环870下方的区域例如经由干法蚀刻减薄,以产生图9的缓冲层950。

84.步骤1130包括在减薄的缓冲层和金属环上沉积共形金属层。在步骤1130的示例中,金属层1070沉积在金属环870和缓冲层950的一部分上,如图10中所示。在实施例中,在沉积金属层1070之前,粘合层1060共形地沉积在金属环870、掩模层880和缓冲层950上以加强共形金属层与金属环870的附着。

85.步骤1140包括移除位于金属环的顶表面上方的共形金属层的至少一部分。在步骤1140的示例中,经由蚀刻移除帽区段1069和帽区段1079。

86.步骤1150包括移除位于半导体基板的光电二极管区域上方的共形金属层的部分。在步骤1150的示例中,移除金属层1070(例如,区段1071和1079)的位于光电二极管区域212、213上方的水平区段1071以产生图5的金属环570。在实施例中,步骤1150还包括移除位于半导体基板的光电二极管区域上方的粘合层的部分。步骤1140和1150可以在单个步骤中执行,诸如单个毯式蚀刻(blanket etching)步骤。

87.步骤1160包括在(i)位于半导体基板的光电二极管区域上方的减薄的缓冲层的部分和(ii)金属环的内侧壁上沉积衰减层。在步骤1160的示例中,层365沉积在位于光电二极管区域212上方的薄缓冲层区域351和金属环370的内侧壁375上。在步骤1160的另一个示例中,衰减层565沉积在缓冲层350的位于光电二极管区域212上方的薄缓冲层区域351、内区段574以及粘合层560的部分和环形层564的部分上。

88.图12是像素阵列基板1200的横截面示意图,像素阵列基板1200是像素阵列基板300的示例。图12的横截面在图3中所示的横截面平面12a中。像素阵列基板1200包括由多个金属环1270和连接相邻环1270的多个互连片段1273形成的金属网格1270a。金属环1270的示例包括金属环370和金属环570。在实施例中,金属环1270和互连片段1273一体形成,使得金属网格1270a是整体式的。在实施例中,每个互连片段1273延伸到包围大光电二极管区域413的相应沟槽中。为清楚起见,并非所有互连片段1273都在图12中标出。在实施例中,像素阵列基板1200包括衰减层1265,衰减层1265是衰减层365、565的示例。虽然光电二极管区域412和413不在横截面12a中,但是图12为了图示金属网格1270a与光电二极管区域412和413的对准而示出它们。

89.虽然在图12中将光电二极管区域412和413的形状图示为正方形,但是,在其他实施例中,光电二极管区域412和413的形状可以与周围的深沟隔离结构和/或周围的金属环1270和互连片段1273定义的形状(例如,菱形或多边形形状)共形。

90.图13是像素阵列基板1300的横截面示意图,像素阵列基板1300是像素阵列基板300的示例。图13的横截面在图3中所示的横截面平面12a中。像素阵列基板1300包括多个光电二极管区域1312、多个光电二极管区域1313和多个金属环1370。光电二极管区域1312、光电二极管区域1313和金属环1370是光电二极管区域212、光电二极管区域213和金属环370或570的相应示例。在实施例中,像素阵列基板1300包括附加的金属环1372,每个附加的金属环1372都在相应的光电二极管区域1313上方对准,使得金属环1370和1372互连以形成金属网格1370a。在实施例中,像素阵列基板1300包括衰减层1365,衰减层1365是衰减层365的示例,衰减层1365涂覆在金属环1370上并覆盖相应光电二极管区域1312的曝光区域。虽然光电二极管区域1312和1313不在横截面平面12a中,但是图13为了示出每个金属环1370与相应光电二极管区域1312的对准而示出它们。

91.光电二极管区域1312包括光电二极管区域1312(k),其中索引k是正整数。图13图示了光电二极管区域1312(1

–

8)。每个光电二极管区域1312(k)具有与其相邻的三个光电二极管区域1313(k)。三个光电二极管区域1313(k)中的两个与光电二极管区域1312(k)侧边相邻。剩余的光电二极管区域1313(k)与光电二极管区域1312(k)角部相邻并且与其他两个光电二极管区域1313(k)侧边相邻。对于每个索引k,光电二极管区域1312(k)和三个光电二

极管区域1313(k)形成二乘二子阵列。

92.在实施例中,每个光电二极管区域1312(k)和与其相邻的三个光电二极管区域1313(k)位于滤色器阵列的单个滤色器下方。例如,当滤色器阵列是拜耳阵列(bayer array)时,绿色滤色器位于光电二极管区域1312和1313上方,其中索引k等于2、4、6或8;红色滤色器位于光电二极管区域1312和1313上方,其中索引k等于1、3和7;而蓝色滤色器位于光电二极管区域1312和1313上方,其中索引k等于5。

93.特征的组合

94.上面描述的特征以及下面要求保护的那些特征可以在不脱离本发明范围的情况下以各种方式组合。以下列举的示例说明了一些可能的、非限制性的组合。

95.(a1)一种像素阵列基板,包括半导体基板、缓冲层和金属环。半导体基板包括第一光电二极管区域。半导体基板的后表面在与第一光电二极管区域上方的后表面的第一后表面区域平行的横截面平面中形成包围第一光电二极管区域的沟槽。缓冲层位于后表面上并且具有(i)位于第一光电二极管区域上方的薄缓冲层区域和(ii)在平行于该横截面平面的平面中在沟槽上方形成环的厚缓冲层区域。金属环位于缓冲层上并覆盖厚缓冲层区域。

96.(a2)在像素阵列基板(a1)的实施例中,金属环包括(i)在厚缓冲层区域上的中间区段,(ii)被中间区段包围并粘合到中间区段的内侧壁和厚缓冲层区域的内侧壁两者的内区段;以及(iii)粘合到中间区段的外侧壁和厚缓冲层区域的外侧壁两者的外区段。

97.(a3)在像素阵列基板(a2)的实施例中,内区段和外区段中的每一个的厚度在二十纳米和四十纳米之间。

98.(a4)像素阵列基板(a2)和(a3)之一的实施例,还包括在中间区段的顶表面上的介电环形层。

99.(a5)在像素阵列基板(a4)的实施例中,(i)内区段包括粘合到介电环形层的内表面的内顶部区域并且(ii)外区段包括粘合到介电环形层的外表面的外顶部区域。

100.(a6)在像素阵列基板(a1)

–

(a5)中任一个的实施例中,厚缓冲层区域的厚度在0.10微米和0.16微米之间。

101.(a7)在像素阵列基板(a1)

–

(a6)中任一个的实施例中,厚缓冲层区域的宽度在0.10微米和0.25微米之间。

102.(a8)在像素阵列基板(a1)

–

(a7)中任一个的实施例中,薄缓冲层区域的厚度在二十纳米和四十纳米之间。

103.(a9)在像素阵列基板(a1)

–

(a8)中任一个的实施例中,缓冲层由氧化物材料形成。

104.(a10)像素阵列基板(a1)

–

(a9)中任一个的实施例,还包括在金属环和厚缓冲层区域之间的粘合层。

105.(a11)在像素阵列基板(a10)的实施例中,粘合层由氮化钛形成。

106.(a12)像素阵列基板(a1)

–

(a11)中任一个的实施例,还包括在(i)薄缓冲层区域、金属环的内侧壁和金属环的顶表面中的至少一个上的衰减层。在包括像素阵列基板(a4)的介电环形层的像素阵列基板(a12)的实施例中,衰减层也可以位于介电环形层的顶表面上。

107.(a13)在像素阵列基板(a12)的实施例中,衰减层由钛和氮化钛中的一种形成。

108.(a14)在像素阵列基板(a1)

–

(a13)中任一个的实施例中,金属环由钨形成。

109.(a15)在像素阵列基板(a1)

–

(a14)中任一个的实施例中,金属环具有在0.1和0.3

微米之间的厚度。

110.(a16)像素阵列基板(a1)

–

(a15)中任一个的实施例,还包括在薄缓冲层区域上的滤色器。滤色器的厚度超过金属环的厚度。在实施例中,滤色器厚度以五纳米和四十纳米之间超过金属环厚度。

111.(a17)在像素阵列基板(a1)

–

(a16)中任一个的实施例中,半导体基板还包括形成二乘二阵列的四个第二光电二极管区域。在横截面平面中,第一光电二极管区域位于由四个第二光电二极管区域的相应中心定义的四边形区域内。

112.(a18)在像素阵列基板(a17)的实施例中,(i)四个第二光电二极管区域包括第一、第二、第三和第四第二光电二极管区域,半导体基板还包括附加的第一光电二极管区域;(ii)半导体基板还包括第五第二光电二极管区域和第六第二光电二极管区域,它们与第三和第四第二光电二极管区域形成附加的二乘二阵列;以及(iii)在横截面平面中,附加的第一光电二极管区域位于由第三、第四、第五和第六第二光电二极管区域的相应中心定义的四边形区域内。

113.(a19)在像素阵列基板(a17)和(a18)中任一个的实施例中,二乘二阵列的像素间距在0.7微米和3.0微米之间,每个第一光电二极管区域的第一宽度在0.7微米和1.0微米之间,并且每个第二光电二极管区域的宽度超过第一宽度。

114.(a20)在像素阵列基板(a1)

–

(a19)中任一个的实施例中,半导体基板还包括第二、第三和第四光电二极管区域。第二光电二极管区域与第一光电二极管区域的第一侧侧边相邻。第三光电二极管区域与第一光电二极管区域的第二侧侧边相邻。第四光电二极管区域与第一光电二极管区域角部相邻并与第二和第三光电二极管区域中的每一个侧边相邻。

115.(b1)一种用于制造像素阵列基板的方法,包括(i)在设置在半导体基板上的缓冲层上形成金属环;(ii)减小缓冲层的不位于金属环下方的缓冲层区域的厚度,以产生减薄的缓冲层;以及(iii)在减薄的缓冲层和金属环上沉积共形金属层。

116.(b2)方法(b1)的实施例,还包括以下步骤:(i)移除位于金属环的顶表面上方的共形金属层的至少一部分,以及(ii)移除位于半导体基板的光电二极管区域上方的共形金属层的部分。

117.(b3)方法(b1)和(b2)之一的实施例,还包括在(i)位于半导体基板的光电二极管区域上方的减薄的缓冲层的部分和(ii)金属环的内侧壁上沉积衰减层。

118.在不脱离本实施例的范围的情况下,可以在以上方法和系统中进行改变。因此应当注意的是,以上描述中包含或附图中所示的内容应当被解释为说明性的,而不是限制性的。在本文中,并且除非另外指出,否则短语“在实施例中”等同于短语“在某些实施例中”,并且并不是指所有实施例。以下权利要求书旨在覆盖本文描述的所有一般和具体特征,以及本方法和系统的范围的所有陈述,就语言而言,可以认为其介于两者之间。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。