1.本发明涉及集成电路设计,尤其涉及一种低功耗的时间数字转换器及转换方法。

背景技术:

2.时间数字转换器是一种将时间间隔转换为数字信号的器件,可以用来计量两个输入信号之间的相位差。时间数字转换器核心的指标是分辨率、动态范围和功耗,传统时间数字转换器专注于解决分辨率和动态范围不可完全满足的矛盾。

3.中国专利:cn113098482 a,2021.07.09(参考文献1)公开了一种低功耗的时间数字转换器及其转换方法,如图1所示,时间数字转换器转换方法为:对两边沿输入信号进行领先滞后判定,首先开启环形慢延时链,环形慢延时链的其中一位输出sdx被计数圈数;之后开启环形快延时链,环形快延时链的其中一位输出fdx被计数;边沿fdx(k)通过d触发器抓取节点边沿sdx(k)的电压状态qx(k)。数据读取模块依次循环抓取各节点数据qx(k),当qn(k)不等于q1(1)时,得到游标残余量(ts-tf)*n*nflap (ts-tf)*ddec (1-q1(1))*0.5n*ts;输出stop信号关断两个环形延时链,圈数计数模块保持此刻的圈数信息nslap和nflap;此结构将游标型环形tdc的传统转换速度提高一倍,且分辨率高,但是延迟单元过多,功耗较大,面积较大,并且存在多个延迟不同的延迟单元难以控制。

4.中国专利:cn113949378a,2020.07.15(参考文献2)公开了一种面积小和功耗低的时间数字转换器。该专利包括环形振荡器和余量产生电路。余量产生电路的每个级都被配置为对环形振荡器的两个不同级的输出进行操作。该专利还包括计数器,用于对次数进行计数,该次数是在被转换为数字值的时间段期间处于第一信号电平和第二信号电平之间的环形振荡器开关的级之一的输出。tdc包括组合器,用于通过将指示由计数器计数的次数的值与余量产生电路的输出进行组合来生成数字值。此结构虽具有低功耗、面积小的优点,但并不能保证高分辨率与宽的动态范围。

5.中国专利:cn113917831a,2022.01.11(参考文献3)公开了一种低功耗高分辨率的时间数字转换器,所述时间数字转换器为两步式n级级联结构,第一步结构包括第一级到第n/2级级联结构,第二步结构包括第n/2 1级到第n级级联结构,第一步结构和第二步结构通过放大器ta连接;每级级联结构包括2个数字时间转换器dtc,分别为第一数字时间转换器和第二数字时间转换器,1个d触发器dff;每个数字时间转换器包括一个输入端、一个输出端和n/2个数字控制起始电压输入引脚。此结构虽具有低功耗和高分辨率的优点,但却不具有宽的动态范围,并且此结构需要全定制设计,复用性不高。

6.为了克服这些问题,需要设计出拥有低功耗、动态范围宽、分辨率高的时间数字转换器。

技术实现要素:

7.发明目的:本发明针对现有技术存在的问题,特别针对时间数字转换器的功耗,提供一种低功耗的时间数字转换器及转换方法,本发明结构和设计简单,功耗低,动态范围

宽,分辨率高。

8.技术方案:本发明的一种低功耗的时间数字转换器包括功耗管理模块、两级时间数字转换器和译码器;两级时间数字转换器分别连接功耗管理模块和译码器;

9.所述功耗管理模块用于生成两级时间数字转换器的第一级和第二级的门控延时信号,两个门控延时信号输入到两级时间数字转换器中,经过两级时间数字转换器采样输出第一级门控延时信号q1《m-1:0》和参考信号的相位差、第二级门控延时信号和参考信号的相位差q2《n-1:0》、以及信号ckd、信号fref_d,信号ckd和信号fref_d输入到耗管理模块用于第二级门控延时信号的生成;译码器将两级时间数字转换器的输出相位差转换成二进制数作为最终的转换输出,并生成选择信号输入到两级时间数字转换器。

10.进一步的,所述功耗管理模块包括计数器,d触发器,异或门和三个与门;具体连接方式为:计数器、第一与门、d触发器和第二与门依次相连接;异或门的输出端与第三与门相连接;

11.反馈信号ckv作为计数器和d触发器的时钟信号,fref作为计数器的复位信号rst,计数器输出信号q[1]和q[3]经过第一与门输出信号gate,所述信号gate与计数器的使能端en和d触发器的d端相连接,gate在ckv的上升沿采样得到同步信号后经过第二与门最终生成功耗管理模块的输出ckv_g,ckv_g为第一级门控延时信号。

[0012]

参考信号fref和计数器的复位、异或门的输入相连接,fref_d和fref经过异或门输出到第三与门,第三与门的另一端输入信号ckd,最终第三与门生成ckd_g,ckd_g为第二级门控延时信号

[0013]

进一步的,所述两级时间数字转换器包括延时链时间数字转换器、选通模块和游标卡尺时间数字转换器。延时链时间数字转换器和选通模块连接;ckv_g与fref输入到延时链时间数字转换器中,选通模块将选择ckd到功耗管理模块中,再将功耗管理模块生成的ckd_g输入到游标卡尺时间数字转换器中,将两级时间数字转换器的输出q1《m-1:0》和q2《n-1:0》输入到译码器中。

[0014]

所述延时链时间数字转换器包括第一延时链和采样单元,所述第一延时链包括m级延时为τ1的延时单元串联;第一级门控延时信号输入到第一延时链时间数字转换器,延时链时间数字转换器的延时单元对应输出e[i]作为m选1选择器的输入,其中i=0,

…

,m-1;每个所述延时单元的输出端连接一个采样单元,参考信号fref与采样单元的另一输入端相连,采样单元输出第一级门控时钟信号和参考信号的相位差q1《m-1:0》;

[0015]

所述选通模块为m选1选择器,e[i]与译码器(300)输出的选择信息作为m选1选择器(202)的输入信号,m选1选择器输出信号ckd到功耗管理模块的第三与门;

[0016]

所述游标卡尺时间数字转换器包括第二延时链、第三延时链和采样单元,所述第二延时链包括n级延时为τ的延时单元串联,所述第三延时链包括n级延时为τ3的延时单元和一个延时为τ4的延时单元串联,;采样单元连接在延时为τ2的延时单元与延时为τ3的延时单元之间。第一级门控时钟信号ckd_g输入到第二延时链,参考信号fref输入到第三延时链,采样单元输出第二级门控延时信号和参考信号的相位差q2《m-1:0》;第三延时链输出信号fref_d到功耗管理模块的异或门。

[0017]

进一步的,所述采样单元为双端输入、单端输出的d触发器。

[0018]

进一步的,延时单元包括两个反相器。

[0019]

进一步的,延迟单元的延迟满足:

[0020]

n*τ3 τ4>n*τ2

ꢀꢀꢀ

(2)

[0021]

进一步的,所述译码器为温度译码器,包括m级依次连接的全加器电路。

[0022]

一种低功耗时间数字转换方法包括如下步骤:

[0023]

步骤1,采用功耗管理模块生成两级时间数字转换器中第一级和第二级的门控信号;

[0024]

具体为:功耗控制模块生成两个窗口信号gate和gate_f,包括两级时间数字转换器的第一级和第二级窗口信号,并根据所述两个窗口信号调制两级时间数字转换器的第一级延时信号ckv和第二级延时信号ckd,得到门控的第一级信号ckv_g和第二级的门控信号ckd_g。

[0025]

步骤2,将生成的第一级和第二级的门控信号分别输入到两级时间数字转换器的两级延时链中,两级时间数字转换器通过参考信号和门控信号获取采样信号q1《m-1:0》和q2《n-1:0》、以及信号ckd,所述采样信号在参考信号fref的上升沿采样得到;

[0026]

步骤3,译码器再将采样信号转换成高精度的二进制码,信号ckd输入到功耗管理模块用于生成第二级的门控信号。

[0027]

有益效果:本发明与现有技术相比,其显著优点是:在两级时间数字转换器的基础上,增加一个功耗管理模块,使两级数字转换器的功耗显著下降,并且依旧保证两级时间数字转换器的范围宽和分辨率高的优点,并且对两级时间数字转换器的改动较小,实现简单,并且功耗管理模块可由代码综合生成,对于不同工艺有更优的移植性并更利于集成。

附图说明

[0028]

图1是参考文献1提出的时间数字转换器的结构图;

[0029]

图2是本发明提供的时间数字转换器的结构图;

[0030]

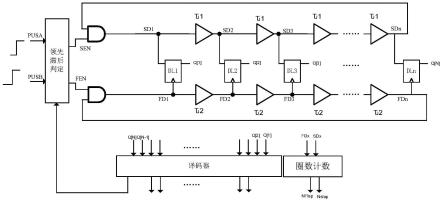

图3是两级时间数字转换器的结构图;

[0031]

图4是译码器的结构图。

[0032]

图中有:功耗管理模块100,两级时间数字转换器200,译码器300;

[0033]

计数器101,第一与门102,d触发器103,第二与门104,异或门105,第三与门106;

[0034]

延时链时间数字转换器201,m选1选择器202,游标卡尺时间数字转换器203,第一延时链204,第二延时链205,第三延时链206。

具体实施方式

[0035]

下面结合实施例对本发明技术方案进行详细说明。

[0036]

本实例提供了一种低功耗的时间数字转换器,如图2所示,包括功耗管理模块100,两级时间数字转换器200和译码器300。

[0037]

其中,所述功耗管理模块由计数器101、第一与门102、d触发器103、第二与门104、异或门105、第三与门106组成。ckv作为计数器的时钟信号,当计数器计数到m(本技术以10为例)时,通过第一与门102输出门信号gate,再由d触发器103同步输出门信号以减小逻辑电路的毛刺,d触发器103的输出与ckv经过第二与门104输出门控的ckv_g信号。由两级时间数字转换器输出的fref_d和fref经过异或门105输出连接到第三与门106的输入,ckd作为

第三与门的输入,第三与门输出为第二个门控时钟ckd_g。

[0038]

其中,计数器中m的取值应满足:

[0039][0040]

所述式(1)中m为计数器所需要计数的最大值,t

ckv

为计数器的时钟信号ckv的周期,t

fref

为参考信号fref的周期,t

dl1

为两级时间数字转换器中第一级延时链dl1的总延时,t

setup

为d触发器的建立时间。

[0041]

其中,如图3所示,所述两级时间数字转换器由延时链时间数字转换器201、m选1选择器202、游标卡尺时间数字转换器203组成。所述延时链时间数字转换器201由第一延时链204和m个采样单元组成,所述第一延时链204由m个延时为τ1的延时单元串联组成,所述采样单元为双端输入单端输出的d触发器。所述游标卡尺时间数字转换器208由第二延时链205、第三延时链206和n个采样单元组成,所述第二延时链204由n个延时为τ2的延时单元串联组成,所述第三延时链206由n-1个延时为τ3的延时单元和一个延时为τ4串联组成,所述采样单元为双端输入单端输出的d触发器。第一延时链204中由ckv_g输入生成e[i](i=0,

…

,m-1)作为m选1选择器202的输入,选择器202的输出ckd输入到功耗管理模块生成门控时钟ckd_g。ckd_g作为第二延时链205的输入,fref作为第三延时链206的输入生成延时的fref_d。其中延迟单元的延迟应满足:

[0042]

n*τ3 τ4>n*τ2

ꢀꢀꢀ

(2)

[0043]

所述式(2)可设定τ3的值。

[0044]

其中,如图4所示,所述译码器300由全加器级联组成。第一级门控延时信号q1《m-1:0》做为译码器的输入,q1《m-1:0》依次作为全加器的输入,输出全加器的求和结果s和进位结果co,根据s和co再连接全加器输出第二级的求和结果s和进位结果co,多级依次类推,最终输出选择信号sel。

[0045]

本发明还提供了一种低功耗时间数字转换方法,包括:

[0046]

(1)采用功耗管理模块将两级时间数字转换器的信号转换成门控信号,使两级时间数字转换器的延时链只在较小的范围内工作。具体包括以下步骤:

[0047]

(1.1)ckv作为计数器的时钟信号,计数到特定值停止计数,在fref的上升沿再复位重新计数,通过第一与门102将计数器的值转换成门信号gate,当gate为高电平时,计数器锁住计数值,gate通过d触发器103与ckv进行同步,此方法可以消除组合逻辑的毛刺,由d触发器同步的信号和ckv经过第二与门104生成门控的ckv_g。

[0048]

(1.2)fref和经过第三延时链206的fref_d信号经过异或门105生成的信号和ckd经过第三与门生成ckd_g。

[0049]

(2)采用两级时间数字转换器采样门控的时钟得到q1《m-1:0》和q2《n-1:0》,经过译码器得到整个时间数字转换器的最终输出。

[0050]

本实例在两级时间数字转换器的基础上,增加一个功耗管理模块,减小两级时间数字转换器的功耗。不仅保留两级时间数字转换器宽范围、高分辨率的优点,还减小了两级时间数字转换器的功耗,并且对两级时间数字转换器的改动较小,实现简单,并且功耗管理模块可由代码综合生成,对于不同工艺有更优的移植性并更利于集成。

[0051]

综上所述,本发明既有两级数字时间数字转换器高分辨率、宽动态范围的优点,又

解决了两级时间数字转换器功耗较高的问题,并且功耗管理模块可通过代码综合实现,复用性较高,且对整体系统的稳定性影响较小,具有良好的应用前景。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。