1.本发明是数模混合集成电路技术领域范围,涉及一种基于时间寄存器的交错式流水型时间数字转换器电路设计。

2.背景内容

3.市面上常见tdc(时间数字转换器)结构有计数型时间数字转换器、延迟链时间数字转换器(快闪型)、游尺延时链型时间数字转换器、环形时间数字转换器等,其中快闪型tdc由延迟链和边沿比较器量化两路输入信号上升沿的时间间隔,该tdc的电路结构简单,结构转换速度快,但量化精度受限于器件的最小门级延时,无法达到亚门级精度,大大限制了快闪型tdc的应用范围,流水线型tdc脱产于快闪型tdc,该种tdc突破了一个反相器延迟时间的限制,可以达到1ps以下,达到了高精度的要求。

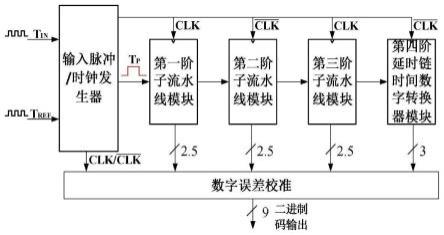

4.图1给出一种现有的基于时间寄存器的流水线型tdc电路,其主要由输入脉冲/时钟发生器模块、第一阶子流水线模块、第二阶子流水线模块、第三阶子流水线模块、第四阶延时链模块和数字误差校准模块构成。原始输入待测信号t

in

和t

ref

经脉冲/时钟发生器后,产生对应脉冲宽度的测量脉冲信号t

p

,以及控制个子tdc模块协同工作的clk时钟信号。其中第一阶子流水线模块和第三阶子流水线模块在时钟信号clk的控制下同步工作;第三阶子流水线模块和最后一阶延时链型子tdc模块在时钟信号的控制下同步工作。其中clk和是相位相差180

°

的同周期信号。待测时间信号t

p

在clk时钟的控制下经第一阶子流水线模块进行粗量化,经第一阶子流水线模块量化后的二进制码传递给数字误差校准模块,同时经第一阶子流水线模块量化后的时间残差的互补时间量输入至下一阶子流水线模块,也即第二阶子流水线模块。第二阶子流水线模块采用同样的方法和原理对上一阶输出的放大后的互补时间量进行再次量化,依次递进,直到最后一级子流水线模块输出量化数值二进制码,给数字误差校准模块,并将此级产生的时间残差的互补时间量经放大后传递给延时链型tdc模块,最后经量化后的输出二进制码传递给数字误差校准模块。值得说明的是,第一阶和第三阶子流水线模块不同工作,第二阶和第四阶子时间数字转换器模块同步工作,第一阶和第三阶子流水线模块在测量时,第二阶和第四阶子时间数字转换器模块则在进行复位操作;反之亦然。

5.上述传统流水线型时间数字转换器存在一下几方面的缺点:第一,在将两个上升沿间的时间差转换为相应宽度的脉冲信号时,总是无法保证产生的时间脉冲其宽度等于两上升沿间的真实时间差;第二,时间脉冲信号在经逻辑门传输时,由于其对信号上升沿和下降沿的响应曲线不同,以及在经时间放大的放大过程中,由于时间放大器的非理想性,不可避免的会使得想要的时间信号脉宽宽度偏离理想值;第三,由于当start和stop信号上升沿间的间隔很小时,无法产生相应的脉冲信号,因此需要实现在start和stop信号间插入一个固定的延时单元;第四,即使在子tdc模块完成一次输入时间量化,并经dtc选通了某一相应开关的情况下,当trigg信号到来产生所需的量化时间余量时,延时链上的高电平set信号不仅会经过这个开关传输至异或门的一个输入端,同时也还会继续沿着延时链往后传播,这无疑会显著增大电路的动态功耗;第五,该流水线型tdc自身不具备抗ptv的鲁棒性,又没

有相应的测量校准机制,因而很难实现实际的应用价值。

技术实现要素:

6.为了消除因器件失配和放大器的非理想引起的测量误差,提高该时间数字转换器系统的测量分辨率,以及降低子流水线模块的动态功耗。本发明在传统流水线型tdc的基础上,采用交错结构代替直线式结构,实现了一种具有高性能的基于时间寄存器的交错式流水线型时间数字转换器电路。

7.为实现上述目的,本发明包输入脉冲/控制信号发生器模块1、第一阶子流水线模块2、第二阶子流水线模块3、第三阶子流水线模块4、第四阶子流水线模块5、第一延时链型数字转换器模块6、第二延时链型数字转换器模块7、数字误差校准模块8以及两个控制开关s1,s2和数据总线;

8.所述输入脉冲/控制信号发生器模块1,其设有两个输入端和三个输出端;其中第一输入端连接输入信号t

in

,第二输入端连接输入信号t

ref

;第一输出端输出脉冲信号ts,第二输出端输出脉冲信号t

p

,第三输出端输出控制信号ctrl;通过对输入信号ts和t

p

的测量,间接实现对输入信号t

in

和t

ref

时间差δt的测量,它们之间存在以下关系δt=t

s-t

p

;其中脉冲信号t

p

是一脉宽固定且已知的脉冲信号t

p

,其可用来实现对该交错式流水线型tdc最低有效位的校准;

9.所述第一阶子流水线模块2,其设有两个输入端和两个输出端;其中第一输入端连接输入脉冲/控制信号发生器模块1第一输出端,用于接收待测量信号ts,或根据第二控制开关s2的连接情况,连接第四阶子流水线模块5的第一输出端,用于接收第四阶子流水线模块5输出的放大后的互补量化残余;第二输入端连接输入脉冲/控制信号发生器模块1的第三输出端,接收控制信号ctrl;第一输出端输出放大后的互补量化残余,第二输出端连接至送往数字误差校准模块8的数据总线;

10.所述第二阶子流水线模块3,其设有两个输入端和两个输出端;其中第一输入端连接第一阶子流水线模块2第一输出端,接收第一阶子流水线模块2输出的放大后的互补量化残余;第二输入端连接输入脉冲/控制信号发生器模块1的第三输出端,接收控制信号ctrl;第一输出端输出放大后的互补量化残余,第二输出端连接至送往数字误差校准模块8的数据总线;

11.所述第三阶子流水线模块4,其设有两个输入端和两个输出端;其中第一输入端连接输入脉冲/控制信号发生器模块1第二输入端,接收待测脉冲信号t

p

,或根据第一控制开关s1的连接情况,连接第二阶子流水线模块3第一输出端,接收第二阶子流水线模块3输出的放大后的互补量化残余;第二输入端连接输入脉冲/控制信号发生器模块1的第三输出端,接收控制信号ctrl;第一输出端连接至第四阶子流水线模块5的第一输入端,第二输出端连接至送往数字误差校准模块8的数据总线;

12.所述第四阶子流水线模块5,其设有两个输入端和两个输出端;其中第一输入端连接至第三阶子流水线模块4第一输出端,接收第三阶子流水线模块4输出的放大后的互补量化残余,第二输入端连接至输入脉冲/控制信号发生器模块1的第三输出端,接收控制信号ctrl;第一输出端输出放大后的互补量化残余,第二输出端连接至送往数字误差校准模块8的数据总线。

13.上述的第一阶子流水线模块2、第二阶子流水线模块3、第三阶子流水线模块4、第四阶子流水线模块5均采用相同结构;该子流水线模块包括时间寄存器、时间数字转换器、数字时间转换器、减法器、时间放大器以及存在于延时链中的控制开关;所述时间寄存器受第一输入端输入的待测时间脉冲信号和第二输入端输入的控制信号控制,其输出信号一方面直接连接到减法器,另一方面传递给时间数字转换器,并经时间数字转换器转化为一定位数的量化数值,作为子流水线模块的第二输出端连接至送往数字误差校准模块8的数据总线;此量化数值经数字时间转换器转化为时间量与时间寄存器直接传递给减法器的信号做差,得到时间残差的互补时间量;再经过时间放大器放大之后作为子流水线模块的第一输出端。

14.所述第一延时链型数字转换器模块6,其设有两个输入端和一个输出端;其中第一输入端根据第一控制开关s1的连接情况,要么连接第二阶子流水线模块3的第一输出端,接收第一阶子流水线模块2输出的放大后的互补量化残余,要么断开,第二输入端连接输入脉冲/控制信号发生器模块1的第三输出端,接收控制信号ctrl;输出端连接至送往数字误差校准模块8的数据总线;

15.所述第二延时链型数字转换器模块7,其设有两个输入端和一个输出端;其中第一输入端根据第二控制开关s2的连接情况,要么连接至第四阶子流水线模块5的第一输出端,接收第四阶子流水线模块5输出的放大后的互补量化残余,要么断开,第二输入端连接至输入脉冲/控制信号发生器模块1的第三输出端,接收控制信号ctrl;输出端连接至送往数字误差校准模块8的数据总线;

16.所述第一控制开关s1,用于切换第二阶子流水线模块3的第一输出端的连接点;当第二阶子流水线模块3第一次产生量化残余输出时,第一控制开关s1连接至第三阶子流水线模块4的第一输入端,当第二阶子流水线模块3第二次产生量化残余输出时,第一开关s1则连接至延时链型数字转换器模块6的第一输入端;

17.所述第二控制开关s2,用于切换第二阶子流水线模块3的第一输出端的连接点;当第四阶子流水线模块5第一次产生量化残余输出时,开关s2连接至第一阶子流水线模块2的第一输入端,当第四阶子流水线模块5第二次产生量化残余输出时,开关s2则连接至延时链型数字转换器模块7的第一输入端;

18.两个延时链型时间数字转换器6、7分别对最后一阶子流水线模块3、5放大输出的量化时间残余的互补时间量进行最后一次细量化,量化输出二进制码送入数字误差校准模块,实现最终的时间量化二进制码输出,至此完成一次完整的输入时间测量过程;由于延时链型时间数字转换器6、7相较于前面的子流水线模块2、3、4、5,其量化输出位宽要多一位,因此具有更高的测量分辨率。

19.所述数据总线用于将各级子流水线模块和延时链型时间转换器模块产生的部分量化二进制码送入到数字误差校准模块8,已完成最后的量化数据校准及合并;

20.所述数字误差校准模块8,设其有两个输入端和一个输出端;其中第一输入端连接数据总线,接收各子tdc模块的量化输出,第二输入端连接输入脉冲/控制信号发生器模块1的第三输出端,接收控制信号ctrl;输出端输出最后的量化二进制码。该数字误差校准模块8,将各级子流水线模块和延时链型时间转换器模块产生的部分量化二进制码进行合成,并转换为最终的二进制码输出;这期间需要对各子时间数字转换器模块的量化输出进行适当

的预处理,然后才能通过移位相加,完成整个数字输出模块的校准工作;数字误差校准模块输出的二进制码即为所测时间的相应数字量。

21.脉冲信号ts依次经过第一阶子流水线模块2、第二阶子流水线模块3、第三阶子流水线模块4、第四阶子流水线模块5,以及第四阶后面的第二延时链型时间数字转换器模块7;脉冲信号t

p

则依次经过第三阶子流水线模块4、第四阶子流水线模块5、第一阶子流水线模块2、第二阶子流水线模块3,以及第二阶子流水线模块后的延时链型时间数字转换器模块6;其中,最后一阶延时链型时间数字转换器模块由于不需要对其自身的量化时间残余进行提取,因此其不需要时间放大器和数字时间转换器;两个控制开关s1和s2控制相应输入信号的流向,只有在脉冲信号ts和t

p

都经过了四个子流水线模块处理,开关s1和s2才闭合;使得每次测量时,脉冲信号ts和t

p

都会经过相同的子流水线模块,因而能够消除子流水线模块的失配以及时间放大器的非线性带来的测量误差问题。

22.与传统流水线型时间数字转换器电路相比,本发明的优点如下:

23.1.本发明由于采用交错式流水线型方式,脉冲信号ts和t

p

都会经过相同的子流水线模块,因而能够消除子流水线模块的失配以及时间放大器的非线性带来的测量误差。

24.2.本发由于的子流水线模块延时链中设有控制开关,实现子流水线模块动态功耗的降低。

25.3.本发明由于输出的二进制码1bit代表的时间精度是多少,可以通过对已知特定脉宽的待测信号t

p

进行测量反推出来,也即进行最低有效位lsb的校准,通过校准后的lsb实现对测量结果的校准,提高该tdc的测量精度。

26.4.本发明由于延时链型时间数字转换器相较于前面的子流水线模块其量化输出位宽要多一位,因此具有更高的测量分辨率。

27.5.本发明由于采用交错式流水线型,实现了子流水线模块的复用,在提高测量分辨率的同时减小了所需的芯片面积。

附图说明

28.图1传统流水线时间数字转换器框图。

29.图2基于时间寄存器的交错式流水线型时间数字转换器实现框图。

30.图3子流水线模块的结构框图。

31.图4子流水线模块电路实现原理图。

32.图5延时链型时间数字转换器模块电路实现原理图。

33.图6子流水线模块时间测量及残差提取流程图。

具体实施方式

34.为了使本发明的技术特点、电路构成、功能与使用场景直观易懂,下面将结合图示,进一步阐述本发明,在以下表述中,除非特别说明,术语“使能”、“连”、“连接”应是广义上的理解。

35.参照图2,本发明包输入脉冲/控制信号发生器模块1、第一阶子流水线模块2、第二阶子流水线模块3、第三阶子流水线模块4、第四阶子流水线模块5、第一延时链型数字转换器模块6、第二延时链型数字转换器模块7、数字误差校准模块8以及两个控制开关s1,s2和

数据总线所述输入脉冲/控制信号发生器模块1,其设有两个输入端和三个输出端;其中第一输入端连接输入信号t

in

,第二输入端连接输入信号t

ref

;第一输出端输出脉冲信号ts,第二输出端输出脉冲信号t

p

,第三输出端输出控制信号ctrl;通过对输入信号ts和t

p

的测量,间接实现对输入信号t

in

和t

ref

时间差δt的测量,它们之间存在以下关系δt=t

s-t

p

;其中脉冲信号t

p

是一脉宽固定且已知的脉冲信号t

p

,其可用来实现对该交错式流水线型tdc最低有效位的校准;

36.所述第一阶子流水线模块2,其设有两个输入端和两个输出端;其中第一输入端连接输入脉冲/控制信号发生器模块1第一输出端,用于接收待测量信号ts,或根据第二控制开关s2的连接情况,连接第四阶子流水线模块5的第一输出端,用于接收第四阶子流水线模块5输出的放大后的互补量化残余;第二输入端连接输入脉冲/控制信号发生器模块1的第三输出端,接收控制信号ctrl;第一输出端输出放大后的互补量化残余,第二输出端连接至送往数字误差校准模块8的数据总线;

37.所述第二阶子流水线模块3,其设有两个输入端和两个输出端;其中第一输入端连接第一阶子流水线模块2第一输出端,接收第一阶子流水线模块2输出的放大后的互补量化残余;第二输入端连接输入脉冲/控制信号发生器模块1的第三输出端,接收控制信号ctrl;第一输出端输出放大后的互补量化残余,第二输出端连接至送往数字误差校准模块8的数据总线;

38.所述第三阶子流水线模块4,其设有两个输入端和两个输出端;其中第一输入端连接输入脉冲/控制信号发生器模块1第二输入端,接收待测脉冲信号t

p

,或根据第一控制开关s1的连接情况,连接第二阶子流水线模块3第一输出端,接收第二阶子流水线模块3输出的放大后的互补量化残余;第二输入端连接输入脉冲/控制信号发生器模块1的第三输出端,接收控制信号ctrl;第一输出端连接至第四阶子流水线模块5的第一输入端,第二输出端连接至送往数字误差校准模块8的数据总线;

39.所述第四阶子流水线模块5,其设有两个输入端和两个输出端;其中第一输入端连接至第三阶子流水线模块4第一输出端,接收第三阶子流水线模块4输出的放大后的互补量化残余,第二输入端连接至输入脉冲/控制信号发生器模块1的第三输出端,接收控制信号ctrl;第一输出端输出放大后的互补量化残余,第二输出端连接至送往数字误差校准模块8的数据总线。

40.上述第一阶子流水线模块2、第二阶子流水线模块3、第三阶子流水线模块4、第四阶子流水线模块5均采用相同结构;参照图3,该子流水线模块包括时间寄存器、时间数字转换器、数字时间转换器、减法器、时间放大器以及存在于延时链中的控制开关;所述时间寄存器受第一输入端输入的待测时间脉冲信号和第二输入端输入的控制信号控制,其输出信号一方面直接连接到减法器,另一方面传递给时间数字转换器,并经时间数字转换器转化为一定位数的量化数值,作为子流水线模块的第二输出端连接至送往数字误差校准模块8的数据总线;此量化数值经数字时间转换器转化为时间量与时间寄存器直接传递给减法器的信号做差,得到时间残差的互补时间量;再经过时间放大器放大之后作为子流水线模块的第一输出端。

41.图4为子流水线模块具体电路实现原理图,其主要包括或门、门控延时链、采样d触发器、编码器、脉冲发生器、时间放大器、控制开关。其有两个输入端和两个输出端,两个输

入端分别连接被测脉冲信号tin和控制信号ctrl;set为电路内部的置位信号,clk为电路内部的时钟信号,两个输出端分别输出放大后的互补量化残余tout和量化数值dout。通过子流水线模块延时链中控制开关的开启,实现子流水线模块动态功耗的降低。具体如图6(b)所示,以该模块输出的3’b001量化二进制码为例,其会控制开关s1闭合,开关s1’断开。延时链上的set信号在经s1传递至其后的异或门时,经不再同时沿延时链继续向后传播,进而实现降低该子流水线模块动态功耗的功能。

42.所述第一延时链型数字转换器模块6,其设有两个输入端和一个输出端;其中第一输入端根据第一控制开关s1的连接情况,要么连接第二阶子流水线模块3的第一输出端,接收第一阶子流水线模块2输出的放大后的互补量化残余,要么断开,第二输入端连接输入脉冲/控制信号发生器模块1的第三输出端,接收控制信号ctrl;输出端连接至送往数字误差校准模块8的数据总线;

43.所述第二延时链型数字转换器模块7,其设有两个输入端和一个输出端;其中第一输入端根据第二控制开关s2的连接情况,要么连接至第四阶子流水线模块5的第一输出端,接收第四阶子流水线模块5输出的放大后的互补量化残余,要么断开,第二输入端连接至输入脉冲/控制信号发生器模块1的第三输出端,接收控制信号ctrl;输出端连接至送往数字误差校准模块8的数据总线;

44.上述两个延时链型时间数字转换器模块如图5所示,其电路结构包括d触发器、门控延时链、或门、编码器。其有两个输入端和一个输出端,两个输入端分别连接被测脉冲信号tin和控制信号ctrl;set为电路内部的置位信号,clk为电路内部的时钟信号,输出端输出量化数值dout。由于延时链型时间数字转换器模块不需要对其自身的量化时间残余进行提取,因此其不需要时间放大器和数字时间转换器模块。ctrl信号时钟处于低电平,脉冲信号tin高电平到来,控制信号en变高,使能门控延时单元,高电位set信号沿门控延时链向后边传输,直到tin脉冲信号下降沿来临,set的高电平停止向后传输,随后clk信号变高,触发沿d触发器对门控延时链的相位状态进行采样,并经编码器后把各个d触发器输出的高低电频信号编码输出得到量化数值。

45.所述第一控制开关s1,用于切换第二阶子流水线模块3的第一输出端的连接点;当第二阶子流水线模块3第一次产生量化残余输出时,第一控制开关s1连接至第三阶子流水线模块4的第一输入端,当第二阶子流水线模块3第二次产生量化残余输出时,第一开关s1则连接至延时链型数字转换器模块6的第一输入端;

46.所述第二控制开关s2,用于切换第二阶子流水线模块3的第一输出端的连接点;当第四阶子流水线模块5第一次产生量化残余输出时,开关s2连接至第一阶子流水线模块2的第一输入端,当第四阶子流水线模块5第二次产生量化残余输出时,开关s2则连接至延时链型数字转换器模块7的第一输入端;

47.所述数据总线用于将各级子流水线模块和延时链型时间转换器模块产生的部分量化二进制码送入到数字误差校准模块8,已完成最后的量化数据校准及合并;

48.所述数字误差校准模块8,设其有两个输入端和一个输出端;其中第一输入端连接数据总线,接收各子tdc模块的量化输出,第二输入端连接输入脉冲/控制信号发生器模块1的第三输出端,接收控制信号ctrl;输出端输出最后的量化二进制码。采用数字误差校准模块8对各阶子tdc输出的局部量化二进制码进行校准与合并,这样做的原因主要有:

49.其一、是数字误差校准模块8输出的二进制码位数不是由每一级子流水线模块和延时链时间数字转换器模块(6或7)输出的位数简单相加,因为每一级子流水线模块的输出的量化数值的二进制代码位数的编码和延时链型时间数字转换器模块(6或7)的量化数值的位数代码编码不能用完;

50.其二、是因为交错式流水线型时间数字转换器电路要对脉冲信号ts和t

p

的量化数值做处理并且做差,才是我们所求的时间间隔,所以要经过数字误差校准模块校准。

51.综上,输入脉冲信号/控制发生器1总共输出三种信号,待测脉冲信号ts和t

p

和控制信号ctrl,其中输出的测脉冲信号ts和t

p

信号分别输入第一阶子流水线模块2和第三阶子流水线模块4,ctrl为控制信号控制各个模块协调工作,第一阶子流水线模块2在ctrl的控制下输出一定位数二进制码量化数值,同时输出时间残差的互补时间量给第二阶子流水线模块3进行和第一阶子流水线模块2相同的处理,也同时输出量化数值和时间残差的互补时间量,但是此时由于开关s1处于打开状态,时间残差的互补时间量通过交错线输入到第三阶子流水线模块4。此时测脉冲信号t

p

信号的处理过程也到达第一阶子流水线模块2,也就是说,第四阶子流水线模块5输出的时间残差的互补时间量通过交错线到达第一阶子流水线模块2。在测脉冲信号ts信号和t

p

信号的处理分别到达了第四阶子流水线模块5和第二阶子流水线模块3时,此时开关s1和s2均关闭,使得第四阶子流水线模块5和第二阶子流水线模块3输出的时间残差的互补时间量分别输出到下一个不同延时链型时间数字转换器模块6和7处理之后将量化数值各自传给数字误差模块8进行校准输出,输出即为我们所需要的δt所对应二进制码值。

52.参照图6以输入脉冲宽度为4.3τ的输入信号为例展示各阶子流水线模块的工作过程。设δt为来自输入端tin的待测时间脉冲,当电路初始化完毕,输入信号set置1后,电路进入正常工作状态,当δt到来后,控制延时链的使能信号en变高,set信号开始在延时链中传播,如图6(a)所示。当δt结束时,控制使能信号en变低,各延时单元的输出状态不再发生变化,并保持当前时刻不变。随后d触发器组对门控延时链的相位状态进行采样,采样结果经译码器译码后,得到3b的粗量化结果,同时控制对应某一开关的闭合,如图6(b)所示。接着控制信号ctrl到来后,控制使能信号en再次变高,延时链上的高电平继续向后传播,并经闭合的开关传输至输出端的异或门,得到待测时间脉冲δt的互补残留时间脉冲信号to,如图6(c)所示,该信号经脉冲序列时间放大器的放大后,得到一组同宽的脉冲序列信号,并作为后一级子流水线tdc模块的待测量信号,如图6(d)所示。重复上述过程,直至最后一级子tdc模块的量化输出,最后将各子tdc模块的量化结果再次进行译码校准,得到最终的待测时间脉冲的二进制量化结果。

53.本发明的工作原理是:

54.参照图2,本发明的时间数字转换器由输入脉冲/控制信号发生器1、第一阶子流水线模块2、第二阶子流水线模块3、第三阶子流水线模块4和第四阶子流水线模块5、两个延时链型时间数字转换器模块6和7、数字误差校准模块8组成,其中输入脉冲/控制信号发生器输出两个脉冲信号,分别是ts和t

p

信号,通过将脉冲信号ts和t

p

的测量值做差,来间接实现对输入信号t

in

和t

ref

差值δt的测量。其中的子流水线模块由时间寄存器、时间数字转换器、数字时间转换器、减法器和时间放大器组成。为了实现交错的目的,如图2所示:我们从开关s1处引出一条通路到第三阶子流水线模块4的第一输入端,从开关s2处引出一条通路到第

一阶子流水线模块2的第一输入端。开关s1左侧接第二阶子流水线模块3右侧接延时链型时间数字转换器模块6,开关s2左侧接第四阶子流水线模块5,右侧接延时链型时间数字转换器模块7,两个延时链模块的输出直接接到数字误差校准模块。最后经数字误差校准模块8校准输出二进制码。

55.假设t

in

和t

ref

信号的初始值为零,且两个信号初始时刻开始的第一个上升沿相差t1时间,我们所需的目的就是测试这个t1时间,这两个信号经过输入脉冲/控制信号发生器,产生两脉冲信号t

p

和ts。

56.假设脉冲信号t

p

在控制信号ctrl、s1和s2的控制下依次经过模块4、模块5、模块2和模块3处理之后产生的局部量化数值分别为a1、a2、a3、a4、a5,t

p

的量化数值关系为第三阶子流水线模块4对应a1,第四阶子流水线模块5的量化数值对应a2,第一阶子流水线模块2对应a3,第二阶子流水线模块3对应a4,延时链型时间数字转换器6对应的量化数值码对应a5。

57.假设脉冲信号ts在控制信号ctrl、s1和s2的控制下依次经过模块2、模块3、模块4和模块5处理之后产生的局部量化数值分别为b1、b2、b3、b4、b5,t

p

的量化数值关系为第一阶子流水线模块2对应b1,第二阶子流水线模块3的量化数值对应b2,第三阶子流水线模块4对应b3,第四阶子流水线模块5对应b4,图1中延时链型时间数字转换器7对应的量化数值码对应b5。

58.当各个局部量化数值a1、a2、a3、a4、a5和b1、b2、b3、b4、b5全部通过数据总线传入数字误差校准模块处理8,并经过校准合并处理后,最终输出t

in

和t

ref

的时间间隔δt所对应的量化二进制码。数字误差校准模块内部的操作是先通过a1、a2、a3、a4、a5将t

p

脉冲信号对应的时间脉宽t1求出,通过b1、b2、b3、b4、b5将ts脉冲信号对应的脉宽时间t2求出,最终δt=t1-t2。

59.以上所述仅是本发明的一种实施例,不构成对本发明的任何限制,显然在本发明的构思下,可以对其电路进行不同的变更与改进,但这些均在本发明的保护之列。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。