1.本发明有关于一种计算机装置的指令执行技术,且特别有关于一种指令模拟装置及其方法。

背景技术:

2.随着计算机指令集系统技术的不断发展,支持各指令集架构的处理器所支持的指令集会逐渐更新版本,导致旧版的处理器无法完整地支持属于处理器相同指令集架构的较新指令集或扩充指令集。若新指令集或扩充指令集中的扩增指令要在旧版处理器上运行的话,旧版处理器可能无法正确执行这些扩增指令甚至发生错误。换句话说,处理器能够支持的指令在经制造后就已经确定,后续的扩增指令可能无法在旧版处理器上正确运行,因此存在处理器指令集的兼容性问题。

3.因此,当某一系列或型号的处理器无法支持更新版本的指令集时,通常便需要淘汰掉这些处理器,从而形成资源的浪费,且变相缩短了使用到这些旧版处理器的电子设备的使用年限。

技术实现要素:

4.本发明提供一种指令模拟装置及其方法,用以解决处理器指令集的兼容性问题,从而延长使用此模拟装置的电子设备的使用年限。

5.本发明的模拟装置包括监测器。监测器用以判断处理器目前需执行的待执行指令是否为可兼容指令或为扩增指令,其中该扩增指令为处理器目前所具备指令集为同一类型的新指令集或扩充指令集中的指令。若判断该待执行指令为扩增指令时,转换该待执行指令为由该处理器原生指令或可兼容指令组成的兼容指令序列所构筑的模拟程序,并通过执行该模拟程序来模拟该待执行指令的执行结果。

6.本发明的转换方法包括下列步骤。判断待执行指令是否为可兼容指令或扩充指令,其中该扩增指令为处理器所具备指令集相同架构的新指令集或扩充指令集中的指令。若判断该待执行指令为扩增指令时,转换该待执行指令为由兼容指令序列所构筑的模拟程序,并通过执行该模拟程序来模拟该待执行指令的执行结果。

7.基于上述,本发明实施例所述的模拟装置及其方法利用监测器来判断应用程序中的待执行指令是否为处理器的可兼容指令或是扩增指令。并且在此待执行指令经判断为扩增指令时,将此待执行指令转换为由兼容指令序列所构筑的模拟程序,随后执行该模拟程序来模拟该待执行指令的执行结果,因此本发明能在略为变动旧版处理器的硬件结构下,于旧版处理器上正确执行新指令集或扩增指令集中的扩增指令,以解决处理器指令集的兼容性问题,亦可延长使用此模拟装置的电子设备的使用年限。

附图说明

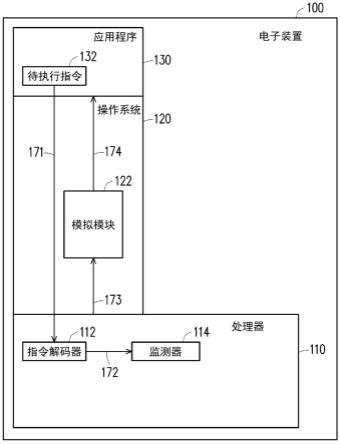

8.图1是依照本发明一实施例的一种电子装置以及位于电子装置中的指令模拟装置

示意图。

9.图2a是依照本发明另一实施例的一种电子装置以及位于电子装置中的指令模拟装置示意图。

10.图2b是依照本发明再一实施例的一种电子装置以及位于电子装置中的指令模拟装置示意图。

11.图3是本发明一实施例的专用硬件的架构图。

12.图4a是依照本发明一实施例的电子装置中处理器的详细结构图。

13.图4b是依照本发明另一实施例的电子装置中处理器的详细结构图。

14.图5a是依照本发明一实施例的模拟模块针对扩增指令执行转换的示意图。

15.图5b是依照本发明另一实施例的模拟模块针对扩增指令执行转换的示意图。

16.图6a/6b是依照本发明一实施例的模拟程序示意图。

17.图7是依照本发明实施例的模拟方法的流程图。

18.图8是依照本发明实施例的转换方法的流程图。

19.其中,附图中符号的简单说明如下:

20.100:电子装置;110:处理器;120:操作系统;130:应用程序;132:待执行指令;112:指令解码器;1122:指令解析单元;1124:微指令序列调用单元;114:监测器;116:专用硬件;116a:处理器当前状态指针寄存器;116b:转换信息指针寄存器;116c:模拟执行结果指针寄存器;116d:私有寄存器;116e:模拟寄存器文件;116f:目的寄存器文件;122:模拟模块;124:保存区域;1242:处理器状态保存区域;1244:转换信息保存区域;1246:模拟执行结果保存区域;160:执行器;160:重命名单元;1604:保留站;1606:执行单元;1608:访存单元;171、172、173、174、175、 176:箭头;280:转换缓存器;410:转换后备缓冲器;420:指令快取;430:分支预测器;440:重新排序缓存区;4402:指令提交单元;4404:微指令缓存区;450:微码存储器;460:微码控制单元;470:微指令序列储存单元;702a、702b:控制单元;704a、704b:扩增指令至模拟程序转换表; 7042a、7042b:扩增指令标签;70422a、70422b:命中扩增指令标签的模拟程序序列指针;7044a、7044b:模拟程序序列指针;706a、706b:模拟程序序列表;7062a、7062b:模拟程序序列;70622a、70622b:命中扩增指令标签所需的模拟程序;708a、708b:虚线箭头;s702、s704、s706、 s708、s710、s712、s714、s716:步骤;s802、s804、s806、s808、s810、 s812、s814、s816:步骤。

具体实施方式

21.本说明书及权利要求书中包含某些术语与专有名词定义如下:

22.可兼容指令:是指相对于某一系列或型号的处理器而言属于原生指令 (native instruction)、或可辨识且解译为原生指令且执行的指令。

23.非兼容指令:是指相对于某一系列或型号处理器目前所具备指令集架构而言为同一类型但属于新指令集或扩充指令集里所以无法正确识别的指令、错误的指令、或与该处理器属于不同指令集架构的指令等三种类型的指令。

24.扩增指令:是指非兼容指令中,相对于某一系列或型号处理器目前所具备指令集架构而言为同一类型但属于新指令集或扩充指令集里所以无法正确识别的指令。举例来说,相对于pentium m处理器而言,avx/avx-512中的指令(例如vaddsd或vaddpd)即是扩增

指令。

25.不可转换指令:是指非兼容指令中的错误指令、或与该处理器属于不同指令集架构的指令(例如对x86处理器而言,arm指令集架构或risc指令集架构中的指令即是不同指令集架构的指令)两种类型的指令。

26.兼容指令序列:是指由至少一条处理器原生指令或可兼容指令所组成的指令序列,该兼容指令序列的执行结果与一扩增指令的执行结果相同。

27.模拟程序:是指将扩增指令转换成由一个由处理器的原生指令或可兼容指令组成的兼容指令序列所构筑的程序,并可由处理器所运行以模拟该扩增指令的执行结果。

28.即时模拟模式:是指当处理器目前所执行的待执行指令为扩增指令时,将该扩增指令转换为由兼容指令序列所构筑的模拟程序,随后并执行该模拟程序以模拟该扩增指令执行结果的过程。传送该待执行指令至处理器执行的应用程序不会感知该即时模拟模式的存在。

29.此处应强调的是,上述可兼容指令、非兼容指令、扩增指令、不可转换指令、兼容指令序列、模拟程序等皆是针对某一系列或型号的处理器而言。举例来说,该系列或型号的处理器可为具备例如arm cortex系列指令集的精简指令集运算(reduced instruction set computing,risc)、intel/amd公司的 x86指令集的复杂指令集运算(complex instruction set computing,cisc) 等指令集的处理器、支持mips(microprocessor without interlocked pipelinestages)或risc-v(risc-five)指令集架构的处理器、能同时支持arm与x86 指令集架构的处理器、或是具备risc/cisc之外的其他指令集架构的处理器,本发明在处理器所支持的指令集架构的类型上并不做特别限定。本领域技术人员应可理解,集成电路制造商可能会依其需求调整处理器所支持的指令集架构的内容,本发明对此并不做任何限制。

30.关于上述自定义名词应说明的是,结合本发明的技术思想,本领域技术人员可自行定义不同的技术名词,但是应区分的是上述自定义名词应从技术实现功能的角度出发理解,而不应以名词名称作区分,本发明并不限制与此。本领域技术人员应可理解,集成电路制造商可能会用不同的名词来定义某一特定的概念和/或称呼某一特定的组件。本说明书及权利要求并不以名称的差异来作为区分的方式,而是以在功能上的差异来作为区分的准则。在通篇说明书及权利要求当中所提及的“包含”及“包括”一词为开放式的用语,故应解释成“包含但不仅限定于”。此外,“耦接”一词在本说明书中包含任何直接及间接的电性连接手段。因此,若文中描述一第一装置耦接至一第二装置,则代表该第一装置可直接电性连接至该第二装置,或经由其它装置或连接手段而间接地电性连接至该第二装置。本领域技术人员应知,上述叙述的变化皆不脱离本发明精神,且应包含于本发明权利要求书内。

31.图1是依照本发明一实施例的一种电子装置100以及位于电子装置100中的模拟装置的示意图。模拟装置应用于具备处理器的电子装置100中。电子装置100例如是平板电脑、智能手机、计算机、服务器

…

等消费性电子装置。

32.请继续参照图1,电子装置100具备处理器110,且处理器110用以运行操作系统120以及应用程序130。操作系统120运行于处理器110之上,用以统整各个应用程序130的运行。应用程序130运行于操作系统120之上,并通过操作系统120使用处理器110及其它硬件(图1未示出,比如硬盘、网卡等等) 提供的各种功能。于电子装置100开机时,可利用基本输入输

出系统(bios) 进行自我检查与初始化,随后通过处理器110运行操作系统120以及用于驱动各个主要元件的驱动器或驱动软件。应用程序130由众多指令组成,这些指令通过处理器110执行来实现应用程序。详细来说,当将应用程序130所指示的待执行指令132从储存介质(例如比如硬盘,未绘示)被读取且储存到电子装置100的动态随机存取存储器(例如系统内存,未绘示)后,再由处理器110依程序顺序执行待执行指令132。当处理器110执行待执行指令132时,指令解码器112分析并产生上述待执行指令132的格式信息(例如将指令切割为各项不同功能的栏位)随后依据格式信息执行待执行指令132的解码操作。另一方面,监测器则114依据指令解码器112所产生的格式信息以判断待执行指令 132是否为可兼容指令(例如是原生指令或可兼容指令)或是扩增指令(如图1 箭头172所示)。若该待执行指令132为可兼容指令时,经由该处理器110执行该待执行指令132并返回结果至应用程序130(图示未绘示)。可兼容指令的执行操作为本领域技术人员的已知技术,本说明书不详细描述。另一方面,当处理器110所执行的待执行指令132被监测器114判定为扩增指令时,则将该待执行指令132当作参数调用模拟模块122(如图1箭头173所示)。模拟模块122转换该待执行指令132(目前为扩增指令)为由兼容指令序列所构筑的模拟程序,并于执行模拟程序里的兼容指令序列来模拟该扩增指令的执行结果后,最后返回该执行结果至应用程序130(如图1箭头174所示)。另一方面,当处理器110所执行的待执行指令132无法为指令解码器112所辨识与解译,而且被监测器114判定为不可转换指令时,则处理器110将报告错误或执行异常至应用程序130(图示未绘示)。关于如何处理上述不可转换指令,应为本领域技术人员的已知技术且不属本发明解决的重点,此处不赘述。模拟模块 122被调用后将读取此待执行指令132(目前为扩增指令),并判断是否能找到对应此扩增指令的模拟程序。模拟模块122通过查询模拟程序列表,并尝试从中找到对应于该扩增程序的模拟程序,其中模拟程序列表为由处理器设计者事先针对每个扩增指令所指示的操作,利用可兼容指令编辑成兼容指令序列后,再据以构筑为模拟程序而组成的表格,而模拟程序列表的搜寻可经由数据库搜寻、地址查找等方式实现。当此扩增指令对应的模拟程序是模拟程序列表的其中一个时,模拟模块122先将其调用出来,随后再执行此模拟程序以产生模拟执行结果后,结束模拟模块112的调用并将执行结果回传给应用程序130。另一方面,若模拟模块122里的模拟程序列表找不到对应于此扩增指令所对应的模拟程序时,模拟模块122将会提供失败结果且通知处理器 110后结束调用过程。应注意的是,模拟模块122是在处理器110执行到由应用程序130而来的待执行指令132、且该待执行指令132是扩增指令时被调用,并在执行对应于扩增指令的模拟程序且产生模拟执行结果后中止运作,因此对应用程序130而言并不会感知模拟模块122对扩增指令的转换与模拟程序的执行过程(整个模拟模块122的运作过程就是即时模拟模式开启的期间),亦即模拟模块122执行的所有操作对应用程序130是透明的。至于模拟模块122 调用模拟程序、以及执行模拟程序的方式将在后文做更详尽的描述。

33.图1的处理器110可以是一核或多核的中央处理器单元(centralprocessing unit,cpu)、微处理器(micro-processor)、或是其他可程序化的处理单元(processing unit)、数字信号处理器(digital signal processor,dsp)、可程序化控制器、专用集成电路(application specific integrated circuits,asic)、可程序化逻辑装置(programmable logic device,pld)或其他类似装置。此外,上述应用程序130对应的待执行指令132是指由应用程序130开发商依据中/高阶程序语言(例如c语言/c 语言/c#语言、

java语言、python语言

…

等)和/ 或低级语言(比如组合语言)所编写的,并使用编译器(compiler)对源码进行编译后,生成可以被处理器110执行的可执行代码(例如机器码或二进制代码),因此,如图1所示待执行指令132经箭头171传递至处理器110执行的是将中/高阶程序语言撰写的程序进行编译与连结处理后的机器码(machinecode)或机器指令。本领域技术人员应理解的是,为了图示绘示和方便说明,上述待执行指令132即是可由处理器识别并执行的机器指令,且在本说明书实施例和权利要求中就不再区分上述待执行指令132的中/高阶程序语言指令与机器指令的差异。

34.图1的监测器114为配置在处理器110内部,并由硬件模块实现。但是需要说明的是,上述监测器114判断上述待执行指令132是否为可兼容指令或为扩增指令的操作,可依据本领域技术人员的设计需求而采用其他电路结构设计或是相应的固件/软件程序自行配置而实现此判断功能。举例来说,上述监测器114可通过驱动更新的方式实现。假设希望让某个旧款处理器来支持新版指令集,因为旧版处理器没有包含类似于监测器114的硬件,因此不仅无法解译新版指令集里的指令,也无法通过设置模拟旗标ef的方式来呼叫模拟模块122协助将扩增指令转换为模拟程序并执行等操作。然而,如果把监测器114的功能编译为软件程序码且成为驱动程序(driver)的一部分后,当旧款处理器引发未定义指令例外(invalid opcode,例如#ud)时,可在获知此例外后经由#ud对应的中断服务程序利用系统呼叫的方式调用监测器114软件(例如写成软件程序码的监测器114可成为回调函数(callback function)供操作系统120调用),并在监测器114判断目前的待执行指令132为扩增指令所以需要转换协助时,由模拟模块122协助调用对应于该扩增指令的模拟程序,随后再执行该模拟程序后再回传执行结果。至于包含监测器114的驱动程序,可以通过实时更新(live update)的方式来进行,而处理器设计者可以在利用旧版处理器原生指令编译好每个扩增指令所对应的模拟程序后,随即通知旧版处理器的使用者经由实时更新处理器驱动程序的途径,让旧版处理器具备支持新指令集/扩充指令集中的能力。总的来说,只要是能实现判断待执行指令 132是否为可兼容指令或为扩增指令的任何任一单元模块、软件程序、硬件单元、或是软/硬件的组合等和/或软件程序,都应该认为是上述监测器114的相应变形,本发明对此不做限制。

35.在一实施例中,电子装置100开机后,操作系统120即开启即时模拟模式功能并于电子装置的储存器中设置用于储存处理器状态、转换/模拟执行过程所需的各项保存区域。也就是说,当处理器110所执行的待执行指令132被监测器114判断为扩增指令时,由于电子装置100已设置相应的保存区域,因此可以直接调用模拟模块122以进行转换该扩增指令并执行模拟程序来产生执行结果。然而,本领域技术人员可根据设计需求自行设计开启即时转换模式来调用模拟模块122的时机和判断条件,例如在监测器114判断待执行指令 132为扩增指令时设置一标志信号并相应开启即时转换模式功能,因此在一实施例中,可在调用模拟模块122前先判断该标志信号是否被设置。在另一实施例中,先判断欲调用模拟模块122的应用程序130是否为操作系统120所认定合法程序,若是才允许读取至驱动程序码读取密码(password),并在密码比对成功后才能调用模拟模块122。这个密码可储存在处理器110的驱动程序里,因此当处理器110需要调用模拟模块122时,将通过驱动程序取得这个密码以进行比对,并于比对成功后才能调用模拟模块122。在又一实施例中,可以对调用模拟模块122与否进行多重认证(authentication)、或对密码进行加密,以确保待执行指令132

模拟过程的安全性,例如先判断取用密码的应用程序130为操作系统120所认定合法程序后读取加密过的密码,并在正确解密后才能调用模拟模块122。控制即时模拟模式的开启与否(亦即是否允许调用模拟模块122)的好处,在于模拟模块122只有在需要对待执行指令132进行即时模拟时才能被成功调用,因此可以防止非授权使用者入侵模拟模块122、或是对待执行指令132的模拟过程进行未经认证的变更或篡改。应可理解的是,何时允许模拟模块122的调用可根据设计而更改,本发明对此并不做任何限制。还需要解释的是,关于调用模拟模块122后配置相应的保存区域的说明,请参考图2和图4部分说明所述。

36.基于上述说明,假设处理器110具备x86指令集,但因为此x86指令集在制造后就已经确定、或是处理器110的硬件结构无法变更以支持x86新指令集或扩充指令集中的扩增指令,因此扩增指令虽然仍是属于x86指令集结构,但处理器110因硬件结构限制无法识别和正确执行此扩增指令。因此,本发明实施例利用模拟装置的监测器114先行判断应用程序需要执行的指令(亦即,待执行指令132)是否属于处理器110内部x86指令集的可兼容指令或属于x86新指令集/扩充指令集中扩增指令后,再决定后续的处理方式。因此,在本发明实施例中,若x86处理器110所执行的待执行指令132属于x86新指令集/扩充指令集中的x86扩增指令时,则在运用本发明实施例下的x86处理器110便会转换此待执行指令132成为由x86处理器110目前所具备指令集中的x86兼容指令序列所构筑的模拟程序,随后模拟模块122执行该模拟程序来模拟该待执行指令132的执行结果,并返回该执行结果至应用程序130。由此,本发明实施例通过模拟模块122的协助,使得具备较旧版本x86指令集的处理器110能够对新x86指令集或x86扩充指令集中的x86扩增指令进行转换而获得模拟程序(如上所示,模拟程序由x86兼容指令序列所构筑),并且通过执行该模拟程序来模拟该待执行指令132的执行结果。在另一实施例中,处理器110是一具备arm指令集架构的arm处理器,待执行指令132则属于相对于该arm处理器110目前的指令集架构而言,是较新的arm指令集或扩充指令集下的扩增指令,而模拟程序里的arm兼容指令序列是由arm处理器目前指令集下的原生指令或可兼容指令所组成,因此属于arm指令集架构的扩增指令可通过执行该模拟程序来模拟该待执行指令132的执行结果。如上所述,本实施例所述的待执行指令、可兼容指令与扩增指令皆为相同指令集架构的指令,不限定是x86指令集架构(或cisc指令集架构)的指令,亦可为 arm指令集架构(或risc指令集架构)、支持mips或risc-v指令集架构的处理器、或其他指令集架构的指令,本发明在指令集架构的类型上不予限制。值得注意的是,运用本发明的处理器110因为可以用相对较旧的指令集架构来支援相对较新指令集架构的运行,这样不仅可以延长包含旧处理器电子设备的使用年限,也可以让处理器设计者在仅变动少许硬件下让旧处理器支援新指令集或扩充指令集的指令。举例来说,只要在处理器110增加与监测器 114相关的硬件、并在指令解码器112、监测器114、以及专用硬件116

…

等基于模拟扩增指令的需求而增加的硬件之间建立传输信号的连线,再搭配以软件构筑模拟模块122与模拟程序列表即可达到目的,不需要对处理器后续的管线级电路、指令预测分支

…

等部分的结构进行修改,所以也能快速地设计出符合需求的处理器。

37.再者,在一实施例中,模拟模块122储存于电子装置100的基本输出输入系统中,并且在包含处理器110的系统开机时,基本输出输入系统将模拟模块122加载至操作系统120中。在另一实施例中,模拟模块122可设置于处理器110的驱动软件中,并由操作系统120运行后将其加载进系统内存;在又一实施例中,模拟模块122可编译至操作系统120的核心

(kernel)中,并在操作系统120执行后等候调用。在又一实施例中,可以在模拟模块122于转换操作运作期间,通知操作系统120禁止响应其他中断(例如禁止响应其他无关的硬件中断)以使转换作业能在不受干扰下进行。本领域技术人员应知,上述实施例的变化皆不脱离本发明精神,且应包含于本发明权利要求书内。

38.图2a是依照本发明另一实施例的一种电子装置100以及位于电子装置 100中的模拟装置的示意图。电子装置100的模拟装置还可在电子装置100的相关存取介质(如,内存)中配置保存区域124,而保存区域124中至少配置处理器状态保存区域1242、转换信息保存区域1244、模拟执行结果保存区域 1246。处理器状态保存区域1242用以保存处理器110的当前工作环境状态参数,转换信息保存区域1244用以在对扩增指令进行转换以调用所需模拟程序运作时的信息暂存(例如调用模拟程序过程中的比对信息、或是模拟程序列表中指向各模拟程序的指针等),模拟执行结果保存区域1246则用来储存模拟程序运行时的暂时信息(例如在模拟程序中所定义变数的对应储存空间、或执行过程中的暂时数据等)与模拟程序的执行结果。如图2a所示,模拟模块122可以将上述相关状态数据暂存至保存区域124(如箭头175所示),而处理器110亦可从保存区域124读取相应的执行结果(如箭头176所示)。应注意的是,在一实施例中,通过基本输入输出系统从电子装置100的相关存取介质中,取得处理器状态保存区域1242、转换信息保存区域1244、以及模拟执行结果保存区域1246的保存区域124的相关参数(例如各保存区域的大小与基底指针)来进行配置,也就是保存区域124不仅可由操作系统120来配置,本发明对保存区域124的配置方式不予限制。至于保存区域124使用方式将在后文做更详尽的描述。

39.图2b是依照本发明再一实施例的一种电子装置100以及位于电子装置 100中的模拟装置的示意图。本实施例的处理器110还包括一专用硬件116,做为处理器110将扩增指令转换为模拟程序、以及执行模拟程序来产生模拟执行结果所需的相关信息专属的储存空间。专用硬件116的使用方式将在后文做更详尽的描述。

40.图3是本发明一实施例的专用硬件116的架构示意图。请结合图2a、图2b 和图3所示,如图3所示,处理器110的专用硬件116包含处理器当前状态指针寄存器116a、转换信息指针寄存器116b、模拟执行结果指针寄存器116c、私有寄存器116d、以及一个用于映射扩增指令体系结构寄存器的模拟寄存器文件116e,处理器110可基于上述寄存器的指针读取主储存器中保存区域124 的状态数据信息。处理器当前状态指针寄存器116a的地址指向主储存器中用来保存处理器110目前状态的相关信息,如处理器110目前工作环境的各种寄存器状态、或待执行指令132的下一条需执行的指令地址等;转换信息指针寄存器116b的地址亦指向主储存器,但该地址所指示的储存空间用来作为扩增指令在转换过程中所需要的暂时储存空间、或用来储存转换过程所需要的信息,例如扩增指令的格式信息、指向各模拟程序的指针等;模拟执行结果指针寄存器116c的地址亦指向主储存器,但该地址所指示的储存空间用来作为扩增指令对应的模拟程序在执行过程中需要的暂时储存空间、或用来储存执行过程所需要的信息(例如扩增指令的中间执行结果等)、以及模拟程序的执行结果。私有寄存器116d可包含一模拟旗标(emulation flag,ef)与缓存扩增指令的寄存器(皆未绘示)。模拟旗标ef用来表示待执行指令132是否为可被转换/模拟的扩增指令,例如当其值被设置为1时表示目前的待执行指令132 为扩增指令,因此需要调用模拟模块122来执行扩增指令的转换与模拟执行操作。另一方面,私有寄存器116d中用来缓存待执行指令132的寄存

器则是做为呼叫模拟模块122时(此时的待执行指令132是扩增指令),将待执行指令 132当作参数提供给模拟模块122的暂时储存空间。模拟寄存器文件 (simulation register file)116e则包含n个(n为大1的自然数)256位寄存器ereg0、 ereg1

…

eregn-1、eregn,该256位寄存器文件支援处理器110特定微操作读写和运算,例如两组256位寄存器可以分别映射一个512位寄存器的高256区域与低256区域,于是处理器110可以通过模拟寄存器文件116e中的256位寄存器堆来映射本身未支持的512位寄存器,如图3利用虚线所示的treg0、treg1

…

tregn-1、tregm(目的寄存器文件(target register file)116f)。关于实现寄存器之间的映射是本领域技术人员的常规应用,本说明书在此并不做详细介绍。此处应说明的是,本说明书中虽采用256位寄存器映射模拟512位寄存器,但并不表示只限制于这两种寄存器之间的模拟。举例来说,在另一实施例中,模拟寄存器文件116e亦可用于其他未被处理器110现有硬件所支持的特定寄存器,例如模拟某特定操作模式专用的基底地址或状态控制寄存器。另一方面,专用硬件116亦可以在处理器110内部所设置的寄存器文件(register file)中,特别指定某些寄存器成为模拟扩增指令执行所需的专用硬件116,本发明对不予限定。

41.图4a是本发明实施例中处理器110的内部结构图,除了前面提过的指令解码器112、监测器114、专用硬件116之外,还包括指令转换后备缓冲器 (lookaside buffer)itlb 410、指令快取420、分支预测器(branch predictor) 430、重新排序(re-order)缓存区440、微码存储器450、微码控制单元460、以及微指令序列储存单元470。指令转换后备缓冲器itlb 410可被用以撷取需执行指令,例如支持应用程序所指示功能的指令(亦即待执行指令132)。指令快取420用以通过页表快取或转址旁路快取的方式从指令转换后备缓冲器410中获得需要执行的指令。分支预测器430与指令快取420协同运作,分支预测器430预测指令是否会产生分支,并在预测有分支产生时将分支指令存入指令快取420。如前所述,私有寄存器116d中包含一个模拟旗标ef以指示目前的待执行指令132是否为可模拟的扩增指令,以及一个可缓存待执行指令132的储存空间,模拟旗标ef的运用与扩增指令的储存后文会再详述。再者,执行器160还包含重命名单元(renaming unit)1602、保留站(reservationstation)1604、执行单元1606、以及访存单元1608。指令解码器112还包含一指令解析单元1122与微指令序列调用单元1124,其中指令解析单元1122与微指令序列调用单元1124以及监测器114耦接,监测器114则进一步与私有寄存器116d,而微指令序列调用单元1124则与微指令序列储存单元470耦接。

42.当待执行指令132从指令快取420送往监测器140时,指令解码器112中的指令解析单元1122会先对待执行指令132进行格式分析,从而切割出前缀 (prefix,pre)、转义码(escape opcode,eop)、操作码(main opcode,mop) 以及其它译码(other decoding information,odi)等格式信息后,再将格式信息(亦即pre/eop/mop/odi)同时送往微指令序列调用单元1124与监测器114。指令解码器中112的微指令序列调用单元1124随后对格式信息进行解码以得知待执行指令132所指示的操作,并据以从微指令序列储存单元470调用对应微指令(μop)序列,并结合待执行指令132的运算元(operands)相关信息(例如运算元的寻址信息)以产生微指令指令后送往执行器160(例如送往重命名单元1602)。该微指令序列在运算元的重命名处理后,同时被送往保留站1604 与重新排序缓存区440,保留站1604根据上述微指令序列的类型发送给执行单元166或访存单元168做进一步处理。重新排序缓

存区440包含一指令提交单元(retire unit)4402与微指令缓存区4404,其中微指令缓存区4404包含多个指令条目(entry),用以储存由重命名单元1602传送过来的微指令序列,而指令提交单元4402则在微指令执行完毕后,由执行单元1606或访存单元1608通知重新排序缓冲去440依据原始的程序顺序进行提交(retire)。

43.接下来说明当处理器110所执行的待执行指令132为扩增指令的处理情形。监测器114依据格式信息(指令解析单元1122对待执行指令132进行格式分析而获得的pre/eop/mop/odi)来判断该待执行指令132是否为扩增指令,若该待执行指令132为扩增指令则设置模拟旗标ef,并指示私有寄存器116d 储存待执行指令132。另一方面,如前所述,当待执行指令132为扩增指令时,微指令序列调用单元1124将无法正确解译格式信息所以将产生一空指令(nooperation performed,nop)。因此当在该空指令为重新排序缓存区440中最老的指令时,指令提交单元4402会去检查模拟旗标ef并发现模拟旗标ef已被设置,所以指令提交单元4402会去引发调用模拟模块122的中断服务程序以调用模拟模块122来进行扩增指令的转换与模拟。对应于扩增指令的模拟程序调用,将在后文利用图5a/图5b来说明,至于模拟程序则以图6a/图6b 的实例做说明。在一实施例中,用来调用模拟模块122的中断服务程序,可以修改调用指令解译错误时所调用的对应于#ud的中断服务程序、或自行定义令一个中断服务程序来达成。例如引发#ud的空指令被提交(retire)且调用对应于#ud的中断服务程序时,可以修改对应#ud中断服务程序先去检查模拟旗标ef的状态,并于模拟旗标ef被设置时通过操作系统120向模拟模块 122提出转换请求、或是在模拟旗标ef未被设置时调用已知用以处理指令解译错误的例外处理程序。在一实施例中,可以将已知#ud中断服务程序与本发明通过#ud来调用模拟模块122的模拟模式专属#ud中断服务程序分开,并依据模拟旗标ef被设置的状态分别调用,例如模拟旗标ef未被设置时调用已知的#ud中断服务程序,但在模拟旗标ef被设置时调用呼叫模拟模块 122的模拟模式专属#ud中断服务程序。在另一实施例中,当引发指令解译错误的空指令被提交时,提交单元4402将先判断模拟旗标ef的状态并在模拟旗标ef被设置时通过自行定义的中断服务程序(例如由处理器110设计者在中断向量表的自订编号中挑选一个向量编号(如20h),并自行定义一中断向量#ne(ne为non-support instruction emulator的缩写)去经由操作系统120呼叫模拟模块122。值得注意的是,中断服务程序呼叫模拟模块122时必须将待执行指令132(目前为扩增指令)当作参数传给模拟模块122,例如将私有寄存器116d中储存待执行指令132的寄存器地址指针传送给模拟模块122。模拟模块122随后进行扩增指令的转换并执行对应的模拟程序,并将模拟程序的执行结果储存于模拟执行结果保存区域1246后便停止模拟模块122的调用(也就是退出即时模拟模式)。另一方面,当被判定为扩增指令的待执行指令132 的模拟执行结果被处理器110从模拟模块122读回时,还需要清除私有寄存器 116d中的模拟旗标ef,表示目前待执行指令132的模拟操作已完成。因此若后续又有待执行指令132是扩增指令时,将再重新设置模拟旗标ef并重新调用模拟模块122且启动扩增指令对应的模拟程序的转换与执行操作。

44.在一实施例中,调用模拟模块122所使用的中断服务程序(亦即对应#ud 中断服务程序或自行定义的中断服务程序#ne),可以是储存在微码唯读存储器450中的微码并由微码控制单元360调用(微码控制单元360可用状态机与组合逻辑电路构筑);在另一实施例中,可以将调用中断服务程序的操作独立架构为一个中断控制单元或模组(例如risc/

risc-v架构下的中断控制单元);在又一实施例中,可通过储存在微码存储器450中的微码所指示的地址去调用。在又一实施例中,可以通过一中断预处理单元(例如将微码控制单元460架构为中断预处理单元、或是将risc/risc-v架构下的中断控制单元改为中断预处理单元),以在对应于待执行指令132(目前扩增指令)的空指令被提交时,去呼叫对应的中断服务程序以调用模拟模块122。在一实施例中,通过中断请求调用模拟模块122以转换扩增指令的方式,可以经由系统呼叫 (system call)来呼叫操作系统120执行模拟模块122,例如把模拟模块122做为一回调函数(callback function),待执行指令132(或格式信息)则被当成参数传给该回调函数,并于回调函数处理完待执行指令132对应的模拟程序的转换与执行后将执行结果储存于模拟执行结果保存区域1246通知处理器110取回。此外,模拟模块122亦可通过内部中断(internal interrupt)或是陷阱(trap)来调用,例如处理器110设计者自行定义一中断向量#ne,并由此系统呼叫以进入操作系统的核心(kernel)去调用模拟模块122,本领域技术人应知这部分的技术细节故不再赘述。在又一实施例中,重新排序缓存区440的每个指令条目 (entry)还包含一模拟标识字段(未显示),用于保存微指令中的模拟标识ef。于是当待执行指令132是扩增指令导致指令解码器112中的微指令序列调用单元1124无法进行解译而产生一空指令时,此时的监测器114会判定待执行指令132是扩增指令所以设置模拟旗标ef,所以被设置的模拟旗标ef将跟随这个空指令被送往重命名单元162与重新排序缓存区440。是以,当重新排序缓冲区440的指令提交单元4402提交这条空指令时,会发现跟随这条空指令的模拟旗标ef被设置,所以将调用对应的中断服务程序来呼叫模拟模块122,以对待执行指令132(亦为扩增指令)进行转换为模拟程序与执行。值得注意的是,如果空指令所伴随的模拟旗标ef并未被设置时,指令提交单元4402将通过中断向量#ud呼叫对应的中断服务程序,来处理这个指令解译错误的例外状况,此为已知的例外处理方式故不再赘述。

45.在一实施例中,处理器110可还包含一转换缓存器280,用以与与微指令序列调用单元1124以及监测器114耦接,并在模拟旗标ef被设置时(例如设定其值为1)储存由微指令序列调用单元1124所送来的模拟程序的微指令(μop) 序列,作为往后遇到相同扩增指令时直接从转换缓存器280取出使用,而不用重复对该条扩增指令执行转换与模拟的操作。是以,当待执行指令132为扩增指令,且该扩增指令所对应模拟程序的微程序序列已储存在转换缓存器 280时,转换缓存器280将发送一清除(clear)信号至私有寄存器116d以使目前私有寄存器中的模拟旗标ef与待执行指令132被清除或失效(disable),表示目前的模拟程序微程序序列已取得,不用再去呼叫模拟模块122行转换/模拟操作。此外,为方便辨识每个模拟程序所对应的扩增指令,可以将扩增指令的指令格式信息(例如pre/eop/mop/odi)作为对应模拟程序的标签(tag)。因此当模拟旗标ef为1时,可以利用扩增指令的指令格式信息(例如 pre/eop/mop/odi)与转换缓存器280的标签进行比对,并在命中(hit)后将相关的模拟程序微指令序列调出来。值得注意的是,储存于转换缓存器280的微指令序列只会在模拟旗标ef被设置时才允许对其内容进行访存或变更,在模拟旗标ef未被设置时则保持其值不变,因此储存于转换缓存器280的模拟程序不会因处理器110切换工作环境(context switch)去执行其他程序而被清除、重置、覆写、或做任何变更。因此,若处理器110若再遇到相同的需模拟扩增指令时,便可从储存于转换缓存器280中取得所需的模拟程序,不需要再去调用模拟模块122并进行重复的转换与模拟执行操作。在又一实施例中,可以将转换缓存

器280设置在多核心处理器的非核心区域(uncore region) 中,例如储存在l3-快取(l3-cache内,这样可以让已执行过模拟操作的模拟程序与其他处理器核心共享。应注意的是,储存于多核心处理器非核心区域的模拟程序应通过宏指令(macroinstruction)的样态来储存,于是需要模拟程序进行模拟操作的处理器核心可对模拟程序进行解码并产生所需的微指令序列后,再送往后续的管线级电路(例如执行器160)去执行。

46.在一实施例中,如图4b所示的处理器110,转换缓存器280里的微指令序列与模拟旗标ef的值将提供给微指令调用单元1124参考。在图4b的处理器 110结构下,当目前的待执行指令132是一条扩增指令而且该条扩增指令以往曾被模拟执行过,所以相关的模拟程序微指令序列会被储存在转换缓存器 280中。如果这条扩增指令再次成为待执行指令132时,由于指令解码器112 的微指令调用单元1124还是无法对其正确解译,但监测器114仍能判定待执行指令132扩增指令因此设置模拟旗标ef。所以此时的微指令调用单元1124 可在对待执行指令132无法正确解码后,随即检查模拟旗标ef并发现已被设置,接下来便去转换缓存器280进行查询,并在转换缓存器280中发现对应该条扩增指令的模拟程序微指令序列,随后可把待执行指令132的运算元相关信息(例如寻址等信息,目前待执行指令132与先前模拟时的运算元可能不同) 与该模拟程序微指令序列相结合,来产生对应于目前待执行指令的微指令序列后再送往后续的执行器160,随后清除私有寄存器116d中的模拟旗标ef与缓存扩增指令的寄存器。当然,若微指令调用单元1124在模拟旗标ef已被设置并前往转换缓存器280进行查询后,却未发现对应该条扩增指令的模拟程序微指令序列时,接下来仍会发出空指令并送给重命名单元1602,并在这条空指令被提交时再通过对应的中断服务程序对该扩增指令进行转换与模拟,这些操作已于前面说明过故不再赘述。

47.值得注意的是,由于扩增指令一般是具备固定格式内容的已知公开信息,因此处理器110设计者可以在分析扩增指令的格式信息后,利用组合逻辑电路或其他类似的设计方式来构筑指令解析单元1122以进行扩增指令的判断,本发明对此不作限制。

48.在一实施例中,可以将图4a或图4b中的指令解码器112所包含的指令解析单元1122复制一份给监测器114,而这个复制的指令解析单元1122仍接收待执行指令132并专门为监测器114判断待执行指令132是否为扩增指令。在这个结构下,由于指令解码器112与监测器114将成为两个分开的模组(并共同接收待执行指令132),因此在设计上也可以用两个独立模组构筑于处理器110 中。

49.接下来利用图5a来说明模拟模块122针对扩增指令执行转换的示意图。图5a中模拟模块122包括一控制单元702a、扩增指令至模拟程序转换表704a、以及模拟程序序列表706a(此即前文提过的模拟程序列表)。控制单元702a负责模拟模块122对扩增指令的转换操作,以取得对应于扩增指令(也就是待执行指令132)的模拟程序,这部分后面会再详述。扩增指令至模拟程序转换表 704a又包含扩增指令标签7042a与模拟程序序列指针7044a两个部分,分别用来储存扩增指令的格式信息、以及扩增指令对应的模拟程序于模拟程序序列表706a中的储存地址。模拟程序序列表706a则储存所有扩增指令的模拟程序序列7062a,并通过模拟程序序列指针7044a而调用。在一实施例中,模拟程序序列表706a中所储存的每个对应于扩增指令的模拟程序序列 7062a,由处理器110设计者针对新指令集或扩增指令集中每个新增加的扩增指令,事先利用由处理器110的可兼容指令(例如原生指令)编辑成可兼容指令序列后,并将这些可兼容指令序列进一步编写成模拟程序。因此,这些模拟程序

便可通过图5a所示的结构而调用,以在对应的扩增指令被执行时(亦即目前的待执行指令132是扩增指令时)产生模拟执行结果。

50.控制单元702a可依据扩增指令的格式信息,包含前缀(pre)、转义码 (eop)、操作码(mop)、以及针对各个扩增指令所需的其他解译需要的信息(odi)等,并与模拟程序转换表704a中的扩增指令标签7042a进行比对,如果比对成功后(也就是扩增指令的格式信息与某个扩增指令标签7042a发生命中(hit)的情形),依据比对成功的扩增指令标签7042a对应的模拟程序序列指针7044a,前往模拟程序序列表706a调用所需的模拟程序。例如,若处理器110传送过来的待执行指令132的信息中,前缀/转换码/操作码/其他解译信息分别为pre_j/eop_j/mop_j/odi_j(j为介于1与n之间的整数),因此控制单元702a将依据此pre_j/eop_j/mop_j/odi_j的扩增指令格式信息对扩增指令标签7042a里的每个扩增指令标签进行比对。如图5a所示,由于该笔扩增指令格式信息已储存在扩增指令至模拟程序转换表704a中因此发生命中(如标号70422a所示),于是可以从命中的扩增指令标签70422a取得对应的模拟程序序列指针70442a(亦即simproj_pointer),接着再利用模拟程序序列指针70442a所指示的地址前往模拟程序序列表706a寻找所需的模拟程序,亦即依据虚线箭头708a所示找到模拟程序序列指针70442a所需的模拟程序 70622a(亦即图5a中经由simproj_pointer所指示的simulation_programj)。最后,控制单元702a将这个模拟程序(也就是simulation_programj)调出后,便完成扩增指令的转换过程。于是模拟模块122可执行模拟程序 simulation_programj,以产生模拟扩增指令(格式信息为 pre_j/eop_j/mop_j/odi_j)的执行结果给处理器110。模拟程序的执行将后文利用图6a/6b的程序范例来说明。

51.在一实施例中,处理器110除了传送扩增指令(或是仅传送扩充指令的格式信息)给模拟模块122之外,还可传送处理器110目前的运行环境信息、以及该扩增指令的运行环境信息等信息给模拟模块122,以判断该扩增指令是否能在处理器110目前的运行状态下执行。举例来说,控制单元702a可在判断该扩增指令无法(或不适合)在处理器110目前运行环境下执行时(例如扩增指令要在保护模式(protected mode)下运行,但目前的处理器却式处于真实模式 (real mode)中),呼叫对应的中断服务程序来通知操作系统120/应用程序130 发生转换/执行异常。在另一实施例中,模拟模块122可仅通过扩增指令的一部分,例如前缀/转义码/操作码(pre/eop/mop)来进行比对以取得模拟程序。

52.应注意的是,在一实施例中,扩增指令转换表704a中的扩增指令标签 7042a可以是对前缀(pre)、转义码(eop)、操作码(mop)、以及其他解译所需信息(odi)做进一步处理后的编码,例如对pre/eop/mop/odi进行加密或哈希(hashing)处理,以对扩增指令的转换过程进行保护,这部分应为本领域技术人员所熟知故不再赘述。在另一实施例中,这些扩增指令以及扩增指令相对应的模拟程序可依据需求而增加、删除、或更新至扩增指令至模拟程序转换表704a与模拟程序序列表706a中。举例来说,可以通过固件更新的方式增加扩增指令至模拟程序转换表704a与模拟程序序列表706a的大小,例如可以在扩增指令至模拟程序转换表704a中增加pre_n 1/eop_n 1/mop_n 1/odi_n 1的扩增指令格式信息与对应的转换指令序列instseqn 1_natinst 1

…

instseqn 1_natinst m(n与m皆为大于1的整数),并以模拟程序指针instseqn 1_pointer则指向与该模拟程序(上述的扩增指令格式信息、模拟程序、以及模拟程序指针皆未显示在图5a中),这两个表可以在修改完毕后,经由固件更新

覆写原先的表格内容。在又一实施例中,对扩增指令至模拟程序转换表704a与模拟程序序列表706a所进行的修改,亦可以与通过实时更新(live update)的方式来进行,本发明对此不做限制。

53.在一实施例中,模拟模块122还可以包括事件处理模组(未显示)。当模拟模块122在转换的过程中发生异常或例外(例如模拟程序不存在、或是目前所转换的扩增指令无法(或不适合)在处理器110目前运行环境下执行)时,将由事件处理模组154将产生异常/例外结果,并将此异常/例外结果通知应用程序 130与操作系统120并进行相应补救步骤,从而避免整个电子装置100因为此异常或例外而发生当机情形。举例来说,该异常/例外结果可为一数字异常标志指令,并返回该数字异常标志指令至应用程序130。在另一实施例中,该应用程序130或是操作系统120可跳过发生异常/例外的指令、显示该指令所指示功能无法执行、或报告错误等。

54.接下来利用图5b来说明模拟模块122针对扩增指令执行转换的另一种实施方式示意图。与图5a实施例相同的是,图5b中模拟模块122也包括一控制单元702b、扩增指令至模拟程序转换表704b、以及模拟程序序列表706b。控制单元702b负责模拟模块122对扩增指令的转换操作,以取得对应于扩增指令(也就是待执行指令132)的模拟程序。扩增指令至模拟程序转换表704b 又包含扩增指令标签7042b与模拟程序序列指针7044b两个部分,分别用来储存扩增指令的格式信息、以及扩增指令对应的模拟程序序列于模拟程序序列表706b中的储存地址。模拟程序序列表706b则储存所有扩增指令的模拟程序序列7062b,并通过模拟程序序列指针7044b而调用。模拟程序序列表 706b中储存每个对应于扩增指令的模拟程序序列7062b,其亦为事先利用由处理器110的可兼容指令(例如原生指令)所编辑的兼容指令序列,并将这些兼容指令序列进一步编写成模拟程序。在又一实施例中,对扩增指令至模拟程序转换表704b与模拟程序序列表706b所进行的修改,亦可以与通过实时更新(live update)的方式来进行,本发明对此不做限制。

55.与图5a不同的是,图5b的实施例让扩增指令不只对应一个模拟程序,例如待执行指令132的格式信息前缀/转换码/操作码/其他解译信息分别为 pre_j/eop_j/mop_j/odi_j时,可能在扩增指令至模拟程序转换表704a对应到三个扩增指令标签与模拟程序指针,例如图5b中的扩增指令标签 pre_j/eop_j/mop_j/odi_j-1、pre_j/eop_j/mop_j/odi_j-2、 pre_j/eop_j/mop_j/odi_j-3,其模拟程序指针分别为simproj-1_pointer、 simproj-2_pointer、simproj-3_pointer。这样做的原因,举例来说,在于扩增指令往往需要支援不同长度的运算元,因此微指令序列可能要包含一些判断或循环,而这些步骤可能在处理器110的执行上产生分支,甚至影响处理器的执行效率。是以,若能事先对运算元长度进行判断,并在除去判断与循环步骤后再据以建立微指令序列,或许能减少或避免在处理器管线级的指令流上产生指令分支并提升处理器110的执行效率。举例来说,如果扩增指令标签pre_j/eop_j/mop_j/odi_j-1、pre_j/eop_j/mop_j/odi_j-2、 pre_j/eop_j/mop_j/odi_j-3分别对应扩增指令的运算元为128位、256位、 512位时,而控制单元702b可以在分析扩增指令的格式信息(例如odi)后,进而得知目前的扩增指令的运算元长度(例如是运算元的最大长度是512位,所以调用pre_j/eop_j/mop_j/odi_j-3所指示的模拟程序),于是就可以更精确的调所需的模拟程序。应注意的是,上述的例子仅作说明之用,本领域技术人员皆知,扩增指令还可以运用运算元长度以外的方式来切割需的模拟程序,本发明对此不作限制。

56.接下来对图5b的运作方式作说明。控制单元702b可依据扩增指令的格式信息,包含前缀(pre)、转义码(eop)、操作码(mop)、以及针对各个扩增指令所需的其他解译需要的信息(odi)等,并与模拟程序转换表704b 中的扩增指令标签7042a进行比对,如果比对成功后(也就是扩增指令的格式信息与某个扩增指令标签7042b发生命中(hit)的情形),依据比对成功的扩增指令标签7042b对应的模拟程序序列指针7044b,前往模拟程序序列表706b 调用所需的模拟程序7062b。举例来说,如果处理器110传送过来的待执行指令132的信息中,前缀/转换码/操作码/其他解译信息分别为 pre_j/eop_j/mop_j/odi_j(j为介于1与n之间的整数),但控制单元702b进一步分析pre_j/eop_j/mop_j/odi_j后(例如分析运算元长度),发现 pre_j/eop_j/mop_j/odi_j应该是pre_j/eop_j/mop_j/odi_j-1,因此与模拟程序转换表704a中pre_j/eop_j/mop_j/odi_j-1比对成功(如标号70422b 所示),因此控制单元702b从扩增指令标签70422b取得对应的模拟程序序列指针70442b(亦即simproj-1_pointer),接着再利用模拟程序序列指针70442b 所指示的地址前往模拟程序序列表706b寻找所需的模拟程序,亦即依据虚线箭头708b所示找到模拟程序序列指针70442b所需的模拟程序70622b,亦即图5b中的simulation_programj-1。最后,控制单元702b将这个模拟程序(也就是由模拟程序序列指针70442b所指示的simulation_programj-1)调出后,再由模拟模块122再执行以产生执行结果提供给处理器110。

57.在一实施例中,处理器110除了传送扩增指令(或是仅传送扩充指令的格式信息)给控制单元702b之外,还可传送处理器110目前的运行环境信息、以及该扩增指令的运行环境信息等信息传给控制单元702b,以判断该扩增指令是否能在处理器110目前的运行状态下执行,这部分与图5a的操作方式相同故不再赘述。此外,在一实施例中,扩增指令转换表704b中的扩增指令标签 7042可以是对前缀(pre)、转义码(eop)、操作码(mop)、以及其他解译所需信息(odi)做进一步处理后的编码,例如对pre/eop/mop/odi进行加密或哈希(hashing)处理,以对扩增指令的转换过程进行保护,这部分应为本领域技术人员所熟知故不再赘述。在另一实施例中,这些扩增指令以及扩增指令相对应的模拟程序可依据需求而增加、删除、或更新至扩增指令至模拟程序转换表704b与模拟程序序列表706b中。这部分与图5a的操作方式相同故不再赘述。

58.应注意的是,不论是图5a或图5b的对扩增指令的转换操作,都可经由转换信息指针寄存器116b所指示的地址,以将转换操作过程所产生的暂时信息(例如在比对扩增指令标签7042a/7042b比对过程中的暂时信息、或是图 5a/5b示例的所有表格与指针、以及控制单元702a/702b运行时所需的程序码等)储存到主储存器的转换信息保存区域1244,而所调用到的模拟程序也可暂时储存于转换信息保存区域1244,随后再等候处理器110执行(例如将指向模拟程序序列指针(如是simproj-1_pointer)传送给处理器110)。在一实施例中,可以将所有被调用过的模拟程序进行标记或记录被调用次数,作为模拟模块122或处理器设计者参考之用。

59.在另一实施例中,可将图5a/图5b的转换操作写成另一个转换模组(未显示),其可设置于模拟模块122中、或做为一回调函数(callback function)供模拟模块122调用(例如通过系统呼叫),因此处理器110可能会因为工作环境的切换而需要变更处理器110状态寄存器的内容。基于这个需求,可以在处理器当前状态保存区域1242设置一状态堆叠(stack,未显示)来储存处理器110 的工作环境信息。举例来说,当处理器110进入模拟模块122时,

会将处理器 110目前的工作环境信息储存在状态堆叠的第一层中,随后当模拟模块122于调用该转换模组时,模拟模块122也会先将目前的运行环境参数储存于状态堆叠的第二层(位于第一层之上),然后再切换至转换模组去执行扩增指令的转换操作。当转换模组完成扩增指令的转换工作并成功调用对应的模拟程序时,模拟模块122需要恢复至调用转换模组之前的工作环境时,便可从状态堆叠第二层调用先前储存的工作环境参数以执行工作环境的恢复操作。最后,当模拟模组122完成扩增指令对应模拟程序的执行后,可读出储存于状态堆叠第一层的工作环境参数并恢复为执行待执行指令132时的工作环境。本发明虽通过堆叠来说明工作环境的储存方式,但本领域技术人员应知,任何可以用来储存工作环境参数的运作方式都属于不脱离本发明精神的等效替换,且应涵盖于本发明权利要求书中。

60.最后,当模拟模块122在执行模拟程序时,可以将模拟过程中所产生的暂时信息,包含在模拟程序所定义数据结构、变数、执行过程中的暂时数据

…

等,经由模拟执行结果指针寄存器116c的指示储存到主储存器的模拟执行结果保存区域1246,而模拟程序的执行结果也可以保留在模拟执行结果保存区域1246,以提供处理器110或给后续扩增指令参考。这样做的好处在于,举例来说,若有应用程序130传送连续的扩增指令给处理器执行,而且这些扩增指令在执行上有相依性(dependency)时,因此若前一个(或一些)扩增指令的模拟程序的执行结果能直接保留给后续扩增指令参考,将可提升扩增指令的模拟效率。值得注意的是,由于保存区域124中的处理器状态保存区域1242、转换信息保存区域1244、模拟执行结果保存区域1246可在模拟模块122被调用期间(也就是即时模拟模式开启的期间)进行访存,因此所有储存在保存区域124里的信息都可被模拟模块122自由运用,本领域技术人员可基于不同应用对此进行调整,但本发明对此不做限制。在一实施例中,可以将执行模拟程序的部分另外边译成一个执行模组(未显示),并在解译模组调用到模拟程序后调用这个执行模组来执行模拟程序。至于执行模组的编写调用都属于本领域技术人员所熟知的部分,故不再详述。

61.接下来利用图6a/6b所例示的模拟程序,来说明对应于扩增指令的模拟程序的内容。图6a/6b是模拟avx-512指令集(avx是advanced vector extensions的缩写)中的vaddsd指令,由于vaddsd无法被指令解码器112 正确解译但却能被监测器114所辨识,因此模拟旗标ef将监测器114所设置,随后通过对应的中断服务程序而调用模拟模块122,而这条vaddsd指令也作为参数提供予模拟模块122。avx-512规格对vaddsd定义的内容为:

62.vaddsd xmm0{k1}{z},xmm1,xmm2

63.vaddsd所定义的操作为:将双精准浮点数(double-precision floating-pointvalue)来源运算元xmm2的低64位与来源运算元xmm1相加,并将结果储存于目的运算元xmm0中。此外,vaddsd还支持罩遮(masking)操作,并在 {k1}=1时执行上述相加操作(k1为8-bit罩遮寄存器的第2个位,亦即bit 0~bit7中的bit 1)。{z}则用来判断最终结果要清零或与原有结果进行合并(merge)。关于vaddsd的其他规定与说明请参阅avx-512规格书,本发明不予赘述。

64.图6a/6b模拟指令emulate_addsd_512的基本信息略述如下:

65.(1)inst:为一数据结构,包含所有可以从机器码(例如已判定为扩增指令的待执行指令132)中解码出来的信息,其中:

66.a.dst:为解码出来的目的寄存器编码;

67.b.src*:指示解码出来的操作数寄存器编码;

68.c.evex.b:表示当前指令支持的操作模式;

69.(2)max_vl:表示当前的向量类寄存器的最大长度,对于avx-512规格而言, max_vl=512;

70.(3)processorcontext:为中断(例如#ne中断)发生时处理器保存的机器状态;

71.(4)dedicatehw:专用硬件116的硬件资源在模拟中的数据结构。

72.接下来略述图6a/6b程序码的内容:

73.(1)第3-6行:对模拟需要用到的储存位置进行初始化;

74.(2)第7-12行:判断当前dst的寄存器编码属于需要模拟的范畴是否在专用硬件 116(由dedicatehw指示)中存在,如果不存在则依据*ctx的指示(由 processorcontext指示)由模拟执行结果保存区域1246读取数据;

75.(3)第14-25行:读取来源运算元(分别由src1/src2表示),其取得方式如前面的寄存器编码(dst)一样,先去判断是否存在专用硬件116中,如果不存在就表示处理器110支持这个寄存器,于是依据*ctx的指示(由processorcontext指示)由处理器状态保存区域1242去读取;

76.(4)第27-49行:依据avx-512规格对vaddsd所定义的操作而撰写的程序码。举例来说:

77.a.第27行:判断目前指令支持的操作模式(broadcast/rc/sae context),并在evex.b为1时依据规格书对运算元启动静态舍入控制;

78.b.第34-49行:判断目前的vaddsd指令是否通过罩遮寄存器(mask register) 进行控制,例如当k1{0}=1时行对应的src1 src2,否则不执行相应的操作;

79.c.最终结果还要依据{z}来决定,例如{z}=1时表示清零操作(zeroing),{z}=0 则表示与原有dst结果进行合并(merge);

80.(5)第51-56行:判断目的寄存器是否为处理器110所支持的寄存器(例如512位寄存器就不是目前处理器110所支持的寄存器,因为处理器110的寄存器只有 256位),并在寄存器是处理器110不支持的寄存器时,除了通过模拟执行结果指针寄存器116c的映射得知所模拟的寄存器是由那些处理器110所支持的模拟寄存器(位于模拟寄存器文件116e中)所模拟之外,亦将这些模拟寄存器所对应的内容依据模拟执行结果指针寄存器116c所指示的地址,储存到模拟执行结果保存区域1246中;若是处理器110所支持的寄存器时则保存到ne的处理器的运行状态中;

81.(6)第58-60行:在确认处理器110目前硬件支持的最大的向量长度(例如256),将计算的结果更新到所有硬件已经支持的向量寄存器上;

82.(7)最后于第62行将执行结果回传。

83.值得注意的是,图6a/6b的第36、48、49是avx-512规格中对vaddsd 所定义的编码版(encoded version)操作,由于这条指令的来源操作数是128位 (xmm1)与64位(xmm2),所以只要利用一个模拟程序即可对vaddsd进行模拟。然而对于其他支援512位来源/目的寄存器的指令就可能需要拆分为多个模拟程序。举例来说,avx-512规格中的addps(或vaddps)指令就可支援512位的寄存器,例如:

84.addps zmm0{k1}{z},zmm1,zmm2

85.其中zmm0/zmm1/zmm2都是512位寄存器,而且若依据avx-512规格所定义的操作进行模拟时将需要许多判断(例如if/else)与循环(for loop)等步骤,然若以编码版(encoded version)来看就不需要这些步骤。所以若直接用编码版的定义,把不同长度的运算元写成不同的模拟程序(例如以128/256/512位作区分),并依据目的/来源运算元长度最大者来调用对应的模拟程序,这样或可提高处理器110的执行效率。举例来说,依据avx-512规格的定义,可以把对addps的模拟分成128/256/512位三种模拟程序,于是当待执行指令132 是addps指令时,可判断来源/目的寄存器的最大长度,并据以调用不同的模拟程序,例如运算元中最大长度是ymm2,其为256位,于是调用addps 专门处理256位寄存器的模拟程序。上述对vaddpd调用对应模拟程序的操作,可以运用图5b所例示的架构来进行,所以不再赘述。

86.图7是依照本发明实施例的模拟方法的流程图,图7的转换方法适用于前述图4a/4b所示的处理器。如图7所示,于步骤s702中,当处理器110所执行的待执行指令132是一扩增指令时,便由硬件触发中断(可为#ud或#ne)并进入对应于的中断服务程序。关于如何进入中断服务程序,请参考图4a/4b相关叙述。此时其他的硬件中断亦将被禁止,以避免在转换与模拟过程中,有无关的硬件中断信号干扰转换模/拟过程,同时避免转换/模拟过程受到攻击。于步骤s704中,构建模拟模块122的模拟执行环境,至于构建模拟模块122 的环境参数可事先编写在基本输出输入系统、处理器的驱动程序、或是编译进操作系统的核心中,并在需要构建模拟模122时调用。处理器110目前的执行环境参数将被保存,例如通过专用硬件116中的处理器当前状态指针寄存器116a里所指示的地址,将处理器110目前的执行环境参数储存至主储存器里的处理器状态保存区域1242中(例将执行环境参数推入(push)状态堆叠中)。于步骤s706中,模拟模块122根据中断服务程序所提供的指针,逐字节读取待执行指令132的格式信息(解码获取指令信息,请参考图4a/4b部分所述) 后,再搭配处理器110目前工作状态以判断目前的待执行指令132是否能在处理器110目前工作模式下运行。若当前的待执行指令132不能在目前处理器的工作环境下运行时(例如目前待执行指令132(为扩增指令)要在保护模式 (protected mode)下运行,但目前的处理器110却工作于真实模式(real mode)中),此时的判断结果将为否,则从步骤s706进入步骤s708将保存的中断程序现场进行恢复,例如从处理器当前状态指针寄存器116a里所指示的地址,读取调用模拟模块122之前储存在处理器状态保存区域1242的处理器110执行工作环境参数读出来(例如从于状态堆叠中取出(pop)先前储存的执行环境参数),以恢复处理器110在调用模拟模块122前的执行状态,随后退出模拟模块122 并结束对待执行指令的转换/模拟操作。若在步骤s706中判断当前待执行指令132可在目前处理器的工作环境下运行时,则从步骤s706进入步骤s710,并由模拟模块122利用待执行指令132的格式信息去调用对应的模拟程序后进入步骤s712,随后依据待执行指令132的指示去读取内存操作数或寄存器操作数。若遇到目前处理器110硬件不支持的架构寄存器,则使用专用硬件 116的模拟寄存器文件116e的映射关系进行查找(随后进行数据储存或修改)。如前所述,在步骤s712进行模拟程序的调用过程中,可以将转换过程的所有信息,通过转换信息指针寄存器116b所指示的地址以储存在转换信息保存区域1244中。于步骤s714中模拟模块112将执行模拟程序。如前所述,在步骤 s714进行模拟程序的执行过程中,可以将执行过程的所有信息,通过模拟执行结果指针寄存器116c所指示的地址而储存在模拟执行结果保存区域1246 中。值得注意的是,模拟

程序所产生的模拟结果也被缓存在模拟执行结果保存区域1246中。于步骤s716中,设置模拟完成信息至模拟执行结果保存区域 1246,随后将保存的中断程序现场进行恢复(亦即从处理器当前状态指针寄存器116a里所指示的地址,将调用模拟模块122前储存在处理器状态保存区域1242的状态堆叠中的处理器110执行工作环境参数读出来),并退出模拟模块122而结束扩增指令的模拟操作。最后,处理器110可利用模拟执行结果指针寄存器116c所指示的地址,去读取待执行指令132的模拟执行结果。

87.图8是依照本发明实施例的判断指执行指令是否为扩增指令的流程图。如图8所示,于步骤s802中,处理器110接收一待执行指令132。步骤s804,处理器110解码待执行指令132。步骤s806,指令解码器112判断待执行指令 132是否为可兼容指令(例如原生指令)。若待执行指令132为可兼容指令时(例如:判断为是),则从步骤s806进入步骤s808,由处理器110执行该可兼容指令并返回执行结果;若待执行指令132不为可兼容指令时(例如:步骤s806 的判断结果为否),则从步骤s806进入步骤s810,由监测器114判断待执行指令132是否为扩增指令。若监测器114判断待执行指令132为扩增指令时(例如:判断为是)则进入步骤s814,监测器114将设置模拟旗标ef为致能,并在待执行指令132提交(retire,如图4a/4b所示,此时是对应于待执行指令132 的空指令被提交)时查询处理器中的一中断向量表(例如#ne)以查找对应的中断服务程序,并经由该中断服务程序去呼叫模拟模块122。中断服务程序呼叫模拟模块122的方式,可经由预先设置的硬件、事先写好的软件、或是由软/硬件组合(例如由微码控制单元执行微码)而成的接口来进行,并在判断目前的待执行令132可调用模拟模块122(例如应用程序130的认证成功)后前往调用模拟模块122。最后进入步骤s816,经由模拟模块122转换该待执行指令132为模拟程序,随后通过执行该模拟程序来模拟该待执行指令132(目前为扩增指令)的执行并返回执行结果。

88.综上所述,本发明实施例所述的指令模拟装置及其方法利用监测器来判断应用程序中的待执行指令是否为处理器的可兼容指令或是扩增指令。并且,若此待执行指令经判断为扩增指令时,处理器将此待执行指令转换为处理器可运行的模拟程序并加以执行,以解决处理器指令集的兼容性问题,从而延长使用此模拟装置的电子设备的使用年限。

89.以上所述仅为本发明较佳实施例,然其并非用以限定本发明的范围,任何熟悉本项技术的人员,在不脱离本发明的精神和范围内,可在此基础上做进一步的改进和变化,因此本发明的保护范围当以本技术的权利要求书所界定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。