一种硅基iii-v族半导体材料的制备方法

技术领域

1.本发明涉及半导体技术领域,尤其涉及一种硅基iii-v族半导体材料的制备方法。

背景技术:

2.随着信息技术的飞速发展,以微电子为基础的信息传输网络面对人们对数据传输速率、信息处理速度等越来越高的需求显得愈发吃力。对于如此困境,以光作为信息传输的载体,将现有成熟的微电子和光电子技术想结合是一条很好的解决途,其在充分发挥硅基微电子成熟工艺技术的同时,还可以发挥光电子的极高传输速率、高抗干扰性和低功耗的优势。硅基光电集成已成为大规模集成电路未来发展的重要方向之一,但由于硅是间接带隙材料,发光效率极低,难以作为增益介质,为此硅基光源已成制约硅基光电集成发展的最大障碍。在硅基光源的实现方案中,硅上单片集成iii-v族半导体光源具有较好的应用前景。但是硅与直接带隙

ⅲ‑ⅴ

族半导体之间通常存在较大的晶格失配,晶格失配又会导致失配应力且主要通过穿透位错进行有效释放,因此在硅上直接外延iii-v族半导体材料时会产生大量的穿透位错,严重影响着硅基光源的性能,尤其是极大地降低器件寿命。

3.在硅上异变外延gaas基iii-v族半导体材料时,尽管gaas与硅的晶格失配度4.1%也会产生面密度高达108cm-2

以上的穿透位错。此时,如何有效阻挡穿透位错向上传播至激光器有源区就显得至关重要。

4.目前对于阻挡穿透位错常用的方法是引入含有晶格失配的应变结构例如,应变量子阱结构、应变量子点结构、应变量子阱与量子点混合结构。利用应变结构中产生的失配应力改变穿透位错的传播方向,以避免穿透位错传播至有源区。从而减少穿透位错传播至有源区。但是,应变结构阻挡穿透位错的效果也十分有限,且应变结构中的失配应力还可能产生额外的穿透位错。因此,即便引入应变结构,硅基iii-v族半导体的穿透位错密度仍高达106cm-2

以上,这严重制约着可覆盖光通信全部波长窗口的硅基量子阱激光器的室温长时间连续激射,受此影响硅上gaas基量子阱激光器的寿命目前也仅有几百小时。为此如何有效阻挡穿透位错传播是硅基iii-v族半导体光源中一直存在的难题。

技术实现要素:

5.本发明提供了一种硅基iii-v族半导体材料的制备方法,用以解决现有硅基iii-v族半导体材料外延生长中穿透位错密度依然较高的问题。本发明相较与现有技术可显著降低硅基iii-v族半导体材料的穿透位错密度,有助于实现硅基iii-v族量子阱激光器的室温连续激射并提升其寿命。

6.本发明提供一种硅基iii-v族半导体材料的制备方法,该方法包括:

7.在硅衬底上至少两次重复生长iii-v族半导体基本外延结构单元,形成重复生长外延结构;

8.在所述重复生长外延结构上继续外延生长iii-v族半导体材料和/或iii-v族半导体器件结构;

9.其中,所述重复生长外延结构包括两个或两个以上的iii-v族半导体基本外延结构单元;所述基本外延结构单元的生长过程,包括:

10.(1)在第一温度条件下生长低温层;

11.(2)在第二温度条件下,在所述低温层上生长中温层,所述第二温度条件高于第一温度条件;

12.(3)在第三温度条件下,在所述中温层上外延生长高温层,所述第三温度条件高于第二温度条件;

13.(4)在所述高温层外延生长过程中暂停高温层外延生长,进行热循环退火,随后继续高温层外延生长。

14.根据本发明实施例提供的一种硅基iii-v族半导体材料的制备方法,所述重复生长外延结构是指两个基本外延结构单元或n个基本外延结构单元,其中n为大于2的整数;自下而上将重复生长外延结构中的基本外延结构单元依次标记为第一单元、第二单元,直至第n单元;

15.所述热循环退火使得所述iii-v族半导体基本外延结构单元的低温层顶部区域与低温层底部区域发生弱关联的晶化,同时使得所述iii-v族半导体基本外延结构单元的高温层连同中温层的顶部区域与中温层底部区域实现彼此弱关联的晶态纯化;所述顶部区域是指低温层,或中温层,或高温层的厚度2/3以上的区域;所述底部区域是指低温层,或中温层,或高温层的厚度1/3以下的区域;

16.其中,所述晶化是指低温层由非晶体态转变成晶态,即低温层由杂乱无序的晶格排列重塑为较为规整的晶格排列;所述弱关联的晶化是指在所述热循环退火中在低温层中顶部区域与底部区域中的晶化过程同时进行、无先后顺序,两个区域彼此的关联性降低,从而中断了穿透位错在低温层向上传播的部分途径;

17.所述晶态纯化是指中温层与高温层得到进一步晶化,即中温层以及高温层由较为规整的晶格排列重塑出极为规整的晶格排列;所述弱关联的晶态纯化是指在热循环退火中所述高温层连同中温层顶部区域与以及中温层与低温层的界面底部区域处的晶态纯化也是同时进行、无先后顺序,彼此的关联性降低,从而提升了高温层晶体质量。

18.根据本发明实施例提供的一种硅基iii-v族半导体材料的制备方法,所述硅衬底为:

19.无偏角的硅衬底,晶面方向为100;或者,

20.有偏角的硅衬底,晶面方向为100。

21.根据本发明实施例提供的一种硅基iii-v族半导体材料的制备方法,所述硅衬底的图形为“v”型、孔型、方形或条形。

22.根据本发明实施例提供的一种硅基iii-v族半导体材料的制备方法,所述第一温度条件下生长低温层的条件为:温度范围350-550℃,v族源与iii族源的流量比或束流比范围20-1000,生长厚度范围是5-50nm;

23.所述第二温度条件下生长中温层的条件为:温度范围550-650℃,v族源与iii族源的流量比或束流比范围50-1000,生长厚度范围是50-500nm;

24.所述第三温度条件下外延生长高温层的条件为:温度范围650-750℃,v族与iii族的流量比或束流比范围50-1000,生长厚度范围是100-2500nm。

25.根据本发明实施例提供的一种硅基iii-v族半导体材料的制备方法,所述热循环退火为原位退火,退火温度范围为300-800℃,所述热循环退火的次数为一次或多次;

26.所述基本外延结构单元的生长过程,还包括:

27.(5)在所述高温层外延生长结束后,进行热循环退火。

28.根据本发明实施例提供的一种硅基iii-v族半导体材料的制备方法,所述低温层、中温层以及高温层均使用同一种材料。

29.根据本发明实施例提供的一种硅基iii-v族半导体材料的制备方法,所述外延生长采用金属有机化学气相沉积mocvd和/或分子束外延mbe。

30.根据本发明实施例提供的一种硅基iii-v族半导体材料的制备方法,所述iii-v族半导体材料为gap系、gaas系、inp系以及gasb系半导体材料中的一种或多种。

31.根据本发明实施例提供的一种硅基iii-v族半导体材料的制备方法,所述iii-v族半导体器件结构包括但不局限于iii-v族半导体激光器、iii-v族超辐射发光二极管、iii-v族发光二极管、iii-v族光放大器、iii-v族光探测器以及iii-v族无源器件。

32.本发明提供硅基iii-v族半导体材料的制备方法,通过在第一温度条件下,在硅衬底上生长低温层,在第二温度条件下,在所述低温层上生长中温层,所述第二温度条件高于第一温度条件,在第三温度条件下,在所述中温层上外延生长高温层,所述第三温度条件高于第二温度条件,进行热循环退火,在所述外延生长高温外延结构上形成iii-v族半导体器件结构。

33.使用本发明实施例的技术方案,所述热循环退火使得第一次生长的低温层顶部区域与所述硅衬底与低温层的界面附近低温层一侧发生弱关联的晶化,使得第二次生长的低温层顶部区域以及第一次外延生长的高温层与第二次生长的低温层的界面附近低温层一侧发生弱关联的晶化,还使得所述高温层连同中温层的顶部区域与中温层底部区域实现彼此弱关联的晶态纯化。

34.其中所述弱关联的晶化是指所述硅衬底与低温层的界面附近以及第一次外延生长的高温层与第二次生长的低温层的界面附近低温层一侧在所述热循环退火中的晶化同时进行且无先后顺序,彼此的关联性降低,因而中断所述硅衬底与低温层的界面处形成的穿透位错向上传播的途径,因而缩短了硅衬底与低温层的界面处形成的失配位错向上穿透的时间。

35.所述弱关联的晶态纯化是指所述高温层连同中温层的顶部区域与中温层底部区域实现彼此弱关联的晶态纯化,也是同时进行、且无先后顺序,彼此的关联性降低,因而缩短了该界面处出现的晶体结构不完善性、特别是穿透位错持续向上延伸的时间。该工艺方法充分地发挥了多步外延生长工艺的潜力,降低硅基iii-v族半导体材料的穿透位错密度,进而显著提高硅基iii-v族半导体器件、特别是发光器件的性能。

附图说明

36.为了更清楚地说明本发明或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

37.图1是本发明实施例提供的硅基iii-v族半导体材料的制备方法的流程示意图之一;

38.图2是本发明实施例提供的硅基iii-v族半导体材料的制备方法的流程示意图之二;

39.图3是本发明实施例提供的硅基iii-v族半导体材料的剖视图。

具体实施方式

40.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明中的附图,对本发明中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

41.本发明发明人对现有技术进行研究发现,在硅衬底上直接异质外延生长iii-v族半导体材料时,低温生长iii-v族半导体材料尽管在硅衬底上的成核点比高温生长iii-v族半导体材料时要多一个数量级甚至更多。理论上成核点多的生长方式会造成更多的缺陷尤其是穿透位错,但是对两种不同的生长方式(即,在硅衬底上纯高温生长iii-v族半导体材料,以及在硅衬底上先低温生长后高温生长iii-v族半导体材料)所获得的iii-v族半导体材料晶体质量进行表征后发现,拥有低温层的硅基iii-v族半导体材料质量要远高于纯高温生长iii-v族半导体材料质量。因此“低温—高温”两步法已成为最常用最基本的硅基iii-v族半导体异质外延方法。但是对于该不合常规的现象尚未有统一的解释,目前被广泛采纳的解释:由于低温生长所形成的低温层是一种由iii族和v族混乱排列的一种呈不定型晶态排列模式(已被实验所证实),因此在低温层中不存在任何穿透位错(非晶体的晶态中无穿透位错可言,但是存在大量的晶体缺陷)。这就使得在“低温—高温”两步法中iii-v族半导体材料的穿透位错产生与后续高温生长过程紧密相关,并非伊始就出现在成核点附近。所以其最终获得的含有低温层的硅基iii-v族半导体材料的晶体质量会大大提高。

42.正如前文所述,由于iii-v族低温层是非晶材料(不定型晶态,自然界中材料若按照晶体结构划分,可以分为单晶、多晶和非晶三大类),且内部存在大量缺陷。因此本领域研究人员在iii-v族低温层上生长iii-v族高温层或者低温层上继续生长iii-v族高温层,通常不会单纯地在硅基iii-v族半导体异变外延中重复使用两步法(实际上就是不会重复多次低温生长iii-v族半导体材料),举例来说,不会单纯采用“低温—高温—低温—高温

…”

方式进行硅基iii-v族半导体异质外延。

43.进一步,硅与iii-v族直接带隙半导体材料之间还存在较大的晶格失配度(譬如硅与gaas的晶格失配度就高达4.1%),这样就会在硅基iii-v族半导体异质外延生长过程中产生大量的穿透位错,并一直贯穿至iii-v族高温层表面。为了有效降低硅基iii-v族半导体材料的表面穿透位错密度,几乎所有硅基iii-v族半导体异质外延报道中都在两步法生长过程中引入热循环退火(具体是在高温生长iii-v族半导体材料过程中或结束后引入热循环退火),这也是研究人员公认的最有效办法。此处,热循环退火是指,将硅基iii-v族半导体材料加热到某一温度并保持一段时间后,再冷却降温至某一温度,同样保持一段时间,并将这样的操作反复多次。

44.目前被研究者所认可的热循环退火降低穿透位错密度的机理是:通过热循环退火

产生足量的热应力使得穿透位错发生滑移,进而穿透位错在滑移过程中相互碰撞而部分湮灭掉。由于无法通过一次热循环退火就将穿透位错密度降到极低的水平,研究人员常常在高温生长的iii-v族层的不同位置反复插入热循环退火以最大程度地降低穿透位错密度,这种降低穿透位错的操作可以等效地看成:先在硅衬底上在低温条件下生长iii-v族低温层,然后在高温条件下两次或两次以上生长所需的iii-v族半导体外延结构,且在每个iii-v族半导体外延结构生长结束后进行热循环退火,也就是“低温—高温—热循环退火—高温—热循环退火

…”

方式。其中热循环退火产生的热应力是利用硅衬底热膨胀系数αs与外延生长的iii-v族半导体材料热膨胀系数αf不同,通过最低退火温度t

min

与最高退火温度t

max

之间的温度差所实现的。热应力具体大小可通过之间的温度差所实现的。热应力具体大小可通过计算(考虑到硅基iii-v族半导体材料异质外延中引入热循环退火的工艺代价,t

min

往往不低于350℃)。

45.基于两步法的基础上,研究人员在实验过程中还发现在低温层与高温层之间插入其他温度层(该生长方式还没有完善的理论依据仅有实验结果),统称为多步法生长(三步法、四步法等),可以进一步提高晶体质量。虽然多种生长方式与热应力的引入相结合可以降低穿透位错密度,但是仍然无法使硅与iii-v族直接带隙半导体材料之间产生大量穿透位错降低至理想的范围。

46.然而,本发明人在研究过程中发现:热循环退火中的“快速降温”过程所带来的降低穿透位错的效果,不仅仅是使得穿透位错发生的滑移、相互碰撞湮灭,还应当包括低温层的晶态转变(非晶-单晶)过程。其中低温层晶态快速转变过程对穿透位错的减少有着至关重要的作用。也就是说,低温层的非晶特性尤其是缺陷在非晶中存在的特性使得纯低温层中无任何穿透位错,然而穿透位错的传播必须借助于晶体介质存在的特性,所以不难想到便可以借用非晶向单晶晶态转变过程来消除穿透位错的传播,也就可以达到降低穿透位错密度的作用。同时值得注意的是非晶中的非相邻区域间的彼此关联性较弱,所以在晶化过程中尤其是非晶层的底部与顶部区域是相互弱关联的,也就是说晶化过程中底部区域的产生的向上传播的位错并不会影响到底部区域的晶化过程,在位错还未传播至顶层区域时顶部区域完成晶化这样就可以迫使原本向上传播的位错改变传播方向形成其他形式的缺陷,例如:界面驻留位错、位错环等。不仅如此,常见的高温层的穿透位错的滑移消除了原本存在于高温层的穿透位错,不仅起到了直接降低表面穿透位错密度的作用还起到了阻挡下方位错向上传播的效果。在上述的多种因素的作用下迫使本可以向上传播穿透位错转换成其他形式的缺陷存在,大大减少了穿透位错在晶体内部的传播,便可极其有效地降低穿透位错密度。

47.本发明的这一发现拓展了研究人员对非高温(低温以及中温)条件下生长层作用的认知,尤其是对iii-v低温层的传统作用认知。接下来,本发明实施例更加细致地分析硅基iii-v族异质外延中的低温层的晶化过程。由于晶化过程是在iii-v族半导体材料生长过程中进行的尤其是热循环退火的作用下进行的,因此硅基iii-v族外延结构的所有部分都同时经历到同样的温度变化,这使得iii-v族低温层的顶部区域和硅衬底—iii-v族低温层界面附近的iii-v族低温层底部区域的晶化是同时进行、无先后顺序,彼此的关联性降低但不是无关联,称之为“弱关联晶化”。可想而知iii-v族外延结构中的高温层与iii-v族低温

层在热循环退火的作用下的晶化过程会存在着时间差,高温层会优先完成晶化,所以低温层的穿透位错在低温层继续的晶化过程中不会再向上传播进而转变成其他形式的缺陷例如位错环、界面驻留位错,而是低温层在热循环退火过程中对穿透位错的降低起到了至关重要的作用,并非仅是通常认识中简单的位错滑移。

48.为了进一步地发挥晶态转变降低穿透位错密度的效果,在iii-v族低温层上还生长iii-v族中温层,因为iii-v族中温层的生长温度低,是一种较为规整的晶格排列的单晶(并非完全长程有序,还包括一些中程有序的排列)依旧可以发挥晶态转变使穿透位错密度降低的能力,以此可以获得比两步法(低温 高温)更好硅基iii-v族半导体材料的晶体质量。

49.具体地,在硅衬底上先生长厚度适中的iii-v族低温层,并且在外延iii-v族中温层之前低温层一直保持在非晶状态,当开始外延iii-v族中温层时,低温层的晶化过程也随之开启,由于低温到中温温度台阶较低,所以在非晶向单晶转变的过程很微弱但依旧存在。在完成中温层生长后。继续外延生长iii-v族高温层,此时不仅有低温层的晶化作用同时还有中温层与高温层的纯化作用(所述的纯化与晶化过程极为相似,较好的iii-v族中温层质量上继续外延生长iii-v族高温层时,在热应力的作用下,iii-v族低温层会开始完全晶化,同时iii-v族中温层以及高温层还会发生由较为规整的晶格排列重塑出极为规整的晶格排列,将此过程我们称之为“晶态纯化”)即,非晶向单晶转化、排列较为规整晶体在向排列极为规整的晶体转化。但是由于温度梯度较低产生热应力较小持续时间较长,高温层与低温层之间并没有形成足够的时间差,此时所获得的晶体质量依旧较差。最后在高温层增加热循环退火步骤,由于热循环退火产生的温度梯度是快速产生的,这样就会在高温层完成穿透位错整合的同时与低温层、中温之间产生足够时间差来减少穿透位错向上传播,充分发挥低温层晶化、中温层与高温层纯化降低穿透位错密度的作用。

50.尽管经此流程高温层的晶体质量大大提升,但由于硅与iii-v族低温层界面处产生的穿透位错相当多,仍不足以使得表面穿透位错密度降至很低水平。正是由于本案发明人发现生长过程中低温与中温的生长规律,所以才敢确信“晶化”以及“纯化”可以有效地降低穿透位错的作用而且不会带来任何不利因素。所以可以再次放心大胆地利用晶化以及纯化作用进一步减少,也就是在iii-v族高温层上两次或多次重复“低温—中温—高温—热循环退火”,将穿透位错密度降至理想范围,整个生长就是“低温—中温—高温—热循环退火—低温—中温—高温—热循环退火”。

51.下面结合图1,具体阐述本发明实施例提供的硅基iii-v族半导体材料的制备方法,参考图1,本方法具体包括如下步骤:

52.步骤110:在硅衬底上至少两次重复生长iii-v族半导体外延结构单元,形成重复生长外延结构;

53.步骤120:在所述重复生长外延结构上继续外延生长iii-v族半导体材料和/或iii-v族半导体器件结构。

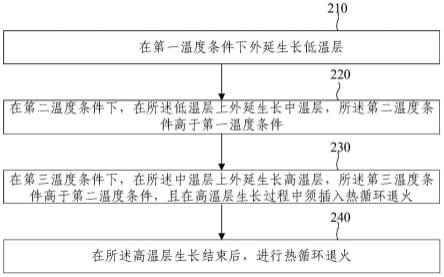

54.参考图2,生长iii-v族半导体外延结构单元,包括如下步骤:

55.步骤210:在第一温度条件下生长低温层;

56.步骤220:在第二温度条件下,在所述低温层上生长中温层,所述第二温度条件高于第一温度条件;

57.步骤230:在第三温度条件下,在所述中温层上外延生长高温层,所述第三温度条件高于第二温度条件,且在高温层生长过程中须插入热循环退火;

58.步骤240:在所述高温层外延生长结束后,进行热循环退火。

59.使用本实施例的技术方案,得到由低温层、中温层和高温层叠置构成的iii-v族半导体基础结构(即基本外延结构单元)。

60.请参考图3所示,本发明实施例采用上述三步法生成硅基iii-v族半导体材料,具体包括:

61.位于硅衬底310上的第一低温层311;

62.位于第一低温层311上的第一中温层312;

63.位于第一中温层312上的第一高温层313;

64.位于第一高温层313上的第二低温层321;

65.位于第二低温层321上的第二中温层322;

66.位于第二中温层322上的第二高温层323。

67.在本发明具体实施例中,硅基iii-v族半导体材料的制备方法可以形成一组或多组低温层、中温层及高温层,不受图3所示实施例的限定,可以根据需要选择。

68.使用本发明实施例的技术方案,在所述两或多单元重复生长外延结构(即重复生长外延结构)中,自下而上的iii-v族半导体外延结构单元至少包括,第一iii-v族半导体外延结构单元(即第一单元)、第二iii-v族半导体外延结构单元(即第二单元)。

69.热循环退火使得所述第一iii-v族半导体外延结构单元的低温层顶部区域与所述硅衬底与低温层的界面附近低温层一侧发生弱关联的晶化,使得所述第二iii-v族半导体外延结构单元的低温层顶部区域以及所述第一iii-v族半导体外延结构单元的高温层与所述第二iii-v族半导体外延结构单元的低温层的界面附近低温层一侧发生弱关联的晶化,还使得所述高温层连同中温层的顶部区域与中温层底部区域实现彼此弱关联的晶态纯化;

70.其中所述弱关联的晶化是指所述硅衬底与低温层的界面附近以及第一iii-v族半导体外延结构单元的高温层与第二iii-v族半导体外延结构单元的低温层的界面附近低温层一侧在所述热循环退火中的晶化同时进行且无先后顺序,彼此的关联性降低,因而中断部分所述硅衬底与低温层的界面处形成的穿透位错向上传播的途径;

71.所述弱关联的晶态纯化是指所述高温层连同中温层的顶部区域与中温层底部区域实现彼此弱关联的晶态纯化,也是同时进行、且无先后顺序,彼此的关联性降低,从而实现其高温层晶体质量的优化。

72.可选地,第一iii-v族半导体外延结构单元的低温层顶部区域与所述硅衬底与低温层的界面附近低温层一侧发生弱关联的晶化,是指低温层由非晶态转变成晶态,即低温层由杂乱无序的晶格排列重塑为较为规整的晶格排列;

73.所述高温层连同中温层的顶部区域与中温层底部区域实现彼此弱关联的晶态纯化,是指中温层与高温层得到进一步晶化,即中温层由较为规整的晶格排列重塑出极为规整的晶格排列。

74.可选地,在使用两组或多组三步法生成iii-v族半导体材料时,由于第一组低温层-中温层-高温层主要是针对硅基的晶格失配问题本身就会产生一定量的穿透位错,第二组低温层-中温层-高温层开始就是针对第一组外延结构残留的穿透位错,通过至少两组的

外延结构化外延生长,由于每组都有非晶结构以及退火步骤,可以有效地将向上传播的穿透位错进行阻断。

75.在本发明实施例中,可以采用至少两组低温、中温及高温生长步骤生成iii-v族半导体材料。经过大量实验证明,这不仅能够降低穿透位错密度,还能够确保最终形成的iii-v族外延结构具有合适厚度。

76.在本发明实施例中,硅衬底为无偏角的(100)晶面硅衬底,或有偏角的(100)晶面硅衬底,或非(100)晶面的所有晶面的硅衬底,优选无偏角的(100)晶面硅衬底。所述硅衬底可为图形硅衬底,图形包括但不限于“v”型、孔型、方形、条形。图形尺寸为微米、亚微米或纳米尺度。

77.硅基iii-v族半导体材料可以为非晶结构,通过第一温度条件提供的低温生长条件在硅衬底上以低温生长的非晶作为桥梁连接了金刚石晶体结构的硅衬底以及闪锌矿结构的iii-v族半导体材料,通过热循环退火彻底发生非晶低温层发生弱关联晶化,消减硅衬底与iii-v族半导体材料之间因晶格失配而形成的穿透位错的数量。

78.而在第二组低温生长的非晶结构用在已外延生长的iii-v族半导体材料结构表面,此时非晶结构的作用不同于第一组外延生长,首先该非晶结构上下连接的均是闪锌矿结构的iii-v族半导体材料,其次该非晶层作为一种无序的非晶结构来改变甚至阻断下方长程有序的单晶结构中穿透位错的传播进程,除此之外由于此时的非晶层的晶格常数与即将生长的iii-v族半导体材料的晶格常数相匹配就不会进一步地产生新的穿透位错。

79.本发明实施例充分发挥低温非晶生长的特性,方法虽然简单但是对减少缺陷提高晶体质量极其有效,相比于常用的高失配的位错阻挡层,本发明的结构不需要再次引入额外的晶格失配,大大降低了结构压力,并且该方法普适有效,简单易行。

80.在本发明实施例中,硅衬底为图形硅衬底,所述图形硅衬底的图形为“v”型、孔型、方形或条形。

81.在本发明实施例中,还可以在高温层或中温层上形成应变层,应变层能够阻挡穿透位错向上传播。

82.在本发明实施例中,第一温度条件下生长低温层的条件为:温度范围350-550℃,v族源与iii族源的流量比或束流比范围20-1000,生长厚度范围是5-50nm;

83.所述第二温度条件下生长中温层的条件为:温度范围550-650℃,v族源与iii族源的流量比或束流比范围50-1000,生长厚度范围是50-500nm;

84.所述第三温度条件下外延生长高温层的条件为:温度范围650-750℃,v族与iii族的流量比或束流比范围50-1000,生长厚度范围是100-2500nm。

85.本发明实施例所提出的工艺参数,各参数之间并不是孤立的,各参数之间是相互关联的,因此需要充分参考各步骤参数之间的关联关系,进行大量实验才得到的。

86.在本发明实施例中,热循环退火的退火温度范围为:300-800℃。使用热循环退火可以促进高温层及下方的低温层再结晶,减少低温层中穿透位错的形成,以达到降低穿透位错密度的能力。

87.在本发明实施例中,低温层、中温层和高温层中至少一个层之后进行热循环退火。这样,可以在任一层之后进行热循环退火或在高温层形成之后单独进行热循环退火。

88.在本发明实施例中,低温层、中温层和高温层均使用同一种材料。

89.在本发明具体实施例中,上述任一层的外延生长采用金属有机化学气相沉积(mocvd)或分子束外延(mbe)或mocvd与mbe的组合,从而实现在清洗后的无偏角硅衬底上外延生长硅基iii-v族半导体材料,来抑制反相畴与穿透位错的生成。

90.下面结合具体示例阐述本发明实施例的硅基iii-v族半导体材料的制备方法。

91.在本发明一种实施例中,利用mocvd,在清洗后的无偏角硅衬底上外延生长一种硅基iii-v族半导体材料,来抑制反相畴与穿透位错生成的工艺方法,但不限于mocvd。

92.在本实施例中,硅衬底采用无偏角(100)硅衬底,iii-v族砷化物采用gaas材料,mocvd载气为高纯度氢气,iii族有机源为高纯度三甲基镓,v族源为高纯度砷烷,反应室压力为100托尔。本实施例提供的硅基iii-v族半导体材料的制备方法的具体步骤如下:

93.步骤301,将硅衬底进行清洗,清除硅衬底上的有机物、金属粒子、氧化层等杂质;

94.步骤302,将清洗完成的硅衬底进行甩干,将甩干后的硅衬底放入外延生长腔室中;

95.步骤303,将腔室温度升至850℃并保持10min,将生长室温度降低至420℃生长10nm的gaas低温层,v/iii流量比为200;

96.步骤304,将温度升至650℃,生长200nm的gaas中温层,v/iii族流量比为100;

97.步骤305,将温度升至680℃,生长500nm的gaas高温层,v/iii族流量比为100;

98.步骤306,将温度提高到750℃保存5min,缓慢降低到350℃并保持400s,然后升温至680℃,完成退火;

99.步骤307,在680℃,生长100nm的gaas高温层,v/iii族流量比为100;

100.步骤308,将温度提高到750℃保存5min,缓慢降低到350℃并保持400s,然后升温至680℃,完成退火;

101.步骤309,在680℃,生长100nm的gaas高温层,v/iii族流量比为100;

102.步骤310,将温度降低至420℃,生长10nm的gaas低温层,v/iii族流量比为200;

103.步骤311,将温度升至650℃,生长200nm的gaas中温层,v/iii族流量比为100;

104.步骤312,将温度升至680℃,生长500nm的gaas高温层,v/iii族流量比为100;

105.步骤313,将温度提高到750℃保存5min,缓慢降低350℃并保持400s,然后升温至680℃,完成退火;

106.步骤314,在680℃,生长100nm的gaas高温层,v/iii族流量比为100;

107.步骤315,将温度提高到750℃保存5min,缓慢降低350℃并保持400s,然后升温至680℃,完成退火;

108.步骤316,在680℃,生长100nm的gaas高温层,v/iii流量比为100。

109.步骤317,在gaas外延层的基础上进行量子阱结构的外延生长。半导体量子阱结构(semiconductor quantum wells)是指两种半导体材料按三明治样式生长成的结构。

110.在本发明另一种实施例中,硅衬底采用有偏角(100)硅衬底,iii-v族砷化物采用inp材料,mocvd载气为高纯度氢气,iii族有机源为高纯度三甲基镓,v族源为高纯度磷烷,反应室压力为100托尔。本实施例提供的硅基iii-v族半导体材料的制备方法的具体步骤如下:

111.步骤401,将硅衬底进行清洗,除硅衬底上的有机物、金属粒子、氧化层;

112.步骤402,将清洗完成的硅衬底进行甩干,将甩干后的硅衬底放入外延生长腔室

中;

113.步骤403,将腔室温度升至750℃并保持10min,将生长室温度降低至420℃生长10nm的inp低温层,v/iii族流量比为990;

114.步骤404,将温度升至650℃,生长200nm的inp中温层,v/iii族流量比为400;

115.步骤405,将温度升至680℃,生长300nm的inp高温层,v/iii族流量比为400;

116.步骤406,将温度提高到750℃保存5min,缓慢降低350℃并保持400s,然后升温至680℃,完成退火;

117.步骤407,在680℃,生长100nm的inp高温层,v/iii族流量比为400;

118.步骤408,将温度提高到750℃保存5min,缓慢降低350℃并保持400s,然后升温至680℃,完成退火;

119.步骤409,在680℃,生长100nm的inp高温层,v/iii族流量比为400;

120.步骤410,将温度降低至420℃生长10nm的inp低温层,v/iii族流量比为990;

121.步骤411,将温度升至650℃,生长200nm的inp中温层,v/iii族流量比为400;

122.步骤412,将温度升至680℃,生长300nm的inp高温层,v/iii族流量比为400;

123.步骤413,将温度提高到750℃保存5min,缓慢降低350℃并保持400s,然后升温至680℃,完成退火;

124.步骤414,在680℃,生长100nm的inp高温层,v/iii族流量比为400;

125.步骤415,将温度提高到750℃保存5min,缓慢降低350℃并保持400s,然后升温至680℃,完成退火;

126.步骤416,在680℃,生长100nm的inp高温层,v/iii族流量比为400。

127.步骤417,在inp外延层的基础上进行超辐射发光二极管结构的外延生长。半导体超辐射发光二极管是一种光电半导体器件,基于超辐射发光现象辐射宽带光。

128.在本发明另一种实施例中,硅衬底采用(100)soi衬底,iii-v族砷化物采用gasb材料,mocvd载气为高纯度氢气,iii族有机源为高纯度三甲基镓,v族源为高纯度锑烷,反应室压力为100托尔。本实施例提供的硅基iii-v族半导体材料的制备方法的具体步骤如下:

129.步骤501,将硅衬底进行清洗,除硅衬底上的有机物、金属粒子、氧化层等杂质;

130.步骤502,将清洗完成的硅衬底进行甩干,将甩干后的硅衬底放入外延生长腔室中;

131.步骤503,将腔室温度升至750℃并保持10min,将生长室温度降低至420℃生长10nm的gasb低温层,v/iii族流量比为250;

132.步骤504,将温度升至650℃,生长200nm的gasb中温层,v/iii族流量比为100;

133.步骤505,将温度升至680℃,生长300nm的gasb高温层,v/iii族流量比为100;

134.步骤506,将温度提高到750℃保存5min,缓慢降低350℃并保持400s,然后升温至680℃,完成退火;

135.步骤507,在680℃,生长100nm的gasb高温层,v/iii流量比为100;

136.步骤508,将温度提高到750℃保存5min,缓慢降低350℃并保持400s,然后升温至680℃,完成退火;

137.步骤509,在680℃,生长100nm的gasb高温层,v/iii流量比为100;

138.步骤510,将温度降低至420℃生长10nm的gasb低温层,v/iii流量比为250;

139.步骤511,将温度升至650℃,生长200nm的gasb中温层,v/iii族流量比为100;

140.步骤512,将温度升至680℃,生长300nm的gasb高温层,v/iii族流量比为100;

141.步骤513,将温度提高到750℃保存5min,缓慢降低350℃并保持400s,然后升温至680℃,完成退火;

142.步骤514,在680℃,生长100nm的gasb高温层,v/iii族流量比为100;

143.步骤515,将温度提高到750℃保存5min,缓慢降低350℃并保持400s,然后升温至680℃,完成退火;

144.步骤516,在680℃,生长100nm的gasb高温层,v/iii族流量比为100。

145.步骤517,在gasb外延层的基础上进行量子点结构的外延生长。量子点(英语:quantum dot)是在把激子在三个空间方向上束缚住的半导体纳米结构,外延生长法是指在一种衬底材料上长出新的结晶,如果结晶足够小,就会形成量子点。根据生长机理的不同,该方法又可以细分成化学气相沉积法和分子束外延法。

146.通过以上实施例可知,iii-v半导体材料包括gap系、gaas系、inp系、gasb系半导体材料中的一种或多种,优选gaas系、inp系材料。所述的材料包括但不限于二元alp、gap、inp、alas、gaas、alsb、gasb、insb等材料,三元bgap、balp、algap、ingap、algaas、ingaas、algasb、ingasb、gaassb等材料,四元bgaasp、algaasp、ingaasp、algainas、ingaassb等材料。在此不做具体限定。

147.另外,在本发明实施例中,iii-v族半导体器件结构包括但不局限于iii-v族半导体激光器、iii-v族超辐射发光二极管、iii-v族发光二极管、iii-v族光放大器、iii-v族光探测器和iii-v族无源器件。

148.以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。