具有并联阻抗以减小测量输入阻抗的测试装置以及相关设备、系统和方法

1.优先权要求

2.本技术要求于2020年12月22日提交的、题为“具有并联阻抗以减小测量输入阻抗的测试装置以及相关设备、系统和方法(test devices having parallel impedances to reduce measurement input impedance and related apparatuses,systems,and methods)”的第17/131,383号美国专利申请的提交日的权益。

技术领域

3.本公开大体上涉及具有并联阻抗以减小测试装置的输入阻抗和电测量仪器的有效测量输入阻抗的测试装置,且更具体地涉及用于与电测量仪器一起用于验证待提供到被测装置(dut)的测试信号的测试装置。

背景技术:

4.在一些情况下,可能需要在将测试信号提供到dut之前验证待提供到dut的测试信号。例如,信号发生器可以用于生成测试信号,且电测量仪器可以用于在将测试信号提供到dut之前验证测试信号。

技术实现要素:

5.在一些实施例中,一种设备包含测试输入端、测量输出端、参考电压电位节点和并联电阻器。所述测试输入端经配置以电连接到信号发生器的信号输出端。所述测试输入端经配置以经由所述信号输出端从所述信号发生器接收测试信号。测量输出端用以电连接到电测量仪器的测量输入端。并联电阻器从测量输出端电连接到参考电压电位节点以减小流入(looking into)电测量仪器的测量输入端的有效测量输入阻抗。

6.在一些实施例中,一种系统包含被测装置(dut)和测试装置。dut包含dut输入端、dut电路系统和电连接在dut输入端与dut电路系统之间的阻尼电阻器。dut输入端具有流入dut输入端的dut输入阻抗。测试装置包含:具有大体上等于dut输入阻抗的输入阻抗的测试输入端;用以电连接到电测量仪器的测量输入端的测量输出端;以及在电测量仪器的测量输入端电连接到测试装置的测量输出端时与电测量仪器并联地电连接的并联电阻器。并联电阻器被选择以将电测量仪器的有效输入阻抗减小到大体上等于dut电路系统的dut电路系统阻抗。

7.在一些实施例中,一种测试双列直插式存储器模块(dimm)的方法包含将电测量仪器的测量输入端电连接到dimm测试装置的测量输出端。dimm测试装置包含并联电阻器,其从测量输出端电连接到参考电压电位节点以减小电测量仪器的有效测量输入阻抗。所述方法还包含:将信号发生器的信号输出端电连接到dimm测试装置的测试输入端;将测试信号从信号发生器的信号输出端提供到dimm测试装置的测试输入端;以及使用电测量仪器验证测试信号。所述方法进一步包含:使信号发生器的信号输出端与dimm测试装置的测试输入

端以电气方式断开连接;将信号发生器的信号输出端电连接到dimm的被测装置(dut)输入端;将测试信号从信号发生器的信号输出端提供到dimm的dut输入端;以及响应于测试信号而测试dimm的操作。

附图说明

8.尽管本公开利用确切地指出且清楚地主张特定实施例的权利要求进行总结,但本公开范围内的实施例的各种特征和优点可以在结合附图阅读时根据以下描述更轻松地确定,在附图中:

9.图1是根据一些实施例的用于测试dut的系统的电路示意性图示;

10.图2是根据一些实施例的示出测试图1的dut的方法的流程图;

11.图3是图1的系统的电路示意性图示,其中信号发生器电连接到测试装置;

12.图4是图1的系统的电路示意性图示,其中信号发生器电连接到dut;

13.图5是用于测试dimm的系统的电路示意性图示,所述系统是图1的系统的实例;并且

14.图6是根据一些实施例的dimm测试装置的示意性图示。

具体实施方式

15.在以下详细描述中,参考形成本公开的部分的附图,且其中借助于图示而示出其中可以实践本公开的实施例的具体实例。足够详细地描述这些实施例,使得本领域的普通技术人员能够实践本公开。然而,可以利用本文实现的其它实施例,并且可以在不脱离本公开的范围的情况下进行结构、材料和过程改变。

16.本文呈现的图示并不意图为任何特定方法、系统、装置或结构的实际视图,而是仅为用于描述本公开的实施例的理想化表示。在一些情况下,各种图式中的类似结构或组件可以保持相同或类似编号以便利读者;然而,编号的类似性不一定意味着结构或组件的大小、组成、配置或任何其它性质是相同的。

17.以下描述可以包含实例以有助于使本领域的普通技术人员能够实践所公开的实施例。术语“示例性”、“举例来说”和“例如”的使用意味着相关描述是解释性的,且虽然本公开的范围旨在涵盖实例和合法等效物,但此类术语的使用并不希望将实施例或本公开的范围限于指定的组件、步骤、特征、功能等。

18.将容易理解的是,如本文中大体描述且在图式中示出的实施例的组件可以多种多样的不同配置来布置和设计。因此,对各种实施例的以下描述并不旨在限制本公开的范围,而是仅表示各种实施例。尽管可以在图式中呈现实施例的各方面,但除非特别指示,否则图式不一定按比例绘制。

19.此外,除非本文另外规定,否则示出和描述的特定实施方案仅是实例且不应被理解为实施本公开的仅有方式。元件、电路和功能可以框图形式示出以免用不必要的细节混淆本公开。相反,除非本文另外规定,否则示出和描述的特定实施方案仅是示例性的且不应被理解为实施本公开的仅有方式。另外,各种块之间的块定义和逻辑划分是特定实施方案的示例。对于本领域的普通技术人员来说将显而易见的是,可以通过许多其它划分解决方案来实践本公开。在很大程度上,已省略关于时序考虑等的细节,其中此类细节对于完全理

解本公开是不必要的且在相关领域的普通技术人员的能力内。

20.本领域的普通技术人员将理解,可以使用各种不同技术和技法中的任一种来表示信息和信号。一些图式可以出于呈现和描述的清楚起见而将信号说明为单个信号。本领域的普通技术人员将理解,信号可以表示信号的总线,其中总线可以具有多种位宽度,且本公开可以在包含单个数据信号的任何数目的数据信号上实施。

21.结合本文公开的实施例描述的各种示意性逻辑块、模块和电路可以通过通用处理器、专用处理器、数字信号处理器(dsp)、集成电路(ic)、专用集成电路(asic)、现场可编程门阵列(fpga)或其它可编程逻辑装置、离散门或晶体管逻辑、离散硬件组件或其经设计以执行本文所描述功能的任何组合来实施或执行。通用处理器(在本文中也可以称为主机处理器或简称为主机)可以是微处理器,但在替代方案中,处理器可以是任何常规处理器、控制器、微控制器或状态机。处理器还可以实施为计算装置的组合,例如dsp和微处理器的组合、多个微处理器、结合dsp核心的一或多个微处理器,或任何其它此类配置。包含处理器的通用计算机在所述通用计算机经配置以执行与本公开的实施例有关的计算指令(例如,软件代码)时被视为专用计算机。

22.可以在描绘为流程图(flowchart)、流图(flow diagram)、结构图或框图的过程方面描述实施例。虽然流程图可以将操作动作描述为顺序过程,但这些动作中的许多可以另一顺序、并行地或大体上同时执行。此外,可以重新布置动作的次序。过程可以对应于方法、线程、函数、程序、子例程、子程序、其它结构或其组合。此外,本文中所公开的方法可以硬件、软件或两者实施。如果以软件实施,则可以将功能作为一或多个指令或代码在计算机可读媒体上存储或传输。计算机可读媒体包含计算机存储媒体和通信媒体两者,通信媒体包含有助于将计算机程序从一处传送到另一处的任何媒体。

23.本文使用例如“第一”、“第二”等标示对元件的任何提及并不限制那些元件的数量或次序,除非明确地陈述此类限制。实际上,这些标示可以在本文中用作区别两个或更多个元件或元件实例的方便方法。因此,对第一元件和第二元件的参考并不意味着此处可以采用仅两个元件或第一元件必须以某一方式在第二元件之前。另外,除非另外说明,否则一组元件可以包含一或多个元件。

24.如本文中所使用,关于给定参数、性质或条件的术语“大体上”意指并包含本领域的普通技术人员将理解的给定参数、性质或条件符合小变异度(例如,在可接受的制造容差内)的程度。借助于实例,取决于大体上符合的特定参数、性质或条件,可以至少90%符合、至少95%符合或甚至至少99%符合所述参数、性质或条件。

25.如本文中所使用,术语“端”是指电子装置的连接节点。例如,“端”可以指导电引脚、导电衬垫、导电迹线或其它导电结构,所述其它导电结构经配置以将电信号传导到电子装置和/或从电子装置传导电信号。

26.测试装置可以用以将信号发生器(例如,误码仪(bert))电连接到电测量仪器(例如,示波器),以在将测试信号提供到dut(例如,双列直插式存储器模块(dimm))之前验证测试信号。作为特定的非限制性实例,可以由bert经由dimm测试装置将可以用于应力眼图测试(stressed eye test)的测试信号提供到示波器,以在将测试信号提供到dimm之前验证测试信号。由于bert可能是相对灵敏且精确的仪器,因此在dimm测试装置的输入阻抗与dimm预期的dut输入阻抗大体上不相同的情况下,bert可能无法适当地起作用或可能甚至

会损坏。并且,如果在电连接到电测量仪器时测试装置的阻抗和电压电位不模拟dimm的阻抗和电压电位,则电测量仪器可能不会发现将提供到dimm的电路系统的相同电信号(例如,示波器可能会发现与将提供到dimm的电路系统的电信号相比具有不同偏移的电信号)。

27.dimm可以包含dut输入端与dimm电路系统之间的阻尼电阻器,所述阻尼电阻器将最终在dimm的测试期间接收电信号。因此,dimm可以具有dut输入阻抗,所述dut输入阻抗为大体上阻尼电阻器的电阻与dimm电路系统的dimm电路系统阻抗的串联组合。不利的是,示波器自身的测量输入阻抗可以大于dimm电路系统的dimm电路系统阻抗,且实际上可以与总dut输入阻抗处于相同数量级(例如,约五十欧姆(50ω))。因此,可以包含测试装置电路系统(例如,阻尼电阻器,用以模拟dimm的dut输入端处的阻尼电阻器)的串联组合与示波器的测量输入阻抗的流入dimm测试装置的输入阻抗可以大于dimm的dut输入阻抗,这相当于测试装置与dimm之间的输入阻抗不匹配。dimm测试装置的输入阻抗与dimm的dut输入阻抗的此不匹配可能会使bert发生故障或被损坏,同时尝试使用dimm测试装置和示波器验证测试信号。此外,示波器的测量输入阻抗与dimm电路系统阻抗之间的不匹配可能会使得不同电信号被传送到示波器和dimm电路系统,即使响应于相同测试信号被分别传送到dimm测试装置和dimm也是如此。

28.本文中公开的实施例减小流入电测量仪器的测量输入端的有效测量输入阻抗,且通过扩展减小将信号发生器电连接到电测量仪器的测试装置的输入阻抗以实现待提供到dut的测试信号的验证。本文中公开的实施例可以使用与电连接到电测量仪器的测量输出端并联的并联电阻器,以将电测量仪器的有效测量输入阻抗和测试装置的输入阻抗减小到分别与dut的dut电路系统阻抗和dut输入阻抗大体上相同。

29.在一些实施例中,dimm测试装置包含一或多个通道,所述一或多个通道中的每一通道包含与并联电阻器和连接器(例如,微型-smp连接器)的并联组合串联的阻尼电阻器,以用于将dimm测试装置电连接到示波器。因此,本文中公开的实施例实现来自bert的测试信号的验证以用于dimm的应力眼图测试。

30.在一些实施例中,一种设备包含测试输入端、测量输出端、参考电压电位节点和并联电阻器。所述测试输入端经配置以电连接到信号发生器的信号输出端。所述测试输入端经配置以经由所述信号输出端从所述信号发生器接收测试信号。测量输出端经配置以电连接到电测量仪器的测量输入端。并联电阻器从测量输出端电连接到参考电压电位节点以减小流入电测量仪器的测量输入端的有效测量输入阻抗。

31.在一些实施例中,一种系统包含dut和测试装置。dut包含dut输入端、dut电路系统和电连接在dut输入端与dut电路系统之间的阻尼电阻器。dut输入端具有流入dut输入端的dut输入阻抗。测试装置包含测试输入端,其具有大体上等于dut输入阻抗的输入阻抗。测试装置还包含测量输出端,以电连接到电测量仪器的测量输入端。测试装置进一步包含在电测量仪器的测量输入端电连接到测试装置的测量输出端时与电测量仪器并联地电连接的并联电阻器。并联电阻器被选择以将电测量仪器的有效输入阻抗减小到大体上等于dut电路系统的dut电路系统阻抗。

32.在一些实施例中,一种测试dimm的方法包含将电测量仪器的测量输入端电连接到dimm测试装置的测量输出端。dimm测试装置包含并联电阻器,其从测量输出端电连接到参考电压电位节点以减小电测量仪器的有效测量输入阻抗。所述方法还包含将信号发生器的

信号输出端电连接到dimm测试装置的测试输入端,以及将测试信号从信号发生器的信号输出端提供到dimm测试装置的测试输入端。所述方法进一步包含:使用电测量仪器验证测试信号;使信号发生器的信号输出端与dimm测试装置的测试输入端以电气方式断开连接;以及将信号发生器的信号输出端电连接到dimm的输入端。另外,所述方法包含将测试信号从信号发生器的信号输出端提供到dimm的输入端,以及响应于测试信号而测试dimm的操作。

33.图1是根据一些实施例的用于测试dut 102的系统100的电路示意性图示。系统100包含dut 102、测试装置104、信号发生器106和电测量仪器108。dut 102可以包含待测试的电子装置。作为非限制性实例,dut 102可以包含待进行应力眼图测试的dimm。dut 102包含:dut输入端140;dut中间节点150;dut参考电压电位节点154(例如,用以接收参考电压电位vref);dut电路系统(未示出),其具有电连接在dut中间端150与参考电压电位节点154之间的dut电路系统阻抗148;以及阻尼电阻器146,其电连接在dut输入端140与dut中间节点150之间。

34.信号发生器106经配置以将测试信号提供到dut 102,作为dut 102的测试的一部分。作为非限制性实例,信号发生器106可以包含具有信号输出阻抗130的驱动器144。响应于提供到dut的测试信号,可以在dut电路系统阻抗148两端施加dut信号vdut。电测量仪器108经配置以在测试信号被提供到dut 102之前,间接测量并验证响应于来自信号发生器106的测试信号而预期的dut信号vdut。测试装置104经配置以将来自信号发生器106的测试信号传送到电测量仪器108,以使得电测量仪器108能够测量并验证dut信号vdut。

35.dut输入端140经配置以电连接到信号发生器106的信号输出端114并且从信号发生器106的信号输出端114接收测试信号。dut输入端140具有流入dut输入端140的dut输入阻抗142。类似地,测试装置104包含测试输入端112,以电连接到信号发生器106的信号输出端114且从信号发生器106的信号输出端114接收测试信号。测试输入端112具有流入测试输入端112的输入阻抗132。输入阻抗132大体上等于dut输入阻抗142。因此,无论信号发生器106的信号输出端114是电连接到dut 102的dut输入端140还是测试装置104的测试输入端112,信号发生器106都将看到大体上相同的输入阻抗。作为非限制性实例,dut输入阻抗142和输入阻抗132可以各自为大体上五十欧姆(50ω)。信号发生器106的信号输出端114经配置以选择性地电连接到dut 102的dut输入端140和测试装置104的测试输入端112。因此,信号发生器106经配置以选择性地将测试信号提供到dut输入端140和测试输入端112。

36.测试装置104包含测量输出端116,以电连接到电测量仪器108的测量输入端118。在一些实施例中,测试装置104还包含参考电压电位端136,以电连接到电测量仪器108的参考电压电位输入端138。参考电压电位端136电连接到参考电压电位节点120。电测量仪器108具有流入测量输入端118的测量输入阻抗128(即,当与测量输出端116断开连接时)。作为非限制性实例,测量输入阻抗128可以为大体上五十欧姆(50ω)。因此,测量输入阻抗128可以大于dut电路系统阻抗148,且可以与dut输入阻抗142处于相同数量级(例如,大体上相同)。

37.测试装置104还包含电连接在测试输入端112与测量输出端116之间的电路系统126。作为非限制性实例,电路系统126可以包含阻尼电阻器124。测试装置104进一步包含从测量输出端116电连接到测试装置104的参考电压电位节点120的并联电阻器122。作为非限制性实例,参考电压电位节点120可经配置以接收参考电压电位(例如,1.1伏,以模拟dimm

的电源电压电位)。作为非限制性实例,参考电压电位节点120可以电连接到vref的可编程端接电压电位。提供到参考电压电位节点120的参考电压电位vref可以与提供到dut 102的参考电压电位节点154的参考电压电位vref大体上相同。然而,参考电压电位节点120(和dut 102的参考电压电位节点154)可以电连接到接地节点、电源节点或任何其它参考电压电位节点。在并联电阻器122从测量输出端116电连接到参考电压电位节点120的情况下,并联电阻器122可以与电测量仪器108的测量输入阻抗128并联地电连接。因此,流入测试输入端112的输入阻抗132大体上为与测量输入阻抗128与并联电阻器122的并联组合串联的电路系统126的阻抗(例如,阻尼电阻器124的电阻)。可以选择并联电阻器122以将输入阻抗132减小到大体上等于dut输入阻抗142。并且,可以选择并联电阻器122以将流入电测量仪器108的测量输入端118的有效测量输入阻抗152(即,在测量输入端118电连接到测量输出端116的情况下)减小到大体上等于dut 102的dut电路系统阻抗148。

38.在不存在并联电阻器122的情况下,流入测试输入端112的输入阻抗132将大体上为与电测量仪器108的测量输入阻抗128串联的电路系统126的阻抗(例如,阻尼电阻器124的电阻)。假设电测量仪器108的测量输入阻抗128与dut 102的dut输入阻抗142大致相同,则阻尼电阻器124和测量输入阻抗128的串联组合将产生大体上比dut输入阻抗142大电路系统126的电阻(例如,阻尼电阻器124的电阻)的输入阻抗132。作为非限制性实例,作为dut 102的dimm的dut输入阻抗142可以为大体上50ω,作为电测量仪器108的示波器的测量输入阻抗128可以为大体上50ω,并且阻尼电阻器124的电阻可以为大体上15ω。因此,在不存在并联电阻器122的情况下,在电测量仪器108电连接到测试装置104的情况下,流入测试输入端112的输入阻抗132将为大体上65ω。假设作为信号发生器106的bert被设计成将测试信号提供到作为dut 102的dimm——所述dimm具有为大体上50ω的dut输入阻抗142,则在不存在并联电阻器122的情况下,测试装置104的65ω的输入阻抗132可以在信号发生器106将测试信号提供到测试装置104时引起信号发生器106的故障或损坏。

39.并且,在不存在并联电阻器122的情况下,流入电测量仪器108的测量输入端118的有效测量输入阻抗152将大于dut电路系统阻抗148(例如,有效测量输入阻抗152可以为大体上50ω且dut电路系统阻抗148可以为大体上35ω)。由于有效测量输入阻抗152与dut电路系统阻抗148之间的不匹配,测量输入阻抗128两端的测量信号vmeas可以不同于dut信号vdut。因此,电测量仪器可以不测量与dut信号vdut大体上相同的信号,所述dut信号vdut将响应于测试信号而被施加到dut电路系统阻抗148。

40.然而,与不存在并联电阻器122的情况下测试装置104的输入阻抗132的值相比,包含并联电阻器122会减小测试装置104的输入阻抗132。如先前所论述,假设阻尼电阻器124具有为大体上15ω的电阻且测量输入阻抗128为大体上50ω,则在不存在并联电阻器122的情况下,测试装置104的输入阻抗132将为大体上65ω(15ω 50ω)。包含并联电阻器122且假设并联电阻器122具有120ω的电阻,则测试装置104的输入阻抗132为大体上50ω(阻尼电阻器124的15ω与电测量仪器108的测量输入阻抗128的50ω与并联电阻器122的120ω的并联组合串联,或换句话说15ω 50ω//120ω~50ω)。因此,包含并联电阻器122使得输入阻抗132能够与dut 102的dut输入阻抗142大体上相同,即使在阻尼电阻器124的电阻与电测量仪器108的测量输入阻抗128(例如,测量输入阻抗128的实际分量)的总和大于dut 102的dut输入阻抗142的情况下也是如此。

41.并且,包含并联电阻器122会将有效测量输入阻抗152减小到与dut电路系统阻抗148大体上相同。因此,假设阻尼电阻器124的电阻与阻尼电阻器146的电阻大体上相同,则由电测量仪器108测量的测量信号vmeas与dut电路系统阻抗148处的dut信号vdut大体上相同。作为非限制性实例,阻尼电阻器124和阻尼电阻器146可以具有为大体上15ω的电阻,并且有效测量阻抗152和dut电路系统阻抗148可以为大体上35ω(例如,120ω的并联电阻器122与50ω的测量输入阻抗的并联组合为大体上35ω)。

42.在一些实施例中,电测量仪器108包含用户界面110。作为非限制性实例,电测量仪器108可以包含示波器,且用户界面110可以包含经配置以显示由信号发生器106提供的测试信号的波形的电子显示器。用户界面110还可以包含一或多个按钮、一或多个标度盘、一或多个滑块、触摸屏界面、用于提供音频警报的音频输出装置、其它输入/输出装置或其组合,以使得用户能够利用电测量仪器108来验证测试信号。

43.在一些实施例中,流入测试输入端112的输入阻抗132大体上等于流入信号发生器106的信号输出端114的信号输出阻抗130。在此类实施例中,测试装置104的输入阻抗132可以匹配信号发生器106的信号输出阻抗130。

44.在一些实施例中,有效测量输入阻抗152与dut电路系统阻抗148大体上相同。在此类实施例中,由电测量仪器108测量的测量信号vmeas与dut信号vdut大体上相同。

45.在一些实施例中,测试装置104包含电连接器134,其经配置以将测试装置104的测量输出端116和参考电压电位端136分别以可拆卸方式电连接到电测量仪器108的测量输入端518和参考电压电位输入138。作为非限制性实例,电连接器134可以包含超小型推接式(smp)连接器。因此,测试装置104可经配置以电连接到电测量仪器108而无需介于中间的高阻抗探针。

46.在一些实施例中,电测量仪器可以包含其自身的测量参考电压电位节点156,其经配置以接收参考电压电位vref(即,在参考电压电位节点120和154处大体上相同的参考电压电位vref)。在此类实施例中,电测量仪器可以不包含参考电压电位输入端138,且测试装置104可以不包含参考电压电位端136。

47.应注意,信号发生器106的信号输出阻抗130、电测量仪器108的测量输入阻抗128和dut 102的dut电路系统阻抗148在图1中描绘为电连接在端和/或节点(例如,信号输出端114,测量输入端118,dut中间节点150,参考电压电位节点120、154、156以及dut输入端140、接地端等)之间的电阻器。然而,信号输出阻抗130、测量输入阻抗128和dut电路系统阻抗148仅为信号发生器106、电测量仪器108和dut电路系统的实际电路系统的小型信号等效电路模型,且不应被解释为表示信号发生器106、电测量仪器108和dut电路系统的实际电路系统。

48.图2是根据一些实施例的示出测试图1的dut 102的方法200的流程图。共同参考图1和图2,在操作202,方法200包含将电测量仪器108的测量输入端118电连接到测试装置104(例如,dimm测试装置)的测量输出端116。如先前所论述,测试装置104包含从测量输出端116电连接到参考电压电位节点120的并联电阻器122,以减小电测量仪器的有效测量输入阻抗152。因此,输入阻抗132可以大体上等于dut 102的dut输入阻抗142,且有效测量输入阻抗152可以大体上等于dut电路系统阻抗148。在一些实施例中,将电测量仪器108的测量输入端118电连接到测试装置104的测量输出端116包含将示波器(例如,图5的示波器508)

电连接到dimm测试装置(例如,图5的dimm测试装置504)的测量输出端(例如,图5的测量输出端516)。在一些实施例中,将示波器电连接到dimm测试装置的测量输出端包含将示波器直接电连接到dimm测试装置的测量输出端,而无需介于中间的高阻抗探针。

49.在操作204,方法200包含将信号发生器106的信号输出端114电连接到测试装置104的测试输入端112。图3示出了信号发生器106的电连接到测试装置104的测试输入端112的信号输出端114。在一些实施例中,将信号发生器106的信号输出端114电连接到测试装置104的测试输入端112包含将bert(例如,图5的bert 506)电连接到dimm测试装置(例如,dimm测试装置504)的测试输入端(例如,图5的测试输入端512)。

50.图3是图1的系统100的电路示意性图示,其中信号发生器106电连接到测试装置104。共同参考图2和图3,在操作206,方法200包含将测试信号302从信号发生器106的信号输出端114提供到测试装置104的测试输入端112。

51.在操作208,方法200包含使用电测量仪器108来验证测试信号302。验证测试信号302可以包含测量和验证测量信号vmeas,其大体上与预期的dut信号vdut相同。在操作210,方法200包含使信号发生器106的信号输出端114与测试装置104的测试输入端112以电气方式断开连接。在操作212,方法200包含将信号发生器106的信号输出端114电连接到dimm的dut输入端140。图4示出了信号发生器106的电连接到dut 102的dut输入端140的信号输出端114。

52.图4是图1的系统100的电路示意性图示,其中信号发生器106电连接到dut 102。共同参考图2和图4,在操作214,方法200包含将测试信号302从信号发生器106的信号输出端114提供到dut 102的测试输入端。在操作216,方法200包含响应于测试信号302而测试dut 102的操作。作为非限制性实例,测试dut 102的操作可以包含对dimm(例如,图5的dimm 502)执行应力眼图测试。

53.如先前所论述,在一些实施例中,dut 102可以包含dimm,测试装置104可以包含dimm测试装置,信号发生器106可以包含bert,且电测量仪器108可以包含示波器。图5示出了此实施例的实例。

54.图5是用于测试dimm 502的系统500的电路示意性图示,所述系统是图1的系统100的实例。系统500包含dimm 502、dimm测试装置504、bert 506和示波器508,它们类似于上文参考图1、图3和图4所论述的dut 102、测试装置104、信号发生器106和电测量仪器108。例如,dimm 502包含dut输入端540、阻尼电阻器548、具有dimm电路系统阻抗550的dimm电路系统、参考电压电位节点556以及流入dut输入端540的dut输入阻抗542,它们类似于参考图1、图3和图4所论述的dut输入端140、阻尼电阻器146、具有dut电路系统阻抗148的dut电路系统、参考电压电位节点154和dut输入阻抗142;dimm测试装置504包含测试输入端512、测量输出端516、参考电压电位端536、smp连接器534、电路系统526、参考电压电位节点520、并联电阻器522和流入测试输入端512的输入阻抗532,它们类似于参考图1、图3和图4所论述的测试输入端112、测量输出端116、参考电压电位端136、电连接器134、电路系统126、参考电压电位节点120、并联电阻器122和输入阻抗132;bert 506包含信号输出端514、驱动器546和流入信号输出端514的信号输出阻抗530,它们类似于上文参考图1、图3和图4所论述的信号输出端114、驱动器144和信号输出阻抗130;并且示波器508包含用户界面510、测量输入端518、参考电压电位输入端538、流入测量输入端518的测量输入阻抗528和流入测量输入

端518的有效测量输入阻抗534,它们类似于上文参考图1、图3和图4所论述的用户界面110、测量输入端118、参考电压电位输入端138、测量输入阻抗128和有效测量输入阻抗152。

55.bert 506、dimm测试装置504和示波器508可以用于测试dimm 502,以如参考图2的方法200所论述的类似方式。例如,bert 506可以先将测试信号544提供到dimm测试装置504以启用示波器508来(例如,使用测量信号vmeas)验证测试信号544或使得系统500的用户能够验证测试信号544,之后将测试信号544提供到dimm 502(例如,从而使得将dimm信号vdimm施加到具有dimm电路系统阻抗550的dimm电路系统)。作为非限制性实例,测试信号544可以是用于应力眼图测试的测试信号。

56.由于dimm测试装置504包含并联电阻器522,因此流入dimm测试装置504的测试输入端512的输入阻抗532可以大体上等于流入dimm 502的dut输入端540的dut输入阻抗542。因此,如果流入测试输入端512的输入阻抗532与流入dut输入端540的dut输入阻抗542大体上不同,则bert 506可以恰当地操作且避免原本可能会(例如,对bert 506的收发器)造成的损坏。并且,有效测量输入阻抗554可以大体上等于dimm电路系统阻抗550。因此,示波器处的测量信号vmeas可以与dimm 502的dimm电路系统处预期的dimm信号vdimm大体上相同。

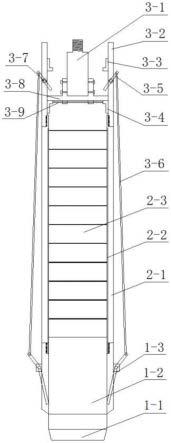

57.图6是根据一些实施例的dimm测试装置600的示意性图示。dimm测试装置600是三通道dimm测试装置的实例。dimm测试装置600包含测试输入端610a-610c,所述测试输入端中的每一者经配置以电连接到信号发生器的信号输出端(例如,分别为图1和图5的信号发生器106或bert 506的信号输出端114或514)。dimm测试装置600还包含阻尼电阻器602a-602c和测量输出端614a-614c。阻尼电阻器602a从测试输入端610a-610c中的相应一者电连接到测量输出端614a-614c中的相应一者(即,阻尼电阻器602a从测试输入端610a电连接到测量输出端614a,阻尼电阻器602b从测试输入端610b电连接到测量输出端614b,且阻尼电阻器602c从测试输入端610c电连接到测量输出端614c)。

58.dimm测试装置600进一步包含参考电压电位节点608和电连接在其相应测量输出端614a-614c与参考电压电位节点608之间的smp连接器606a-606c(即,smp连接器606a电连接在测量输出端614a与参考电压电位节点608之间,smp连接器606b电连接在测量输出端614b与参考电压电位节点608之间且smp连接器606c电连接在测量输出端614c与参考电压电位节点608之间)。作为非限制性实例,可以将为大体上1.1伏的参考电压电位提供(例如,参考电压电位可以是可编程的端接电压电位)到参考电压电位节点608以模拟可以在dimm上预期的状况。smp连接器606a-606c中的每一者经配置以电连接到电测量仪器(例如,图1的电测量仪器108,图5的示波器508)。作为非限制性实例,电测量仪器可以包含多个输入通道,并且smp连接器606a-606c中的两者或更多者可以同时电连接到电测量仪器以验证多个测试信号。

59.dimm测试装置600还包含并联电阻器604a-604c。并联电阻器604a-604c从所述dimm测试装置的相应测量输出端614a-614c电连接到参考电压电位节点608(即,并联电阻器604a从测量输出端614a电连接到参考电压电位节点608,并联电阻器604b从测量输出端614b电连接到参考电压电位节点608,且并联电阻器604c从测量输出端614c电连接到参考电压电位节点608)。因此,并联电阻器604a-604c与电连接到smp连接器606a-606c的一或多个电测量仪器的测量输入阻抗并联地电连接,从而减小对应的有效测量输入阻抗和输入阻抗612a-612c。

60.作为非限制性实例,电连接到smp连接器606a-606c的一或多个电测量仪器的测量输入阻抗可以为大体上50ω,阻尼电阻器602a-602c的电阻可以为大体上15ω,且并联电阻器604a-604c的电阻可以为大体上120ω。因此,流入测试输入端610a-610c中的每一者的输入阻抗612a-612c可以为大体上50ω。并且,连接到smp连接器606a-606c的电测量仪器的有效测量输入阻抗可以减小到大体上35ω。因此,dimm测试装置600的通道中的每一者可以适合用于测试待施加到dimm的测试信号,所述dimm具有为大体上50ω的输入阻抗和为大体上35ω的dimm电路系统阻抗。

61.如本公开中所使用,术语“模块”或“组件”可以指经配置以执行可存储在计算系统的通用硬件(例如,计算机可读媒体、处理装置等)上和/或由其执行的模块或组件和/或软件对象或软件例程的动作的特定硬件实施方案。在一些实施例中,本公开中描述的不同组件、模块、引擎和服务可以实施为在计算系统上执行(例如,作为单独线程)的对象或过程。虽然本公开中描述的系统和方法中的一些大体上被描述为在(存储在通用硬件上和/或由其执行的)软件中实施,但特定硬件实施方案或软件与特定硬件实施方案的组合也是可能的和预期的。

62.如本公开中所使用,参考多个元件的术语“组合”可以包含所有元件的组合或一些元件的各种不同子组合中的任一种。例如,短语“a、b、c、d或其组合”可以指以下任一者:a、b、c或d;a、b、c和d中的每一者的组合;以及a、b、c或d的任何子组合:例如a、b和c;a、b和d;a、c和d;b、c和d;a和b;a和c;a和d;b和c;b和d;或c和d。

63.本公开中且尤其在所附权利要求书(例如,所附权利要求书的主体)中所使用的术语通常意图为“开放”术语(例如,术语“包含(including)”应解释为“包含(但不限于)”,术语“具有”应解释为“至少具有”,术语“包含(includes)”应解释为“包含(但不限于)”等)。

64.另外,如果意图特定数目的所引入权利要求叙述,则将在所述权利要求中明确叙述这种意图,且在不存在这种叙述的情况下,不存在这种意图。例如,为了帮助理解,以下所附权利要求可能含有引入性短语“至少一个”和“一或多个”的使用以引入权利要求陈述。然而,此类短语的使用不应解释为暗示通过不定冠词“一(a/an)”引入权利要求叙述将含有如此引入的权利要求叙述的任何特定权利要求限于仅含有一个此类叙述的实施例,即使在同一个权利要求包含介绍性短语“一或多个”或“至少一个”和例如“一”的不定冠词时也如此(例如,“一”应被解译为意味“至少一个”或“一或多个”);这同样适用于使用定冠词来引入权利要求叙述的情况。

65.另外,即使明确陈述了所引入的权利要求陈述的特定数目,本领域的技术人员将认识到此类陈述通常应当解释为意指至少所陈述的数目(例如,在没有其它修饰语的情况下仅陈述“两个陈述”通常意味着至少两个陈述,或两个或更多个陈述)。此外,在使用类似于“a、b和c等中的至少一个”或“a、b和c等中的一或多个”的惯例的那些情况下,一般来说,此类结构意图仅包含a、仅包含b、仅包含c、包含a和b、包含a和c、包含b和c或包含a、b和c等。

66.另外,应理解,无论在描述、权利要求书还是附图中,呈现两个或更多个替代术语的任何转折性词语或短语预期包含所述术语中的一个、所述术语中的任一个或这两个术语的可能性。例如,短语“a或b”应理解为包含“a”或“b”或“a和b”的可能性。

67.虽然本文已相对于某些示出的实施例描述了本公开,但本领域的普通技术人员将认识和了解本发明不限于此。实际上,在不脱离如下文所要求的本发明的范围及其合法等

效物的情况下,可以对所说明和描述的实施例作出许多添加、删除和修改。另外,来自一个实施例的特征可以与另一个实施例的特征组合,同时仍然涵盖在发明人所预期的本发明的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。