一种基于pe架构通道的卷积神经网络加速器

技术领域

1.本发明涉及卷积神经网络技术领域,更具体地说,它涉及一种基于pe架构通道的卷积神经网络加速器。

背景技术:

2.卷积神经网络以其强大的表征能力,在目标识别、自动驾驶及人工智能等领域得到了广泛的应用,成为了深度学习领域重要的算法之一。随着算法地不断演进,卷积神经网络的网络结构变得越来越深,给部署卷积神经网络的设备带来极大挑战。卷积神经网络中的卷积运算占据了整个网络90%以上的运算量,卷积神经网络加速器的关键组件是处理卷积运算的功能单元。

3.目前,卷积神经网络加速器通常采用脉动阵列结构,如图1所示。该结构由功能相同的运算单元(pe)组成矩阵形式,每个运算单元的功能为进行乘加运算,并设计相应的缓存和控制逻辑。该架构运算过程如下:1) 权值广播:将阵列中的每一行pe分成一组,权值参数按行广播到各组中,各组中的pe共用同一个权值参数;2)输入特征:将阵列中对角线上pe划分成一组,输入特征按行输入到各组中,各组内的pe共用同一个输入特征值;3)输出结果:将整列中的每一列pe划分成一组,将各组内每个pe的计算结果相加,即可得到卷积计算的中间结果。该方案主要侧重点在于能效,主要体现在数据复用方面,首先权值参数广播到网络中,存储到每个pe的缓存中,直到对应该权值参数的所有输入特征数据都输入完之后才更换,体现了权值参数的复用;其次,输入特征按行输入后,每个卷积的输入特征有重叠,体现了输入特征的复用;脉动阵列结构具有设计简单而规则、容易实现高并行性,且运算单元间通信比较简单的优势,但这种结构也存在明显的缺点,主要包括:1)采用脉动阵列结构时,运算单元(pe)易出现闲置率较高的情况,进而导致降低加速器的效率;2)采用脉动阵列结构时,由于需要带宽的成比例增加来维持所需要的加速倍数,因而脉动阵列的可扩展性差;卷积神经网络不仅局限于网络架构,由于其基于硬件进行实现,并非所有硬件都具有类似nvidia图像处理器或大型专用处理器的算力,其所能够输入的图像大小受限。

技术实现要素:

4.本发明提供一种基于pe架构通道的卷积神经网络加速器,解决相关技术中的技术问题。

5.根据本发明的一个方面,提供了一种基于pe架构通道的卷积神经网络加速器,包括:运动检测模块,其用于检测与视频图像中的运动对象相对应的候选图像区域;第一cnn模块,其使用具有第一图像尺寸的滑动窗口处理运动检测模块检测到的候选图像区域,并在候选图像区域内生成第一人脸窗口;第一图像尺寸在第一cnn模块的最大输入图像尺寸与最小输入尺寸之间;

第二cnn模块,其使用具有第二图像尺寸的滑动窗口处理运动检测模块检测到的候选图像区域,并在候选图像区域内由第一人脸窗口划分的第一子区域内生成第二人脸窗口;第三cnn模块,其使用具有第三图像尺寸的滑动窗口处理运动检测模块检测到的候选图像区域,并在候选图像区域内由第二人脸窗口划分的第二子区域内生成第三人脸窗口;第一cnn模块、第二cnn模块、第三cnn模块均采用硬件cnn模块,并且第一cnn模块、第二cnn模块与第三cnn模块耦合;第三图像尺寸大于硬件cnn模块的最大输入尺寸;图像分割模块,其连接运动检测模块以及第一cnn模块,用于处理运动检测模块输出的候选图像区域获得图像金字塔,图像金字塔包含不同分辨率的图像集,图像分割模块还用于将图像金字塔的图像集中的图像分割为输入第一cnn模块的图像块,图像块的大小小于硬件cnn模块的最大输入尺寸;所述硬件cnn模块包括一个以上的cnn子模块,cnn子模块包括至少一个以上的n个pe运算单元,n个pe运算单元并行运算;一个pe运算单元输出一个输出特征图,n个pe运算单元同时输出n个输出特征图。

6.进一步地,所述第一图像尺寸是基于所述硬件cnn模块的最小输入尺寸成正比。

7.进一步地,所述第一图像尺寸与所述硬件cnn模块的最小输入尺寸相同。

8.进一步地,所述pe运算单元包括一个以上的n个乘法器以及一组加法树,其中n个乘法器分别接收n个输入通道的输入特征数据以及所述输入特征数据对应的权值参数,并进行卷积运算,加法树用于对所述pe运算单元的一个以上的n个乘法器的卷积运算的结果进行累加运算获得输出特征图。

9.进一步地,所述输入特征数据、权值参数、输出特征谱存储于缓存中,其中输入特征数据对应于输入特征谱缓存,输入特征谱缓存包含至少一个以上的a个地址空间,其中一个地址空间对应的存储输入特征谱的一个位置的输入特征数据,并且每个地址空间对应的输入特征谱的一个位置的输入特征数据对应于n个输入通道进行划分;其中权值参数对应于权值参数缓存,权值参数缓存包含至少一个以上的b个地址空间,其中一个地址空间对应的存储权值参数中一个卷积核的数据,并且每个地址空间对应的存储权值参数中一个卷积核的数据对应于n个输入通道进行划分;所述输出特征谱对应于输出特征谱缓存,输出特征谱缓存包含至少一个以上的c个地址空间,其中一个地址空间对应的存储n个输出特征谱的同一个位置的输出特征,并且每个地址空间对应的存储的n个输出特征谱的同一个位置的输出特征对应于n个pe运算单元进行划分。

10.进一步地,所述n个pe运算单元中的一个pe运算单元分为至少一个以上的n个时段进行运算,在一个时段的运算中pe运算单元输入一组权值参数以及对应于所述权值参数的输入特征数据。

11.进一步地,所述第三cnn模块包括:输入模块,其用于将第三cnn模块输入的大于第三cnn模块最大输入尺寸的图像块分割为尺寸小于第三cnn模块最大输入尺寸的a个子图像;

三个依次串联的卷积层以及池化层,卷积层与池化层交叉分布,池化层为最大池化层,最后一个池化层输出a组特征图;合并模块,其用于将最后一个池化层输出a组特征图合并之后得到二维的合并特征图集合,输出到最终决策模块;最终决策模块包括重建模块以及分类模块,重建模块接收到二维的合并特征图集合,将二维的合并特征图集合合并和重新组织为一维向量,分类模块对所述一维向量处理获得人脸检测决策。

12.进一步地,所述最后一个池化层输出的a组特征图为三维特征图。

13.进一步地,所述第三cnn模块在候选图像区域内由第二人脸窗口划分的第二子区域内基于第三图像尺寸生成具有第三图像尺寸的第三图像块集合,并且基于第四图像尺寸将第三图像块集合的每一个子图像划分为小于第三cnn模块的最大输入大小的第四图像块;每一个子图像划分数量相同的a组第四图像块。

14.进一步地,所述第三cnn模块对a组第四图像块进行卷积以及池化获得a组特征图,将最后一个池化层输出a组特征图合并之后得到二维的合并特征图集合,并基于二维的合并特征图集合生成人脸检测决策。

15.本发明的有益效果在于:本发明能够基于输入图像尺寸小的小型的输入硬件cnn模块处理高像素的图像,并且对于硬件cnn模块的架构进行优化,使其能够并行加速卷积,能够同时保证图像处理的速率。

附图说明

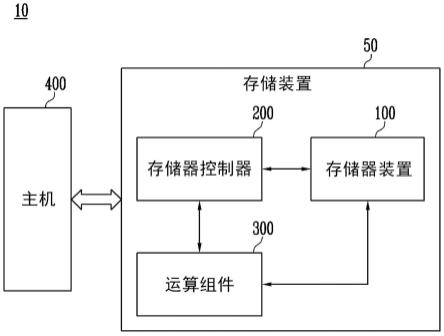

16.图1是本发明实施例的硬件cnn模块的模块示意图;图2是本发明实施例的硬件cnn模块的架构示意图;图3是现有技术中用于处理高分辨率输入图像的基于完整图像的常规的cnn系统200的框图;图4是本发明实施例的基于子图像的cnn系统的框图;图5是本发明实施例的应用基于pe架构通道的卷积神经网络加速器的人脸检测系统的框图;图6是本发明实施例的第一级cnn的框图;图7是本发明实施例的第二级cnn的框图;图8是本发明实施例的第三级cnn的框图一;图9是本发明实施例的用于46x46图像块的示例性输入图像分割方案;图10是本发明实施例的第三级cnn的框图二;图11是本发明实施例的最终决策模块的框图;图12是本发明实施例的硬件cnn模块的架构示意图;图13是本发明实施例的硬件cnn模块的 pe运算单元的内部结构图;图14是本发明实施例的硬件cnn模块的输入特征谱的存储方式示意图;图15是本发明实施例的硬件cnn模块的卷积核在权值参数缓存中的存储方式示意

图;图16是本发明实施例的硬件cnn模块的一个pe的时段1的运算流程示意图;图17是本发明实施例的硬件cnn模块的一个pe的时段2的运算流程示意图;图18是本发明实施例的硬件cnn模块的一个pe的时段3的运算流程示意图;图19是本发明实施例的硬件cnn模块的一个pe的时段4的运算流程示意图;图20是本发明实施例的硬件cnn模块的一个pe的时段5的运算流程示意图;图21是本发明实施例的硬件cnn模块的一个pe的时段6的运算流程示意图;图22是本发明实施例的硬件cnn模块的一个pe的时段7的运算流程示意图;图23是本发明实施例的硬件cnn模块的一个pe的时段8的运算流程示意图;图24是本发明实施例的硬件cnn模块的一个pe的时段9的运算流程示意图;图25是本发明实施例的n个pe并行计算,并行输出n个通道的计算结果的流程图;图26是本发明实施例的输出特征谱的存储方式示意图。

17.图中:常规的cnn系统200、基于子图像的cnn系统210、输入模块212、第一处理模块220、合并模块222、第二处理模块224、a输入图像202、a子图像204、应用基于pe架构通道的卷积神经网络加速器的人脸检测系统300、视频图像302、人脸检测决策316、运动检测模块304、图像分割模块306、第一级cnn 308、第二级cnn 310、第三级cnn 312、最终决策模块314、b输入模块802、b子图像804、b合并模块808、重建模块902。

具体实施方式

18.现在将参考示例实施方式讨论本文描述的主题。应该理解,讨论这些实施方式只是为了使得本领域技术人员能够更好地理解从而实现本文描述的主题,并非是对权利要求书中所阐述的保护范围、适用性或者示例的限制。可以在不脱离本说明书内容的保护范围的情况下,对所讨论的元素的功能和排列进行改变。各个示例可以根据需要,省略、替代或者添加各种过程或组件。例如,所描述的方法可以按照与所描述的顺序不同的顺序来执行,以及各个步骤可以被添加、省略或者组合。另外,相对一些示例所描述的特征在其它例子中也可以进行组合。

19.在本实施例中提供了一种基于pe架构通道的卷积神经网络加速器,该基于pe架构通道的卷积神经网络加速器,包括:运动检测模块,其用于检测与视频图像中的运动对象相对应的候选图像区域;第一cnn模块,其使用具有第一图像尺寸的滑动窗口处理运动检测模块检测到的候选图像区域,并在候选图像区域内生成第一人脸窗口;第一图像尺寸在第一cnn模块的最大输入图像尺寸与最小输入尺寸之间;第二cnn模块,其使用具有第二图像尺寸的滑动窗口处理运动检测模块检测到的候选图像区域,并在候选图像区域内由第一人脸窗口划分的子区域内生成第二人脸窗口;第三cnn模块,其使用具有第三图像尺寸的滑动窗口处理运动检测模块检测到的候选图像区域,并在候选图像区域内由第二人脸窗口划分的子区域内生成第三人脸窗口;在本实施例中,第一cnn模块、第二cnn模块、第三cnn模块均通过硬件cnn模块实现并耦合,也即第一cnn模块、第二cnn模块、第三cnn模块均是基于硬件实现而并非是软件。

20.在本实施例中,第一图像尺寸与硬件cnn模块的最小输入尺寸基本相同;

第三图像尺寸大于硬件cnn模块的最大输入尺寸;第一图像尺寸、第二图像尺寸、第三图像尺寸依次增大;在本实施例中,运动检测模块采用背景减法模块检测候选图像区域;在本实施例中提供了一种硬件cnn模块,如图1-2所示,硬件cnn模块包括第一cnn子模块和第二cnn子模块;图1中仅是一种示例,硬件cnn模块也可以包括三个以上的cnn子模块。

21.第一cnn子模块包括串联连接的多个conv(卷积)层、relu层(附图中未示出)和pool(池化)层;每个conv层使用一组卷积核从输入图像中提取特定的特征集;每个conv层之后连接relu层以及pool层,他们由对应的conv层创建;pool(池化)层基于局部相关性的思想,通过从局部相关的一组元素中进行采样或信息聚合,从而得到新的元素值。通常我们用到两种池化进行下采样:(1)最大池化(max pooling)。

22.从局部相关元素集中选取最大的一个元素值。

23.(2)平均池化(average pooling)。

24.从局部相关元素集中计算平均值并返回;第二cnn子模块包括多个串联的fc层(全连接层)和relu层,每个fc层(例如第二cnn子模块中的fc(1)层)都配置为执行矩阵乘法。每个fc层(最后一个fc层除外)后面都跟着一个相应的relu层(附图中未示出);在第二cnn子模块的最后一个fc层(如图的fc(n)层)连接决策模块(也未示出),决策模块基于第二cnn子模块的最后一个fc层的输出生成硬件cnn模块的输出。

25.在一个实施例中,第二cnn子模块包括3到8个fc层和relu层,而第一子模块cnn包括1到8个conv层、relu和pool层;在上述的实施例中,relu层都作为应用relu激活函数,用于将将非线性特性引入cnn网络;在一个实施例中,每个conv层中的卷积核的数量最多为50,并且仅允许3

×

3大小的卷积核。此外,卷积步长固定为1,不使用零填充。

26.在一个实施例中,第一cnn子模块的pool层使用最大池化的方法来从滤镜图像的2x2区域的每一个中选择最大值。

27.在一些实施例中,第一cnn子模块的pool层同时支持最大池化和平均池化,但是池化窗口大小固定为2

×

2,步长固定为2。换句话说,在每个pool层之后,图像的宽度和高度分别减小了一半。

28.现有技术中的小型cnn硬件受到算力限制,有些小型cnn硬件最大输入分辨率为1280像素(例如40x32),因为下采样到该分辨率的人脸图像会丢失太多重要的人脸信息。其次,小型cnn硬件的学习能力也受到极大限制。不能将小型cnn硬件直接应用到上述的神经网络中。

29.现有技术中用于处理高分辨率输入图像的基于完整图像的常规的cnn系统200的框图如图3所示,常规的cnn系统200可以在第一卷积层(conv(1))中接收完整的高分辨率输入图

像,并开始对高分辨率输入图像执行特征提取操作。这样,常规的cnn系统200可以直接处理整个高分辨率输入图像,而无需对输入图像进行分割。但是,常规的cnn系统200需要使用能够处理高分辨率输入图像的昂贵的大规模芯片。

30.如图4所示,基于子图像的cnn系统210包括:输入模块212、第一处理模块220、合并模块222和第二处理模块224,第一处理模块220能够提供至少一个以上的n个子图像的卷积处理。

31.cnn系统210将高分辨率a输入图像202转换为较小的a子图像204,以便可以在高分辨率a输入图像202(例如,具有1280像素以上的图像)上使用小型cnn模块。

32.cnn系统210的输入模块212将高分辨率a输入图像202转换为多组a子图像204,每个a子图像204的大小小于或等于小型cnn模块所允许的最大输入大小。

33.在实际的应用过程中,相邻的a子图像204之间可能存在重叠或间隙,在实际的转换过程中都有可能出现。

34.在本实施例中可以采用时分复用第一cnn子模块的方式或者适配多个第一cnn子模块的方式,或者是二者的结合;第二处理模块224至少包括一个第二cnn子模块;一组a子图像204可以同步的被第一处理模块220卷积处理,获得一组输出特征图;合并模块222用于将第一处理模块220输出的多个输出特征图合并生成完整特征图;完整特征图输入到第二处理模块224进行处理,第二处理模块224的处理与常规的基于完整图像的cnn系统200对于卷积层的输出特征的处理相同。

35.在一个实施例中,第一处理模块220输出的多个输出特征图以特征映射图阵列206的方式输入合并模块222,特征映射图阵列206包括一组三维(3d)矩阵(即,特征映射图为二维,而多个特征映射图为一维)。例如,特征映射图阵列206可以由大小为2x2x48的9个三维矩阵(即3x3的数组)组成。在上面的示例中,合并模块222创建一个6x6x48的3d矩阵。可以将合并的3d矩阵展平为一维(1d)向量,将创建一个大小为1728的1d向量。最后,将扁平化的一维矢量发送到第二处理模块224;在一个实施例中,第二处理模块224应用的第二cnn子模块由于集成于小型cnn硬件,可以采用屏蔽小型cnn硬件的第一cnn子模块的方式来进行应用,进一步的也可以采用软件的方式代替实现fc层和relu层。

36.在本发明的一个实施例中,对于上述的第一cnn子模块采用如下的硬件架构,包括输入特征缓存、权值参数缓存、输出特征缓存、pe运算单元以及后处理单元。输入特征缓存用于存储输入特征数据;权值参数缓存用于存储权值参数;pe运算单元用于接收输入特征缓存和权值参数缓存的数据进行卷积运算;后处理单元接收pe运算单元的运算结果,并选择进行累加、激活函数、池化或者上采样等操作;输出特征缓存存储后处理单元输出的运算结果。针对于不同尺寸及不同运算方式的卷积核,可采用一种通用的运算流程在本发明中的卷积神经网络加速器架构进行运算。

37.对于 n x n 的卷积核可按照本发明地提出地运算规则分成 n x n 时段进行运算,并将各时段的运算结果进行累加,得到该 n x n 卷积核的卷积运算结果。各时段的运算在通道维度上进行并行,以实现多通道并行的卷积运算。为满足该架构多通道并行的计

算特点,采用同一位置多通道数据拼接的数据排列方式存储数据。输入特征数据、权值参数按该数据排列方式分别存储于输入特征缓存和权值参数缓存中。运算过程中,按照特定的取数规则从输入特征缓存和权值参数缓存取出数据输入到pe中进行运算。pe运算输出的输出特征图仍然按照以上数据排列方式存储于输出特征图缓存中。

38.的n个pe运算单元并行运算。运算过程中,首先为每个pe输入权值参数,然后将n个输入通道的特征图同时输入n个pe中,每个pe计算输出一个输出通道特征图,n个pe可同时输出n个通道的输出特征图,经过后处理单元对n个通道的输出特征图选择进行累加、激活函数、池化或者上采样等运算,将最终的n通道的输出特征图存储于输出特征图缓存中;pe的内部部署了n个乘法器和一组加法树,如图13所示。n个乘法器分别接收n个输入通道的输入特征数据和相应的权值参数,并将输入特征数据与权值参数相乘的结果输入到加法树相加,以实现输入特征数据与权值参数的卷积运算。

39.本发明所采用的输入特征图的存储方式;输入特征图按从左到右,从上到下的顺序依次存入输入特征图缓存中。假设输入通道变为n,输入特征缓存的每个地址空间存储输入特征图一个位置的n个通道的数据。如图14所示,地址0,存储p11位置c1,c2,...,cn n个通道的数据(p11_c1, p11_c2, ..., p11_cn);地址1,存储p12位置c1,c2,...,cn n个通道的数据(p12_c1, p12_c2, ..., p12_cn);地址2,存储p13位置c1,c2,...,cn n个通道的数据(p13_c1, p13_c2, ..., p13_cn);地址3,存储p14位置c1,c2,...,cn n个通道的数据(p14_c1, p14_c2, ..., p14_cn);地址4,存储p21位置c1,c2,...,cn n个通道的数据(p21_c1, p21_c2, ..., p21_cn);地址5,存储p22位置c1,c2,...,cn n个通道的数据(p22_c1, p22_c2, ..., p22_cn);地址6,存储p23位置c1,c2,...,cn n个通道的数据(p23_c1, p23_c2, ..., p23_cn);地址7,存储p24位置c1,c2,...,cn n个通道的数据(p24_c1, p24_c2, ..., p24_cn);地址8,存储p31位置c1,c2,...,cn n个通道的数据(p31_c1, p31_c2, ..., p31_cn);地址9,存储p32位置c1,c2,...,cn n个通道的数据(p32_c1, p32_c2, ..., p32_cn);地址10,存储p33位置c1,c2,...,cn n个通道的数据(p33_c1, p33_c2, ..., p33_cn);地址11,存储p34位置c1,c2,...,cn n个通道的数据(p34_c1, p34_c2, ..., p34_cn);

地址12,存储p41位置c1,c2,...,cn n个通道的数据(p41_c1, p41_c2, ..., p41_cn);地址13,存储p42位置c1,c2,...,cn n个通道的数据(p42_c1, p42_c2, ..., p42_cn);地址14,存储p43位置c1,c2,...,cn n个通道的数据(p43_c1, p43_c2, ..., p43_cn);地址15,存储p44位置c1,c2,...,cn n个通道的数据(p44_c1, p44_c2, ..., p44_cn)。

40.三、本发明所采用的卷积核的存储方式;卷积核按从左到右,从上到下的顺序依次存储到权值参数缓存中。假设卷积核尺寸为3x3,假设输入通道数变为n,卷积核在权值参数缓存中的存储方式如图15所示,地址0,存储k1位置c1,c2,...,cn n个通道的数据(k1_c1, k1_c2, ..., k1_cn);地址1,存储k2位置c1,c2,...,cn n个通道的数据(k2_c1, k2_c2, ..., k2_cn);地址2,存储k3位置c1,c2,...,cn n个通道的数据(k3_c1, k3_c2, ..., k3_cn);地址3,存储k4位置c1,c2,...,cn n个通道的数据(k4_c1, k4_c2, ..., k4_cn);地址4,存储k5位置c1,c2,...,cn n个通道的数据(k5_c1, k5_c2, ..., k5_cn);地址5,存储k6位置c1,c2,...,cn n个通道的数据(k6_c1, k6_c2, ..., k6_cn);地址6,存储k7位置c1,c2,...,cn n个通道的数据(k7_c1, k7_c2, ..., k7_cn);地址7,存储k8位置c1,c2,...,cn n个通道的数据(k8_c1, k8_c2, ..., k8_cn);地址8,存储k9位置c1,c2,...,cn n个通道的数据(k9_c1, k9_c2, ..., k9_cn)。

41.作为一种具体的应用示例,本实施例以3x3的卷积核为例,提供一个pe的运算过程;预设条件:假设卷积核尺寸为3x3,卷积步长为1,输入通道为n。

42.计算阶段需要进行的9个时段的计算如下:如图16所示,时段1,将卷积核k1位置上n个通道的数据(即权值参数缓存地址0存储的权值参数)输入到pe中,卷积核k1位置的权值参数所滑过的输入特征图区域为p11,p12,p21,p22四个位置上n个通道的数据(即输入特征图缓存地址0,1,4,5中存储的数据),依次将输入特征图缓存地址0,1,4,5中的数据输入到pe中,与卷积核k1位置上n个通道的数据进行卷积运算,得到时段1的计算结果t1_po(由t1_po11,t1_po12,t1_po21,t1_po22组成)。

43.如图17所示,时段2,将卷积核k2位置上n个通道的数据(即权值参数缓存地址1中存储的权值参数)输入到pe中,卷积核k2位置的权值参数所滑过的输入特征图区域为p12,p13,p22,p23四个位置上n个通道的数据(即输入特征图缓存地址1,2,5,6中存储的数据),依次将输入特征图缓存地址1,2,5,6中的数据输入到pe中,与卷积核k2位置上n个通道的数据进行卷积运算,并将计算结果与t1_po对应位置的数据进行累加,得到时段2的计算结果t2_po(由t2_po11,t2_po12,t2_po21,t2_po22组成)。

44.如图18所示,时段3,将卷积核k3位置上n个通道的数据(即权值参数缓存地址2中存储的权值参数)输入到pe中,卷积核k3位置的权值参数所滑过的输入特征图区域为p13,

p14,p23,p24四个位置上n个通道的数据(即输入特征图缓存地址2,3,6,7中存储的数据),依次将输入特征图缓存地址2,3,6,7中的数据输入到pe中,与卷积核k3位置上n个通道的数据进行卷积运算,并将计算结果与t2_po对应位置的数据进行累加,得到时段3的计算结果t3_po(由t3_po11,t3_po12,t3_po21,t3_po22组成)。

45.如图19所示,时段4,将卷积核k4位置上n个通道的数据(即权值参数缓存地址3中存储的权值参数)输入到pe中,卷积核k4位置的权值参数所滑过的输入特征图区域为p21,p22,p31,p32四个位置上n个通道的数据(即输入特征图缓存地址4,5,8,9中存储的数据),依次将输入特征图缓存地址4,5,8,9中的数据输入到pe中,与卷积核k4位置上n个通道的数据进行卷积运算,并将计算结果与t3_po对应位置的数据进行累加,得到时段4计算结果t4_po(由t4_po11,t4_po12,t4_po21,t4_po22组成)。

46.如图20所示,时段5,将卷积核k5位置上n个通道的数据(即权值参数缓存地址4中存储的权值参数)输入到pe中,卷积核k5位置的权值参数所滑过的输入特征图区域为p22,p23,p32,p33四个位置上n个通道的数据(即输入特征图缓存地址5,6,9,10中存储的数据),依次将输入特征图缓存地址5,6,9,10中的数据输入到pe中,与卷积核k5位置上n个通道的数据进行卷积运算,并将计算结果与t4_po对应位置的数据进行累加,得到时段5计算结果t5_po(由t5_po11,t5_po12,t5_po21,t5_po22组成)。

47.如图21所示,时段6,将卷积核k6位置上n个通道的数据(即权值参数缓存地址5中存储的权值参数)输入到pe中,卷积核k6位置的权值参数所滑过的输入特征图区域为p23,p24,p33,p34四个位置上n个通道的数据(即输入特征图缓存地址6,7,10,11中存储的数据),依次将输入特征图缓存地址6,7,10,11中的数据输入到pe中,与卷积核k6位置上n个通道的数据进行卷积运算,并将计算结果与t5_po对应位置的数据进行累加,得到时段6计算结果t6_po(由t6_po11,t6_po12,t6_po21,t6_po22组成)。

48.如图22所示,时段7,将卷积核k7位置上n个通道的数据(即权值参数缓存地址6中存储的权值参数)输入到pe中,卷积核k7位置的权值参数所滑过的输入特征图区域为p31,p32,p41,p42四个位置上n个通道的数据(即输入特征图缓存地址8,9,12,13中存储的数据),依次将输入特征图缓存地址8,9,12,13中的数据输入到pe中,与卷积核k7位置上n个通道的数据进行卷积运算,并将计算结果与t6_po对应位置的数据进行累加,得到时段7计算结果t7_po(由t7_po11,t7_po12,t7_po21,t7_po22组成)。

49.如图23所示,时段8,将卷积核k8位置上n个通道的数据(即权值参数缓存地址7中存储的权值参数)输入到pe中,卷积核k8位置的权值参数所滑过的输入特征图区域为p32,p33,p42,p43四个位置上n个通道的数据(即输入特征图缓存地址9,10,13,14中存储的数据),依次将输入特征图缓存地址9,10,13,14中的数据输入到pe中,与卷积核k8位置上n个通道的数据进行卷积运算,并将计算结果与t7_po对应位置的数据进行累加,得到时段8计算结果t8_po(由t8_po11,t8_po12,t8_po21,t8_po22组成)。

50.如图24所示,时段9,将卷积核k9位置上n个通道的数据(即权值参数缓存地址8中存储的权值参数)输入到pe中,卷积核k9位置的权值参数所滑过的输入特征图区域为p33,p34,p43,p44四个位置上n个通道的数据(即输入特征图缓存地址10,11,14,15中存储的数据),依次将输入特征图缓存地址10,11,14,15中的数据输入到pe中,与卷积核k9位置上n个通道的数据进行卷积运算,并将计算结果与t8_po对应位置的数据进行累加,得到时段9计

算结果t9_po(由t9_po11,t9_po12,t9_po21,t9_po22组成)。

51.时段9计算出的t9_po(由t9_po11,t9_po12,t9_po21,t9_po22组成)即为该卷积核与输入特征图卷积计算的最终结果po(由po11,po12,po21,po22组成)。

52.上述一个pe进行卷积运算的流程,其输出一个通道的运算结果。在本发明中同时例化了n个pe,可并行计算出n个输出通道的运算结果。也即可以通过n个pe同时并行的方式输出n个输出特征图;如图25所示,n个卷积核分别作为n个pe的权重参数输入;输入通道为n,并行输入n个pe中;每个pe的运算步骤与前述的一个pe的运算过程相同,并行计算输出n个通道的计算结果。其对应关系为:pe1计算输出c1通道的结果,pe2计算输出c2通道的结果,

……

,pen计算输出cn通道的结果。

53.本发明所采用的输出特征图的存储方式;输出特征图按从左到右,从上到下的顺序依次存储到输出特征图缓存中。以3x3的卷积核为例计算出的n通道输出特征图,其在输出特征图缓存中存储方式如图26所示,地址0,存储p11位置c1,c2,...,cn n个通道的数据(p11_c1, p11_c2, ..., p11_cn);地址1,存储p12位置c1,c2,...,cn n个通道的数据(p12_c1, p12_c2, ..., p12_cn);地址2,存储p13位置c1,c2,...,cn n个通道的数据(p13_c1, p13_c2, ..., p13_cn);地址3,存储p14位置c1,c2,...,cn n个通道的数据(p14_c1, p14_c2, ..., p14_cn);本发明中,采用的n通道并行计算的架构,使得输出特征图的存储方式与输入特征图的存储方式保持了相同的形式。因此,缓存的输出特征图直接可以用于下一层的卷积运算,无需再进行数据重排,省去了数据组织排列的硬件电路模块,简化了硬件设计。

54.应用上述基于子图像的cnn系统210,在一个实施例中提供一种应用基于pe架构通道的卷积神经网络加速器的人脸检测系统300,如图5所示,应用基于pe架构通道的卷积神经网络加速器的人脸检测系统300接收视频图像302作为输入,并生成人脸检测决策316作为输出。在一些实施例中,输入视频图像302是由摄像机捕获的视频的视频帧。应用基于pe架构通道的卷积神经网络加速器的人脸检测系统300至少包括运动检测模块304、图像分割模块306、第一级cnn 308、第二级cnn 310、第三级cnn 312以及最终决策模块314。

55.输入视频图像302首先被运动检测模块304接收。

56.视频中的人脸与运动有关。因此,为了降低计算复杂度,运动检测模块304可用于基于与先前接收的视频帧的比较来发现和识别每个视频帧内与运动相关联的区域。这样的运动区域可以包括人类对象和非人类对象,例如移动的车辆。另外,在移动的人类物体的情况下,移动区域可以包括人脸和人体。运动检测模块304的输出可以具有不同大小的一组从输入视频图像302识别出的运动区域318,发送到应用基于pe架构通道的卷积神经网络加速器的人脸检测系统300中的后续人脸检测模块,以检测运动区域内的大部分或所有人脸。

57.图像分割模块306通过以不同的下采样因子对运动区域318进行下采样,来生成图像金字塔(高斯金字塔),将运动区域318划分为图像金字塔的形式。

58.在一个实施例中,图像金字塔的最高分辨率由第一级cnn308的输入大小和可以检测到的人脸的期望最小大小来确定。

59.第一级cnn 308的输入大小可以是用户定义的参数,但是最小输入大小受第一级cnn 308的最小输入大小限制。例如,由于硬件限制第一级cnn的最小输入大小为16x16,限制输入大小必须至少为16

×

16。

60.此外,最高分辨率表示还将确定可以由应用基于pe架构通道的卷积神经网络加速器的人脸检测系统300检测到的最小人脸。更具体地说,可以通过将第一级cnn 308的输入大小乘图像分割模块306使用的下采样因子来确定可以检测到的最小脸部。

61.例如,如果将16x16用作第一级cnn308的输入大小,并且图像分割模块306使用初始下采样因子3,则可以检测到的最小人脸为48x48。如果金字塔和面片生成模块306使用初始下采样因子2并将16x16用作输入大小,则可以检测到的最小脸部将改为32x32。

62.图像分割模块306的下采样因子是人脸检测精度和速度之间的权衡。另一方面,可以将初始下采样因子确定为可以检测到的人脸的所需最小尺寸与第一级cnn308的输入尺寸之比。例如,如果将16

×

16用作输入的第一级cnn308的输入大小,并且可以检测到的所需人脸的最小大小约为48

×

48,则应使用3的初始下采样因子。第一级cnn308的最小输入大小即16

×

16。

63.图像分割模块306为每个接收到的运动区域318生成该运动区域318的多分辨率表示的图像金字塔。即,图像分割模块306生成与原始输入视频图像302的相同部分相对应的不同分辨率的图像集。如上所述,第一阶段cnn308不是基于整体来处理图像金字塔的每个图像,而是基于用户指定的输入大小来处理图像块。例如,如果输入大小为16x16,则图像金字塔的每个图像都进一步划分为一组16x16图像块。

64.在一个实施例中,图像分割模块306使用滑动窗口的方法将图像金字塔的每个图像划分为一组图像块。更具体地,将定制步长的滑动窗口(例如16

×

16滑动窗口)步进通过金字塔的每个图像到定制步长(例如行和列方向)上的2或4个像素。可以在每个滑动窗口位置创建图像块。图像分割模块306生成并输出与运动区域318的多分辨率表示集相对应的相同大小的图像块集。

65.与运动区域318的低分辨率表示相比,运动区域318的较高分辨率表示可以产生更多的图像块。由第一级cnn 308接收图像块集,第一级cnn 308可以按顺序一次处理一个图像块,或者为了提高处理速度,一次处理多个图像块,可以并行处理。

66.如图6所示,第一级cnn308的conv(1)层包括十个步长为3

×

3的卷积核。因此,conv(1)层的输出尺寸为14

×

14

×

10。 mp(max-pooling最大池化层)(1)层使用具有2个步长的2x2池化窗口。因此,mp(1)层的输出尺寸为7x7x10。 conv(2)层包含16个步长为1的3x3卷积核。因此,conv(2)层的输出尺寸为5

×5×

16。 mp(2)层使用跨度为2的2

×

2合并窗口。因此,mp(2)层的输出尺寸为3

×3×

16。fc(1)和fc(2)的输出分别是32

×

1和16

×

1向量。

67.在一个实施例中,在最终的16

×

1输出向量中,前两个输出用于生成人脸检测置信度得分(也称为“人脸分类器”);接下来的四个输出是图像块中的人脸的边界框坐标(如果在图像块中检测到人脸)(也称为“边界框回归算子”)。最后的十个输出代表检测到的人脸的五个人脸标记点的位置,即左眼,右眼,鼻子和嘴巴的两个角(也称为“标记定位算子”)。因此,第一级cnn308输出与图6所示的图像块集的子集相对应的一组候选人脸窗口。

68.对于第一级cnn 308输出的每个候选人脸窗口,从原始输入视频图像302中找到对应的图像块,然后将裁剪的块大小调整为第二级cnn310的指定输入大小。

69.此输入大小应大于第一级cnn308的输入大小。

70.例如第二级cnn 310被配置为具有24x24的输入大小。结果,调整大小后的图像块的大小也是24x24。从候选人脸窗口生成缩放的图像块的过程可以以硬件,软件或硬件和软件的组合来实现。相应的处理模块可以位于第一级cnn 308和第二级cnn 310之间,第二级cnn 310可以一次处理一个接收到的图像块,或者可以通过并行处理提高处理速度。

71.如图7所示,第二级cnn500的conv(1)层包括跨度为1的28个3

×

3卷积核。因此,conv(1)层的输出尺寸为22x22x28(基于24x24的输入图像尺寸)。 mp(1)层使用跨度为2的2x2池窗口。因此,mp(1)层的输出尺寸为11x11x28。

72.conv(2)层包含跨度为1的32个3x3卷积核。因此,conv(2)层的输出尺寸为9x9x32。 mp(2)层使用跨度为2的2x2池窗口。因此,mp(2)层的输出尺寸为5x5x32。 conv(3)层包含48个步长为1的3x3卷积核。

73.因此,conv(3)层的输出大小为3

×3×

48。 mp(3)层使用跨度为2的2x2池窗口。因此,mp(3)层的输出尺寸为2x2x48。

74.fc(1)和fc(2)的输出分别是128x1和16x1向量。

75.第二级cnn310中最后一个fc层的输出仍然是16

×

1输出矢量,并且前两个输出用于生成人脸检测置信度得分或(也称为“人脸分类器”);接下来的四个输出是输入是图像块中的人脸的边界框坐标(也称为“边界框回归算子”)。最后的10个输出代表检测到的脸部的五个人脸标记点的位置,即左眼,右眼,鼻子和嘴巴的两个角的位置(也称为“标记定位算子”)。但是,由于第二级cnn310中的输入图像分辨率高于第一级cnn308中的输入图像分辨率,并且第二级cnn310比第一级cnn308更强大,因此第二级cnn310的人脸检测精度也更高。比第一级cnn308的因此,第二级cnn310输出与图像块集的子集相对应的一组候选人脸窗口。

76.对于第二级cnn310输出的每个候选人脸窗口,从原始输入视频图像302中找到对应的图像块,然后将裁剪的块大小调整为第三级cnn312的指定输入大小。

77.此输入大小应大于第一级cnn308和第二级cnn310的输入大小。

78.例如第三级cnn 312被配置为具有46xx46的输入大小。结果,调整大小后的图像块的大小也是46x46。

79.从候选人脸窗口生成缩放的图像块的过程可以以硬件,软件或硬件和软件的组合来实现。相应的处理模块可以位于第二级cnn 310和第三级cnn312之间,第三级cnn312可以一次处理一个接收到的图像块,或者可以通过并行处理提高处理速度。

80.如图8所示,第三级cnn 312的conv(1)层包括步长1的32个3

×

3卷积核。因此,conv(1)层的输出尺寸为44

×

44

×

32(基于46

×

46的输入图像尺寸)。 mp(1)层使用跨步2的2x2池化窗口。因此,mp(1)层的输出尺寸为22x22x32。 conv(2)层包含50个步长为1的3x3卷积核。因此,conv(2)层的输出大小为20

×

20

×

50。 mp(2)层使用跨度为2的2x2池化窗口。因此,mp(2)层的输出尺寸为10x10x50。 conv(3)层包含50个步长为1的3x3卷积核。因此,conv(3)层的输出大小为8

×8×

50。 mp(3)层使用跨度为2的2x2池化窗口。因此,mp(3)层的输出尺寸为4x4x50。fc(1)和fc(2)的输出分别是256 x 1和16 x 1向量;

第三级cnn 312的输入的图像块具有46

×

46

×

1 = 2116的大小(即,仅使用一个灰度图像通道)。在第三级cnn312的以上描述中,第三级cnn312的最大输入大小需要大于2116,在一个实施例中,对于一个最大输入大小小于2116的第三级cnn312,第三级cnn312还包括一个b输入模块802,用于接收46x46输入图像块。b输入模块802用于将图像块划分为尺寸为30x30的四个b子图像804;图9示出了根据本文所述的一些实施例的用于46x46图像块的示例性输入图像分割方案。从图9的左侧可以看到,输入图像块具有四个重叠的b子图像804,每个b子图像804的大小为30

×

30,并且在相邻b子图像804之间移动了16个像素。如图9所示,图中采用将四个b子图像804偏移使它们分离可见,但是并不代表实际的位置。实际上,这四个b子图像804的行坐标分别从1和17开始,四个子图像的列坐标分别从1和17开始,也即四个子图像实际是如图9中后面的一个小的图像所示的排列。

81.如图10所示,对于给定的30x30b子图像804,第三级cnn 312的conv(1)层包含32个3x3的步长1的卷积核。因此,conv(1)层的输出大小为28x28x32。 mp(1)层使用具有2个步长的2x2池化窗口。因此,mp(1)层的输出尺寸为14x14x32。 conv(2)层包含50个第1步的3x3卷积核。因此,conv(2)层的输出大小为12x12x50。 mp(2)层使用跨度为2的2x2池化窗口。因此,mp(2)层的输出尺寸为6x6x50。 conv(3)层包含50个步长为1的3x3卷积核。因此,conv(3)层的输出大小为4

×4×

50。 mp(3)层使用步长为2的2x2池化窗口。因此,mp(3)层的输出具有大小为2

×2×

50,即50

×2×

2的特征图1006。在一组4个b子图像804的情况下,mp(3)层产生4组2

×2×

50个特征图的输出;第三级cnn 312还包括b合并模块808,其用于接收和合并2

×2×

50的特征图;如图9所示,按照分离的策略进行逆向合并,四个2

×

2特征图合并为一个4

×

4特征图,4组2

×2×

50个特征图合并为50个4

×

4特征图的集合。

82.如图11所示,最终决策模块314包括重建模块902以及fc层(fc(1)和fc(2)),重建模块902接收到50个4

×

4特征图的集合,该重建模块902将2d特征图的集合合并和重新组织为大小为800

×

1的1d向量。 1d向量由fc层(fc(1)和fc(2))的两个阶段进一步处理,随后为给定的检测到的运动区域318输出人脸检测决策316。在所示的实施例中,人脸检测决策316可以包括人脸分类器、边界框回归算子和标记定位算子。

83.通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到上述实施例方法可借助软件加必需的通用硬件平台的方式来实现,当然也可以通过硬件,但很多情况下前者是更佳的实施方式。基于这样的理解,本实施例的技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质(如rom/ram、磁碟、光盘)中,包括若干指令用以使得一台终端(可以是手机,计算机,服务器,空调器,或者网络设备等)执行本实施例各个实施例的方法。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。