1.本发明涉及一种射频(radiofrequency,rf)功率封装和射频功率器件。更 特别地,本发明涉及一种rf功率封装,其中静电释放(electrostatic discharge, esd)器件布置在封装主体或壳体内部。该rf功率器件包括此rf功率封装。

背景技术:

2.rf功率封装是本领域已知的。这些rf功率封装配置为对在从100khz至 40ghz的频率上、处于1w和5kw范围内的各水平上的功率进行传递。这些封 装包括多个端子,通过这些端子输入或输出电信号,并且通过这些端子提供功 率或接地。

3.rf功率封装安装在印刷电路板(printed circuit board,pcb)上。此板是更 大的rf功率器件的一部分。此器件包括电触点,从器件的外部可以到达这些 电触点。这些触点可以暴露在静电释放事件中。这些释放事件的结果是,rf功 率器件的诸如rf功率封装之类的组件可能被损坏。

4.器件在高静电电压应力下的性能能够使用诸如充电器件模型或人体模型之 类的模型来确定。使用人体模型,可以对人接触器件时发生的静电释放esd进 行模拟。例如,根据jedec js-001标准,人体可以被建模为100pf的电容器和 1500ohm的放电电阻器。在测试期间,将电容器充电至放电电压,例如2kv, 并且之后通过布置为与期间的一端子串联的放电电阻器对电容器放电。

5.通常,器件应当满足特定esd要求,此esd要求与该器件在不因为esd 相关损坏而造成故障的情况下应当能够承受的放电电压水平有关。

6.任何器件的esd性能主要是由布置在其内部的电子线路确定的。rf功率 封装包括诸如场效应晶体管(field-effect transistor,fet)之类的放大线路,以 及用于阻抗匹配和/或偏置的无源线路。这些组件中的每一个均易受到esd损 坏。

7.近来,氮化镓(gallium nitride,gan)已经出现作为有希望用于实现rf 功率放大器件的材料。在这些器件中,所使用的基于gan的功率fet包括栅 极、源极和漏极触点。栅极触点是由具有小于反向偏置的小漏电流的肖特基接 触形成的。

8.小于反向偏置的相对小的漏电流使得gan fet易于受到esd相关损坏。 例如,若人体模型(human body model,hbm)测试是通过在源极触点或漏极 触点处施加正电压且将栅极触点接地来进行的,则仅放电电压的一小部分落在 放电电阻器上,而反向偏置的肖特基二极管表现出高串联电阻。由此,在源极 或漏极触点处可能出现过高的电压,且gan fet可能击穿。

9.rf功率封装是本领域已知的。实例性的rf功率封装包括封装主体或壳体、 以及至少部分布置在封装主体或壳体中的导电基底。该rf功率封装还包括半 导体裸片,半导体裸片安装在导电基底上且布置在封装主体或壳体中,其中, 半导体裸片包括放大电路,放大电路具有用于输入或输出电信号的esd感测触 点。rf功率封装此外还包括多个端子,多个端子与导电基底物理分离,并且每 个端子包括在封装主体或壳体外部提供的第一端子表

面以及在封装主体或壳体 内部提供的第二端子表面,其中,多个端子中的一端子构成rf端子,rf端子 配置用于输入待放大电路放大的信号或输出经放大电路放大的信号。rf端子通 过rf端子连接线点连接至esd感测触点。

10.已知的rf功率封装配置为安装在pcb上。通常在pcb上布置esd器件 以提供所需的esd保护。这些器件通常包括第一esd触点和第二esd触点。 在工作器件,第一esd触点和第二esd触点中的一个接地,而第一esd触点 和第二esd触点中的另一个直接或通过其它组件连接至需要esd保护的rf功 率封装。esd器件阻止或限制与放电相关的任何esd脉冲到达esd感测触点。

11.esd器件可以包括布置在第一esd触点和第二esd触点之间的多个二极 管、晶体管或硅可控整流器。例如,一个或多个二极管能够布置为,二极管的 阳极连接至第一esd触点且二极管的阴极连接至第二esd触点;而一个或多 个其它二极管能够配置为,二极管的阳极连接至第二esd触点且二极管的阴极 连接至第一esd触点。以此方式,针对在要保护的端子处发生的正电压和负电 压,能够提供低欧姆放电路径。通过提供低欧姆放电路径,放电电流的大部分 将流过esd器件,由此保护具有esd感测触点的器件或组件。

12.申请人发现,将已知的rf功率封装的安装过程可能会失败。申请人还发 现,这样的失败能够归因于在安装已知的rf功率封装时发生的esd损坏。

技术实现要素:

13.本发明的目的在于提供一种rf功率封装,该rf功率封装能够在消除或至 少降低esd损坏风险的情况下安装或操纵。

14.根据本发明,该目标通过如权利要求1中限定的rf功率封装实现,并且 特征在于,rf功率封装还包括esd器件,esd器件用于保护放大电路免受由 静电放电引起的损坏。esd器件包括第一esd触点和第二esd触点。此外, 多个端子中的一端子构成安装mnt端子,esd器件安装在mnt端子上。第一 esd触点通过第一esd连接线直接或通过rf端子连接线的至少一部分间接电 连接至放大电路的esd感测触点,并且第二esd触点在使用时电接地。

15.根据本发明,esd器件被提供在封装内部,并且布置在rf功率封装的端 子上。以此方式,能够更好地保护放大电路的esd感测触点免受esd损坏, 即便是在安装rf功率封装时。

16.导电基底能够配置为至少在使用时电接地。此外或替选地,多个端子中的 一端子可以构成接地gnd端子,gnd端子在使用时电接地。此gnd端子优 选布置为邻近mnt端子。esd器件的第二esd触点可以通过第二esd连接 线电连接至gnd端子或电连接至导电基底。

17.第一esd连接线可以包括与rf端子连接线共享的公共部分,以及在公共 部分的一端和第一esd触点之间延伸的独立部分。向esd器件看去在公共部 分的端子处的阻抗优选远大于自从放大电路看出来公共部分的端子处的阻抗。 以此方式,esd器件并不显著影响rf功率封装的rf性能。若对阻抗进行估计, 这尤其对rf功率封装的通常在100khz和40ghz的范围内的工作频率进行保 持。

18.放大电路可以包括场效应晶体管fet,例如,基于氮化镓的fet或基于硅 的横向双扩散金属氧化物半导体(laterally diffused metal oxide semiconductor, ldmos)晶体管。在此情况下,放大电路的esd感测触点电连接至fet的栅 极或漏极,或由fet的栅极或漏

极形成。此外或替选地,放大电路的esd感 测触点能够是电连接至fet的漏极或栅极处的键合焊盘或键合条。此外,rf 端子连接线可以包括rf键合线,rf键合线的一端键合至键合焊盘或键合条。 rf键合线的另一端可以键合至rf端子。替选地,rf端子连接线可以包括阻 抗匹配网络,阻抗匹配网络包含rf键合线。此阻抗匹配网络可以包括分流电 容器,分流电容器具有非接地端子以及至少在使用时电接地的接地端子。在此 情况下,rf键合线的另一端能够键合至分流电容器的非接地端子,并且rf端 子连接线可以包括在分流电容器的非接地端子和rf端子之间的进一步的rf键 合线。阻抗匹配网络通常用在放大电路的输入端(即栅极)处。然而,阻抗匹 配网络还可以用在放大电路的输出端(即漏极)处。

19.esd器件可以包括esd半导体裸片,半导体裸片上集成有esd线路,并 且esd半导体裸片包括具有后表面的半导体基底,esd半导体裸片经由后表面 固定连接至mnt端子的第二表面。第一esd触点和第二esd触点能够布置在 esd半导体裸片的前表面上,该前表面与半导体基底的后表面相对。此外,第 一esd连接线可以包括将rf端子连接线电连接至第一esd触点处的键合线, 并且第二esd连接线可以包括将第二esd触点电连接至gnd端子或导电基底 处的键合线。第一esd连接线的键合线可以在rf端子和第一esd触点之间或 在esd感测触点和第一esd触点之间延伸。此外,多个端子中的一端子可以 构成非连接(non-connected,nc)端子。在此情况下,mnt端子能够是gnd 端子、rf端子或nc端子。在本发明的背景下,nc端子是并不电连接至其上 安装有rf功率封装的pcb上的电子线路处的端子。通常,nc端子处的电压 在工作期间是浮动的。

20.替选地,esd器件可以包括esd半导体裸片,esd半导体裸片上集成有 esd线路,并且esd半导体裸片包括具有后表面的导电半导体基底,esd半 导体裸片经由后表面固定连接至mnt端子的第二表面。在此情况下,后表面 形成第一esd触点,并且第二esd触点布置在esd半导体裸片的前表面上, 前表面与半导体基底的后表面相对。第二esd连接线可以包括将第二esd触 点电连接至gnd端子或导电基底处的键合线。此外,mnt端子能够是rf端 子。替选地,多个端子中的一端子可以构成非连接nc端子。在后一种情况下, mnt端子能够是nc端子,并且第一esd连接线可以包括将mnt端子电连接 至rf端子连接线处的键合线。在此后一种情况下,第一esd连接线的键合线 可以在rf端子和mnt端子之间或在esd感测触点和mnt端子之间延伸。

21.替选地,esd器件可以包括esd半导体裸片,esd半导体裸片上集成有 esd线路,并且esd半导体裸片包括具有后表面的导电半导体基底,esd半 导体裸片经由后表面固定连接至mnt端子的第二表面。在此情况下,后表面 形成第二esd触点,并且第一esd触点布置在esd半导体裸片的前表面上, 前表面与半导体基底的后表面相对。第一esd连接线可以包括将第一esd触 点电连接至rf端子连接线处的键合线。在此情况下,第一esd连接线的键合 线可以在rf端子和第一esd触点之间或在esd感测触点和第一esd触点之 间延伸。此外,mnt端子能够是gnd端子,或者多个端子中的一端子构成非 连接nc端子。在后一种情况下,mnt端子可以是nc端子,并且第二esd 连接线可以包括将mnt端子电连接至gnd端子或导电基底处的键合线。

22.导电基底可以包括大体矩形基部和凸部,大体矩形基部与mnt端子在第 一方向上分离,凸部整体连接至大体矩形基部并且在第一方向上延伸以至于凸 部的一端布置为与mnt端子在垂直于第一方向的第二方向上分离。大体矩形 基部与分离于该具有圆角或倒角

的大体矩形基部的矩形基部可以是相同的。第 二esd连接线包括连接至导电基底处的键合线,甚至键合线连接至导电基底的 凸、且优选平行于第二方向。在此实施例中,导电基底的形状不同于常见的矩 形形式,以允许esd器件接地。此外,由于从放大电路的输出端(例如漏极) 延伸出来的键合线通常在第一方向上延伸向rf端子,第二esd连接线的键合 线与这些键合线之间的电磁耦合很小甚至没有。在使用esd器件来保护放大电 路的输入端时采用类似的考虑。

23.rf功率封装可以是诸如方形扁平无引脚(quad flat no-leads,qfn)或双 列扁平无引脚(dual flat no-leads,dfn)封装之类的扁平无引线封装。在此 情况下,多个端子中的一端子可以对应于扁平无引脚风中的各自焊盘(land)。 替选地,rf功率封装可以是模塑引线框封装或诸如陶瓷引线框封装之类的非模 塑引线框封装,其中,多个端子中的每个端子对应于模塑引线框封装或非模塑 引线框封装的各自引线。

24.在模塑引线框封装的情况下,引线是在将rf功率封装从引线框分离之前 引线框的一部分。在此情况下,导电基底通过在将封装从引线框分离之前的多 个分离的连接部件物理且电连接至引线框,并且其中,在将封装从引线框分离 期间例如通过切割、打孔或推挤将每个连接部件划分为第一连接部件和第二连 接部件,第一连接部件仍连接至导电基底,第二连接部件仍连接至引线框。rf 功率封装还可以包括连接至至少一个第一连接部件部分且自其延伸的框部分, 其中,esd器件安装在框部分上。此外,框部分可以在一对第一连接部件部分 之间延伸。更特别地,框部分和第一连接部件部分能够是一体成型的。esd器 件可以采用与上述esd半导体裸片类似的配置,即esd器件可以具有位于半 导体裸片顶部的第一esd触点和第二esd触点,或者这些触点之一布置在esd 半导体裸片的半导体基底的背面。

25.根据第二方面,本发明提供了一种rf功率器件。rf功率器件包括印刷电 路板和上述rf功率封装,印刷电路板包括多个焊垫。rf功率封装安装至印刷 电路板,以至于rf功率封装的每个端子例如通过焊接固定连接至多个焊垫中 的各自焊垫。印刷电路板可以包括集成在印刷电路板中的单独焊垫或金属块 (coin),单独焊垫或金属块例如通过焊接固定连接至rf功率封装的导电基底。

附图说明

26.接下来将参照附图对本发明进行更详细的描述,其中,相同的附图标记用 于指代相同或相似的组件。在附图中:

27.图1至7示出了依照本发明的rf功率封装的变型实施例的示意性俯视图;

28.图8示出了依照本发明的模塑封装的透视图;

29.图9示出了图8的模塑封装的截面图;以及

30.图10依照本发明的rf功率器件的示例。

具体实施方式

31.图1示出了依照本发明的rf功率封装1a的一实施例。封装1a是dfn 型封装,包括裸片焊盘10形式的导电基底,半导体裸片30安装在裸片焊盘10 上。rf功率fet集成在半导体裸片10上。图1仅示出了连接至功率fet的栅 极处的键合条31和连接至功率fet的漏极处的

键合条32。功率fet的源极未 示出,但是此触点通过半导体裸片30的半导体基底中的通孔或通过导电的半导 体基底接地。在此,需要注意的是,单rf功率封装1a安装在pcb上时,通 过固定安装在pcb上的接地焊盘或pcb中的金属块上的裸片焊盘10实现rf 功率fet接地。同时,通过裸片焊盘10还实现rf功率fet的散热。

32.如图所示,rf功率封装1a包括两个额外的半导体裸片。第一个半导体裸 片40布置在输入端子rf1和栅极键合条31之间。半导体裸片40包括集成的 电容器,电容器的第一端子连接至键合条41。该电容器的第二端子接地。这能 够通过半导体裸片40中的通孔或通过半导体裸片40的导电的半导体基底接地。 通过其上安装有半导体裸片40的裸片焊垫10进一步实现接地。

33.多个键合线b6在输入端子rf1和半导体裸片40上的电容器的非接地端子 之间延伸。其它多个键合线b5在电容器的非接地端子和栅极键合条31之间延 伸。以此方式实现lc类型的阻抗匹配网络。

34.进一步的半导体裸片50布置在半导体裸片30和输出端子rf2之间。同样, 该裸片包括电容器,电容器的一个端子连接至键合条51。另一端子以与半导体 裸片40上的电容器相似的方式接地。

35.多个键合线b3在漏极键合条32和输出端子rf2之间延伸。这些键合线形 成漏极触点和输出端子rf2之间的rf端子连接线。更多个b4在漏极键合条 32和半导体裸片50上的电容器的非接地端子之间延伸。以此方式形成连接至 漏极键合条32处的分流lc串联网络。

36.半导体裸片30上的rf功率fet包括输出电容。对于大的器件,输出电容 对于fet的rf性能可能具有恶化效果。为了避免此恶化,分流lc网络配置 作为分流电感,分流电感与输出电容在rf功率封装的工作频率的相同或接近 频率处谐振。分流lc串联网络的串联电容阻止dc路径接地。

37.图1示出了额外的端子20。提供接地端子gnd以在封装1a安装在pcb 上时接地。非连接端子nc并未电连接至pcb上的线路。这些端子可以例如通 过焊接连接至pcb上的焊盘,但是这些焊盘并未连接至其它线路并且在工作时 具有浮动又或未定义的电势。

38.在图1中,esd半导体裸片60形式的esd器件安装在非连接端子nc上。 其上安装有esd半导体裸片的端子也称为安装端子mnt。esd半导体裸片60 包括第一键合焊垫61形式的第一esd触点以及第二键合焊垫62形式的第二 esd触点。输出端子rf2通过键合线b1形式的第一esd连接线连接至第一键 合焊盘61。第二键合焊盘62通过键合线b2形式的第二esd连接线连接至导 电基底10。

39.在图1中,esd半导体裸片60配置为保护rf功率fet免受由发生在输 出端子rf2处且到达功率fet的漏极触点处的静电放电引起的esd相关损坏。 在此情况下,功率fet的漏极被认为是esd感测触点。如图1中所示,第一 esd触点采用第一esd连接线通过由键合线b3形成的rf端子连接线的至少 一部分间接电连接至该esd感测触点。第二esd触点通过键合线b2和导电基 底10接地。

40.第一esd触点和esd感测触点之间的连接线还能够是直接连接线。图2 中示出了连接线的示例。在此情况下,半导体裸片60具有导电半导体基底。第 一esd触点采用布置在半导体裸片60顶部上的第一键合焊盘61的形式,而第 二esd触点采用布置在半导体裸片60的半导体基底的背面上的导电金属的形 式。

41.第一esd连接线又包括键合线b1。然而,键合线b1此时在漏极键合条 32和第一键合焊盘61之间间接延伸。第二esd触点通过接地端子gnd接地。

42.在图3中,esd半导体裸片70还提供用于保护rf功率fet免受由发生 在输入端子rf1处且到达rf功率fet的栅极触点处的静电放电引起的esd 相关损坏。在此情况下,功率fet的栅极被认为是esd感测触点。与esd半 导体裸片60类似,esd半导体裸片70包括第一键合焊垫71形式的第一esd 触点以及第一键合焊垫72形式的第二esd触点。第一键合焊垫71通过键合线 b7连接至输入端子rf1。第二键合焊垫72通过连接至导电基底10处的键合线 b8接地。

43.图4至6示出了依照本发明的dfn类型的rf功率封装的进一步实施例。 这些实施例的区别在于:a)esd半导体裸片是否包括位于esd半导体裸片的 上表面上的第一esd触点和第二esd触点,或者这些触点之一是否布置在esd 半导体裸片的导电半导体基底的背面;以及b)esd半导体裸片安装在安装端 子mnt上。

44.图第一esd触点第二esd触点mnt端子4顶面顶面rf25顶面背面gnd6背面顶面rf2

45.技术人员很容易理解,图4至6中示出的esd保护措施可以额外地或替选 地被是现在输入端处用以保护rf功率fet的栅极。

46.图7示出了rf功率封装1g的一实施例,在该rf功率封装中,导电基底 10包括在第一方向d1上延伸离开本质上矩形基部11的凸部12。凸部12和基 部11整体连接。在此实施例中,第二esd连接线包括将第二键合焊垫62连接 至凸部12以接地的键合线b2。如图所示,键合线b2沿着与第一方向d1垂直 的第二方向d2延伸。第一esd触点实现在esd半导体裸片60的导电半导体 基地的背面。

47.在图7的实施例中,这些线之间的相互正交布置使得键合线b2与键合线 b3和b4中任一个之间的电磁耦合最小化。此电磁耦合可导致rf信号的丢失, 由此降低封装的效率。

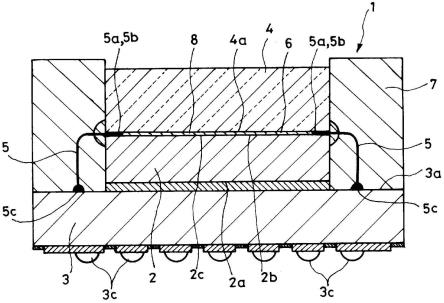

48.在图1至7中示出了具有esd半导体裸片的不同配置的若干实施例。技术 人员很容易理解,在本发明的背景下可以有其它实施例。此外,在图1至7中 忽略了模塑料。在诸如dfn封装或qfn封装之类的扁平无引线封装中,模塑 料以本领域中已知的方式覆盖导电基底10,端子20以及半导体裸片30、40、 50、60、70。

49.图8示出了模塑的引线框封装100。此类型封装是通过首先采用自引线框 凸出的连接部件将包括多个引线20的引线框连接至导电热沉10处来实现的。 这些连接部件通过铆钉103铆接至热沉10。引线框和热沉10的组合因而布置 在用于应用模塑料的模具中。一旦固化,则模塑料提供热沉10和引线20之间 的相互固定,这意味着当封装100与引线框分离且连接部件被切断时,热沉10 和引线20保持相互固定。

50.图8示出了与引线框分离之后的且没有模塑料的封装100。作为将封装100 与引线框分离的结果,在热沉10的拐角处提供的连接部件中的每个连接部件划 分为保持为连接至热沉10处的第一连接部件部分102以及保持连接至引线框处 的第二连接部件部分(未示出)。

51.封装100在热沉10的两侧包括框部分101,框部分101整体连接至第一连 接部件部

分102。框部分101包括用于应力释放目的的孔104。类似的孔105 能够提供在输出引线rf2中,输出引线rf2与第一连接部件部分102和框部分 101分离一距离101a。

52.在封装100中,esd半导体裸片60布置在框部分101的顶部。为了将半 导体裸片30附接至热沉10,使用在附接半导体裸片30时至少部分为液体的粘 合剂。因此,粘合剂的一部分可以流出到热沉10上的其它区域。对于小尺寸封 装,邻近布置在热沉10上的裸片之间的区域应当尽可能最小化。然而,当裸片 之间过于接近时,存在着粘合剂从一个裸片流到另一裸片的风险。在此,这可 能引起与裸片顶面处的触点偶然短路。在图8中,因为框部分101相对于半导 体裸片30位于高处,此粘合剂引起esd半导体裸片60的第一esd触点和地 之间的偶然短路的风险更低。

53.图8还示出了大的输出引线rf2和多个小的输入引线20,其中一个引线直 接或间接连接至rf功率fet栅极。应当注意的是,在输入端或输出端可以提 供额外的引线。

54.在图8中示出了单独裸片30具有连接至各自引线处的漏极键合条32以及 输入键合焊垫31。应当注意的是,输入键合焊垫31可以直接或者通过阻抗匹 配网络连接至布置在半导体裸片30上的rf功率fet的栅极。类似地,在裸片 30或者封装100的其它裸片(未示出)的输入端和输出端可以提供额外的线路。

55.图9示出了图8中的封装100沿直线c-c的截面图。如图所示,封装100 提供有盖108,盖108包括盖基部108a和自盖基底108a延伸的盖侧壁108b。 所应用的模塑料形成封装主体110,封装主体110包括将引线20、rf1、rf2 和热沉10相互固定的下部分110b,以及上部分110a。引线20、rf1、rf2延 伸通过封装主体110。在封装内部,键合线键合至引线20、rf1、rf2的暴露 表面。

56.粘合剂111布置在上部分110a和盖侧壁108b之间以用于将盖108固定附 接至封装主体110。以此方式,在封装100内部形成气腔109。此类型封装因而 已知为气腔模塑封装。应当注意的是,盖108可以通过使用与封装主体110相 同的模塑料来实现。

57.在其它实施例中,在提供用于实现封装主体110的模塑料的同时形成盖108。 在这些封装中,没有出现气腔,并且需要在应用模塑料之间实现全部必要的电 子连接线。与这些完全模塑封装相比,气腔模塑封装提供了更优的rf性能, 这是因为模塑料不存在损耗,否则会围绕在诸如键合线之类的电子组件周围。

58.图10示出了依照本发明的rf功率器件200的示例。器件200包括诸如图 1的封装1a之类的rf功率封装,该rf功率封装安装在pcb 201上。pcb 201 通常为允许具有多个不同层上的金属线的多层板。

59.pcb 201包括焊垫202a、202b,其上通过焊接固定安装有引线20和导电 基底10。如图所示,引线rf1和rf2连接至pcb 201上的金属线203(仅部分 被示出)。非连接引线nc连接至焊垫202a,但是这些焊垫并未进一步连接至 pcb 201上的电子线路。接地引线gnd通过通孔204连接至pcb 201的接地 层。

60.技术人员应当清楚的是,rf功率器件200可能具有更多的配置,例如用于 容置诸如图8和图9中的模塑封装之类的不同类型封装。

61.在上文中,通过本发明的详细实施例对本发明进行了解释。然而,应当注 意的是,在不违背所附权利要求所限定的本发明的范围的情况下,可能存在各 种修改。例如,采用上述形式的esd保护同样可以提供用于保护封装内的其它 线路触点,而不是针对到达rf功

率fet的栅极或漏极处的放电引起的损坏进 行保护。同样地,在这些实施例中,esd半导体裸片可以布置在端子上。类似 地,申请人意识到上述发明构思还可以用于其它类型的封装,不是rf功率封 装,但是仍具有封装主体或壳体、导电基底、多个端子以及安装在导电基底上 的半导体裸片。此封装的一示例可以是电子封装,该电子封装中的半导体裸片 包括电子线路,该电子线路具有一个或多个esd感测触点。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。