1.本发明涉及多赫蒂放大器。

背景技术:

2.在移动体通信中,发送用功率放大器通常要求高效率且低失真。另外,为了应对近年来的高速且大容量的通信而使用高papr(peak average power ratio:峰值平均功率比)的调制波信号。在将高papr的信号通过功率放大器放大的情况下,为了满足失真的标准,使功率放大器以相对于饱和输出功率回退的较低的平均输出功率工作。通常,回退量与效率是相反的关系,因此使用高papr的情况下无法期待高效率。但是通过使用被称为多赫蒂放大器的放大器,能够解决上述问题。因此,多赫蒂放大器以通信用基站为中心被广泛采用。

3.在多赫蒂放大器中,使用λ/4线路将偏置为ab级或b级的主放大器和偏置为c级的峰值放大器并联地合成。λ/4线路配置于一方的放大器的输出,也配置于另一方的放大器的输入。在大信号输入时,两个放大器同样地工作并以同相合成,因此表现出与两个合成放大器同样的特性,实现较大的饱和电力。另一方面,在小信号输入时,仅主放大器工作,并且在主放大器的输出侧连接的λ/4线路作为阻抗逆变器发挥功能,因而通过高负载阻抗获得高效率。因此,多赫蒂放大器能够在较宽的输出功率范围实现高效率。

4.但是多赫蒂放大器存在以下问题:由于主放大器与峰值放大器的晶体管到合成点为止的匹配电路的频率特性而难以宽频带化。为了解决该问题而提出一种多赫蒂放大器:通过使用晶体管的源极端子与漏极端子之间的寄生电容cds和电长度比90度延迟线路短的线路,从而等效地构成90度延迟电路。该电路不需要以往所需的从晶体管到合成点为止的匹配电路,能够宽频带化。此外,还提出一种多赫蒂放大器:在90度延迟电路的一部分使用接合线,在昂贵的晶体管芯片上仅形成晶体管,除此以外的电路形成于树脂基板等便宜的基板,并用接合线将它们连接(例如,参照专利文献1)。由此能够降低成本。

5.专利文献1:日本特表2017-501662号公报

6.但是存在由于接合线所具有的电感而导致多赫蒂放大器的频率特性劣化的问题。具体而言,根据信号的合成点的位置,可以想到两种情况。

7.第一种是合成点为峰值放大器的焊盘端的情况。在该情况下,朝向主放大器侧的接合线和朝向输出端子侧的两根接合线相对于峰值放大器的焊盘连接。由于焊盘尺寸有限,因此其负载阻抗由于构成峰值放大器的晶体管的位置而变得不均匀,产生晶体管的不平衡动作。不平衡动作会成为输出功率、增益、效率降低以及振荡的原因。此外,由于上述的两根接合线在布局上接近,因此存在产生互感、负载阻抗的频率偏差的问题。

8.第二种是合成点为树脂基板上的线缆焊盘端的情况。在该情况下,存在因接合线的电感成分而产生负载阻抗的频率偏差的问题。这些频率偏差和不平衡动作会阻碍多赫蒂放大器的高效率且宽频带的特性,因此需要改善。

技术实现要素:

9.本发明是为了解决上述那样的课题所做出的,其目的在于获得一种能够实现高效率且宽频带的特性的多赫蒂放大器。

10.本发明的多赫蒂放大器的特征在于,具备:第一晶体管芯片,其具有第一漏极焊盘;第二晶体管芯片,其具有第二漏极焊盘;传输线路;第一电容;第一接合线,其将所述第一漏极焊盘与所述传输线路的一端连接;第二接合线,其将所述第二漏极焊盘与所述第一电容的一端连接;以及输出端子,其连接于所述传输线路的另一端以及所述第一电容的另一端,所述第一电容的电容值被选择为与所述第二接合线的电感谐振。

11.在本发明中,第一电容的电容值被选择为与第二接合线的电感谐振。由此,从第一晶体管芯片以及第二晶体管芯片输出的信号的合成点不在第二晶体管芯片的第二漏极焊盘端,而是移至集成有电路的树脂基板上。因此即使是使用第一接合线以及第二接合线,将第一晶体管芯片以及第二晶体管芯片与树脂基板上的电路连接的结构,也不会产生频率特性的劣化,能够实现高效率且宽频带的特性。

附图说明

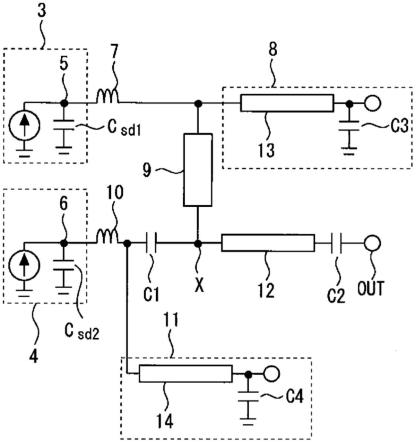

12.图1是表示实施方式1的多赫蒂放大器的电路图。

13.图2是表示实施方式1的多赫蒂放大器的布局图。

14.图3是将实施方式1的多赫蒂放大器的从晶体管到合成点部分提取出来而成的电路图。

15.图4是与图3等效的电路图。

16.图5是与图3等效的电路图。

17.图6是表示比较例1的结构的电磁场计算模型的布局图。

18.图7是表示比较例2的结构的电磁场计算模型的布局图。

19.图8是表示实施方式1的结构的电磁场计算模型的布局图。

20.图9是采用一般使用的非线形晶体管模型计算出的多赫蒂放大器的3db增益压缩点和漏极效率的频率特性。

21.图10是表示400mhz频带的3db增益压缩点和漏极效率的最小值的图。

22.图11是表示将谐振频率用中心频率标准化的情况下的400mhz频带的3db增益压缩点和漏极效率的最小值的图。

23.图12是表示实施方式2的多赫蒂放大器的电路图。

24.图13是表示实施方式2的多赫蒂放大器的布局图。

25.图14是表示实施方式3的多赫蒂放大器的电路图。

26.图15是表示实施方式4的多赫蒂放大器的电路图。

27.图16是对实施方式1、4的3db增益压缩点和漏极效率进行比较的图。

28.图17是表示实施方式5的多赫蒂放大器的电路图。

具体实施方式

29.一边参照附图、一边对实施方式的多赫蒂放大器进行说明。对相同或者对应的构成要素标注相同的附图标记,并且有时省略重复的说明。

30.实施方式1.

31.图1是表示实施方式1的多赫蒂放大器的电路图。图2是表示实施方式1的多赫蒂放大器的布局图。

32.在树脂基板1之上形成有芯片焊盘2。晶体管芯片3、4芯片焊接于芯片焊盘2之上。树脂基板1例如由fr4等材料构成。树脂基板1的基板厚度为200~500um。通过选择基板厚度较薄的材料,从而能够降低晶体管芯片3、4的热阻。另一方面,较厚的树脂基板1通过多层布线化,能够提高电路的集成度,实现小型化以及低成本化。

33.晶体管芯片3、4是gan-hemt等设备。在晶体管芯片3形成有主放大器。在晶体管芯片4形成有峰值放大器。另外,晶体管芯片3、4也可以是同一芯片。

34.晶体管芯片3、4分别具有漏极焊盘5、6。晶体管芯片3、4分别具有源极和漏极之间的寄生电容csd1、csd2。寄生电容csd1、csd2不仅包括晶体管的固有电容,还包括在漏极焊盘5、6的电容。

35.晶体管芯片3的漏极焊盘5经由接合线7而与偏置电路8和传输线路9的一端连接。晶体管芯片4的漏极焊盘6经由接合线10而与电容c1的一端和偏置电路11连接。接合线7、10根据漏极焊盘5、6的尺寸并列配置有多根。接合线7、10的高度相对于晶体管芯片3、4的表面为50um~200um左右,优选设定为较低。

36.电容c1的另一端与传输线路9的另一端连接,并且经由阻抗变换电路12以及电容c2而与输出端子out连接。电容c1例如是表面安装型的层叠陶瓷电容器等。偏置电路8、11、传输线路9、阻抗变换电路12、电容c1、c2、输出端子out集成于树脂基板1之上。

37.偏置电路8具有90度线路13和接地用的电容c3。偏置电路11具有90度线路14和接地用的电容c4。但是偏置电路8、11不限于该结构,只要是具有同样的功能的结构即可。阻抗变换电路12也是90度线路,但不限于此,只要是能够实现期望的阻抗变换的结构即可。

38.传输线路9的电长度和特性阻抗设定为从漏极焊盘5到漏极焊盘6的电长度为90度。电容c1的电容值被选择为与接合线10所具有的等效电感以工作频率的中心频率谐振。由此,从晶体管芯片3、4输出的信号的合成点x不在晶体管芯片4的漏极焊盘6端,而是移至集成有电路的树脂基板1上。

39.图3是将实施方式1的多赫蒂放大器的从晶体管到合成点提取出来的电路图。图4及图5是与图3等效的电路图。电容c1的电容值被设定为与接合线10的电感谐振,因此图3能够如图4那样表示。在等效电路中,合成点x和漏极焊盘6端为相同节点。

40.通过适当地选择传输线路9的长度和线路宽度,能够形成传输线路9的电长度为90度且具有特性阻抗zc的与图5所示的电路等效的电路。另外,zc的选择通常是设计事项,但大多设定为由lp评价等获得的功率匹配的多个阻抗中的与实数分量对应的阻抗。根据图5可知,从主放大器的漏极焊盘5端到信号的合成点x的电长度为90度,并且峰值放大器的漏极焊盘6端到合成点x的电长度为0度,这与常用的多赫蒂放大器的电路图是等效的。因此即使是使用接合线7、10将晶体管芯片3、4与树脂基板1上的电路连接的结构,也不会产生频率特性的劣化,能够实现高效率且宽频带的特性。

41.为了明确实施方式1的效果而进行了多赫蒂放大器的rf特性的计算。图6是表示比较例1的结构的电磁场计算模型的布局图。图7是表示比较例2的结构的电磁场计算模型的布局图。图8是表示实施方式1的结构的电磁场计算模型的布局图。另外,省略偏置电路8、11

和阻抗变换电路12。

42.图6是合成点x为树脂基板上的情况。图7是合成点x为漏极焊盘6的情况。图6、图7均设计为从漏极焊盘5到漏极焊盘6的电长度为90度。计算使用常用的电磁场计算cad软件并考虑了布局造成的影响。树脂基板1的基板厚度为330um,相对介电常数为4.3。传输线路9的线路宽度为150um。晶体管芯片3、4的厚度为100um。以晶体管芯片3、4的上表面为基准,接合线7、10的高度为150um。接合线7、10以100um的间距配置。图8中的电容c1的电容值设定为2.9pf。传输线路9的线路长调整为等效的90度延迟电路的特性阻抗zc为52ω。

43.图9是采用一般使用的非线形晶体管模型计算出的多赫蒂放大器的3db增益压缩点和漏极效率的频率特性。根据计算结果可知,3db增益压缩点(3db compression output power)、漏极效率(drain efficiency)都是实施方式1为最宽频带且高效率。

44.另外,在本实施方式中,从漏极焊盘5到漏极焊盘6的电长度为90度,但实际上只要是

±

10度左右就能够获得足够良好的特性。图10是表示400mhz频带的3db增益压缩点和漏极效率的最小值的图。可知如果电长度以90度为基准

±

10度,则对3db增益压缩点的影响非常小,漏极效率的降低也在-4~5pts左右。

45.另外,电容c1和接合线10严格来说不需要以工作频率的中心频率谐振,即使谐振频率相对于工作频率的中心频率偏差

±

30%左右,也能够实现足够的宽频带且高效率。图11是表示将谐振频率用中心频率标准化的情况下的400mhz频带的3db增益压缩点和漏极效率的最小值的图。可知即使谐振频率偏差30%,3db增益压缩点的劣化也是0.3db左右,漏极效率的降低也小于3pts,因此能够实现足够良好的特性。

46.另外,在本实施方式中以两个晶体管尺寸相同的情况的对称多赫蒂为前提进行了说明,但也可以是晶体管尺寸不同的非对称多赫蒂。

47.实施方式2.

48.图12是表示实施方式2的多赫蒂放大器的电路图。图13是表示实施方式2的多赫蒂放大器的布局图。与实施方式1相比,增加了电感器l1、l2和电容c5、c6。

49.电感器l1的一端与接合线7和传输线路9的连接点连接。电感器l2的一端与接合线10和电容c1的连接点连接。电感器l1的另一端经由电容c5接地。电感器l2的另一端经由电容c6接地。

50.电感器l1、l2例如是表面安装型的芯片部件或者在树脂基板1上形成为高阻抗线路。电容c5、c6用于rf接地,因此选择在工作频率下足够低的阻抗的电容。电感器l1、l2的电感设定为比与寄生电容csd1、csd2并联谐振的值大的值。

51.为了实现实施方式1,从漏极焊盘5到漏极焊盘6的电长度需要是90度。因而寄生电容csd1、csd2的电容值取决于工作频率而具有上限。因此,在寄生电容csd1、csd2大的情况下,无法实现实施方式1。

52.对此,在实施方式2中,电感器l1、l2相对于寄生电容csd1、csd2并联连接,因而能够等效地减小寄生电容的大小。因此,即使寄生电容csd1、csd2大的情况下,也能够实现与实施方式1同样的特性。电感器l1、l2的电感在能够构成电路的范围内尽可能大地设定,这能够实现宽频带的特性。

53.在树脂基板1上构成使用了90度线路的偏置电路的情况下,即使以能够实现的最小线路宽度布局,也无法实现足够高的特性阻抗,这成为电路损失增加的重要因素。对此,

通过将偏置电路8、11连接于电感器l1、l2的接地点,从而能够抑制因偏置电路8、11的连接而引起的电路损失的增加。

54.只要是并联地连接的电容c5、c6从工作频率以两倍高的频带且足够低的阻抗,则也可以省略偏置电路8、11。在该情况下,供电部设定于电容c5、c6与电感器l1、l2的连接点。

55.实施方式3.

56.图14是表示实施方式3的多赫蒂放大器的电路图。与实施方式2相比,通过电容c5使电感器l1、l2的接地共通化,通过偏置电路8使偏置电路共通化。由此能够使电路小型化。其他结构以及效果与实施方式2相同。

57.实施方式4.

58.图15是表示实施方式4的多赫蒂放大器的电路图。与实施方式1相比,在合成点x连接有由电容c7、c8和电感器l3构成的并联谐振电路15。电容c8是接地用的电容,选择在动作频带下足够低的阻抗的电容。电容c7和电感器l3被选择成以工作频率的中心频率并联谐振。

59.并联谐振电路15的频率特性具有与从漏极焊盘5到合成点x的等效90度延迟电路的频率特性相反的极性。因而电路的频率特性降低。因此,实施方式4能够期待比实施方式1更宽频带的特性。本电路的作用和效果在以往技术中已经示出,因此省略详细说明。为了获得该效果,并联谐振电路15需要与信号的合成点连接。因此,合成点不是漏极焊盘端,而是位于树脂基板1上,这样能够不引起不平衡动作而实现这一点对于现有技术是有利的。

60.为了明确实施方式4的效果,进行了多赫蒂放大器的rf特性的计算。图16是将实施方式1、4的3db增益压缩点和漏极效率进行了比较的图。实施方式4中的电容c7为1.67pf,电容c8为7pf,电感器l3为1.294nh。可知3db增益压缩点、漏极效率均为实施方式4比实施方式1宽频带且高效率。

61.另外,本实施方式能够与实施方式2或3的结构组合。另外,在电容c7由表面安装型的芯片电容构成的情况下,通过将两个芯片电容并联连接而构成,由此能够减少电路损失。两个芯片电容的电容值之和被选择为与电容c7相同。

62.实施方式5.

63.图17是表示实施方式5的多赫蒂放大器的电路图。与实施方式1相比,偏置电路8的连接位置变更为合成点x。若从合成点x观察偏置电路8的阻抗,则表现出与实施方式4的并联谐振电路同样的频率特性。因此,具有与从漏极焊盘5到合成点x的90度延迟电路的频率特性相反的极性,因而电路的频率特性降低。因此,获得与实施方式4同样的效果,并且删除实施方式4中的并联谐振电路而能够小型化。另外,本实施方式能够与实施方式2的结构组合。

64.附图标记说明

[0065]1…

树脂基板;3

…

晶体管芯片(第一晶体管芯片);4

…

晶体管芯片(第二晶体管芯片);5

…

漏极焊盘(第一漏极焊盘);6

…

漏极焊盘(第二漏极焊盘);7

…

接合线(第一接合线);8

…

偏置电路(第一偏置电路);9

…

传输线路;10

…

接合线(第二接合线);11

…

偏置电路(第二偏置电路);15

…

并联谐振电路;c1

…

电容(第一电容);c5

…

电容(第二电容);c6

…

电容(第三电容);l1

…

电感器(第一电感器);l2

…

电感器(第二电感器);out

…

输出端子。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。