1.本公开涉及光电子器件技术领域,尤其涉及一种掩埋结构半导体激光器及其制备方法。

背景技术:

2.掩埋结构半导体激光器具有阈值电流低、发光效率高、功耗小及特征温度高等优点,在光纤通信系统中有重要的应用价值。掩埋结构半导体激光器中利用起电流阻挡作用的半导体材料形成的电流通道将电流限制在有源量子阱材料范围内,从而改善了激光器性能。控制电流通道相对于量子阱材料的位置对掩埋结构半导体激光器的性能至关重要,是器件结构设计的重要内容。

技术实现要素:

3.鉴于上述问题,本发明提供了一种掩埋结构半导体激光器及其制备方法,以解决上述技术问题。

4.本公开的一个方面提供了一种掩埋结构半导体激光器,包括:

5.衬底、缓冲层、有源层、盖层、掩埋结构及接触层;

6.所述缓冲层、有源层、盖层自下而上生长于所述衬底上,被刻蚀至衬底,形成底部宽、顶部窄的梯形结构;

7.所述掩埋结构对称设于所述梯形结构两侧,且将所述盖层上表面的两侧区域覆盖,使所述盖层上表面中间区域的宽度小于所述有源层的宽度;

8.所述接触层设于所述掩埋结构和所述盖层上。

9.可选地,所述掩埋结构的第一上表面与所述衬底表面平行,第二上表面与所述第一上表面连接,向内倾斜延伸至所述盖层的中间区域。

10.可选地,所述掩埋结构的材料为反向pn结材料或半绝缘半导体材料。

11.可选地,所述衬底的材料为inp,所述缓冲层的材料为inp,所述有源层的材料为ingaasp,所述盖层的材料为inp。

12.本公开的另一个方面提供了一种掩埋结构半导体激光器的制备方法,包括:

13.在衬底上依次生长缓冲层、有源层、盖层;

14.在所述盖层上制作双层掩膜,包括掩膜上层和掩膜下层;

15.根据所述掩膜上层上的掩膜图形去除所述掩膜上层以外区域的盖层、有源层、缓冲层至衬底,形成底部宽、顶部窄的梯形结构;

16.根据所述掩膜上层上的掩膜图形腐蚀所述掩膜下层,使所述掩膜下层的宽度小于所述有源层的宽度,去除所述掩膜上层;

17.生长掩埋材料,形成掩埋结构,所述掩埋结构对称设于所述梯形结构两侧,且将所述掩膜下层两侧的盖层的上表面覆盖,使所述盖层上表面中间区域的宽度小于所述有源层的宽度;

18.去除所述掩膜下层,在所述掩埋结构和所述盖层上生长接触层。

19.在本公开实施例采用的上述至少一个技术方案能够达到以下有益效果:

20.本公开实施例提供的一种掩埋结构半导体激光器,通过掩埋结构的设置形成了宽度小于有源层的电流限制通道,可以通过采用双层掩膜实现了对掩埋激光器中电流限制通道尺寸及其相对于量子阱材料位置的有效控制,有利于减小漏电流。

附图说明

21.为了更完整地理解本公开及其优势,现在将参考结合附图的以下描述,其中:

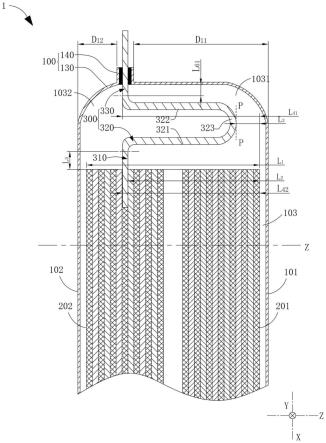

22.图1示意性示出了本公开实施例提供的一种掩埋结构半导体激光器的初始材料结构示意图;

23.图2示意性示出了本公开实施例提供的一种掩埋结构半导体激光器在制备过程中根据掩膜上层图形刻蚀后的结构示意图;

24.图3示意性示出了本公开实施例提供的一种掩埋结构半导体激光器在制备过程中的掩膜下层刻蚀后的示意图;

25.图4示意性示出了本公开实施例提供的一种掩埋结构半导体激光器在制备过程中去除掩膜上层后的示意图;

26.图5示意性示出了本公开实施例提供的一种掩埋结构半导体激光器的掩膜结构的生长示意图;

27.图6示意性示出了本公开实施例提供的一种掩埋结构半导体激光器的接触层的生长示意图;

28.附图标记说明:

29.衬底-10;缓冲层-20;有源层-30;盖层-40;掩膜下层-50;掩膜上层-60;掩埋结构-70;接触层80。

具体实施方式

30.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。在下面的详细描述中,为便于解释,阐述了许多具体的细节以提供对本公开实施例的全面理解。然而,明显地,一个或多个实施例在没有这些具体细节的情况下也可以被实施。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

31.在此使用的术语仅仅是为了描述具体实施例,而并非意在限制本公开。在此使用的术语“包括”、“包含”等表明了所述特征、步骤、操作和/或部件的存在,但是并不排除存在或添加一个或多个其他特征、步骤、操作或部件。

32.在此使用的所有术语(包括技术和科学术语)具有本领域技术人员通常所理解的含义,除非另外定义。应注意,这里使用的术语应解释为具有与本说明书的上下文相一致的含义,而不应以理想化或过于刻板的方式来解释。

33.图1~6示意性示出了本公开实施例提供的掩埋结构半导体激光器在制备过程中的结构变化。

34.如图1~6所示,本公开实施例提供了一种掩埋结构半导体激光器,包括:衬底10、

缓冲层20、有源层30、盖层40、掩埋结构70及接触层80;缓冲层20、有源层30、盖层40自下而上生长于衬底10上,被刻蚀至衬底10,形成底部宽、顶部窄的梯形结构;掩埋结构70对称设于梯形结构两侧,且将盖层40上表面的两侧区域覆盖,使盖层40上表面中间区域的宽度小于有源层30的宽度;接触层80设于掩埋结构70和盖层40上。

35.在该掩埋结构半导体激光器中,掩埋结构70的第一上表面与衬底10表面平行,第二上表面与第一上表面连接,向内倾斜延伸至盖层40的中间区域,形成了宽度小于有源材料宽度wa的电流限制通道,可以有效提升电流限制作用。

36.可选地,掩埋结构70的材料为反向pn结材料或半绝缘半导体材料。

37.可选地,衬底10的材料为inp,缓冲层20的材料为inp,有源层30的材料为ingaasp,盖层40的材料为inp。

38.本公开实施例还提供了一种掩埋结构半导体激光器的制备方法,以inp基材料体系为例,以参考图1~6,该方法包括如下步骤。

39.如图1所示,步骤一,在inp衬底10上依次生长inp缓冲层20、ingaasp有源层30、盖层40。

40.如图1所示,步骤二,在盖层40上制作双层掩膜,包括掩膜上层60和掩膜下层50。可选的,掩膜下层50材料为sio2,掩膜上层60材料为光刻胶,掩膜图形宽度为w1。

41.如图2所示,步骤三,根据掩膜上层60上的掩膜图形去除掩膜上层60以外区域的盖层40、有源层30、缓冲层20至衬底10,形成底部宽、顶部窄的梯形结构。掩膜下未被去除的盖层40顶部宽度为w2,w2小于或等于掩膜图形宽度w1及有源层30宽度wa

42.如图3所示,步骤四,根据掩膜上层60上的掩膜图形腐蚀掩膜下层50,腐蚀后的掩膜下层50宽度为w3,w3小于w2,掩膜下层50的宽度小于有源层30的宽度。

43.如图4所示,在掩膜下层50腐蚀完毕后,利用丙酮去除掩膜上层60。

44.如图5所示,步骤五,严格清洗器件表面后,生长掩埋材料,形成掩埋结构70,掩埋结构70对称设于梯形结构两侧,且将掩膜下层50两侧的盖层40的上表面覆盖,使盖层40上表面中间区域(即掩膜下层50所在位置)的宽度小于有源层30的宽度。由于掩膜下层50的宽度w3小于w2,掩埋结构70的边缘在平行于衬底10的方向向盖层40及有源层30上方延伸,形成了宽度小于有源材料宽度wa的电流限制通道,可以有效提升电流限制作用。

45.如图6所示,步骤6,去除掩膜下层50,在掩埋结构70和盖层40上生长接触层80。

46.本公开实施例提供的掩埋结构半导体激光器的制备方法利用双层掩膜实现了对掩埋激光器中电流限制通道尺寸及其相对于量子阱材料位置的有效控制,有利于减小漏电流。

47.本领域技术人员可以理解,本公开的各个实施例和/或权利要求中记载的特征可以进行多种组合或/或结合,即使这样的组合或结合没有明确记载于本公开中。特别地,在不脱离本公开精神和教导的情况下,本公开的各个实施例和/或权利要求中记载的特征可以进行多种组合和/或结合。所有这些组合和/或结合均落入本公开的范围。

48.尽管已经参照本公开的特定示例性实施例示出并描述了本公开,但是本领域技术人员应该理解,在不背离所附权利要求及其等同物限定的本公开的精神和范围的情况下,可以对本公开进行形式和细节上的多种改变。因此,本公开的范围不应该限于上述实施例,而是应该不仅由所附权利要求来进行确定,还由所附权利要求的等同物来进行限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。