模/数转换器

背景技术:

1.各种模/数数据转换器和转换技术可用于将电信号从模拟域转换为数字域。通常,模/数转换的过程包含对模拟信号进行采样,并将采样的模拟信号与阈值进行比较。取决于比较结果而记录二分结果。将样本与阈值进行比较的过程可重复数次,其中每次连续比较使用不同的阈值和样本的残留。迭代次数通常由特定迭代中的噪声电平以及最终数字信号的分辨率确定。

2.逐次逼近寄存器(sar)转换器是模/数转换器(adc)的一个实例。sar adc对最佳对应于模拟信号的电压的数字值执行二分搜索。在sar adc中,将电压输入与参考电压的一半进行比较。如果电压输入大于参考电压的一半,那么在寄存器中存储逻辑

‘1’

。或者,如果电压输入小于参考电压的一半,那么在寄存器中存储逻辑

‘0’

。接下来,如果先前比较指示电压输入大于参考电压的一半,那么将电压输入与参考电压的四分之三进行比较。同样,如果比较指示大于条件,那么在寄存器中存储逻辑

‘1’

。相反,如果比较指示小于条件,那么在寄存器中存储逻辑

‘0’

。或者,先前比较指示电压输入小于参考电压的一半,那么将电压输入与参考电压的四分之一进行比较。同样,如果比较指示大于条件,那么在寄存器中存储逻辑

‘1’

。相反,如果比较指示小于条件,那么在寄存器中存储逻辑

‘0’

。对于参考电压的低阶倍数,此过程继续进行。如将理解,上述过程能够在相对较短时间内提供具有高分辨率的adc结果。特定来说,只能使用单个迭代来产生每一位分辨率。例如,对于10位分辨率,理论上需要10次迭代,且对于20位分辨率,理论上需要20次迭代。

技术实现要素:

3.本文公开了一种两步逐次逼近寄存器(sar)模/数转换器(adc),其通过动态错误校正来提高粗略sar adc分辨率。在一个实例中,一种模/数转换器(adc)电路包含信号输入端子、采样和保持电路和逐次逼近寄存器(sar)adc。所述采样和保持电路包含耦合到所述信号输入端子的输入端子。所述sar adc包含比较器、第一电容式数/模转换器(cdac)和第二cdac。所述第一cdac包含耦合到所述信号输入端子的第一输入端子、耦合到所述采样和保持电路的输出端子的第二输入端子和耦合到所述比较器的第一输入端子的输出端子。所述第二cdac包含耦合到所述信号输入端子的第一输入端子、耦合到所述比较器的第二输入端子的输出端子。

4.在另一实例中,一种模/数转换器(adc)电路包含采样和保持电路和sar adc。所述采样和保持电路经配置以对待数字化的输入信号进行采样。所述sar adc耦合到所述采样和保持电路,并经配置以对所述输入信号进行数字化。所述sar adc包含比较器、第一cdac和第二cdac。所述第一cdac耦合到所述比较器的第一输入端子,并经配置以对待数字化的所述输入信号进行采样,以及对所述采样和保持电路的输出进行采样。所述第二cdac耦合到所述比较器的第二输入端子,并经配置以对待数字化的所述输入信号进行采样。

5.在另外实例中,一种adc电路包含第一信号输入端子、第二信号输入端子、第一采样和保持电路、第二采样和保持电路和sar adc。所述第一采样和保持电路包含耦合到所述

第一信号输入端子的输入端子。所述第二采样和保持电路包含耦合到所述第二信号输入端子的输入端子。所述sar adc包含比较器、第一cdac和第二cdac。所述第一cdac包含耦合到所述第一信号输入端子的第一输入端子、耦合到所述第一采样和保持电路的输出端子的第二输入端子和耦合到所述比较器的第一输入端子的输出端子。所述第二cdac包含耦合到所述第二信号输入端子的第一输入端子、耦合到所述第二采样和保持电路的输出端子的第二输入端子、耦合到所述比较器的第二输入端子的输出端子。

附图说明

6.针对各种实例的具体描述,现在参考附图,附图中:

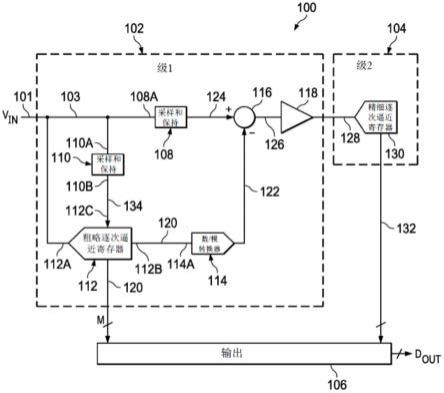

7.图1展示根据本描述的两步逐次逼近寄存器(sar)模/数转换器(adc)的框图;

8.图2展示根据本描述的采样和保持电路和缓冲器的示意图;

9.图3展示根据本描述的具有动态误差连接的两步sar adc的第一级的框图;

10.图4展示根据本描述的粗略sar adc的示意图;

11.图5展示根据本描述的用于粗略sar adc中的数字化的时序图;

12.图6展示根据本描述的差分输入两步sar adc的框图;和

13.图7展示根据本描述的差分输入粗略sar adc的示意图。

具体实施方式

14.在此描述中,术语“耦合(couple/couples)”意味着间接或直接有线或无线连接。因此,如果第一装置耦合到第二装置,那么所述连接可为通过直接连接或通过经由其它装置及连接的间接连接。而且,在此描述中,陈述“基于”意味着“至少部分基于”。因此,如果x是基于y,那么x可依据y及任何数目个其它因素而变。

15.在两步逐次逼近寄存器(sar)模/数转换器(adc)中,粗略级sar adc的分辨率受到采样带宽失配、时钟偏移和其它因素的限制。一些两步sar adc试图通过使用采样和保持放大器或将粗略adc的电容式模/数转换器(cdac)与主cdac合并来提高分辨率。但是,采样和保持放大器消耗过多的功率,并且将粗略adc cdac与主cdac合并限制了转换速度。

16.本文公开的两步sar adc通过减少与采样带宽失配相关联的误差在不添加采样和保持放大器或合并粗略adc cdac与主cdac的情况下提高粗略adc分辨率。本公开的两步sar adc在转换期间修改粗略sar adc的搜索目的地,以补偿不同采样路径中的信号相依残留误差。实施方案使用主cdac的按比例缩小的副本来产生主cdac的采样输入电压,并将采样输入电压施加在粗略adc cdac中以调整粗略sar adc的搜索目的地。经调整的搜索目的地补偿不同采样路径中的误差。

17.图1展示根据本描述的两步逐次逼近寄存器(sar)模/数转换器(adc)100的框图。两步sar adc 100包含第一级102、第二级104和输出电路系统106。两步sar adc 100产生表示在信号输入端子101处接收的模拟信号的m位数字输出。第一级102产生m个位中的预定数目的最高有效位,且第二级104产生m个位的其余部分。例如,在产生16位输出的两步sar adc 100的实施方案中,第一级102产生6个最高有效位(具有1个或更多个额外冗余位),且第二级104产生10个最低有效位。输出电路系统106接收由第一级102和第二级104产生的数字值,并组合(例如,级联与重叠)数字值以产生数字输出值。两步架构允许减小第一级102

和第二级104中使用的电容器的大小。

18.第一级102包含采样和保持电路108、采样和保持电路110、sar adc 112、数/模转换器(dac)114(主dac)、减法电路系统116和残余放大器118。采样和保持电路108、采样和保持电路110和sar adc 112耦合到信号输入端子101。采样和保持电路108包含耦合到信号输入端子101的输入端子108a,采样和保持电路110包含耦合到信号输入端子101的输入端子110a,且sar adc 112包含耦合到信号输入端子101的输入端子112a。采样和保持电路108、采样和保持电路110和sar adc 112中的每一者获取在信号输入端子101处提供的待数字化的输入信号103的样本。sar adc 112的输出端子112b耦合到输出电路系统106及dac 114的输入端子114a。sar adc 112将所获取的样本数字化,并将数字值120提供到输出电路系统106和dac 114。dac 114将数字值120转换为模拟电压122。减法电路系统116耦合到采样和保持电路108、dac 114和残余放大器118。减法电路系统116从采样和保持电路108提供的采样124中减去模拟电压122,以产生表示sar adc 112的总未调整误差的残余信号126。残余放大器118耦合到减法电路系统116,并放大残余信号126以产生经放大的残余信号128。

19.第二级104包含sar adc 130。sar adc 130耦合到残余放大器118,并且对经放大的残余信号128数字化以产生数字值132。sar adc 130将数字值132提供到输出电路系统106以与数字值120组合。

20.采样和保持电路110是采样和保持电路108的按比例缩小版本。采样和保持电路110包含耦合到信号输入端子101的输入端子110a和耦合到sar adc 112的输入端子112c的输出端子110b。对于由采样和保持电路108获取的任何给定样本124,采样和保持电路110获取具有与样本124相同的电压的样本134。图2展示根据本描述的采样和保持电路110的实施方案的示意图。采样和保持电路108和sar adc 112也在图2中展示以供参考。在图2中,采样和保持电路108包含比采样和保持电路110更高的电容和更低的电阻。采样和保持电路110的电容和电阻与采样和保持电路108的电容和电阻的比率在两步sar adc 100的不同实施方案中有所不同。

21.采样和保持电路110包含采样电容器202、电阻器204(表示开关电阻)、电阻器206(表示开关电阻)、开关208、开关210、放大器212、开关214、开关216和开关218。当对输入信号103进行采样时,开关208和210闭合,且当采样完成并且采样和保持电路110处于保持状态时,开关208和210断开。放大器212缓冲跨采样电容器202的电压以提供给sar adc 112。在采样期间(例如,在采样间隔内),开关214和开关216断开,且开关218闭合,从而将放大器212与采样电容器202断开。类似地,当采样和保持电路110处于保持状态(例如,在保持间隔中)时,开关214和开关216闭合,且开关218断开,从而将放大器212与采样电容器202连接。

22.放大器212包含经由开关214耦合到采样电容器202的输入端子212a和耦合到sar adc 112的输入端子112c的输出端子212b。开关214包含耦合到采样电容器202的端子202b的端子214a和耦合到放大器212的输入端子212a的端子214b。开关216包含耦合到采样电容器202的端子202a的端子216a和耦合到放大器212的输出端子212b的端子216b。开关218包含耦合到放大器212的输出端子212b的端子218a和耦合到放大器212的输入端子212a的端子218b。

23.图3展示粗略sar adc 300的框图。粗略sar adc 300是sar adc 112的实施方案。粗略sar adc 300包含用于对输入信号103进行采样的采样网络302。采样信号308(v

n2

)提供

在采样网络302的输出端子处。但是,由于采样带宽的不同,采样信号308不同于由采样和保持电路110提供的样本134(v

n1

)。如前文解释,样本134与从中导出残余信号126的样本124相同。粗略sar adc 300通过获得样本134与采样信号308的差,且从采样信号308中减去差,以产生与样本134的电压相同的电压304,以用作数字化中的参考,来补偿采样信号308与样本124的差。

24.图4展示根据本描述的粗略sar adc 400的示意图。sar adc 400是sar adc 112和sar adc 300的实施方案。sar adc 400包含cdac 402、cdac 404、比较器406、sar控制电路408、开关410和开关412。cdac 402包含二进制加权电容器414和开关416。开关416是可控的,以将二进制加权电容器414的底板连接到输入端子112a或输入端子112c,且借此将二进制加权电容器414充电到输入信号103或样本134。cdac 402包含耦合到比较器406的输入端子406a的输出端子402a、耦合到sar adc 112的输入端子112c的输入端子402b、以及耦合到sar adc 112的输入端子112a的输入端子402c。二进制加权电容器414的顶板耦合到输出端子402a。

25.类似地,cdac 404包含二进制加权电容器418和开关420。开关420是可控的,以将二进制加权电容器418的底板连接到输入端子112a、参考电压源或共同电压源(例如,接地)。开关410和412是可控的,以分别将二进制加权电容器414和二进制加权电容器418的顶板连接到接地。cdac 404包含耦合到比较器406的输入端子406b的输出端子404a和耦合到sar adc 112的输入端子112a的输入端子404c。二进制加权电容器418的顶板耦合到输出端子404a。

26.比较器406将二进制加权电容器418的顶板上的电压与二进制加权电容器414的顶板上的电压进行比较,并将比较结果提供到sar控制电路408。sar控制电路408耦合到比较器406、cdac 402和cdac 404,且基于比较结果设置数字值120的位。sar控制电路408产生控制开关410、开关412、开关416和开关420的开关控制信号422。sar控制电路408基于比较器406的输出确定将如何设置开关420,并相应地激活开关控制信号422。

27.在每一样本数字化开始时(获取阶段),sar控制电路408设置开关416和开关420,以将二进制加权电容器414和二进制加权电容器418的底板连接到sar adc 112的输入端子112a,使得二进制加权电容器414和二进制加权电容器418被充电到输入信号103。在sar控制电路408选择数字值120的一或多个位(位的数目基于校正动态误差所需的冗余)的值之后,sar控制电路408设置cdac 402的开关416以将二进制加权电容器414的底板连接到sar adc 112的输入端子112c,从而将样本134施加到二进制加权电容器414的底板。因此,将二进制加权电容器414的顶板上的电压设置为样本134的电压减去先前从输入端子112a采样的电压(即,v

n1-v

n2

)。因此,施加到比较器406的参考电压从零偏移到v

n1-v

n2

,且数字化继续进行。通过将参考从零偏移到v

n1-v

n2

,由sar adc 400数字化的电压实际上是样本134的电压,而不是由二进制加权电容器418从输入端子112a采样的电压。

28.图5展示用于使用sar adc 400作为两步sar adc 100中的粗略sar adc来进行数字化的时序图。在间隔502中,采样和保持电路108、采样和保持电路110、cdac 402和cdac 404对输入信号103进行采样。在间隔502的末尾,开关214和216闭合,并且放大器212的输出在间隔504上稳定。在间隔502的末尾,开关416被设置成将信号输入端子101与二进制加权电容器414断开。在间隔514期间,电容器416的底板浮动。在间隔504的末尾,在dec位间隔之

前,开关416被设置为将采样和保持电路110的输出端子110b连接到二进制加权电容器414,因此二进制加权电容器414的顶板变为v

n1-v

n2

。在间隔506中,确定在间隔504中选择的位中的误差(与在间隔504上使用零作为参考有关的误差)。在一些实施方案中,在由两步sar adc 100完成数字化之后,对误差进行数字校正。在间隔508中,使用v

n1-v

n2

作为在比较器406的406a处施加的参考电压(而非常规的零)在sar adc 400中进行剩余位决策。

29.图6展示根据本描述的差分输入两步sar adc 600的框图。差分输入两步sar adc 600包含第一级602、第二级604和输出电路系统606。第一级602包含采样和保持电路608、采样和保持电路609、采样和保持电路610、采样和保持电路611、sar adc 612、数/模转换器(dac)614(主dac)、减法电路系统616和残余放大器618。采样和保持电路608、采样和保持电路610和sar adc 612耦合到信号输入端子601。采样和保持电路609、采样和保持电路611和sar adc 612耦合到信号输入端子603。采样和保持电路608包含耦合到信号输入端子601的输入端子608a,采样和保持电路610包含耦合到信号输入端子601的输入端子610a,并且sar adc 612包含耦合到信号输入端子601的输入端子612a。采样和保持电路608、采样和保持电路610和sar adc 612中的每一者获取在信号输入端子601处提供的待数字化的输入信号605(v

in

)的样本。

30.采样和保持电路609包含耦合到信号输入端子603的输入端子609a,采样和保持电路611包含耦合到信号输入端子603的输入端子611a,并且sar adc 612包含耦合到信号输入端子603的输入端子612e。采样和保持电路609、采样和保持电路611和sar adc 612中的每一者获取在信号输入端子603处提供的待数字化的输入信号607(v

in-)的样本。

31.采样和保持电路608和采样和保持电路609是采样和保持电路108的实施方案。采样和保持电路610和采样和保持电路611是采样和保持电路110的实施方案。采样和保持电路610是采样和保持电路608的按比例缩小版本,且采样和保持电路611是采样和保持电路609的按比例缩小版本。采样和保持电路610包含耦合到信号输入端子601的输入端子610a和耦合到sar adc 612的输入端子612c的输出端子610b。对于由采样和保持电路608获取的任何给定样本624,采样和保持电路610获取具有与样本624相同的电压的样本634。采样和保持电路611包含耦合到信号输入端子603的输入端子611a和耦合到sar adc 612的输入端子612d的输出端子611b。对于由采样和保持电路609获取的任何给定样本644,采样和保持电路611获取具有与样本644相同的电压的样本635。

32.图7展示根据本描述的差分输入粗略sar adc 700的示意图。差分输入粗略sar adc 700是sar adc 612的实施方案。差分输入粗略sar adc 700包含cdac 702、cdac 704、cdac 714、cdac 716、比较器706、sar控制电路708、开关710、开关712、开关718和开关720。sar控制电路708耦合到比较器706、cdac 702、cdac 704、cdac 714和cdac 716。cdac 702、cdac 704、cdac 714和cdac 716包含二进制加权电容器和开关。在cdac 702中,开关是可控的以将电容器的底板连接到输入端子612e或输入端子612d,且借此将电容器充电到输入信号607或样本635的电压。cdac 702包含耦合到比较器706的输入706d的输出端子702a、耦合到输入端子612d的输入端子702b和耦合到输入端子612e的输入端子702c。cdac 702的电容器的顶板耦合到输出端子702a。在cdac 702中,开关是可控的以将cdac 702的电容器的底板连接到输入端子612e或输入端子612d,且借此将电容器充电到输入信号607或样本635的电压。

33.cdac 716包含耦合到比较器706的输入端子706c的输出端子716a、耦合到输入端子612c的输入端子716b、以及耦合到sar adc 612的输入端子612a的输入端子716c。cdac 716的电容器的顶板耦合到输出端子716a。在cdac 716中,开关是可控的以将cdac 716的电容器的底板连接到输入端子612a或输入端子612c,且借此将电容器充电到输入信号605或样本634的电压。

34.cdac 704包含耦合到比较器706的输入端子706b的输出端子704a和耦合到输入端子612e的输入端子704b。cdac 704的电容器的顶板耦合到输出端子704a。cdac 704的开关是可控的,以将电容器的底板连接到输入端子612e、参考电压源或共同电压源(例如,接地)。

35.cdac 714包含耦合到比较器706的输入端子706a的输出端子714a和耦合到输入端子612a的输入端子714b。cdac 714的电容器的顶板耦合到输出端子714a。cdac714的开关是可控的,以将电容器的底板连接到输入端子612a、参考电压源或共同电压源(例如,接地)。

36.在每一采样数字化开始时,sar控制电路708设置cdac 702和cdac 704的开关,以将cdac 702和cdac 704的电容器的底板连接到信号输入端子603,并将cdac 702和cdac 704的电容器充电到输入信号607的电压。在sar控制电路708选择数字值620的一或多个位的值之后,sar控制电路708经由开关控制信号722设置cdac 702的开关以将cdac 702的电容器的底板与信号输入端子603断开,并将cdac 702的电容器的底板连接到采样和保持电路611的输出611b,以将电容器充电到样本635的电压。因此,cdac 702的电容器的顶板上的电压被设置为样本635的电压减去输入信号607的先前采样的电压。

37.类似地,在每一采样数字化开始时,sar控制电路708设置cdac 714和cdac 716的开关,以将cdac 714和cdac 716的电容器的底板连接到信号输入端子601,并将cdac 714和cdac 716的电容器充电到输入信号605的电压。在sar控制电路708选择数字值620的一或多个位的值之后,sar控制电路708设置cdac 716的开关以将cdac 716的电容器的底板与信号输入端子601断开,并将cdac 716的电容器的底板连接到采样和保持电路610的输出610b,以将电容器充电到样本634的电压。因此,cdac 716的电容器的顶板上的电压被设置为样本634的电压减去输入信号605的先前采样的电压。

38.在所描述实施例中,修改是可能的,且在权利要求书的范围内,其它实施例是可能的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。