技术特征:

1.一种模/数转换器(adc)电路,其包括:信号输入端子;采样和保持电路,其包括耦合到所述信号输入端子的输入端子;逐次逼近寄存器(sar)adc,其包括:比较器;第一电容式数/模转换器(cdac),其包括:第一输入端子,其耦合到所述信号输入端子;第二输入端子,其耦合到所述采样和保持电路的输出端子;及输出端子,其耦合到所述比较器的第一输入端子;及第二cdac,其包括:第一输入端子,其耦合到所述信号输入端子;及输出端子,其耦合到所述比较器的第二输入端子。2.根据权利要求1所述的adc电路,其中所述采样和保持电路包括:采样电容器;及放大器,其包括:输入端子,其耦合到所述采样电容器;及输出端子,其耦合到所述第一cdac的所述第二输入端子。3.根据权利要求2所述的adc电路,其中所述采样和保持电路包括:第一开关,其包括:第一端子,其耦合到所述采样电容器的第一端子;及第二端子,其耦合到所述放大器的所述输入端子;第二开关,其包括:第一端子,其耦合到所述采样电容器的第二端子;及第二端子,其耦合到所述放大器的所述输出端子;及第三开关,其包括:第一端子,其耦合到所述放大器的所述输出端子;及第二端子,其耦合到所述放大器的所述输入端子。4.根据权利要求1所述的adc电路,其中:所述采样和保持电路为第一采样和保持电路;且所述adc电路包括第二采样和保持电路,其包括耦合到所述信号输入端子的输入端子。5.根据权利要求4所述的adc电路,其进一步包括:主数/模转换器(dac),其包括耦合到所述sar adc的输出的输入;及减法电路系统,其耦合到所述主dac和所述第二采样和保持电路。6.根据权利要求5所述的adc电路,其中:所述sar adc是第一sar adc;且所述adc电路进一步包括:残余放大器,其耦合到所述减法电路系统;及第二sar adc,其耦合到所述残余放大器。

7.根据权利要求1所述的adc电路,其中所述sar adc进一步包括sar控制电路,所述sar控制电路耦合到所述比较器和所述第一cdac,并且经配置以在给定位决策循环中:将所述第一cdac的电容器的底板与所述信号输入端子断开;及将所述底板连接到所述采样和保持电路。8.一种模/数转换器(adc)电路,其包括:采样和保持电路,其经配置以对待数字化的输入信号进行采样;逐次逼近寄存器(sar)adc,其耦合到所述采样和保持电路,并经配置以数字化所述输入信号;其中所述sar adc包括:比较器;第一电容式数/模转换器(cdac),其耦合到所述比较器的第一输入,并经配置以:对待数字化的所述输入信号进行采样;及对所述采样和保持电路的输出进行采样;及第二cdac,其耦合到所述比较器的第二输入,并经配置以对待数字化的所述输入信号进行采样。9.根据权利要求8所述的adc电路,其进一步包括sar控制电路,所述sar控制电路耦合到所述比较器、所述第一cdac和所述第二cdac,并且经配置以:设置所述第一cdac的开关以在第一位的选择期间将所述第一cdac的电容器充电到待数字化的所述输入信号的电压;及设置所述第一cdac的开关以在第二位的选择期间将所述第一cdac的电容器充电到所述采样和保持电路的所述输出的电压。10.根据权利要求9所述的adc电路,其中所述第一cdac经配置以向所述比较器提供等于待数字化的所述输入信号的所述电压与所述采样和保持电路的所述输出的所述电压的差的电压。11.根据权利要求8所述的adc电路,其中:所述采样和保持电路为第一采样和保持电路;所述adc电路包括第二采样和保持电路,所述第二采样和保持电路经配置以对待数字化的所述输入信号进行采样;且所述第一采样和保持电路包括所述第二采样和保持电路的按比例缩小版本。12.根据权利要求8所述的adc电路,其中所述采样和保持电路包括:采样电容器;放大器;及开关,其经配置以:在采样间隔内将所述放大器与所述采样电容器断开;及在保持间隔内将所述放大器连接到所述采样电容器。13.根据权利要求8所述的adc电路,其进一步包括:主dac,其耦合到所述sar adc,并经配置以产生对应于所述sar adc产生的数字值的电压;及减法电路系统,其耦合到所述主dac,并经配置以产生所述采样和保持电路的所述输出与所述主dac产生的所述电压的差。

14.根据权利要求13所述的adc电路,其中:所述sar adc是第一sar adc;且所述adc电路进一步包括:残余放大器,其耦合到所述减法电路系统,并经配置以放大所述减法电路系统的输出;及第二sar adc,其耦合到所述残余放大器,并经配置以数字化所述残余放大器的输出。15.一种adc电路,其包括:第一信号输入端子;第二信号输入端子;第一采样和保持电路,其包括耦合到所述第一信号输入端子的输入端子;第二采样和保持电路,其包括耦合到所述第二信号输入端子的输入端子;逐次逼近寄存器(sar)adc,其包括:比较器;第一电容式数/模转换器(cdac),其包括:第一输入端子,其耦合到所述第一信号输入端子;第二输入端子,其耦合到所述第一采样和保持电路的输出端子;及输出端子,其耦合到所述比较器的第一输入端子;及第二cdac,其包括:第一输入端子,其耦合到所述第二信号输入端子;第二输入端子,其耦合到所述第二采样和保持电路的输出端子;及输出端子,其耦合到所述比较器的第二输入端子。16.根据权利要求15所述的adc电路,其中所述sar adc包括:第三cdac,其包括:第一输入端子,其耦合到所述第一信号输入端子;及输出端子,其耦合到所述比较器的第三输入端子;及第四cdac,其包括:第一输入端子,其耦合到所述第二信号输入端子;及输出端子,其耦合到所述比较器的第四输入端子。17.根据权利要求15所述的adc电路,其中所述第一采样和保持电路包括:第一采样电容器;第一放大器,其包括耦合到所述第一cdac的所述第二输入端子的输出端子;第一开关,其包括:第一端子,其耦合到所述第一采样电容器的第一端子;及第二端子,其耦合到所述第一放大器的输入端子;第二开关,其包括:第一端子,其耦合到所述第一采样电容器的第二端子;及第二端子,其耦合到所述第一放大器的所述输出端子;及第三开关,其包括:第一端子,其耦合到所述第一放大器的所述输出端子;及

第二端子,其耦合到所述第一放大器的所述输入端子。18.根据权利要求17所述的adc电路,其中所述第二采样和保持电路包括:第二采样电容器;第二放大器,其包括耦合所述第二cdac的第二输入端子的输出端子;第三开关,其包括:第一端子,其耦合到所述第二采样电容器的第一端子;及第二端子,其耦合到所述第二放大器的输入端子;第四开关,其包括:第一端子,其耦合到所述第二采样电容器的第二端子;及第二端子,其耦合到所述第二放大器的所述输出端子;及第五开关,其包括:第一端子,其耦合到所述第二放大器的所述输出端子;及第二端子,其耦合到所述第二放大器的所述输入端子。19.根据权利要求15所述的adc电路,其进一步包括:第三采样和保持电路,其耦合到所述第一输入端子,其中所述第一采样和保持电路是所述第三采样和保持电路的按比例缩小版本;及第四采样和保持电路,其耦合到所述第二输入端子,其中所述第二采样和保持电路是所述第四采样和保持电路的按比例缩小版本。20.根据权利要求15所述的adc电路,其进一步包括sar控制电路,所述sar控制电路耦合到所述比较器所述第一cdac和所述第二cdac,并且经配置以在给定位决策循环中:将所述第一cdac的电容器的底板与所述第一信号输入端子断开;将所述第一cdac的所述电容器的所述底板连接到所述第一采样和保持电路;将所述第二cdac的电容器的底板与所述第二信号输入端子断开;及将所述第二cdac的所述电容器的所述底板连接到所述第二采样和保持电路。

技术总结

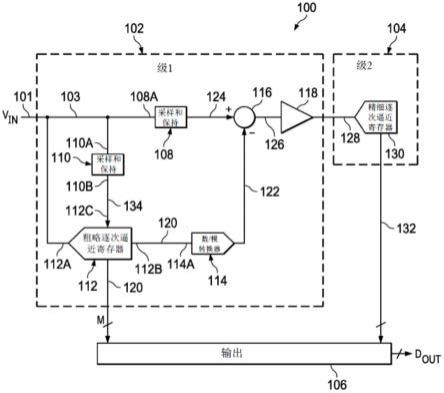

本发明公开一种模/数转换器(ADC)电路,其包含信号输入端子(101)、采样和保持电路(110)和逐次逼近寄存器(SAR)ADC(112)。所述采样和保持电路(110)包含耦合到所述信号输入端子(101)的输入端子(110A)。所述SAR ADC(112)包含比较器、第一电容式数/模转换器(CD AC)和第二CD AC。所述第一CD AC包含耦合到所述信号输入端子的第一输入端子、耦合到所述采样和保持电路的输出端子的第二输入端子和耦合到所述比较器的第一输入端子的输出端子。所述第二CD AC包含耦合到所述信号输入端子的第一输入端子、耦合到所述比较器的第二输入端子的输出端子。子。子。

技术研发人员:S

受保护的技术使用者:德州仪器公司

技术研发日:2020.10.19

技术公布日:2022/6/17

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。