1.本发明涉及在形成在半导体衬底(半导体层)中的沟槽中实施的屏蔽二极管和电阻器实施例,该屏蔽二极管和电阻器例如与晶体管(例如,屏蔽栅金属氧化物半导体场效应晶体管(mosfet))组合;特别地,涉及一种半导体器件及制作方法。

背景技术:

2.功率晶体管,例如金属氧化物半导体场效应晶体管(mosfet),可以在一个电压范围内工作,并在广泛的应用范围中使用,例如在功率转换器电路、以太网供电桥(power-over-ethernet bridge)等中使用。这种晶体管可以在半导体管芯中实施,半导体管芯可以包括集成的无源器件,例如二极管和/或电阻器(例如,用于静电放电保护、电流控制等)。在当前的实施例中,这种集成无源器件的形成可能需要专用处理操作,这可能会增加制造时间和成本。

技术实现要素:

3.在总体方面,半导体器件可以包括半导体衬底、形成在半导体衬底中的沟槽和衬在沟槽上的第一介电层。半导体器件可以进一步包括布置在沟槽的下部中的第一半导体材料。第一介电层可以布置在半导体衬底和第一半导体材料之间。半导体器件还可以包括布置在第一半导体材料上的第二介电层和布置在沟槽的上部中的第二半导体材料。第一介电层可以布置在半导体衬底和第二半导体材料之间。第二介电层可以布置在第一半导体材料与第二半导体材料之间。半导体器件还可以包括限定在第二半导体材料中的二极管或电阻器中的至少一者。

4.在另一个总体方面,半导体器件可以包括半导体衬底、形成在半导体衬底中的第一沟槽、形成在半导体衬底中的第二沟槽、以及衬在第一沟槽和第二沟槽中的第一介电层。第一半导体材料可以布置在第一沟槽的下部和第二沟槽的下部中。第一介电层可以布置在半导体衬底与第一沟槽和第二沟槽中的第一半导体材料之间。半导体器件还可以包括第二介电层,该第二介电层布置在第一沟槽和第二沟槽中的第一半导体材料上。半导体器件还可以包括布置在第一沟槽的上部和第二沟槽的上部中的第二半导体材料。第一介电层可以布置在半导体衬底与第一沟槽和第二沟槽中的第二半导体材料之间。第二介电层可以布置在第一沟槽和第二沟槽中的第一半导体材料与第二半导体材料之间。对于第一沟槽和第二沟槽中的每一个,半导体器件还可以包括限定在第二半导体材料中的二极管或电阻器中的至少一者。

5.在另一个总体方面,一种半导体器件的制作方法可以包括在半导体衬底中形成沟槽,形成衬在沟槽内的屏蔽介电层,以及在沟槽的下部中形成屏蔽电极。屏蔽介电层可以布置在屏蔽电极和半导体衬底之间。该方法还可以包括在屏蔽电极上形成层间介电层,在沟槽的上部中形成多晶硅电极。屏蔽介电层可以布置在多晶硅电极和半导体衬底之间。层间电介质可以布置在屏蔽电极和多晶硅电极之间。该方法还可以包括掺杂多晶硅电极以限定

二极管或电阻器中的至少一者。

附图说明

6.图1a和1b是示意性地示出示例性半导体器件的视图的框图。

7.图2是示出可以根据图1a布置的半导体器件的俯视图的图。

8.图2a至图2g是示出图2的半导体器件的横截面视图的图。

9.图3是示出可以根据图1a布置的半导体器件的俯视图的图。

10.图3a至图3d是示出图3的半导体器件的横截面视图的图。

11.图4是示出可以根据图1b布置的半导体器件的俯视图的图。

12.图4a和4b是示出图4的半导体器件的横截面视图的图。

13.图5是示出可以根据图1b布置的示例性半导体器件的俯视图的图。

14.图5a-5e是示出图5的半导体器件的横截面视图的图。

15.图6是示出用于在屏蔽沟槽中产生二极管和/或电阻器的方法600的流程图。

16.在附图中,其不一定按比例绘制,类似的参考符号可以在不同视图中指示类似和/或类似的部件(元件、结构等)。附图通过示例而不是限制的方式总体地示出了在本公开中讨论的各种实施例。对于相关视图中的相同和/或类似元件,在一个附图中显示的参考符号可以不重复。在多个附图中重复的参考符号可能不是关于这些附图中的每一个具体讨论的,而是为相关视图之间的上下文提供的。此外,当示出元件的多个实例时,并不是在附图中所有类似的元件都用参考符号具体地表示。

具体实施例

17.本公开涉及用于在沟槽或多个沟槽中实施二极管和/或电阻器的方法,其中沟槽被布置(形成、蚀刻等)在半导体器件的半导体衬底中。在一些实施例中,二极管和/或电阻器可以在包括晶体管器件的半导体器件中实施,例如屏蔽沟槽栅金属氧化物半导体场效应晶体管(屏蔽沟槽栅mosfet)。在本文描述的实施例中,可以使用半导体层(例如,多晶硅层)来实施,半导体层也用于分别实施相应mosfet器件的屏蔽电极和栅电极。也就是说,在本文描述的方法中,二极管和/或电阻器可以在不利用表面多晶硅层的情况下实施。因此,在一些实施例中,可以省略或消除与生产表面多晶硅相关联的处理操作,从而降低处理复杂性和或成本。此外,本文描述的方法使得能够对用于形成这种二极管和/或电阻器的半导体层进行平坦化,这可以实现改进的工艺控制(例如,减少处理变化,允许更精确的临界尺寸控制(critical dimension control),并因此使得能够生产更小的器件几何形状)。

18.在示例实施例中,沟槽实施的二极管和/或电阻器可以被屏蔽免受例如来自共用半导体衬底中包括的mosfet的漏极电位。即,与二极管和/或电阻器电隔离的接地屏蔽电极可用于将沟槽实施的器件与mosfet的、存在于相应半导体衬底背面的漏极电位屏蔽开。该屏蔽可以防止漏极电位引起表面反转(例如,寄生mosfet行为),该表面反转可以对二极管和/或电阻器的操作产生不利影响,例如降低阻断电压(blocking voltage)和/或增加泄漏电流。此外,在本文描述的方法中,可以使用与相关联的mosfet的源极电位电耦接的阱区来实现附加屏蔽。例如,阱区可以是p阱区(对于n沟道mosfet实施例)或n阱区(对于p沟道mosfet实施例)。在一些实施例中,阱区可以是与相关联的mosfet的主体区共用的共用阱

区。

19.为了本公开的目的,结合屏蔽沟槽栅mosfet来描述沟槽实施的屏蔽二极管和电阻器的示例,沟槽实施的屏蔽二极管和电阻器可以统称为沟槽实施的器件或沟槽器件。即,通过示例和说明的目的,将沟槽实施器件和屏蔽沟槽栅mosfet描述为在共用半导体衬底中实施。在一些实施例中,其他晶体管器件可以与这种沟槽实施的器件组合,例如非屏蔽沟槽栅mosfet,或其他类型的晶体管。

20.根据本文描述的方法实施的二极管和/或电阻器可用于静电放电(esd)保护、电压钳位、电流流动等。例如,这种二极管和/或电阻器可用于具有薄栅电介质的mosfet的esd保护,用于以太网供电桥等。此外,虽然本文引用了特定的材料,但在实施例中,可以使用其他适当的材料。例如,多晶硅电极可以使用其他材料,例如使用其他半导体材料来实施。这种二极管和/或电阻器可以被配置为能够连接(电耦接)到外部控制电路。例如,用于感测器件温度的二极管可以被连接到外部温度感测电路。

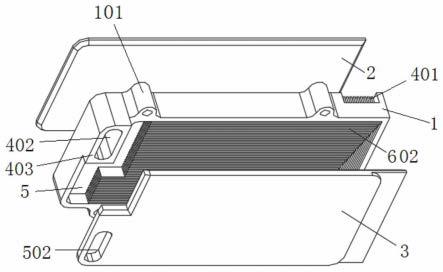

21.图1a和1b是示意性地示出示例性半导体器件的视图的框图,所述示例性半导体器件分别是半导体器件100和半导体器件150。具体地,图1a和1b示出了半导体器件的示例性布置(例如,平面图),其可以包括沟槽实施的器件(二极管和/或电阻器)的实施例,例如本文描述的那些。图1a和1b的示例以示例的方式给出,并且实施例可以包括除所示之外的元件、区域和/或区。例如,实施例可以包括用于实施用于信号通信的信号焊盘和/或信号总线的金属化层(metallization layer),例如gad焊盘金属、栅极总线金属、源极焊盘金属、源极总线金属、用于外部连接到沟槽实施的器件(二极管和/或电阻器)的信号焊盘等,该信号焊盘和/或信号总线可以用于在晶体管和/或半导体器件100和/或150中包括的其他电路元件的操作期间进行电信号的传送。

22.参考图1a,半导体器件100包括围绕器件100的周界布置的端接区域(termination region)110。在实施例中,作为一些示例,端接区域110可以包括布置在介电衬里沟槽、保护环植入物和/或介电填充沟槽中的浮动电极和/或接地电极。在图1a的示例中,器件100还包括沟槽器件区域(区域)120a、沟槽器件区域120b和有源区130,其中有源区130布置在沟槽器件区域120a和沟槽器件区域120b之间。在一种实施例中,可以在有源区130中实施mosfet,而可以在区域120a和120b中实施沟槽实施的二极管和/或电阻器,例如本文描述的那些。在一些实施例中,在具有较大的有源区130或器件100的较小的总面积(例如,较小的半导体衬底面积)的情况下,器件100可以仅包括区域120a或120b中的一者。在一些实施例中,器件100可以包括附加的沟槽器件区域,或者可以包括不同形状或尺寸的沟槽器件区域,例如与端接区域110同心并围绕有源区130的周界布置的沟槽器件区域。在一些实施例中,器件100可仅在区域120a或120b中的一个的部分中或在区域120a和120b两者的相应部分中包括沟槽器件区域。

23.参考图1b,半导体器件150包括围绕器件150的周界布置的端接区域160。在实施例中,与器件100一样,作为一些示例,端接区域160可以包括布置在介电衬里沟槽、保护环植入物和/或介电填充沟槽中的浮动电极和/或接地电极。在图1b的示例中,器件150还包括沟槽器件区域170a、沟槽器件区域170b、沟槽器件区域170c、沟槽器件区域170d和有源区180,其中沟槽器件区域170a-170d围绕有源区180的周界布置,并且邻近(例如,直接邻近)端接区域。

24.与器件100一样,在一种实施例中,可以在有源区180中实施mosfet,而可以在沟槽器件区域170a-170d中实施沟槽实施的二极管和/或电阻器,例如本文描述的那些。类似于器件100,在一些实施例中,器件150可以包括更少或更多的沟槽器件区域,或者可以包括不同形状或大小的沟槽器件区域。

25.虽然本文示出和描述了不同器件元件和区域的特定布置,但在一些实施例中,这些元件和区域可以具有其他布置。例如,沟槽实施的器件可以在半导体管芯内的其他位置(例如,在半导体管芯的中心部分,而不是沿着管芯的边缘)实施。例如,焊盘金属(例如,栅极焊盘金属、源极焊盘金属等)可以在端接区域内和/或沟槽器件区域内通过有源区实施。还可以实施这种焊盘金属以允许外部连接到沟槽实施的器件,例如用于温度感测的二极管(例如,单面二极管)。在一些实施例中,总线金属可以用于沿半导体管芯的边缘将焊盘金属连接到形成在半导体管芯内部的沟槽实施的器件。

26.图2、3、4和5是分别示出半导体器件200、300、400和500的布局视图的图。为了说明的目的,在图2、3、4和5中的每一个中,示出了相应半导体器件的一部分。半导体器件200和300可以具有与图1a的半导体器件100的布置相对应的布置,而半导体器件400和500可以具有与图1b的半导体器件150的布置相对应的布置。

27.图2a至图2g示出了半导体器件200沿着图2所示的相应切割线的横截面图,其示出了半导体器件200的底层结构的示例。图3a至图3d示出了半导体器件300沿着图3所示的相应剖面线的横截面图,其示出了半导体器件300的底层结构的示例。图4a-4b示出了半导体器件400沿着图4所示的相应剖面线的横截面图,其示出了半导体器件400的底层结构的示例。图5a-5e示出了半导体器件500沿着图5所示的相应剖面线的横截面图,其示出了半导体器件500的底层结构的示例。由于图2、3、4和5的布局视图在它们各自的底层结构中最好地理解,进一步参考其相对应的横截面视图来描述这些布局视图中的每一个。

28.示例器件200、300、400和500可以包括类似的特征、元件和/或结构,例如漏极接触金属、包括在重掺杂半导体衬底层中或与重掺杂半导体衬底层一起的外延层、植入区等。为了简洁和清楚的目的,可以不针对每个器件或器件的每个单独视图来描述这种类似的特征。此外,在器件200、300、400和500的各种视图中,通过引用的方式显示了一些示出的元件,并且可以不明确地引用或描述。更进一步地,可以包括在器件200、300、400和500中的一些元件可能没有明确地在所示的视图中显示。作为两个示例,这种元件包括mosfet源注入区域和重体注入。

29.参考图2及其在图2a至图2g中的相对应横截面图,器件200可以包括围绕器件200的周界布置的端接区域210。器件200还可以包括沟槽器件区域220和有源区230(例如,如图1a中器件100的布置)。在该示例中,在沟槽器件区域220中实施多串背靠背二极管224,并且在有源区230中实施屏蔽沟槽栅mosfet(在该示例中为n沟道mosfet),其中背靠背二极管电耦接在有源区230中实施的mosfet的栅极端子和源极端子(地)之间。

30.如图2所示,器件200包括栅极金属化物(gate metallization)202(例如,栅极总线),栅极金属化物202可以用于向mosfet提供栅极信号,以及源极金属化物204(例如,源极总线),源极金属化物204可以用于向mosfet以及器件200的其他元件提供源极电位(电接地)。如图2中进一步所示,器件200包括沟槽232和半导体台面234,其从端接区域210延伸穿过沟槽器件区域220,并进入有源区230。

31.图2a示出了沿着图2中的剖面线2a-2a的器件200的横截面图。从图2和图2a可以看出,剖面线2a-2a延伸穿过端接区域210中的栅极金属化物202(在图2中沿着器件200的顶部)和有源区230。如图2a的横截面图所示,栅极金属化物202经由接触236(也在图2中示出)与布置在沟槽的上部的多晶硅电极(polysilicon electrode,或者简写为poly electrode)233电耦接。如本文所使用的,接触或多个接触可以指在半导体工艺中使用金属化物形成的电接触。

32.在有源区230中,多晶硅电极233实施mosfet的栅电极。如图2a进一步所示,在有源区230中,屏蔽多晶硅(shield polysilicon,或者简写为shield poly)212被嵌入(recessed)沟槽232中,并且层间电介质211布置在屏蔽多晶硅212和多晶硅电极233之间。同样在沟槽232中,如图2a所示,在有源区230中,在沟槽的下部中包括屏蔽电介质213,而在沟槽232的上部中包括(较薄的)栅极电介质214。

33.在端接区域210中,如图2a所示,未嵌入的屏蔽多晶硅212布置在衬有屏蔽电介质213的端接沟槽中。出于参考目的,在图2和2a中都指示了外部端接沟槽216。图2和2a(以及图2b-2e和2g)还示出了阱区228(例如,用于n沟道mosfet的p型阱区),其布置在沟槽232附近(例如,在器件200的半导体衬底的表面处)。阱区228可以包括mosfet的主体区,并且还可以向沟槽器件区域220中的沟槽实施器件提供侧壁屏蔽。阱区228的深度可以取决于特定的实施例,例如取决于在有源区230中实施的mosfet的工作电压。

34.在该示例中,器件200包括布置在半导体衬底的底表面上的漏极接触金属240,其中半导体衬底包括高掺杂区域242和更轻掺杂的外延区域244。在一些实施例中,外延区域244可以包括具有不同掺杂浓度的一个或多个外延层,例如,外延区域244的掺杂浓度可以分级(例如,随着距离高掺杂区域242的距离而减小)。器件200还包括介电材料246,该介电材料246将栅极金属化物202和源极金属化物204与器件200的底层元件隔离,但使用延伸穿过介电材料246的金属接触限定电连接的情况除外。

35.图2b和2c示出了沿着图2中的2b&2c-2b&2c指示的剖面线的器件200的两个示例性横截面图。从图2、2b和2c可以看出,剖面线2b&2c-2b&2c延伸穿过端接区域210和沟槽器件区域220中的源极金属化物204。剖面线2b&2c-2b&2c还从源极金属化物204延伸穿过接触227到阱区228,并穿过背靠背沟槽实施的二极管224串的相应阳极区224a。将图2c与图2b进行比较,图2c中的阱区228形成为使得它们比图2b中的阱区228深。如本文所讨论的,这种较深的阱区228可以为沟槽实施的器件提供额外的屏蔽,例如屏蔽背靠背二极管224免受来自背面漏极接触(例如,漏极接触金属240)的mosfet漏极电位的影响。

36.图2d示出了沿着图2中的剖面线2d-2d的器件200的横截面图。从图2和图2d可以看出,剖面线2d-2d延伸穿过端接区域210和沟槽器件区域220中的源极金属化物204。剖面线2d-2d还穿过接触227,从源极金属化物204延伸到阱区228,穿过背靠背沟槽实施的二极管224串的相应阴极区224b,以及穿过相应接触226延伸到所示的阴极224b(例如,三串背靠背二极管224中的最后一个二极管中的每一个的相应阴极224b,如图2f中进一步所示)。

37.图2e示出了沿着图2中的剖面线2e-2e的器件200的横截面图。从图2和图2e可以看出,剖面线2e-2e延伸穿过端接区域210和沟槽器件区域220中的源极金属化物204。剖面线2e-2e还从源极金属化物204延伸穿过接触222到屏蔽多晶硅212。也如图2和2e所示,在该示例中,外部端接沟槽216中的屏蔽多晶硅212在该示例中不通过源极金属化物而接触(例如,

是电浮动的)。在一些实施例中,布置在外部端接沟槽(例如沟槽216)中的屏蔽多晶硅(例如,屏蔽多晶硅212)可以电耦接到器件200的另一部分(例如沟槽232的端部)中的源极金属化物204。这种屏蔽多晶硅可以是物理(和电)连续的。在一些实施例中,可以省略沟槽216,和/或沟槽232端部的端部可以使用氧化物填充沟槽沿着剖面线4a-4a和4b-4b连接到另一个沟槽上,如图4所示。

38.图2f示出了沿着图2中的剖面线2f-2f的器件200的横截面图。从图2和图2f可以看出,剖面线2f-2f从端接区域210延伸穿过沟槽232中的一个,穿过沟槽器件区域220并进入有源区230。如图2f所示,在沟槽232中,屏蔽多晶硅212在多晶硅电极233下方延伸,其中,多晶硅电极233实施器件200的mosfet的栅电极和背靠背二极管224的串。因此,屏蔽多晶硅212被布置在多晶硅电极233和漏极金属接触之间,例如,以实施接地场板,以在mosfet的操作期间屏蔽背靠背二极管224的串免受漏极电位。

39.如图2f所示,背靠背二极管224的串中的相邻二极管共享阴极224b或阳极224a。最右边的阴极224b(在图2f的视图中)经由接触226电耦接到源极金属化物204,并且屏蔽多晶硅212经由接触222电耦接到源极金属化物,接触222靠近背靠背二极管224的串(例如,邻近层间电介质211的垂直部分)。在一些实施例中,接触222可以与背靠背二极管224(或其它沟槽实施的器件,例如在本文描述的示例中)间隔(例如,横向间隔)小于10微米。这样的布置(连同在沟槽实施的器件下面的屏蔽多晶硅)可以减少和/或防止直接邻近沟槽实施的器件的主体区中mosfet漏极电位的积聚,可以导致沟槽实施的二极管的p型区域的沟槽侧壁反转(例如,改变导电类型)。如上所述,该电位可以经由所施加的mosfet漏极电位而发生,特别是在电瞬态期间,或由于雪崩电流在主体区中的横向电流,雪崩电流将横向流过主体区到有源区。

40.还如图2和2f所示,多晶硅电极233的栅电极部分(例如,多晶硅电极233的第一部分)经由有源区230中的接触236与栅极金属化物202耦接,而多晶硅电极233的第二部分包括沟槽器件区域220中的背靠背二极管224。在其它实施例中,可以使用不同的多晶硅电极来分别实施多晶硅电极233的不同部分。即,第一多晶硅电极可用于第一(栅电极)部分,第二多晶硅电极可用于包括背靠背二极管224(或其它沟槽实施的器件)的第二部分。不同的多晶硅电极可以由相同的半导体材料形成,也可以由不同的半导体材料形成。

41.图2g示出了沿着图2中的剖面线2g-2g的器件200的横截面图。从图2和图2g可以看出,剖面线2g-2g从端接区域210延伸穿过台面234中的一个,穿过沟槽器件区域220并进入有源区230。如图2和图2g中所示,源极金属化物204经由有源区330中的接触237和经由沟槽器件区域220中的接触227与阱区228电耦接。在该横截面图中,在有源区230中的台面234上方的栅极金属化物202布置在介电材料246上,而不与任何底层元件接触。

42.参考图3,器件300在结构上类似于图2的器件200。与器件200相比,器件300的不同之处在于,其包括二极管短路金属化物306,其用于短路阳极和阴极以从背靠背二极管串产生单面二极管。如本文所述,这种二极管元件的一个应用是感测器件温度(例如,器件300的温度)。器件300与器件200的不同之处还在于,其源极金属化物被修改以适应二极管短路金属化物306,并且从修改的源极金属化物到沟槽实施的二极管的接触也短路阳极和阴极以形成单面二极管。在该示例中,器件300的结构在其他方面与器件200的结构相同。因此,与器件200的那些相似(或相同)的器件300的具体细节不必参考图3或其在图3a至图3d中的对

应横截面图再次详细描述。

43.出于比较和上下文的目的,用与对应元件的200系列参考号相对应的300系列参考号来参考器件300与器件200的相同和类似元件。例如,器件300包括端接区域310,沟槽实施的器件(沟槽器件)区域320、有源区330、栅极金属化物302、源极金属化物304、屏蔽多晶硅312、屏蔽电介质313、屏蔽多晶硅接触322、二极管串324、阳极324a、阴极324b、从源极金属化物304到二极管的接触326、从源极金属化物304到主体区328的接触327和337、沟槽332、多晶硅电极333、台面334、从栅极金属化物302到多晶硅电极333的栅电极部分的接触336和介电材料346,以及未具体引用的其他元件。

44.图3a示出了沿着图3中的剖面线3a-3a的器件300的横截面图。从图3a与图2a的比较中可以看出,在该示例中,器件300沿截面线3a-3a的横截面图与器件200沿截面线2a-2a的横截面图相同。因此,为了简洁起见,这里不进一步讨论图3a。

45.图3b示出了沿着图3中的剖面线3b-3b的器件300的横截面图。从图3和图3b可以看出,剖面线3b延伸穿过端接区域310(沿着图3中视图的顶部)、穿过沟槽器件区域320中的二极管短路金属化物306和端接区域310中的源极金属化物304(沿着图3中视图的底部)。剖面线3b-3b还从二极管短路金属化物306延伸穿过接触307到二极管串324。虽然图3b的横截面图是穿过阳极324a,如图3(以及图3c)所示,接触307分别短接阳极324a和相邻的阴极324b,这导致背向二极管被配置为作为单面二极管操作。

46.图3c示出了沿着图3中的剖面线3c-3c的器件300的横截面图。从图3和图3c可以看出,剖面线3c-3c从端接区域310延伸穿过沟槽332中的一个,穿过沟槽器件区域320并进入有源区330。再次参考图2f,图3c中所示的横截面图(沿着器件300的沟槽332)类似于图2f中所示的器件200的横截面图(沿着沟槽232)。

47.如图3c与图2f的比较所示,器件300在许多方面与器件200不同。首先,二极管串324包括两个阳极324a,而不是器件200的背靠背二极管串224的四个阳极224a。第二,(二极管短路金属化物306的)接触307和(源极金属化物304的)接触326使阳极324a中的相应一个与二极管串324中的阴极324b中的相应一个短路,以形成两个单面二极管,而不是如在器件200中实施的背靠背二极管配置。

48.还如图3和3d所示,多晶硅电极333的栅电极部分(例如,多晶硅电极333的第一部分)经由有源区330中的接触336与栅极金属化物302耦接,而多晶硅电极333的第二部分包括沟槽器件区域320中的单面二极管324。在其它实施例中,可以使用不同的多晶硅电极来分别实施多晶硅电极333的不同部分。即,第一多晶硅电极可用于第一(栅电极)部分,第二多晶硅电极可用于包括单面二极管324(或其它沟槽实施的器件)的第二部分。不同的多晶硅电极可以由相同的半导体材料形成,也可以由不同的半导体材料形成。

49.图3d示出了沿着图3中的剖面线3d-3d的器件300的横截面图。从图3和图3d可以看出,剖面线3d-3d从端接区域310延伸穿过台面334中的一个,穿过沟槽器件区域320并进入有源区330。再次参考图2g,图3d中所示的横截面图(沿着器件300的台面334)类似于图2g中所示的器件200的横截面图(沿着台面234)。如图3d与图2g的比较所示,器件300与器件200的不同之处在于,二极管短路金属化物的一部分也布置在介电材料346上,例如,除了布置在介电材料346上的栅极金属化物302的一部分之外。

50.参考图4及其在图4a-4b中的相对应横截面图,器件400可以包括围绕器件400的周

界布置的端接区域460。器件400还可以包括沟槽器件区域470和有源区480(例如,如图1b中器件150的布置)。在该示例中,在沟槽器件区域470中可以掺杂n型或p型的多晶硅电阻器424,并且在有源区480中实施屏蔽沟槽栅mosfet,其中多晶硅电阻器424电耦接在有源区480中实施的mosfet的栅极端子和源极端子(地)之间。

51.如图4所示,器件400包括栅极金属化物402,栅极金属化物402包括可以用于向mosfet提供栅极信号的栅极焊盘403,以及源极金属化物404,源极金属化物404可以用于向mosfet以及器件400的其他元件提供源极电位。如图4中进一步所示,器件400包括沟槽432和半导体台面434,其从沟槽器件区域470延伸进入有源区480。

52.在该示例中,器件400还包括与上述器件200和300类似的元件。例如,如图4、4a和4b所示,器件400包括屏蔽多晶硅412、层间电介质411、屏蔽电介质413、屏蔽多晶硅接触422、从源极金属化物404到多晶硅电阻器424的接触426、从源极金属化物404到主体区428的接触427、多晶硅电极433、从栅极金属化物402到多晶硅电极433的栅电极部分的接触436、介电材料446,以及未具体引用的其他元件。

53.如图4所示,沟槽332可以在栅极焊盘403下是不连续的,或者在一些实施例中,可以在栅极焊盘下是连续的,例如在图5的器件500中。在器件400中,沟槽器件区域570的一部分被布置在栅极焊盘403的第一部分之下,而填充氧化物的沟槽的布置被布置在栅极焊盘403的第二部分之下。在一些实施例中,可以将沟槽从栅极焊盘下排除。在栅极焊盘下的特征的具体布置或特征的排除将取决于具体的实施例。

54.图4a示出了沿着图4中的剖面线4a-4a的器件400的横截面图。从图4和4a可以看出,剖面线4a-4a延伸穿过沟槽432中的一个。如图4a所示,在沟槽432中,屏蔽多晶硅412在多晶硅电阻器424和多晶硅电极433下面延伸。在该示例中,可以使用相同的处理操作沉积或形成多晶硅电阻器424和多晶硅电极433。如图4a所示,屏蔽多晶硅412布置在多晶硅电阻器和漏极金属接触之间,以及多晶硅(例如,栅电极233)和漏极金属接触之间,例如,以实施接地场板,以在mosfet的操作期间屏蔽多晶硅电阻器424和多晶硅电极433免受漏极电位的影响。

55.如图4a可以看出,多晶硅电阻器424的第一端可以经由接触437与栅极金属化物402电耦接,并且多晶硅电阻器424的第二端可以经由接触426与源极金属化物电耦接,而源极金属化物也可以经由靠近多晶硅电阻器424的接触422耦接到屏蔽多晶硅412。也如图4a的截面图所示,栅极金属化物可以经由接触436与聚(栅极)电极433电耦接。

56.也如图4和图4d所示,分离的(例如,不同的)半导体材料部分分别用于实施栅电极和多电阻器424。例如,多晶硅电极433经由有源区480中的接触436与栅极金属化物402耦接。另外,分离的多晶硅电极包括在沟槽器件区域470中的多电阻器424。在一些实施例中,这些多晶硅电极可以形成为相同半导体材料的不同部分。在其它实施例中,不同的半导体材料可以分别用于栅电极和多电阻器424。

57.图4b示出了沿着图4中的剖面线4b-4b的器件400的横截面图。从图4和图4b可以看出,剖面线4b-4b延伸穿过器件400的台面434中的一个。如图4和图4b所示,源极金属化物404经由接触427与阱区428电耦接。在该横截面图中,在台面434上方的栅极金属化物402布置在介电材料446上,而不与任何底层元件接触。

58.参考图5及其在图5a-5e中的相对应横截面图,器件500可以包括围绕器件500的周

界布置的端接区域560。器件500还可以包括沟槽器件区域570和有源区580(例如,如图1b中器件150的布置)。在该示例中,在沟槽器件区域570中实施多串背靠背二极管524,并且在有源区580中实施屏蔽沟槽栅mosfet,其中背靠背二极管电耦接在有源区580中实施的mosfet的栅极端子和源极端子(地)之间。

59.如图5所示,器件500包括栅极金属化物502,栅极金属化物502包括可以用于向mosfet提供栅极信号的栅极焊盘503,以及源极金属化物504,源极金属化物504可以提供与mosfet的有源区以及器件500的其他元件的电连接。如图5进一步所示,器件500包括沟槽532和半导体台面534,其延伸穿过沟槽器件区域570和有源区580的布置在沟槽器件区域570的任一侧的部分。

60.在该示例中,器件500还包括与上述器件200、300和400类似的元件。例如,如图5和5a-5e所示,器件500包括屏蔽多晶硅512、层间电介质511、屏蔽电介质513、屏蔽多晶硅接触522、从源极金属化物504到背靠背二极管524的串的接触526、从源极金属化物504到主体区528的接触527、多晶硅电极533、从栅极金属化物502到多晶硅电极533的栅电极部分的接触536、介电材料546,以及未具体引用的其他元件。

61.图5a示出了沿着图5中的剖面线5a-5a的器件500的横截面图。从图5和5a可以看出,剖面线5a-5a延伸穿过端接区域560中的栅极金属化物502(在图5中沿着器件500的顶部)和有源区580,并且穿过有源区580中的源极金属化物504(在图5中沿着器件500的底部)。如图5a的横截面图和图5的布局图所示,栅极金属化物502经由接触536与布置在沟槽的上部的多晶硅电极533电耦接。也如图5和5a所示,源极金属化物经由接触527与有源区580中的台面中包括的主体区电耦接。

62.在有源区580中,多晶硅电极533实施mosfet的栅电极。如图5a进一步所示,在有源区580中,屏蔽多晶硅512被嵌入沟槽532中,并且层间电介质511布置在屏蔽多晶硅512和多晶硅电极533之间。同样在沟槽532中,如图5a所示,在有源区580中,在沟槽的下部中包括屏蔽电介质513,而在沟槽532的上部中包括(较薄的)栅极电介质514。

63.在端接区域560中,如图5a所示,未嵌入的屏蔽多晶硅512布置在衬有屏蔽电介质513的端接沟槽中。根据实施例的不同,该未嵌入的屏蔽多晶硅可以电耦接到源极金属化物504,或者可以浮动。在示例实施例中,端接沟槽可以交替地包括嵌入的屏蔽多晶硅和氧化物填充沟槽。图5和5a(以及图5b-5c)还示出了阱区528(例如,用于n沟道mosfet的p型阱区),其布置在沟槽532附近(例如,在器件500的半导体衬底的表面处)。阱区528可以包括mosfet的主体区,并且还可以向沟槽器件区域570中的沟槽实施器件提供侧壁屏蔽。如本文所讨论的,阱区528(在图5a中不接触阱)的深度可以取决于特定的实施例,例如取决于在有源区580中实施的mosfet的工作电压。

64.图5b和5c示出了沿着图5中的5b&5c-5b&5c指示的剖面线的器件500的两个示例性横截面图。从图5、5b和5c可以看出,剖面线5b&5c-5b&5c延伸穿过端接区域560中的栅极金属化物502、穿过沟槽器件区域570中的栅极焊盘503的中心,并且穿过有源区580中的源极金属化物504(在图5的视图中器件500的底部)。图5b示出了其中阱区528在栅极焊盘503下连续的实施例。与图5b相比,图5c示出了其中阱区528在栅极焊盘503下不连续的实施例。

65.图5d和5e示出了沿着图5中的5d&5e-5d&5e指示的剖面线的器件500的两个示例性横截面图。从图5、5d和5e可以看出,剖面线5d&5e-5d&5e延伸穿过沟槽532中的一个,例如从

图5中器件500左侧的有源区580,穿过沟槽器件区域570,并进入器件500右侧的有源区580。如图5d和5e所示,在沟槽532中,屏蔽多晶硅512在多晶硅电极533下方延伸,其中多晶硅电极533例如通过植入多晶硅电极533的部分来实施器件500的mosfet的栅电极和背靠背二极管524的串。因此,屏蔽多晶硅512被布置在多晶硅电极533和漏极金属接触之间,例如,以实施接地场板,以在mosfet的操作期间屏蔽背靠背二极管524的串免受漏极电位以及mosfet的栅电极。

66.也如图5、5d和5e所示,分离的(例如,不同的)半导体材料部分分别用于实施栅电极和背靠背二极管524。例如,多晶硅电极533经由有源区580中的接触536与栅极金属化物502耦接。另外,分离的多晶硅电极包括在沟槽器件区域570中的背靠背二极管524。在一些实施例中,这些多晶硅电极可以形成为相同半导体材料的不同部分。在其它实施例中,不同的半导体材料可以分别用于栅电极和背靠背二极管524。

67.在该实施例中,在栅极焊盘503的每一侧镜像背靠背二极管524的串,图5d中屏蔽多晶硅512位于背靠背二极管524的串之间。与图5d相比,在图5e中,层间介电层的部分511a也与屏蔽多晶硅512一起布置在背靠背二极管524的串之间。在一些实施例中,例如,基于栅极焊盘的宽度,可以加宽背靠背二极管524的串之间的屏蔽多晶硅512,从而增加背靠背二极管524的串之间的距离和隔离度。图5d和5e的方法可以用于减小由于漏极电位而在栅极焊盘503下的电场,以及减小栅极焊盘503下的栅极到源极电容。

68.此外,在图5d和5e中,如在图2f中,背靠背二极管524的串中的相邻二极管共享阴极或阳极。背靠背二极管524的串在串的一端经由接触536电耦接到栅极焊盘503,并且在串的另一端经由接触526电耦接到源极金属化物504。类似地,如图2f中,如图5、5d和5e所示,屏蔽多晶硅512经由接触522电耦接到源极金属化物,接触522各自靠近(例如在10微米内)相应的背靠背二极管524的串(例如,邻近层间电介质511的垂直部分)。也如图5、5d和5e所示,多晶硅电极533的栅电极部分经由各自的接触536与栅极金属化物502耦接。

69.图6是示出用于在屏蔽沟槽中产生二极管和/或电阻器的方法600的流程图。在实施例中,方法600可以用于生产包括mosfet的半导体器件,例如本文描述的那些器件。在方框602,方法600包括在半导体衬底中形成介电衬里沟槽。在一些实施例中,方框602的沟槽可以与相对应屏蔽沟槽栅mosfet的栅极沟槽的形成结合形成,例如在图2、3、4和5的实施例中。方框602处的介电衬里可以是屏蔽介电衬里(例如,可以比mosfet器件中使用的相对应栅极电介质厚)。在方框604,可以在方框602的沟槽的下部中形成屏蔽电极,其中介电衬里布置在屏蔽电极和半导体衬底之间。在实施例中,方框604的屏蔽电极可以结合相对应mosfet的栅极沟槽中包括的栅极屏蔽电极的形成来形成。

70.在方框606,方法600包括在方框604的屏蔽电极上形成层间电介质(例如,多晶硅间电介质),其中层间电介质可以结合mosfet栅极沟槽中层间电介质的形成而形成。在方框608,在沟槽的上部中形成多晶硅电极,其中屏蔽介电层布置在多晶硅电极和半导体衬底之间,层间介电层布置在屏蔽电极和多晶硅电极之间。在实施例中,方框608的多晶硅电极可以结合mosfet栅极沟槽中栅电极的形成而形成。

71.在方框610,该方法包括掺杂多晶硅电极以在方框608的多晶硅电极中限定以下各项中的至少一者:背靠背二极管、一个或多个单面二极管、或一个或多个电阻器。作为一些示例,多晶硅电极的掺杂可以与半导体器件的其他部分的掺杂结合来执行,例如源区、主体

区和/或重体区的掺杂。

72.在方框612,该方法包括将方框604的屏蔽电极与电接地(例如,与n沟道mosfet的源极端子和/或主体区)电耦接。在一些实施例中,屏蔽电极可以绑定到其他电位或保持浮动。在图6的示例中,屏蔽电极可以使用靠近沟槽实施的器件的接触(金属接触)耦接到电接地。在方框614,方法600包括与沟槽的侧壁相邻的一个或多个接地区。一个或多个接地区可以包括阱区(例如,与相对应mosfet的主体区共用)。在一些实施例中,邻近沟槽侧壁的区域可以耦接到其他电位(例如,耦接到相对应的p沟道mosfet的源极电位),或者保持浮动。

73.本文描述的各种实施例是通过示例的方式并出于说明的目的而给出的。在这种实施例以及其他实施例中,特定材料、掺杂方法和/或不同器件元件之间的关系上的变化是可能的。例如,用于形成沟槽实施的器件的半导体材料可以是未掺杂的多晶硅(例如,可以在形成后掺杂,或者保持未掺杂)。用于沟槽实施的器件(例如,二极管和/或电阻器)的掺杂可以使用用于掺杂相应晶体管(例如,mosfet)器件的栅电极(或其他元件)的相同掺杂操作来执行,或者可以使用与用于掺杂相应晶体管器件的元件的不同的掺杂来执行。

74.在一些实施例中,栅电极可以使用重度原位掺杂的多晶硅来形成,而沟槽实施的器件可以使用包括掺杂和/或未掺杂部分的单独沉积的多晶硅材料(再沉积的多晶硅)来形成。在一些实施例中,可以在沟槽中形成和嵌入(例如,蚀刻)屏蔽多晶硅,然后可以在嵌入的屏蔽多晶硅的顶部对沟槽进行介电填充。然后可以将介电填充蚀刻到所需的厚度和/或图案化和蚀刻以用作栅极介电。然后可以沉积、平坦化和掺杂一个多个多晶硅层(例如,第二半导体材料、第三半导体材料等)以形成栅电极和/或沟槽实施的器件。

75.在包括用于温度感测的单面二极管的实施例中,二极管(例如,二极管串的每一端)可以连接到焊盘金属,用于外部连接到控制电路。在这样的实施例中,可以省略到主体区、mosfet源极区域和/或mosfet栅极的接触。然而,相关联的主体区可以连接到屏蔽多晶硅和/或源极金属化物,以提供对施加电位(例如,mosfet漏极电位)的屏蔽。在实施例中,沟槽实施的器件可以与相对应的晶体管(例如,mosfet)器件串联和/或并联连接,并且可以在半导体管芯中内部连接,和/或可以具有在半导体管芯外部的一个或多个连接。

76.为了本公开的目的,应当理解,当诸如层、区域或衬底之类的元件被称为在另一元件上、连接到另一元件上、电连接到另一元件上、耦接到另一元件上或电耦接到另一元件上时,它可以直接在另一元件上、连接到另一元件上或耦接到另一元件上,或者可以存在一个或多个中间元件。相反,当一个元件被称为直接在另一个元件或层上、直接连接到或直接耦接到另一个元件或层时,不存在中间元件或层。尽管在整个详细描述中可能不使用术语直接在之上、直接连接到或直接耦接到,但是可以这样称呼被示出为直接在之上、直接连接到或直接耦接的元件。可以修改本技术的权利要求书以列举在说明书中描述或在附图中示出的示例性关系。

77.如在本说明书中所使用的,单数形式可以包括复数形式,除非根据上下文明确指示特定情况。空间上相对的术语(例如,之上、上方、上方的、之下、底下、下方、下方的等)旨在涵盖除图中描绘的方位之外的器件在使用或操作中的不同方位。在一些实施例中,上方和下方的相对术语可以分别包括垂直上方和垂直下方。在一些实施例中,术语相邻可以包括横向相邻或水平相邻。

78.可以使用各种半导体处理和/或封装技术来实施一些实施例。可以使用与半导体

衬底相关联的各种类型的半导体处理技术来实施一些实施例,所述半导体衬底包括但不限于,例如,硅(si)、碳化硅(sic)、砷化镓(gaas)、氮化镓(gan)和/或等等。

79.尽管已如本文所描述的说明了所描述的实施例的某些特征,但本领域技术人员现在将出现许多修改、替换、改变和等效物。因此,应当理解,所附权利要求旨在涵盖落入实施例的范围内的所有此类修改和改变。应当理解,它们仅通过示例而非限制的方式呈现,并且可以在形式和细节上进行各种改变。除了互斥组合之外,本文所描述的装置和/或方法的任何部分可以以任何组合来组合。本文描述的实施例可以包括所描述的不同实施例的功能、部件和/或特征的各种组合和/或子组合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。