1.本发明涉及一种用于制造量子器件的工具,并且更具体地涉及一种用于杜兰(dolan)桥约瑟夫森结器件的生产价值的制造的集群(cluster)工具。

背景技术:

2.杜兰桥约瑟夫森结量子位(qubit)的制造目前正在非制造设备上进行开发,该设备可以处理小片晶片,而不是整个晶片。处理的均匀性不足以实现具有与量子芯片的制造一致的公差的图像形成。当前的制造技术可能由于蒸发角度不一致而导致图像尺寸变化,以及由于工艺控制不足而导致结介电变化。结介电变化可以改变量子器件(诸如量子位)的频率,并且还可以将可以耦合到量子器件的缺陷引入到结介电中,从而缩短器件的相干时间。因此,需要在全晶片规模上制造量子装置的系统和方法。

技术实现要素:

3.根据本发明的实施例,沉积系统包括沉积源和设置在沉积源的沉积路径内的扫描台(stage)。扫描台包括支撑平台和机械致动器,支撑平台配置成在其上支撑晶片,机械致动器耦接到支撑平台。机械致动器被配置成相对于沉积源平移支撑平台。沉积系统包括接近(proximity)掩模,接近掩模设置在沉积源与扫描台之间的沉积源的沉积路径内,接近掩模限定缝隙。沉积系统包括与扫描台通信的控制器,该控制器被配置成控制机械致动器以相对于缝隙平移晶片,使得沉积角度保持基本上恒定。在操作中,接近掩模防止具有不与缝隙对准的轨迹的沉积源材料接触晶片。沉积系统提供能够完整晶片生产的化学沉积均匀性,使得能够在晶片的整个表面上形成一系列均匀特征。之后,晶片可以被分割成单独的芯片。

4.根据本发明的实施例,群集工具包括多个可选择的制造工具。多个可选择的制造工具包括沉积系统,沉积系统包括沉积源和扫描台,扫描台设置在沉积源的沉积路径内。扫描台包括支撑平台和机械致动器,支撑平台配置成在其上支撑晶片,机械致动器耦接到支撑平台。机械致动器被配置成相对于沉积源平移支撑平台。沉积系统包括接近掩模,接近掩模设置在沉积源与扫描台之间的沉积源的沉积路径内,接近掩模限定缝隙。沉积系统包括与扫描台通信的控制器,该控制器被配置成控制机械致动器以相对于缝隙平移晶片,使得沉积角度保持基本上恒定。在操作中,接近掩模防止具有不与缝隙对准的轨迹的沉积源材料接触晶片。多个可选择的制造工具还包括介电系统,该介电系统包括被配置为在晶片上形成介电层的介电源。除了提供由沉积系统提供的化学沉积控制之外,群集工具能够在不破坏真空的情况下完全处理晶片上的结构。

5.根据本发明的实施例,一种用于执行成角度的沉积的方法包括:提供沉积源;以及在所述沉积源的沉积路径中设置接近掩模,所述接近掩模在相对于所述沉积源的第一位置处具有缝隙。该方法还包括在沉积源材料的沉积期间相对于缝隙平移晶片,使得沉积角度保持实质上恒定,且使得接近掩模防止具有偏离缝隙对准的轨迹的沉积源材料接触晶片。

该方法使得能够在较大表面区域(例如晶片表面)上以高均匀性进行角蒸发。该方法实现了具有与量子芯片的制造一致的公差的图像形成。

附图说明

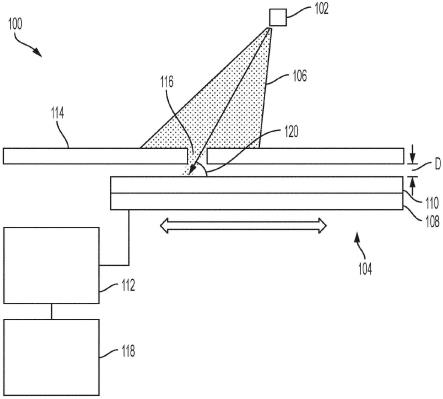

6.图1是根据本发明的实施例的沉积系统的示意图。

7.图2是根据本发明的实施例的具有与图1的沉积系统不同的沉积角度的沉积系统的示意图。

8.图3是杜兰桥约瑟夫森结的示意图。

9.图4a是具有其上形成有第一层和第二层的剥离掩模的衬底的平面图的示意图。

10.图4b是具有其上形成有第一层和第二层的剥离掩模的衬底的横截面图的示意图。

11.图5a是具有沉积在剥离掩模的第二层上和暴露的衬底上的金属层的衬底的平面图的示意图。

12.图5b是具有沉积在剥离掩模的第二层上和暴露的衬底上的金属层的衬底的横截面视图的示意图。

13.图6a是形成在沉积在衬底上的金属层的一部分上的介电层的平面图的示意图。

14.图6b是形成在沉积在衬底上的金属层的一部分上的介电层的横截面图的示意图。

15.图7a是通过定向沉积形成的第二金属层的平面图的示意图。

16.图7b是通过定向沉积形成的第二金属层的横截面视图的示意图。

17.图8是定向沉积的示意图。

18.图9是在晶片上设置材料的沉积源的示意图。

19.图10是其上形成有掩模的晶片的示意图。

20.图11是根据本发明的一些实施例的沉积源和接近(proximity)掩模的平面图的示意图。

21.图12为根据本发明的一些实施例的沉积源与接近掩模的平面图的示意图。

22.图13是其中支撑平台相对于沉积路径的角度是可选择的沉积系统的示意图。

23.图14是包括沉积腔室的沉积系统的示意图。

24.图15为根据本发明的一些实施例的群集工具的示意图。

25.图16是根据本发明的一些实施例的用于执行成角度的沉积的方法的示意图。

具体实施方式

26.图1是根据本发明的实施例的沉积系统100的示意图。沉积系统100包括沉积源102和设置在沉积源102的沉积路径106内的扫描台104。扫描台104包括支撑平台108,支撑平台108配置为在其上支撑晶片110。扫描台104还包括耦合到支撑平台108的机械致动器112。机械致动器112被配置成相对于沉积源102平移(translate)支撑平台108。沉积系统100包括接近掩模114,接近掩模114设置在沉积源102与扫描台104之间的沉积源102的沉积路径106内。接近掩模114限定缝隙116。沉积系统100包括与扫描台104通信的控制器118。控制器118被配置以控制机械致动器112以相对于缝隙116平移晶片110,使得沉积角度120保持实质上恒定。在操作中,接近掩模114防止具有偏离缝隙116对准的轨迹的沉积源材料接触晶片110。

27.术语“基本上恒定”旨在是指沉积角可以变化

±

10

°

或更小。根据一些实施方式,沉积角度可以变化

±5°

或更小。

28.图2是根据本发明的实施例的沉积系统200的示意图。在图2中,接近掩模202被配置成使得缝隙204直接位于沉积源206下方。在该实施例中,沉积角度208是90

°

。根据本发明的一些实施例,沉积角度定义为晶片212的沉积表面210与线214之间的角度,线214将沉积源206连接至晶片212并穿过缝隙204的中心。

29.图1和图2示意性示出的沉积系统可用于在晶片上形成均匀结构。例如,该系统可以用于形成杜兰桥约瑟夫森结。图3是杜兰桥约瑟夫森结300的示意图。杜兰桥约瑟夫森结300包括在衬底304上形成的第一引线302。杜兰桥约瑟夫森结300包括形成在第一引线302上的第二引线306,具有在第一引线302与第二引线306之间形成的介电层。

30.图4a-7b示意性地示出了用于形成杜兰桥约瑟夫森结的实例过程。图4a和4b是具有剥离掩模的衬底400的平面图和截面图的示意性图示,该剥离掩模具有形成在其上的第一层402和第二层404。第一层402和第二层404例如使用光刻构图而被构图到在其上将形成杜兰桥约瑟夫森结的衬底400的暴露部分406、408。可以选择第一层402和第二层404,使得蚀刻暴露衬底400的大于第二层404中的开口面积的部分。第一层402可以包括例如有机聚合物或可溶于有机溶剂中的材料。第二层404可包括例如钛或硅。例如,可使用反应离子蚀刻来蚀刻第一层402和第二层404。蚀刻可以比第二层404更快地蚀刻第一层402。

31.该工艺可包括在掩模和暴露的衬底上沉积金属。在一个实例中,使用90

°

沉积来沉积金属。图5a和5b是具有沉积在剥离掩模的第二层504上和暴露的衬底500上的金属层502的衬底500的平面图和截面图的示意性图示。沉积在衬底500上的金属层502的部分506形成杜兰桥约瑟夫森结的第一引线。金属层502可以包括例如铝、铅、钛、钽、氮化钽、氮化钛、钒或铌。

32.该工艺可包括在沉积于衬底上的金属层的部分上形成介电层。这可以包括在金属层上沉积介电材料,或者将金属层暴露于氧以形成介电层。图6a和6b为形成于沉积于衬底608上的金属层604的部分602上的介电层600的平面图及截面图的示意图。

33.该工艺可以包括使用定向沉积形成第二金属层,其中沉积角不同于用于形成杜兰桥约瑟夫森结的第一引线的沉积角。例如,沉积源可以被定位为具有45

°

和60

°

之间的沉积角。图7a和图7b是通过定向沉积形成的第二金属层700的平面图和截面图的示意图。第二金属层700的部分702可以形成杜兰桥约瑟夫森结的第二引线。重叠的第一引线704、介电层706、以及第二引线702形成约瑟夫森结708。由于金属沉积的方向性质,额外的金属特征710可通过用于形成第一引线704的开口通过90

°

沉积而沉积在衬底上。此外,如图7a示意性地示出的,形成在第一引线704上的介电层706的部分保持暴露。第二金属层700可包括例如铝、铅、钛、钽、氮化钽、氮化钛、钒或铌。

34.图8是定向沉积的示意图。在图8中,表示沉积材料的轨迹的两条线800、802是平行的,使得能够在衬底804上受控地形成特征。掩模806防止沉积角度808实质上偏离。虽然这种设置可能足以在单个芯片上沉积特征,但其不足以在整个晶片上构图特征。经典的计算机芯片形成在半导体晶片上,其然后被分成芯片。随着量子计算的进展,存在恒定的推动来增加量子处理器中的量子位的数目。需要能够以大量可靠地形成量子位芯片的加工技术。然而,图8所示的定向沉积技术依赖于控制沉积角度808的能力。如图9所示,当使用单个沉

积源将金属布置在大面积上时,沉积的角度可改变。

35.图9是在晶片902上设置材料的沉积点源900的示意图。如由三个箭头904、906、908所表示的,沉积角度在晶片902的表面上显著变化,这导致晶片902上的特征尺寸的变化,以及特征的相对位置的变化。图10是晶片1000的示意图,该晶片具有形成在其上的掩模1002,如用于产生杜兰桥约瑟夫森结的图4中的掩模402、404。图10示出了对于掩模1002中的三个开口中的每一个,沉积角度如何不同。角度的变化导致形成在晶片1000上的特征的尺寸及相对位置的变化。因而,当晶片1000被划分成芯片时,芯片上的特征将因芯片而异。

36.在图1中示意性地示出的沉积系统解决了沉积角度变化的问题。系统100在沉积源102与晶片110之间包括接近掩模114,并且实现晶片110跨接近掩模114中的缝隙116的扫描。系统100确保沉积角度120及从沉积源102至晶片110的距离在整个晶片110上保持实质上恒定。由此,在沉积之后,晶片110可以被分割成基本上相同的芯片。系统100不需要准直蒸发源,简化了系统设计。

37.从沉积源102至接近掩模114的距离可相对较短,从而减少材料损失与工具覆盖区(tool footprint)。缝隙116可具有例如约2cm或更小的宽度。减小缝隙116的尺寸增强了角度控制,但不利于生产量。相反地,增加缝隙116的尺寸允许以更快的速率沉积,但也导致角度控制的劣化。接近掩模114与晶片110之间的距离d可以为约2cm或更小。如果距离d过大,该材料在穿过缝隙116之后将散开。根据一些实施例,接近掩模114与110晶片之间的距离d可以为约1cm。

38.图11是根据本发明的一些实施例的沉积源1100和接近掩模1102的平面图的示意图。沉积源1100跨越接近掩模1102中的缝隙1104的长度。沉积源1100可以是布置在舟皿或托盘中的连续沉积源,或者可以是一系列点源。或者,沉积源1100可以是具有一定程度方向性的超高真空(uhv)喷涂/溅射源。在图11中,沉积源1100具有等于接近掩模1102中的缝隙1104的长度ls的长度ld。在一些实施例中,沉积源1100可以比缝隙1104更短或更长。然而,配置沉积源1100以跨越缝隙1104可确保源材料在晶片上的均匀沉积。

39.接近掩模1102可以包括能够承受高热而不翘曲的材料。接近掩模1102可包括例如金属、陶瓷或热稳定碳。沉积系统可包括冷却系统,该冷却系被配置成冷却沉积腔室的侧面和/或接近掩模1102,以帮助沉积材料粘附至沉积腔室和接近掩模1102,而不是剥落或形成斑点,这些斑点使晶片移位并在晶片上产生缺陷。接近掩模1102可包括散热器,以帮助冷却接近掩模1102以促进具有不与缝隙1104对准的轨迹的沉积材料的附着。根据本发明的一些实施例,该系统可以包括在沉积源1100与接近掩模1102之间的准直元件。例如,金属支架或蜂窝结构可以放置在沉积源1100附近以捕获具有偏离期望沉积角度的轨迹的沉积材料。

40.图12是根据本发明的一些实施例的沉积源1200和接近掩模1202的平面图的示意图。沉积源1200跨越接近掩模1202中的缝隙1204的长度ls。然而,缝隙1204不跨越接近掩模1202的长度l

p

。相反,缝隙1204仅在垂直方向暴露出部分晶片,使得能够沿着缝隙1204更好地控制角度。图12中所示的配置可用于在单次扫描中跨晶片沉积多行芯片。例如,晶片可以与缝隙1204对准,从而在单次扫描中跨晶片沉积第一组芯片行,然后可以将缝隙1204或者晶片逐步(step)到另一组行,并且可以再次跨缝隙1204扫描晶片以沉积在第二组芯片行上。接近掩模1202可以包括可调整的部分1206、1208,使得能够调整缝隙1204的长度ls和位置。

41.图13是沉积系统1300的示意图,其中支撑平台1304相对于沉积路径1306的角度1302是可选择的。在本实施例中,机械致动器可经配置以在方向1312上相对于晶片1310的沉积表面1308以倾斜角度平移支撑平台1304。扫描台1314可包括使得能够调整角度1302的调整机构。支撑平台1304可以具有用于沉积杜兰桥约瑟夫森结的第一引线的第一配置,并且然后可以将角度1302调整到用于沉积杜兰桥约瑟夫森结的第二引线的第二配置。沉积系统1300可在缝隙1316之前包括电子枪,以提供光束中的原子的准直。离子化光束可以增强准直,并且具有缝隙的第二接近掩模可以被添加在紧靠晶片1310的沉积表面1308处以进一步改善准直。或者,可使用离子注入源。为了提供准直,高电流(例如,具有在衬底上方的电子网格的等离子体浸没注入)可用于在沉积之前来中和射束。缝隙1316可以是准直缝隙。图13中示意性示出的配置可利用附加的化学沉积控制技术,因为间隙从晶片1310到缝隙1316显著变化。

42.沉积系统可包括沉积腔室。图14是包括沉积腔室1402的沉积系统1400的示意图。沉积源1404、扫描台1406以及接近掩模1408设置在沉积腔腔室1402中。沉积系统1400包括接近掩模固定件1410,所述接近掩模固定件1410被配置以相对于沉积源1404可释放地固定接近掩模1408的位置,以使得能够选择沉积角度1412。

43.根据本发明的一些实施例,沉积源1404是金属蒸发源。根据一些实施例,沉积源1404为溅射沉积源。溅射沉积源可使得能够控制膜厚度、精确的介电沉积以及用于多元件材料的精确的原子组成。根据一些实施例,沉积源1404为中空阴极等离子体喷射(hcpj)溅射沉积源。沉积腔室1402与支撑平台1414可接地。根据一些实施例,沉积系统1400包括被配置为照射沉积源1404的激光器1416,并且沉积系统1400被配置为通过脉冲激光沉积来沉积沉积源材料。根据一些实施例,沉积腔室1402包含气体入口1418及气体出口1420,气体入口1418及气体出口1420被配置以将气体引入沉积腔室1402及从沉积腔室1402移除气体,且沉积系统1400被配置以通过溅射沉积来沉积源材料。虽然图14中的沉积腔室1402被示意性地示出为具有每个前述特征,但沉积腔室1402可以具有特征的全部或子集,这取决于所使用的沉积方法。根据一些实施例,沉积系统1400包括在沉积源1404与接近掩模1408之间的用于材料离子化与束控制的电子枪。沉积系统1400也可以包括电极板以引导沉积材料,潜在地导致更快的膜形成和更好的角度控制。本发明的实施例不限于本文所述的沉积方法。本文所述的沉积方法作为非限制性实例提供。

44.图15为根据本发明的一些实施例的群集工具1500的示意图。群集工具1500包括多个可选择的制造工具1502-1518。制造工具1502-1518包括沉积系统1502。例如,沉积系统1502可以包括图1中示意性示出的沉积系统100的特征。沉积系统1502可以被配置成以第一沉积角度在晶片上沉积沉积源材料。制造工具1502-1518还包括介电系统1504。介电系统1504包含经配置以在晶片上形成介电层的介电源1522。介电源1522可以是用于沉积(例如,使用溅射沉积、分子束外延或化学气相沉积)的介电材料的源。或者,介电源1522可为氧源,且氧源可用于氧化晶片上的金属,由此形成氧化物层。

45.根据本发明的一些实施例,群集工具1500还包括第二沉积系统1506。第二沉积系统1506可以被配置为以第二沉积角度将源材料沉积在晶片上。第二沉积角度可不同于第一沉积角度。例如,第一沉积角度和第二沉积角度中的一个可以是90

°

,而第一沉积角度和第二沉积角度中的另一个可以是小于90

°

的角度。第二沉积系统1506可包括蒸发罩以及准直

缝隙。

46.沉积系统1502、介电系统1504和第二沉积系统1506可以用于在晶片上形成多个杜兰桥约瑟夫森结。例如,沉积系统1502可以形成多个杜兰桥约瑟夫森结的多条第一引线,像图5a和5b中的第一引线506。随后,介电系统1504可在第一引线上形成介电层,与图6a和图6b中的介电层600相似。然后,第二沉积系统1506可以形成多个杜兰桥约瑟夫森结的多条第二引线,如图7a和图7b中的第二引线702。沉积系统1502、1506中的每一者中的接近掩模与扫描台的组合使得能够在晶片的表面上形成多个均匀特征。之后,晶片可以被分割成单独的芯片。例如,晶片可以具有大约200mm的直径,并且可以被分成20mm

×

20mm的芯片。

47.群集工具1500可包括用于准备晶片的额外制造工具。例如,群集工具1500可包括退火系统1508。退火系统1508可包含经配置以退火晶片的热源1524。退火系统1508可以是例如快速热退火系统或激光退火系统。群集工具1500可包含清洁系统,所述清洁系统经配置以清洁晶片的沉积表面。例如,群集工具1500可包括siconi清洁系统1510。siconi清洁系统可包括经由化学工艺操作的系统,该化学工艺去除氧化的硅。更具体地,其可指在真空处理腔室中使用氟化铵作为温和hf源的工艺。hf材料与晶片表面上的氧化硅反应以产生sif4和作为易从晶片表面去除的挥发性副产物的水。群集工具1500也可包括溅射清洁系统、反应离子蚀刻清洁系统或等离子体清洁系统1512。群集工具1500也可包括溅射金属沉积系统或溅射封装系统1514。

48.群集工具1500可包含经配置以将封装层安置于晶片上的封装系统1516。封装系统1516可以是例如原子层沉积(ald)或金属有机化学气相沉积(mocvd)封装系统、或等离子体封装系统。封装材料的沉积可以是定向的,并且可以包括例如用氧化硅或氧化铝的膜封装晶片。

49.群集工具1500可包括附加的反应性离子蚀刻工艺和清洁系统1518。群集工具1500可包括输入/输出1520,输入/输出1520经配置以接收用于处理的晶片,且一旦处理完成就输出晶片。群集工具1500可包含自动化传送系统,该自动化传送系统经配置以将晶片从一个制造工具传送至另一制造工具。例如,组合工具1500可以在输入/输出1520处接收晶片,然后在多个可选择的制造工具1502-1518中对晶片进行处理。可以在可选择的制造工具1502-1518中的每中或在可选择的制造工具1502-1518的子集中处理晶片。根据本发明的实施例,群集工具1500在输入/输出1520处接收晶片,使用siconi清洁系统1510清洁晶片,使用沉积系统1502沉积第一杜兰桥约瑟夫森结引线,使用介电系统1504形成介电层,并且使用第二沉积系统1506沉积第二杜兰桥约瑟夫森结引线。群集工具1500接着使用退火系统1508来退火晶片,且在输入/输出1520处输出晶片。作为非限制性实例提供了该过程。群集工具1500可包括比图15中示意性示出的制造工具更多的、更少的或替代的制造工具,并且制造工具的位置和顺序可不同于图15中示出的制造工具的位置和顺序。

50.群集工具1500可经配置以同时处理多个晶片。例如,每个可选择的制造工具1502-1518可以被配置成在给定时间保持一个或多个晶片。晶片可以从一个制造工具传递到下一个制造工具,使得多个晶片同时在生产过程中的不同阶段。群集工具1500可实现晶片的生产而不破坏真空。

51.群集工具1500实现工艺控制和原位测量。金属层的厚度可以被控制,在沉积期间,沉积腔室和晶片的温度可以被控制。例如,沉积系统1502、1506可以包括在沉积期间冷却晶

片的制冷系统,以避免由于原子聚集而在沉积膜中形成团块和凸块。例如,制冷系统可以将晶片冷却到-30℃或更低。

52.群集工具1500还使得能够控制介电层的厚度,且确保跨越接近掩模中的缝隙的金属沉积的均匀性。群集工具1500提供能够进行全晶片生产的化学沉积均匀性,并且能够优化每个处理步骤。群集工具1500可以使用与多个可选择的制造工具1502-1518中的每个可选择的制造工具兼容的光刻材料。此外,在将晶片输入至群集工具1500之前,可在晶片上形成诸如图4中示意性示出的具有第一层402和第二层404的剥离掩模的剥离掩模。

53.图16是根据本发明的一些实施例的用于执行成角度的沉积的方法1600的示意图。方法1600包括提供沉积源1602。方法1600包括将接近掩模布置在沉积源的沉积路径中,接近掩模在相对于沉积源的第一位置处具有缝隙1604。方法1600包括在沉积源材料的沉积期间相对于缝隙平移晶片,使得沉积角度保持实质上恒定,且使得接近掩模防止具有偏离缝隙对准的轨迹的沉积源材料接触晶片1606。

54.根据一些实施例,方法1600进一步包括在沉积于晶片上的沉积源材料上形成介电层。方法1600可进一步包括:将缝隙相对于沉积源的位置改变至不同于第一位置的第二位置;以及在沉积源材料的第二沉积期间相对于缝隙平移晶片,使得第二沉积的角度保持实质上恒定,且使得接近掩模防止具有不与缝隙对准的轨迹的沉积源材料接触晶片。

55.根据本发明的一些实施例,蒸发单元包括能够在金属沉积期间扫描的晶片台以及与源成角度的接近掩模。蒸发单元可以包括细长的源材料容器,以使材料能够跨细长的准直罩均匀供应,从而在晶片被扫描通过细长的蒸发准直开口时使得能够进行均匀的晶片涂覆。根据本发明的一些实施例,群集工具能够在不破坏真空的情况下原位完全处理装置模块结构。群集工具包括用于晶片清洁、金属沉积、介电沉积、退火、全晶片扫描有角度的金属蒸发(具有生产价值的临界尺寸控制)和封装的工具。

56.已经出于说明的目的呈现了本发明的各种实施方式的描述,但并不旨在是详尽的或者限于所公开的实施方式。在不脱离所描述的实施例的范围和精神的情况下,许多修改和变化对本领域普通技术人员将是显而易见的。这里使用的术语被选择来最好地解释实施例的原理、实际应用或对在市场中找到的技术的技术改进,或者使得本领域普通技术人员能够理解这里公开的实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。