存储体组交错

背景技术:

1.便携式计算设备(“pcd”)对于人们来说正在成为个人水平和专业水平的必需品。这些设备可以包括蜂窝电话(例如,智能手机)、便携式数字助理(“pda”)、便携式游戏控制台、掌上电脑和其他便携式电子设备。pcd通常包含集成电路或片上系统(“soc”),其包括被设计成一起工作以向用户交付功能的许多组件。例如,soc可以包含任意数目的处理器,诸如具有多个核的中央处理单元(“cpu”)、图形处理单元(“gpu”)等。在其他功能中,这样的处理器可以访问存储器。

2.soc处理器可以访问的一种常见类型的存储器被称为双倍数据速率同步动态随机存取存储器(“ddr-sdram”,或简称为“ddr”)。由于pcd是电池供电设备,其中节省功率是重要目标,因此pcd中的ddr的常见类型是低功率drr(“lpddr”)。ddr技术(包括lpddr技术)已经在通常被称为ddr、ddr2、ddr3、ddr4、ddr5等的迭代中发展。一些后来的ddr迭代的特征(称为存储体组(bank group))将存储器组织成两个或更多个存储体组,每个存储体组具有两个或更多个存储体。两个或更多个存储体组可以被并行访问。例如,在具有两个存储体组的ddr方案中,在发出访问第一存储体组的命令之后,存储器控制器可以在第一存储体组访问完成之前发出访问第二存储体组的命令。在两个存储体组之间发出以交替方式或乒乓(ping-ponging)方式引导的连续的访问命令比两个或更多个连续的访问命令被引导到同一个存储体组导致更低的等待时间。

3.将前述示例扩展到具有四个存储体组的ddr方案,存储器控制器可以以尝试将两个连续访问被引导到同一存储体组的实例最小化的方式在四个存储体组之间交错访问命令。更一般地,为了提高存储器利用率,存储器控制器可以以尝试在所有的存储体组和存储体之间均匀分布访问的方式在四个存储体组之间交错访问命令。希望进一步改善存储体组和存储体之间的分布,从而改善存储器利用率,并且在ddr系统中提供相关的益处。

技术实现要素:

4.公开了用于同步动态随机存取存储器(sdram)系统中的存储体交错的系统、方法和计算机程序产品。

5.一种用于存储体交错的示例性方法可以包括存储器控制器通过对初始的物理存储器地址的多个存储体组地址位、初始的物理存储器地址的多个存储体地址位以及初始的物理存储器地址的多个行地址位进行散列处理,来生成新的存储体组地址位和新的存储体地址位。该方法还可以包括存储器控制器通过用相应的新的存储体组地址位和存储体地址位替换初始的物理存储器地址的存储体组地址位和存储体地址位来生成经修改的物理存储器地址。该方法可以包括存储器控制器向sdram芯片提供经修改的物理存储器地址。

6.另一种用于存储体交错的示例性方法可以包括存储器控制器生成物理存储器地址,该物理存储器地址具有相较于物理存储器地址的最高有效位(msb)更靠近物理存储器地址的最低有效位(lsb)被定位的多个存储体组地址位。该方法可以包括存储器控制器向sdram芯片提供物理存储器地址。

附图说明

7.在附图中,除非另有说明,否则在各个视图中,相似的附图标记指代相似的部分。对于具有字母字符标记的附图标记,诸如“102a”或“102b”,字母字符标记可以区分出现在同一附图中的两个相似的部分或元件。在所有附图中,当一个附图标记旨在涵盖具有相同附图标记的所有部分时,可以省略附图标记的字母字符标记。

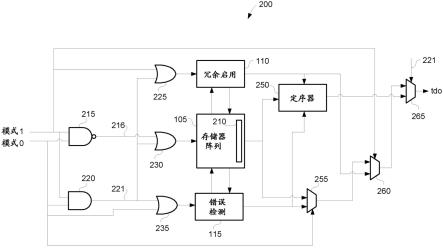

8.图1是根据示例性实施例的体现用于交错存储体组的系统和方法的ddr-sdram系统的框图。

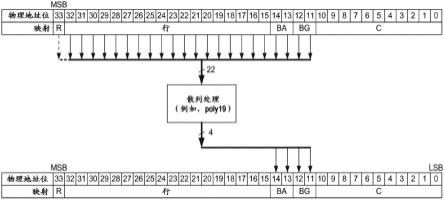

9.图2示出了根据示例性实施例的将散列方法应用于物理存储器地址方案或映射。

10.图3还示出了根据示例性实施例的图2的散列方法。

11.图4示出了根据示例性实施例的将散列方法应用于另一物理存储器地址方案或映射。

12.图5还示出了根据示例性实施例的图4的散列方法。

13.图6示出了根据示例性实施例的将散列方法应用于又一物理存储器地址方案或映射。

14.图7还示出了根据示例性实施例的图6的散列方法。

15.图8是示出根据示例性实施例的读取命令和相关信号的序列的时序图。

16.图9示出了根据示例性实施例的物理存储器地址方案或映射的示例。

17.图10是示出根据示例性实施例的用于交错与对存储体组地址进行散列处理相关的存储体组的方法的流程图。

18.图11是示出根据示例性实施例的用于对与基于操作模式选择物理地址方案或映射相关的存储体组进行交错的方法的流程图。

19.图12是根据示例性实施例的pcd的框图。

具体实施方式

20.本文使用的词语“示例性”是指“用作示例、实例或说明”。词语“说明性的”在本文可以用作“示例性的”的同义词。在本文中描述为“说明性的”或“示例性的”的任何方面不一定被解释为比其他方面更优选或更有利。

21.随着ddr-sdram技术的不断发展,改善ddr-sdram中的存储体和存储体组之间的分布变得愈加重要。例如,lpddr5规范要求,当操作的频率超过1600mhz时,被称为bl16的类型(其为128位边界上的32字节访问)的两个连续突发(burst)访问必须在不同的存储体组中。(另一种类型的突发访问被称为bl32,其为256位边界上的64字节访问。)

22.如图1所示,存储器系统100可以包括耦合到存储器控制器104的ddr-sdram或ddr 102。ddr 102被组织为两个存储列(rank)106:第一存储列106a和第二存储列106b。第一存储列106a被组织为四个存储体组(bank group)110:第一存储体组110a、第二存储体组110b、第三存储体组110c和第四存储体组110d。第二存储列106b被类似地组织为另外四个存储体组110:第五存储体组110e、第六存储体组110f、第七存储体组110g和第八存储体组110h。存储体组110可以替代地由索引0-3来标识:存储体组110a和110e各自可以被标识为“bg_0”;存储体组110b和110f各自可以被标识为“bg_1”;存储体组110c和110g各自可以被标识为“bg_2”;并且存储体组110d和110h各自可以被标识为“bg_3”。每个存储体组110可以

被组织为四个存储体(bank)112,这些存储体也可以被标识为bank_0、bank_1、bank_2和bank_3。为清楚起见,在图1中以概念性的方式描绘了ddr 102,并且没有指示各自的物理存储器芯片。相反,存储列106、存储体组110和存储体112可以以任何方式被映射到物理存储器芯片。尽管在图1所示的实施例中存在四个存储体组110,每个存储体组具有四个存储体112,但是在其他实施例中可以有其他数目的存储体组和存储体。

23.尽管为清楚起见,在图1中没有示出ddr 102与存储器控制器104之间传送的所有信号,但是与本公开相关的一些信号可以包括:激活(“act”)信号、行地址选择(“ras”)信号、列地址选择(“cas”)信号、(行和列)地址(“addr”)、存储体地址(“ba”)、存储体组(“bg”)地址、存储列地址(“r”)和突发地址(“b”)。应当理解,这些信号被概念性地示出,并不一定表示物理总线或信号线。根据上面关于图1描述的示例,存储列地址r可以由一位组成,存储体组地址可以由两位bg[1:0]组成,并且存储体地址可以由两位ba[1:0]组成。此外,例如,行地址可以是18位r[17:0],列地址可以是6位c[5:0](例如,表示2kb页面中的bl16地址),并且突发地址可以是4位b[3:0]。然而,如下所述,在许多示例中,突发地址可以被设置为零。因此,完整的物理地址(不包括突发地址)可以由总共例如34位组成。

[0024]

根据本公开的一个方面,随机化存储体和存储体组之间的访问可以通过改善存储体和存储体组上的分布来改善存储器利用率。随机化访问可以包括将散列算法应用于存储体地址、存储体组地址或者存储体地址和存储体组地址两者。该算法可以将存储体地址和存储体组地址与例如行地址进行散列处理。在一些示例中,该算法可以将存储体地址和存储体组地址仅与行地址进行散列处理;不将存储体地址和存储体组地址与任何其他位(诸如列地址的位)进行散列处理。存储器控制器104(图1)可以在访问请求期间在向ddr 102提供物理地址之前对物理地址执行散列算法。

[0025]

如图2所示,在一个示例中,使用poly19散列算法将存储体组地址位bg[1:0]和存储体地址位ba[1:0]与行地址位r[17:0]一起进行散列处理。在图3中示出了将poly19散列算法应用于物理地址。在一些实施例中,存储列地址位r也可以与前述位一起被散列,如从存储列地址位r起的虚线箭头所示。在图2-图3所示的示例中,物理地址被定义为具有映射到第33位位置的存储列地址(位)r、映射到第32位位置至第15位位置的行地址r[17:0]、映射到第14位位置的ba[1]、映射到第13位位置的ba[0]、映射到第12位位置的bg[1]、映射到第11位位置的bg[0]以及映射到第10位位置至第5位位置的列地址c[5:0]。然而,为清楚起见,在图2中,第10位位置至第1位位置都被表示为列或“c”位,因为在一些示例(未示出)中可以被映射到第4位位置至第1位位置的突发地址b[3:0]在本示例中被固定为0值。在本示例中,第0位未被使用,因此也被固定为0值。

[0026]

散列算法可以在物理地址位的集合与散列矩阵之间执行矩阵乘法运算。在图3所示的poly19散列的示例中,该物理地址位的集合包括第11位至第32位,其可以用符号“a[32:11]”来表示,其中“a”是物理地址位阵列。图3中的散列矩阵是从伽罗瓦域(2)或“gf(2)”上的本原多项式推导出的:x4 x 1。矩阵乘法的结果是物理地址位的另一集合,并且因此散列算法的输出是物理地址位的另一集合,即,新的存储体地址位和存储体组位:{ba[1],ba[0],bg[1],bg[0]}。在图3中,矩阵乘法还以扩展形式被示为对ba[1]、ba[0]、bg[1]和bg[0]中的每一个的按位异或运算的字符串(由符号“^”表示)(为简洁起见,使用符号“ba1”、“ba0”、“bg1”和“bg0”来示出)。注意,只有由存储体组地址bg[1:0]和存储体地址ba

[1:0]组成的四个位(通过散列)被改变。也就是说,存储器控制器104保持存储列地址、行地址、列地址和突发地址不变。

[0027]

如图4所示,在另一示例中,使用poly19散列算法将存储体组地址位bg[1:0]和存储体地址位ba[1:0]类似地与行地址位r[17:0]一起进行散列处理。在一些实施例中,存储列地址位r也可以与前述位一起被散列处理,如从存储列地址位r起的虚线箭头所示。在图5中示出了将poly19散列算法应用于物理地址。在图4-图5所示的示例中,物理地址被定义为具有映射到第33位位置的存储列地址(位)r、映射到第32位位置至第15位位置的r[17:0]、映射到第14位位置的ba[1]、映射到第13位位置的ba[0]、映射到第12位位置的c[5]、映射到第11位位置的bg[1]、映射到第10位位置至第8位位置的c[4:2]、映射到第7位位置的bg[0]以及映射到第6位位置至第5位位置的c[1:0]。然而,为清楚起见,在图4中,第6位位置至第1位位置都被表示为列或“c”位,因为在一些示例(未示出)中可以被映射到第4位位置至第1位位置的突发地址b[3:0]在本示例中被固定为0值。在本示例中,第0位未被使用,因此也被固定为0值。

[0028]

在图5所示的poly19散列的示例中,该物理地址位的集合包括{a[32:13],a[11],a[7]}。由于图5中的基础的散列算法是与上面关于图3描述的相同的poly19,因此图5中的散列矩阵与图3中的散列矩阵相同。矩阵乘法的结果是物理地址位的集合,并且因此散列算法的输出是物理地址位的集合:{ba[1],ba[0],bg[1],bg[0]}。矩阵乘法在图5中也以与上面关于图3描述的相同方式以扩展形式示出。注意,只有由存储体组地址bg[1:0]和存储体地址ba[1:0]组成的四个位(通过散列)被改变。也就是说,存储器控制器104保持存储列地址、行地址、列地址和突发地址不变。

[0029]

如图6所示,在另一示例中,使用poly37散列算法将存储体组地址位bg[1:0]和存储体地址位ba[1:0]类似地与行地址位r[17:0]一起进行散列处理。然而,注意,在该实施例中,存储列地址位r也与前述位一起被散列处理。在图7中示出了将poly37散列算法应用于物理地址。在图6-图7所示的示例中,物理地址被定义为具有映射到第15位位置的存储列地址(位)r、映射到第33位位置至第16位位置的r[16:0]、映射到第14位位置的ba[1]、映射到第13位位置的ba[0]、映射到第12位位置的c[5]、映射到第11位位置的bg[1]、映射到第10位位置至第8位位置的c[4:2]、映射到第7位位置的bg[0]以及映射到第6位位置至第5位位置的c[1:0]。然而,为清楚起见,在图6中,第6位位置至第1位位置都被表示为列或“c”位,因为在一些示例(未示出)中可以被映射到第4位位置至第1位位置的突发地址b[3:0]在本示例中被固定为0值。在本示例中,第0位未被使用,因此也被固定为0值。

[0030]

在图7所示的poly37散列的示例中,该物理地址的集合包括{a[33:13],a[11],a[7]}。图7中的散列矩阵是从gf(2)上的本原多项式推导出的:x5 x2 1。矩阵乘法的结果是物理地址位的集合,并且因此散列算法的输出是物理地址位的集合:{r,ba[1],ba[0],bg[1],bg[0]}。对于r、ba[1]、ba[0]、bg[1]和bg[0]中的每一个,在图7中还以扩展形式示出了矩阵乘法。注意,只有由存储体组地址bg[1:0]和存储体地址ba[1:0]组成的四个位(通过散列)被改变。也就是说,存储器控制器104保持存储列地址、行地址、列地址和突发地址不变。尽管在前述示例中使用了poly19和poly37散列算法,但是本领域普通技术人员将会理解,可以使用其他散列算法。

[0031]

如图8所示,在存储器读取操作的序列的示例中,作为上述散列方法或用于改善存

储体交错的其他方法的结果,没有两个连续的bl16读取命令(“rdx”)被引导到同一存储体组,从而符合lpddr5规范的该要求。图8所示的示例中的写入时钟(“wck”)频率可以是3200mhz。应当注意,在图8中,数据在延迟之后出现在数据总线上,这是读取时延。还应注意,尽管命令(“cmd”)和数据在图8中垂直对齐,但是在rd命令流与数据响应流之间存在时间延迟。

[0032]

图8中所示的示例还示出了,尽管在存储体之间的分布相对较小,但是仍然可以实现高ddr利用率。如果不是图8所示的示例,而是其中所有的读取事务都被引导到同一存储体组的示例(未示出),则只能实现50%的ddr利用率。假设在图8中,所有的rdx是到同一bg的rd0。每隔一个奇数周期(1、5、9

……

)最多会有一个rd0。因此,只有50%的数据总线可以被利用。

[0033]

如果不是图8所示的示例,而是其中两个bl16读取事务(即64字节随机事务)被引导到同一存储体(在同一存储体组中)的示例(未示出),则只能实现8%的ddr利用率。更具体地,在这种情况下,两个bl16事务将被引导到同一存储体中的不同行,即,存储体冲突。每次这样的访问需要激活同一存储体中的不同行。同一存储体的两次激活之间的最小时间是ddr trc时序,为60ns。在3200mhz下,数据总线上两次bl16数据传输的持续时间为5ns。因此,数据总线利用率将是5/60,约为8%。

[0034]

如果不是图8所示的示例,而是其中两个bl16读取事务(即64字节随机事务)被分布在12个存储体上的示例(未示出),则可以实现100%的ddr利用率。由于对于在数据总线上各自花费5ns的两个bl16事务,最多每60ns激活一个存储体,因此需要60/5个存储体(即并行的12个存储体)来实现100%的利用率。然而,从图8所示的示例中可以注意到,8个bl16读取事务(即256字节随机事务)可以被分布在仅4个存储体上,并且仍然实现100%的ddr利用率。因此,该示例示出了,即使在4个存储体的相对较小的分布的情况下,也可以实现100%的ddr利用率。

[0035]

根据本发明的另一方面,通过将一个或多个存储体地址位和存储体组地址位分别映射到相较于最高有效位(“msb”)更靠近最低有效位(“lsb”)的物理地址位位置,可以增加存储体和存储体组之间的分布。存储器控制器104(图1)可以在访问请求期间在向ddr102提供物理地址之前执行这种映射。

[0036]

传统上,与行地址相比,列地址可以被映射到ddr物理地址的较低阶的位。也就是说,根据传统的ddr地址映射方案(未示出),相较于物理地址的msb端更靠近lsb端的一组顺序的位置可以定义列地址,并且物理地址中更靠近物理地址的msb端的另一组顺序的位置可以定义行地址。此外,传统上,与存储体地址相比,存储体组地址可以被映射到物理地址的更高阶的位,并且与行地址和列地址相比,存储体地址可以被映射到物理地址的更高阶的位。

[0037]

如图9所示,在各种示例中,一个或多个存储体组地址位或存储体地址位可以被映射到物理地址中相较于msb更靠近lsb的位置。这些示例认识到,在存储体组分布与页面命中率之间存在折中。只要存储体组分布足以满足期望的约束,诸如上面提到的没有两个连续的bl16读取命令被引导到同一存储体组的lpddr5要求,最大化页面命中率对于性能和功效来说就是最好的。然而,存储体组地址位或存储体地址位被映射到离lsb越近(并且离msb越远),对页面命中率的负面影响越大(即,页面未命中的可能性越大)。尽管在所示示例中,

物理地址大小是34位(即第33位位置定义msb),但是本文描述的原理可以被应用于其他大小的物理地址。地址位的数目取决于dram密度。

[0038]

在一个可以被称为“默认”映射的映射示例中,存储体地址位和存储体组地址位被映射到大约在物理地址中间但稍微更靠近lsb的位置,诸如,例如跨越第11位位置至第14位位置。因为第33位位置定义了msb,所以第14位位置与msb之间的距离是19个位位置,而第11位位置与lsb之间的距离是11个位位置。注意,第11位位置至第14位位置中的每个位置相较于msb更靠近lsb。更具体地,在图9所示的“默认”映射示例中,ba[1]被映射到第14位位置,ba[0]被映射到第13位位置,bg[1]被映射到第12位位置,并且bg[0]被映射到第11位位置。此外,在该默认映射示例中,存储列地址位r被映射到第33位位置,行地址r[17:0]被映射到第32位位置至第15位位置,并且列地址c[5:0]被映射到第10位位置至第5位位置。虽然突发地址b[3:0]可以被映射到第4位位置至第1位位置,但是这些位通常被固定为0值。在所示示例中,物理地址的第0位未被使用(即,也被设置为固定值0),因为突发单元是16位的,所以突发单元是一对字节。可以注意到,在默认映射示例中,存储体地址位和存储体组地址位被映射到比行地址更低阶的位位置和比列地址更高阶的位位置。

[0039]

在图9所示的另一映射示例中,其可以被称为“同步模式”映射,存储体地址位和存储体组地址位被类似地映射到物理地址中行地址与列地址之间的位置。更具体地,在图9所示的“同步模式”映射示例中,ba[1]被映射到第14位位置,ba[0]被映射到第13位位置,bg[1]被映射到第11位位置,并且bg[0]被映射到第7位位置。在本示例中,两个存储体地址位ba[1:0]和存储体地址位中的一个地址位bg[1]被映射到物理地址的大约中间的位置,而另一存储体地址位bg[0]被映射到甚至更靠近lsb的位置。此外,在该同步模式映射示例中,存储列地址位r被映射到第33位位置,行地址r[17:0]被映射到第32位位置至第15位位置,列地址位c[2]被映射到第12位位置,列地址位c[5:3]被映射到第10位位置至第8位位置,列地址位c[1:0]被映射到第6位位置至第5位位置,并且其余的位(在第4位位置至第0位位置中)被固定为0值。术语“同步模式”是指wck cas同步模式。与除wck cas同步模式之外的操作模式相比,存储列到存储列的切换引起相对较高的惩罚(penalty)。存储列位r被映射到物理地址msb(即所示示例中的第33位位置),因为最大化同一存储列中的批次(即连续访问)可以帮助避免存储列到存储列的切换的相对较高的惩罚。

[0040]

在图9所示的又一映射示例中,其可以被称为“优化刷新模式”映射,ba[1]被映射到第14位位置,ba[0]被映射到第13位位置,bg[1]被映射到第7位位置,并且bg[0]被映射到第11位位置。换句话说,在优化刷新模式映射示例中,bg[0]和bg[1]被映射到与它们在同步模式示例中所映射到的位置交换(即,相反)的位置。注意,在优化刷新模式示例中,存储体组地址的较低阶的位bg[0]被映射到物理地址中比存储体组地址的较高阶的位bg[1]所映射到的位置(第7)更高阶的位置(第11)。术语“优化刷新模式”是指每存储体刷新命令,该每存储体刷新命令用于刷新具有相同ba[1:0]位和bg[0]位的一对存储体。因此,将bg[1]映射到比bg[0]更低阶的位置可以提高性能,因为同时刷新的存储体将阻塞更窄的地址空间。在本示例中,两个存储体地址位ba[1:0]和存储体地址位中的一个存储体地址位bg[0]被映射到物理地址的大约中间的位置,而另一存储体地址位bg[1]被映射到甚至更靠近lsb的位置。其余的位(即存储列地址、行地址和列地址)被映射到与上述同步模式映射示例中相同的位置。

[0041]

在图9所示的又一映射示例中,其可以被称为“自由运行模式”映射,除了一个例外,存储体地址、存储体组地址、行地址和列地址被映射到与上述优化刷新模式中相同的位置。术语“自由运行模式”是指wck自由运行模式。在自由运行模式中,由存储列到存储列的切换引起的上述惩罚低于同步模式中的损失。由于双存储列ddr系统可以被视为两个存储列的存储体的单个系统(例如,总体32个存储体),因此可以通过将存储列地址位r映射到相较于msb更接近lsb的物理地址来利用总体存储体增加存储体分布。图9中所示的自由运行模式映射示例与优化刷新模式映射示例之间的区别在于,在自由运行模式示例中,存储列地址位r可以被映射到第15位位置,而在刷新模式(以及上述其他模式)中被映射到该位位置的r[0]位可以被映射到第33位位置。在所示的示例中,其中第33位位置定义了msb,第15位位置与msb之间的距离是18个位位置,而第15位位置与lsb之间的距离是15个位位置。

[0042]

如图10所示,响应于存储器访问命令,可以执行用于sdram系统中存储体组交错的示例性方法。如框1002所示,存储器控制器(图10中未示出)可以通过对初始的物理存储器地址的多个存储体组地址位、初始的物理存储器地址的多个存储体地址位以及初始的物理存储器地址的多个行地址位进行散列处理,来生成新的存储体组地址位和新的存储体地址位。如上文关于图2-图7所述,可以将与存储体组地址(例如,两位)结合的存储体地址(例如,也是两位,总共四位)与行地址进行散列处理,以获得更随机化的存储体地址和存储体组地址。除了行地址之外的位(诸如列地址位)可以从与存储体组地址进行散列处理的位中被排除。

[0043]

如框1004所示,存储器控制器可以通过用相应的新的存储体组地址位和存储体地址位替换初始的物理存储器地址的存储体组地址位和存储体地址位,来生成经修改的物理存储器地址。如框1006所示,存储器控制器然后可以向物理sdram存储器芯片提供经修改的物理存储器地址,而不是初始的或原始的物理存储器地址。

[0044]

如图11所示,如框1102所示,响应于存储器访问命令,可以开始用于sdram系统中的存储体组交错的示例性方法。存储器控制器(图11中未示出)可以诸如以上面关于图9描述的方式来生成物理存储器地址,在该物理存储器地址中,一个或多个存储体组位或者一个或多个存储体地址位或者存储列位中的每一个位相较于msb更靠近lsb被定位。

[0045]

尽管图11中未示出,但是存储器控制器可以取决于sdram正进行操作的模式,从两个或更多个替代方案当中选择一个映射。例如,当sdram系统在wck cas同步模式下操作时,存储器控制器可以生成物理存储器地址,在该物理存储器地址中,存储体组位中的一个位比sdram系统在默认模式(即,除了wck cas、刷新模式或wck自由运行模式之外的任何模式)下操作时更靠近lsb被定位。当sdram系统在优化刷新模式下操作时,可以将存储体组地址的较低阶的位映射到物理地址中的比存储体组地址的较高阶的位更高阶的位置。存储器控制器然后可以向物理sdram存储器芯片提供物理地址,如框1104所示。当sdram系统在wck自由运行模式下操作时,可以将存储列地址映射到相较于msb更靠近lsb的位置。

[0046]

应当理解,上述方法1100(图11)和1000(图10)可以以组合方式体现。也就是说,根据方法1000的存储体地址位和存储体组地址位的散列可以应用于根据方法1100被映射到物理存储器地址的位。

[0047]

如图12所示,用于存储体组交错的系统和方法的说明性或示例性实施例可以被体现在pcd 1200中。pcd 1200包括片上系统(“soc”)1202,即体现在集成电路芯片中的系统。

soc 1202可以包括cpu 1204、gpu 1206或其他处理器。cpu 1204可以包括多个核,诸如第一核1204a、第二核1204b等,直至第n核1204n。soc 1202可以包括模拟信号处理器1208。

[0048]

显示控制器1210和触摸屏控制器1212可以耦合到cpu 1204。soc 1202外部的触摸屏显示器1214可以耦合到显示器控制器1210和触摸屏控制器1212。pcd 1200还可以包括视频解码器1216。视频解码器1216耦合到cpu 1204。视频放大器1218可以耦合到视频解码器1216和触摸屏显示器1214。视频端口1220可以耦合到视频放大器1218。通用串行总线(“usb”)控制器1222也可以耦合到cpu 1204,并且usb端口1224可以耦合到usb控制器1222。用户标识模块(“sim”)卡1226也可以耦合到cpu 1204。

[0049]

一个或多个存储器可以耦合到cpu 1204。一个或多个存储器可以包括易失性存储器和非易失性存储器两者。易失性存储器的示例包括静态随机访问存储器(“sram”)1228以及动态ram(“dram”)1230和1231。这种存储器可以在soc 1202的外部(诸如dram1230),或者在soc 1202的内部(诸如dram 1231)。耦合到cpu 1204的dram控制器1232可以控制向dram 1230和1231写入数据以及控制从dram 1230和1231读取数据。

[0050]

dram控制器1232可以是上面关于图1描述的存储器控制器1204的示例,并且一个或两个dram 1230-1231可以是上面关于图1描述的ddr 1202的示例。dram控制器1232可以被配置为(包括在一些示例中通过固件)控制上面关于图10-图11描述的方法。在dram控制器1232或其他处理器由固件、软件等来配置的实施例中,存储在其中(或任何其他数据存储介质中)的相关联的存储器和固件可以定义“计算机程序产品”或“计算机可读介质”,如专利词典中所理解的那样。

[0051]

立体声音频codec(编解码器)1234可以耦合到模拟信号处理器1208。此外,音频放大器1236可以耦合到立体声音频codec1234。第一立体声扬声器1238和第二立体声扬声器1240可以分别耦合到音频放大器1236。此外,麦克风放大器1242可以耦合到立体声音频codec 1234,并且麦克风1244可以耦合到麦克风放大器1242。调频(“fm”)无线电调谐器1246可以耦合到立体声音频codec 1234。fm天线1248可以耦合到fm无线电调谐器1246。此外,立体声耳机1250可以耦合到立体声音频codec 1234。可以耦合到cpu 1204的其他设备包括数字(例如,ccd或cmos)相机1252。

[0052]

调制解调器或射频(“rf”)收发器1254可以耦合到模拟信号处理器1208。rf开关1256可以耦合到rf收发器1254和rf天线1258。此外,小键盘1260、具有麦克风的单声道耳机1262和振动器设备1264可以耦合到模拟信号处理器1208。

[0053]

电源1266可以经由电源管理集成电路(“pmic”)1268耦合到soc 1202。电源1266可以包括可充电电池或者从连接到ac电源的ac到dc变压器得到的dc电源。

[0054]

soc 1202可以具有一个或多个内部热传感器或片上热传感器1270a,并且可以耦合到一个或多个外部热传感器或片外热传感器1270b。模数转换器(“adc”)控制器1272可以将由热传感器1270a和1270b产生的压降转换成数字信号。

[0055]

在该示例性或说明性实施例中,触摸屏显示器1214、视频端口1220、usb端口1224、相机1252、第一立体声扬声器1238、第二立体声扬声器1240、麦克风1244、fm天线1248、立体声耳机1250、rf开关1256、rf天线1258、小键盘1260、单声道耳机1262、振动器1264、热传感器1270b、adc控制器1272、pmic 1268、电源1266、dram 1230以及sim卡1226在soc 1202的外部。然而,将会理解,在其他实施例中,这些设备中的一个或多个可以被包括在这样的soc

中。

[0056]

对于本发明所属领域的普通技术人员来说,在不脱离其精神和范围的情况下,替换的实施例将变得显而易见。因此,尽管已经详细说明和描述了所选择的方面,但是应当理解,在不脱离由所附权利要求限定的本发明的精神和范围的情况下,可以在其中进行各种替换和变更。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。